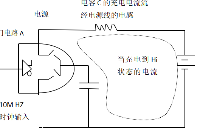

在某單板上,由于CPU芯片GMII接口的電源上只加了磁珠濾波,引起的故障:在網口通信時,當通信包的內容為低速碼型(全0全1)時,沒有丟包;當更改為偽隨機包時(碼型速率快),丟包嚴重。最終在磁珠后加電容,問題解決。

2022-10-25 17:06:18 3935

3935

PCB layout需要豐富的經驗和扎實的理論基礎支持,還要多踩幾個坑,多做幾個仿真加深對走線的理解,才能形成閉環的走線設計。

2022-07-19 15:10:41 4372

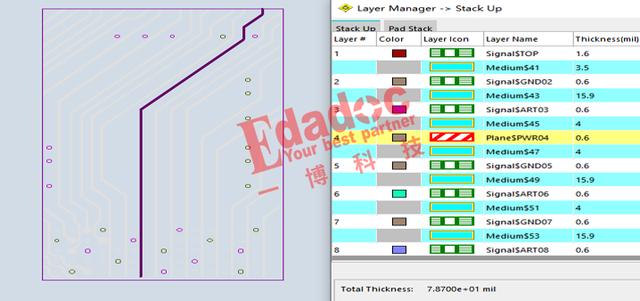

4372 很多人對于PCB走線的參考平面感到迷惑,經常有人問:對于內層走線,如果走線一側是VCC,另一側是GND,那么哪個是參考平面?

2022-09-09 13:05:47 5352

5352 本文要點PCB走線具有電感和電容,這兩者共同決定了走線的阻抗。有時,了解走線的電感有助于估算因串擾而引起的耦合度。雖然沒有設定具體的走線電感值,但它是理解某些系統中的信號行為的有力工具。所有PCB走

2024-12-13 16:54:57 3898

3898

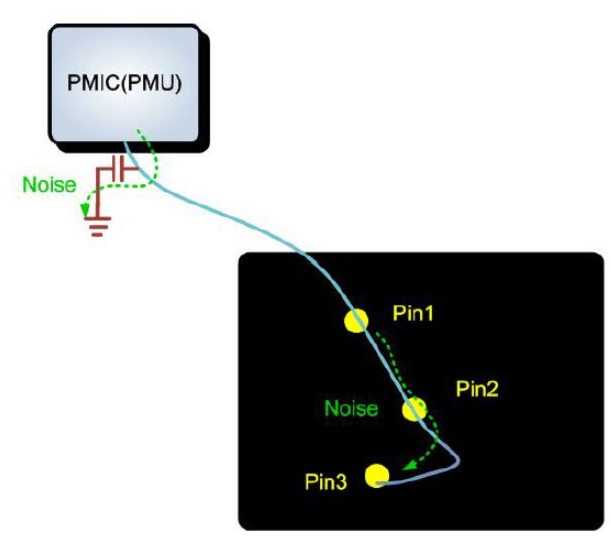

消除串擾的方法合理的PCB布局-將敏感的模擬部分與易產生干擾的數字部分盡量隔離,使易產生干擾的數字信號走線上盡量靠近交流地,使高頻信號獲得較好的回流路徑。盡量減小信號回路的面積,降低地線的阻抗,采用多點接地的方法。使用多層板將電源與地作為獨立的一層來處理。合理的走線拓樸結構-盡量采用菊花輪式走線

2009-06-18 07:52:34

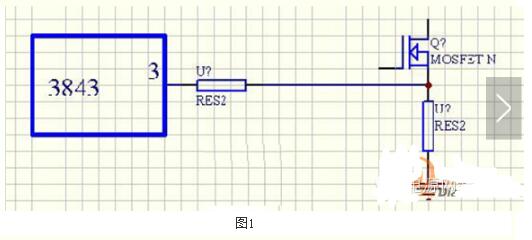

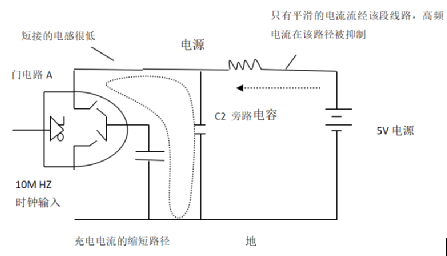

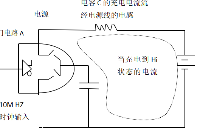

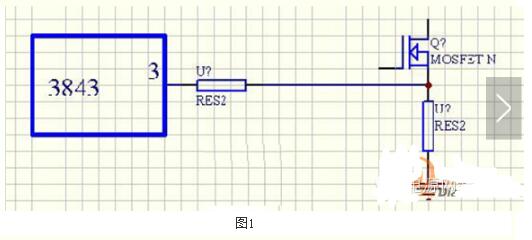

電源的VCC引腳,由于端子較遠,VCC走線過長,寄生電感導致的電路振蕩現象;增加儲能電容之后,這個情況可能不會出現;簡單理解就是,在負載需要瞬態變化的電流時,引線電感不能提供,而有儲能電容提供;如果

2019-03-27 07:39:54

地,差模電感后電容接輸出地。14、高頻脈沖電流流徑的區域:A:盡量縮小由高頻脈沖電流包圍的面積上圖所標示的5個環路包圍的面積盡量小。B:電源線、地線盡量靠近,以減小所包圍的面積,從而減小外界磁場環路切割

2020-08-01 07:54:14

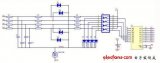

電源布局、網口電路、音頻走線的PCB設計

2021-03-04 06:10:24

`幫忙看下下圖那三根線怎么處理合適下圖keepout層圓圈邊上的頂層那三根線這樣好,還是兩個一連另外個垂直。或者還有其他辦法。下圖點亮的那個線是DGND,隔開他們的底層那個線式一個電源線。我就這樣走

2011-07-19 16:14:30

本帖最后由 leozh456 于 2012-2-19 00:16 編輯

AD9 自動走線時部分線路已經手動走完了線,后自動走線時那些已經手動走過的線比如電源地等焊盤,軟件會在原來基礎上從新走線

2012-02-19 00:16:35

好的圖像質量的保證。 PCB走線如果可能的話,信號走線使用6mil, 走線間距使用6mil. 放置0.1uF的退耦電容在對應的DSP電源腳上,并盡可能的靠近。它的走線盡可能的粗。電源正極的走線最少要

2023-04-13 16:09:54

斯1艾1姆1科1技全國1首家P|CB樣板打板所以時鐘IC引腳一般都接RC端接,但蛇形走線并非起電感的作用,相反的,電感會使信號中的上升元中的高次諧波相移,造成信號質量惡化,所以要求蛇形線間距最少是線寬

2013-08-29 15:43:30

2、濾波電感。對一些重要信號,如INTEL HUB架構中的HUBLink,一共13根,跑233MHz,要求必須嚴格等長,以消除時滯造成的隱患,繞線是唯一的解決辦法。一般來講,蛇形走線的線距>=2

2017-11-22 20:04:14

RC端接,但蛇形走線并非起電感的作用,相反的,電感會使信號中的上升元中的高次諧波相移,造成信號質?惡化,所以要求蛇形線間距最少是線寬的兩倍,信號的上升時間越小就越?受分布電容和分布電感的影響。 因為

2018-09-20 11:05:23

、阻抗匹配 2、濾波電感。對一些重要信號,如INTEL HUB架構中的HUBLink,一共13根,跑233MHz,要求必須嚴格等長,以消除時滯造成的隱患,繞線是唯一的解決辦法。一般來講,蛇形走線的線距

2020-07-14 18:02:17

:1、阻抗匹配 2、濾波電感。 對一些重要信號,如INTEL HUB架構中的HUBLink,一共13根,跑233MHz,要求必須嚴格等長,以消除時滯造成的隱患,繞線是唯一的解決辦法。一般來講,蛇形走線

2018-08-30 10:14:44

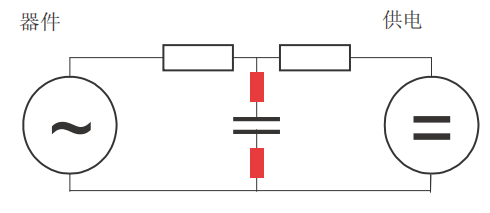

本期干貨:PCB設計中電源布局、網口電路、音頻走線應該注意哪些問題呢?一.電源布局1、電源入口處隨著電流方向電容擺放順序:由大到小2、電源出口處隨著電流方向電容擺放順序:由大到小3、輸出開關腳SW

2017-09-14 17:45:50

的數據;在走線時一般遵循3W法則(繞線的間距要兩倍于線寬),這樣可消除線間78%的互感,盡量減少因電感變化而引起的阻抗不連續。 另外說明我不是高手,抬得越高摔得越痛;若想見識高手,可以到WWW

2014-11-19 11:54:01

短。1.5 合理分配電源和地。1.6 DGND、AGND、實地分開。1.7 電源及臨界信號走線使用寬線。1.8 數字電路放置於并行總線/串行DTE接口附近,DAA電路放置於電話線接口附近。2. 元器件

2014-03-14 17:44:44

2、濾波電感。對一些重要信號,如 INTEL HUB架構中的HUBLink,一共13根,跑233MHz,要求必須嚴格等長,以消除時滯造成的隱患,繞線是唯一的解決辦法。一般來講,蛇形走線的線距>

2019-05-22 02:48:05

2、濾波電感。對一些重要信號,如INTEL HUB架構中的HUBLink,一共13根,跑233MHz,要求必須嚴格等長,以消除時滯造成的隱患,繞線是唯一的解決辦法。一般來講,蛇形走線的線距>

2016-12-07 22:20:49

走線時shift+空格,為什么改變不了走線模式呢???

2019-09-30 01:34:26

這拷貝的電源走線到信號走線一下線就變細了怎么弄的哦

2019-07-17 05:35:09

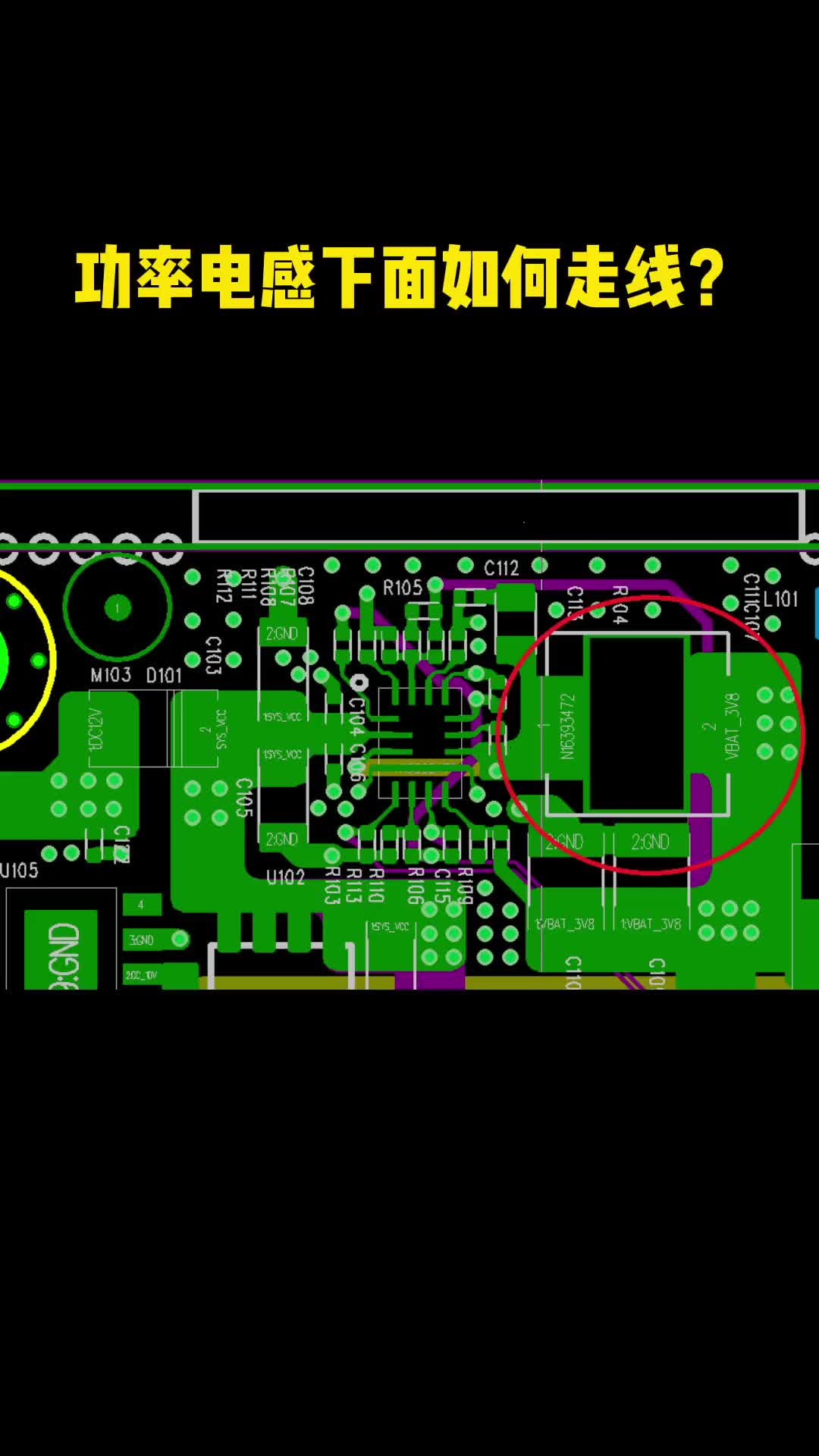

問題: 為何DC-DC 功率電感下方不該鋪銅跟走線回答: 從Eddy Current角度分析:如果鋪了銅,沒有凈空[1],則電感的磁場,會在該下方的金屬上,產生Eddy Current [2]。而

2020-11-18 13:36:31

近年來,裝機行業流行一個術語,即“走背線”,那么走背線是什么?裝機之家小編簡單介紹下,通俗的說:走背線就是針對電腦機箱,裝機的時候,將機箱內部和電源的線材做到最干凈整潔,從傳統來說,線材都是從機箱

2021-12-29 07:13:36

`內層的地層與電源層可以走線嗎理論上地層與電源層相鄰的面積越完整越近高頻的阻抗越 低,實務上當外層(top and bottom side)的高速走線電磁幅 射太強的時候,為了降低表層幅射強度,在

2014-02-19 18:23:03

有的板子在同一層 但是走線和焊盤顏色分信號線和電源線是怎么設置的

2019-11-26 21:30:08

問一個比較弱智的問題,如果我使用的是四層板,中間兩層分別為地和電源層,并且想要在電源層走線,我在添加層的時候,是不是只能選擇add layer而不是add plane?我現在是add plane,怎么能夠實現在電源層走線?

2019-07-04 04:36:10

在AD中運用腳本文件可以進行圓形螺旋走線,那么,如果要進行矩形走線,腳本文件應如何編寫?

2016-10-04 19:58:26

如何消除電路中的電感?混沌與混沌同步原理是什么?常用的模擬電感電路有哪幾種?

2021-04-22 06:29:49

東西是真的存在嗎(還是只有我沒懷疑)?說到芯片,就是引腳寄生電感,走線長點,就是引線電感這些東西,說到傳輸線,也說有寄生電感。那么它們到底是怎么來的呢?

2021-01-28 07:00:38

開關電源地如何布局走線

2021-03-11 07:56:58

有一種新概念使您能夠只用兩條引線進行4線電阻測量為什么使用4條線測量電阻?2x4線電阻測量是怎樣的?哪種萬用表適合您?

2021-04-09 06:34:22

有關,但線過長會增大分布電容和分布電感,使信號質量,所以時鐘IC引腳一般都接RC端接,但蛇形走線并非起電感的作用,相反的,電感會使信號中的上升元中的高次諧波相移,造成信號質量惡化,所以要求蛇形線間距最少

2010-10-28 00:05:05

、阻抗匹配 2、濾波電感。對一些重要信號,如INTEL HUB架構中的HUBLink,一共13根,跑233MHz,要求必須嚴格等長,以消除時滯造成的隱患,繞線是唯一的解決辦法。一般來講,蛇形走線的線距

2018-11-23 17:02:19

計算機板中出現,其主要起到一個濾波電感和阻抗匹配的作用,提高電路的抗干擾能力。計算機主機板中的蛇形走線,主要用在一些時鐘信號中,如 PCI - Clk,AGPCIk、IDE、DIMM 等信號線。二

2023-03-22 10:33:44

PCB長距離走線和短距離加個過孔走線哪種走線更合理?

2019-09-25 22:11:32

在電源內縮上來走線可以嗎???

2019-06-13 05:35:05

STM323.3v電源線,地線T字形走線可以嗎?可以這樣處理嗎?

2019-03-01 06:36:02

比如電源走線線寬要加粗(例如20~30mil,第一優先),信號線一般寬度(例如10mli),但有些IC引腳很細,例如8mil左右。這如果選擇8mil線寬走線會警報提示不符合10mil寬度,想問下這個怎么設置?

2019-04-12 04:58:24

>25,以最小化兩個差分對信號之間的串擾; · 使差分對的兩信號走線之間的距離S滿足:S=3H,以便使元件的反射阻抗最小化; · 將兩差分信號線的長度保持相等,以消除信號的相位差; · 避免在差分對

2018-11-27 10:56:15

蛇形走線,因為應用場合不同而具不同的作用:(1)如果蛇形走線在計算機板中出現,其主要起到一個濾波電感和阻抗匹配的作用,提高電路的抗干擾能力。計算機主機板中的蛇形走線,主要用在一些時鐘信號中,如

2019-03-22 06:20:09

高速中的蛇形走線,適合在那種情況?有什么缺點沒,比如對于差分走線,又要求兩組信號是正交的。回答:”蛇形走線,因為應用場合不同而具不同的作用:(1)如果蛇形走線在計算機板中出現,其主要起到一個濾波電感

2019-05-09 07:35:35

家居走線電路:插座,電路圖,照明及開關

2009-06-10 14:55:38 625

625 在不同的應用場合,蛇型走線的意義也不同: 1.濾波電感和阻抗匹配的作用,提

2006-04-16 20:41:46 682

682 、阻抗匹配 2、濾波電感。對一些重要信號,如INTEL HUB架構中的HUBLink,一共13根,跑233MHz,要求必須嚴格等長,以消除時滯造成的隱患,繞線是唯一的解決辦法。一般來講,蛇形走線的線距>

2006-04-16 21:44:36 1158

1158 PCB走線策略

布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得

2006-09-25 14:11:02 7284

7284 蛇形走線的作用

人和同行討論也參考了一些資料,蛇形走線作用大致如下:希望大家補充糾正。

PC

2009-01-18 13:19:33 1806

1806 蛇形走線的優點

RE:蛇形走線有什么作用? 電感作用 視情況而定,比如PCI板上的蛇行線就是為了適應PCI 33MHzClock的

2009-03-25 11:43:50 6672

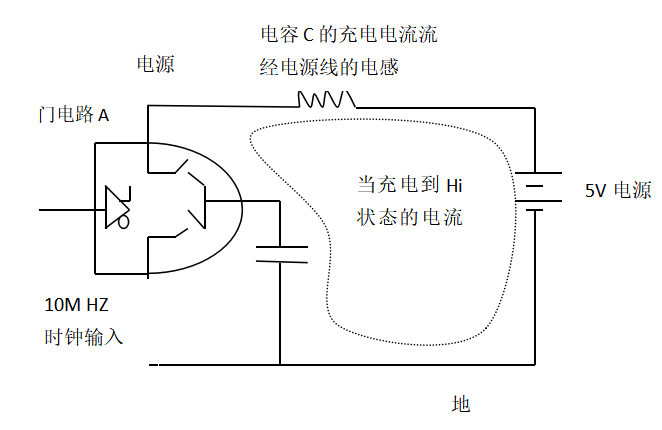

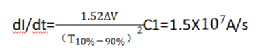

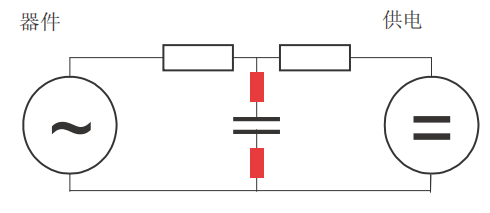

6672 電源線中的電感產生的問題比電阻更嚴重。快速變化的電流通過電源的電感引起電源和所供電的邏輯電路之

2010-06-12 15:26:24 1951

1951

在電路板PCB設計時,有時候需要在不增加PCB走線寬度的情況下提高該走線通過大電流的能力,通常是在PCB走線上鍍錫(或叫上錫),下面以在PCB底層走線鍍錫為例,使用Protel DXP2004軟件

2011-10-31 15:00:27 0

0 文章主要是討論和分析開關電源印制板布線原則、開關電源印制板銅皮走線的一些事項、開關電源印制板大電流走線的處理以及反激電源反射電壓的一個確定因素等方面,解決鋁基板在

2012-05-23 15:46:52 12309

12309

文章主要是討論和分析開關電源印制板布線原則、開關電源印制板銅皮走線的一些事項、開關電源印制板大電流走線的處理以及反激電源反射電壓的一個確定因素等方面,解決鋁基板在開關電源中的應用、多層印制板在開關電源電路中的應用的一些大家關注的問題。

2013-04-25 17:13:35 8868

8868

蛇形走線的主要作用-------另類走線

2016-03-11 15:32:22 0

0 PCB設計與走線PCB設計與走線layout對PCB走線與擺件規則全面了解和 掌握提升走線和擺件技能。

2016-07-21 16:33:13 0

0 開關電源的PCB設計(布局、排版、走線)規范,感興趣的小伙伴們可以看看。

2016-07-26 14:09:33 0

0 開關電源的PCB設計(布局、排版、走線)規范

2016-09-06 16:03:47 0

0 開關電源的PCB設計(布局、排版、走線)規范,感興趣的小伙伴們可以瞧一瞧。

2016-11-11 18:18:32 0

0 bga走線方法

2017-09-18 15:49:24 16

16 很多人對于PCB走線的參考平面感到迷惑,經常有人問:對于內層走線,如果走線一側是VCC,另一側是GND,那么哪個是參考平面?

2018-03-08 17:18:54 10628

10628

本文首先介紹了開關電源PCB板設計步驟,其次闡述了開關電源的PCB板布局走線,最后介紹了開關電源的PCB板布局走線注意事項,具體的跟隨小編一起來了解一下。

2018-05-25 10:59:10 27654

27654

pcb的18種特殊走線的畫法與技巧!

2019-08-20 14:57:24 5383

5383

PCB走線的參考平面在哪?

很多人對于PCB走線的參考平面感到迷惑,經常有人問:對于內層走線,如果走線一側是VCC,另一側是GND,那么哪個是參考平面?

2019-08-20 15:47:13 7703

7703 從原理上說,直角走線會使傳輸線的線寬發生變化,造成阻抗的不連續。其實不光是直角走線,頓角,銳角走線都可能會造成阻抗變化的情況。

2019-09-25 14:32:27 2387

2387 規則一:高速信號走線屏蔽規則 如上圖所示: 在高速的PCB設計中,時鐘等關鍵的高速信號線,走需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會造成EMI的泄漏。 建議屏蔽線,每1000mil,打孔

2020-02-14 11:53:40 13255

13255 本文詳細闡述了pcb電源線走線規則。芯片的電源引腳和地線引腳之間應進行去耦。去耦電容采用0.01uF的片式電容,應貼近芯片安裝,使去耦電容的回路面積盡可能減小。

2020-02-24 16:47:50 28324

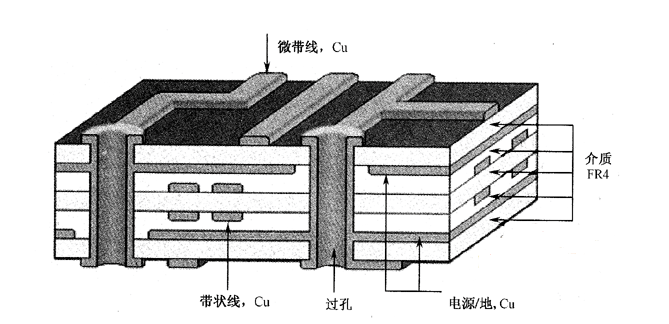

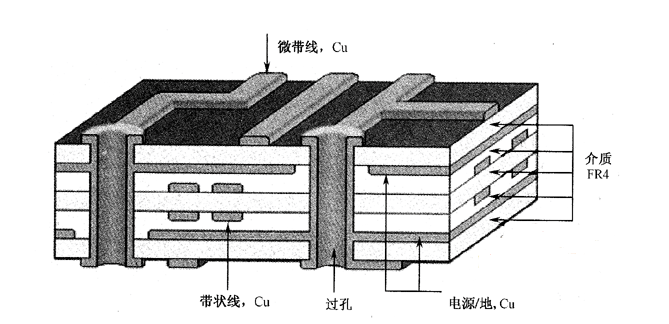

28324 表層走線與內層走線更為規范的說法應該是微帶線與帶狀線。兩種走線方式因為介質和參考面不同,會存在比較明顯的差異。

2020-12-19 10:23:13 7579

7579

UG-042:評估16引線SOIC和16引線QSOP數字隔離器

2021-04-21 10:10:59 7

7 共模扼流圈用于減少特定類型的電噪聲,稱為共模噪聲。共模扼流圈也稱為電流補償扼流圈或電流消除扼流圈。德鍵共模扼流電感 (TCPSEH) 適用在交流/電力電源 (具有大電流流動的電源線),及信號線 (來自信號的失真的問題)。

2021-04-28 09:44:06 1787

1787 LTC1727/LTC1728:8引線MSOP和5引線SOT-23封裝的微功耗精密三電源顯示器產品手冊

2021-05-09 17:34:51 11

11 吉時利源表、萬用表一直備受客戶青睞,在使用過程中經常有人問:四線測試法是什么?今天安泰測試就簡單給大家分享一下到底什么是四線測試法。 四線測試法是目前為止較好的消除引線電阻引入誤差(或將其將至較小

2021-05-19 10:27:27 8721

8721

問題: 泰克吉時利源表萬用表:四線測試法是什么? 答案: 四線測試法是目前為止最好的消除引線電阻引入誤差(或將其將至最小的)的測試方案 · 兩線測量法: 傳統的電阻測量通常用的是兩線測量法來進行測量

2021-10-21 14:38:21 2437

2437 近年來,裝機行業流行一個術語,即“走背線”,那么走背線是什么?裝機之家小編簡單介紹下,通俗的說:走背線就是針對電腦機箱,裝機的時候,將機箱內部和電源的線材做到最干凈整潔,從傳統來說,線材都是從機箱

2022-01-06 15:24:10 2

2 布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過 Layout 得以實現并驗證,由此可見,布線在高速 PCB 設計中

2022-02-11 15:24:33 30

30 在多層PCB設計過程中,一個方法是完整的面作為電源面,另一個設計方法包括電源走線或者結合兩種技術。下面介紹一下兩種技術的優缺點。

2022-08-16 09:08:05 2683

2683

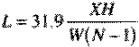

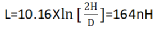

其中W為走線寬度,l為走線長度,可以發現PCB走線電感與敷銅厚度無關,走線電感主要由長度l決定。

2023-01-19 09:11:00 5967

5967

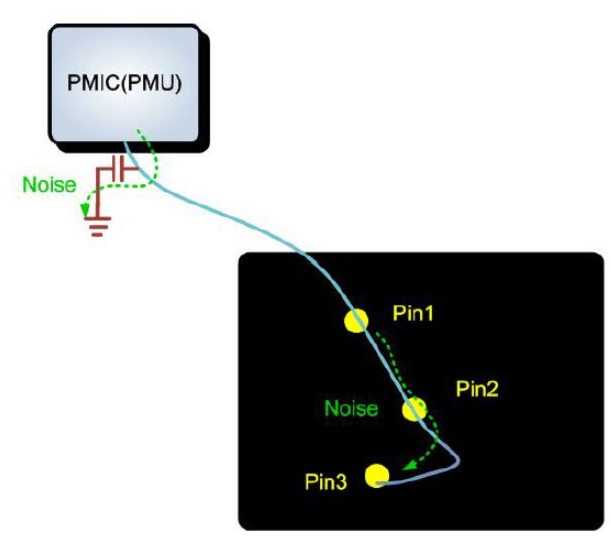

星狀走線的威力是要在 BGA的IC才會顯示出來因為主電源出口會有Bypass電容,所以Noise會順著Bypass電容流到GND,確保流出去的電源都是純凈 無污染。

2023-03-28 15:44:25 3124

3124

蛇形走線是PCB設計中會遇到的一種比較特殊的走線形式(如下圖所示),很多人不理解蛇形走線的意義,下面對蛇形走線的作用進行簡單介紹。

2023-03-30 18:14:23 6216

6216 今天給大家分享的是:PCB走線中需要注意的7個點。 一、PCB 電源布線 數字電路很多時候需要的電流是不連續的,所以對一些高速器件就會產生浪涌電流。 如果電源走線很長,則由于浪涌電流的存在進而會導致

2023-06-19 15:46:15 4366

4366

,影響信號的完整性,直角布線會產生額外的寄生電容和寄生電感。如果頻率較低的話,直角無所謂。但是一般情況,還是要盡可能的避免直角走線,因為每個優秀工程師必備的基本素質就是注

2022-08-15 10:10:14 2399

2399

在多層PCB尤其是高速PCB中,經常將介質之間的若干個金屬層(Plane)分配給電源和地(PoweriGnd)網絡。這樣PCB上的走線就可以大致分為兩類:微帶線和帶狀線。微帶線的附近只有一個金屬平面,通常位于PCB的表層(Top/Bottom Laver)

2023-08-28 14:53:37 3097

3097

如何優化PCB走線來減小回路電感和環路面積? 隨著電路設計的復雜性和頻率的不斷提高,電路中的電感和環路造成的影響也越來越明顯。因此,優化PCB走線以減小回路電感和環路面積已經成為了這個領域中的一項

2023-10-23 09:58:56 6583

6583 什么是環路面積?怎么減小走線的環路電感? 環路面積是指電路中電流在閉合路徑上所圍成的面積。環路電感是在電路中由于閉合電流所引起的磁感應強度變化而產生的電動勢。 為了減小走線的環路電感,我們可以采取

2023-11-09 09:30:15 7204

7204 PCB走線的電感決定了接收的串擾強度。PCB互連設計的一大挑戰是保持系統阻抗,同時減少串擾,因此需要降低走線的電感。設計人員需要使用數值工具和合適的分析公式來計算PCB走線的電感。1電路模型的作用一流的PCB設計和分析工具無需根據電路模型來檢查阻抗、噪聲和其他效應。不過

2023-11-11 08:12:43 3486

3486

電子發燒友網站提供《電源機箱的實際走線效果測試.doc》資料免費下載

2023-11-15 10:32:52 0

0 為什么回路電流走零線不走地線,漏電電流走地線不走零線? 回路電流走零線不走地線,漏電電流走地線不走零線的原因涉及到電路的工作原理、安全性、電流路徑以及人體的安全等多個方面。 首先,回路電流走零線不走

2023-11-23 09:45:54 1996

1996 什么是走線的拓撲架構?怎樣調整走線的拓撲架構來提高信號的完整性? 走線的拓撲架構是指電子設備內部的信號線路布局方式。它對信號傳輸的完整性和穩定性有著重要影響。正確的走線拓撲架構可以降低信號傳輸中

2023-11-24 14:44:40 1441

1441 LED顯示屏的走線方式所說的線指的就是顯示屏的電源線和網線(又稱信號線),大多數情況下電源線和網線是分開的,它們遵循各自的走線規則,電源線連接上電路,網線連接上電腦或者控制盒。

2024-03-07 09:43:43 6575

6575

【EMC技術案例】共模電感與電源模塊之間PCB走線導致RE超標案例

2025-09-28 15:05:04 566

566

【EMC技術案例】芯片下方電源走線導致ESD測試Fail案例

2025-10-20 17:02:22 547

547

雖然我看到過DDR的走線參考電源平面也能調試成功的案例,但是依然不妨礙我還想問:到底DDR走線能不能參考電源層啊?

2025-11-11 17:44:20 630

630

電子發燒友App

電子發燒友App

評論