低阻抗地面的可靠性確定之后,PCB設(shè)計(jì)的下一步是電源布線。

電源面與電源走線

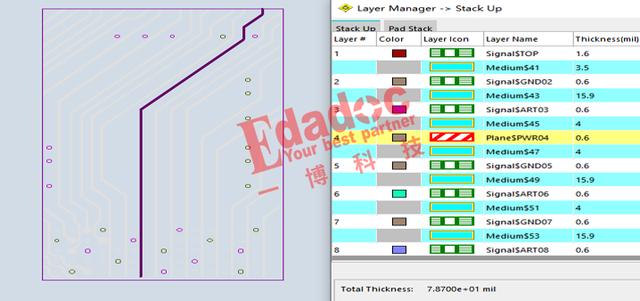

在多層PCB設(shè)計(jì)過程中,一個(gè)方法是完整的面作為電源面,另一個(gè)設(shè)計(jì)方法包括電源走線或者結(jié)合兩種技術(shù)。下面介紹一下兩種技術(shù)的優(yōu)缺點(diǎn)。

電源平面的優(yōu)點(diǎn)

電源平面的缺點(diǎn)

? 實(shí)現(xiàn)容易、時(shí)間短

?低電感電源

? 與地面之間形成一個(gè)大電容

? 每個(gè)供電系統(tǒng)都需要一個(gè)平面

? 如果不同供電面之間沒有用地面隔離,則會(huì)增加它們之間的串?dāng)_

? 一個(gè)低阻抗的躁聲源會(huì)影響整個(gè)供電系統(tǒng)

? 誘導(dǎo)PCB設(shè)計(jì)者很少考慮電源設(shè)計(jì)

布電源線的優(yōu)點(diǎn)

布電源線的缺點(diǎn)

? 在同一層上,可以放置多個(gè)供電系統(tǒng),因此可以減少電源面之間的串?dāng)_

? 可以減少每個(gè)供電系統(tǒng)內(nèi)部的串?dāng)_

? 需要仔細(xì)地考慮電源布線

? 為了保證電源的穩(wěn)定,較高的供電阻抗需要一個(gè)額外的電容

? 在高電流時(shí),具有較大直流阻抗顯然,最優(yōu)方案是把兩者優(yōu)點(diǎn)相結(jié)合,因此應(yīng)該采用本地電源面并且通過跡線連接到供電系統(tǒng)上,不同的供電系統(tǒng)應(yīng)設(shè)在同一層或通過地面分離以減少這些供電系統(tǒng)之間的串?dāng)_,雖然本地電源面易于操作,但當(dāng)連接電源引腳和腿耦電容到平面上時(shí),應(yīng)該特別謹(jǐn)慎。

(a) 退耦電容的連接

微控制器最關(guān)鍵的引腳去耦(請參照第 3 章)往往是在 PCB 設(shè)計(jì)過程中最苛刻的一部分,即使是在一個(gè)多層設(shè)計(jì)中,每毫米跡線都要仔細(xì)考慮。

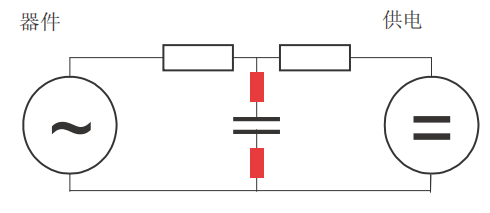

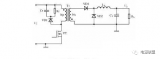

(b) 擬定等效電路

當(dāng)考慮到最佳位置,方向和電容的連接時(shí),紙和鉛筆仍然是有益的工具,畫一個(gè)草圖可能會(huì)非常有用。 每一條線應(yīng)擬阻抗畫出,即使實(shí)際意義并不大。 圖 5-5 清楚地暗示:2 個(gè)紅線標(biāo)識(shí)的阻抗應(yīng)盡量低,而其它 2 個(gè)可以不作重點(diǎn)考慮。

-

電源

+關(guān)注

關(guān)注

185文章

18841瀏覽量

263537 -

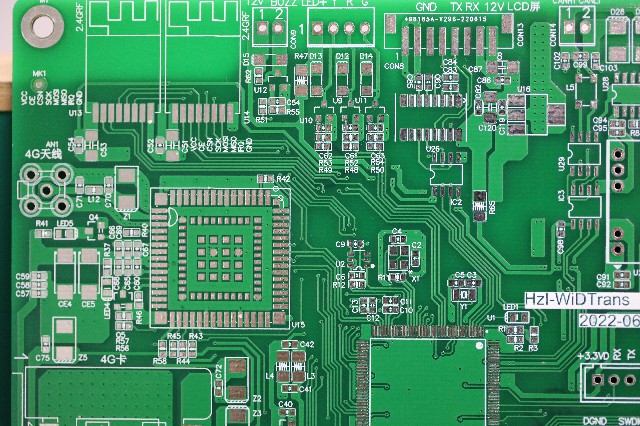

pcb

+關(guān)注

關(guān)注

4404文章

23878瀏覽量

424294 -

布線

+關(guān)注

關(guān)注

9文章

821瀏覽量

86145

發(fā)布評論請先 登錄

雙電源冗余供電的靜態(tài)切換方案有哪些優(yōu)缺點(diǎn)?

Neway微波產(chǎn)品國產(chǎn)化替代電源模塊的優(yōu)缺點(diǎn)

MCU 的 3.3V 電源線走線有沒有問題?比如濾波電容的位置、走線長度這些是不是規(guī)范?

機(jī)房布線,上走線、下走線,哪個(gè)好?

到底DDR走線能不能參考電源層啊?

技術(shù)資訊 I Allegro 設(shè)計(jì)中的走線約束設(shè)計(jì)

言必信_(tái)內(nèi)置式和插座式電源濾波器的區(qū)別

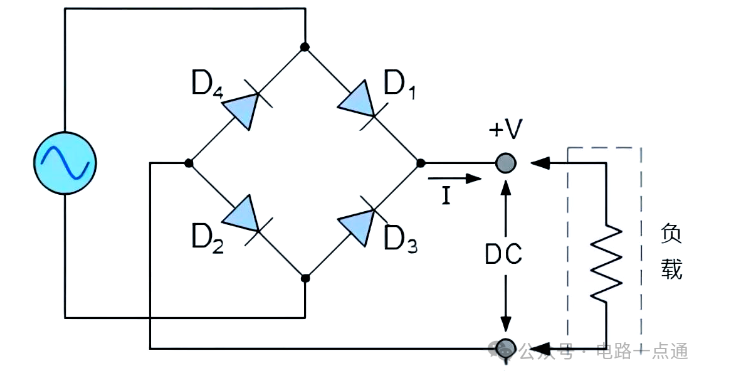

橋式整流電路的原理、優(yōu)缺點(diǎn)及應(yīng)用場景分析

PCBA 表面處理:優(yōu)缺點(diǎn)大揭秘,應(yīng)用場景全解析

機(jī)柜配線架的走線方式

電源面與電源走線技術(shù)的優(yōu)缺點(diǎn)

電源面與電源走線技術(shù)的優(yōu)缺點(diǎn)

評論