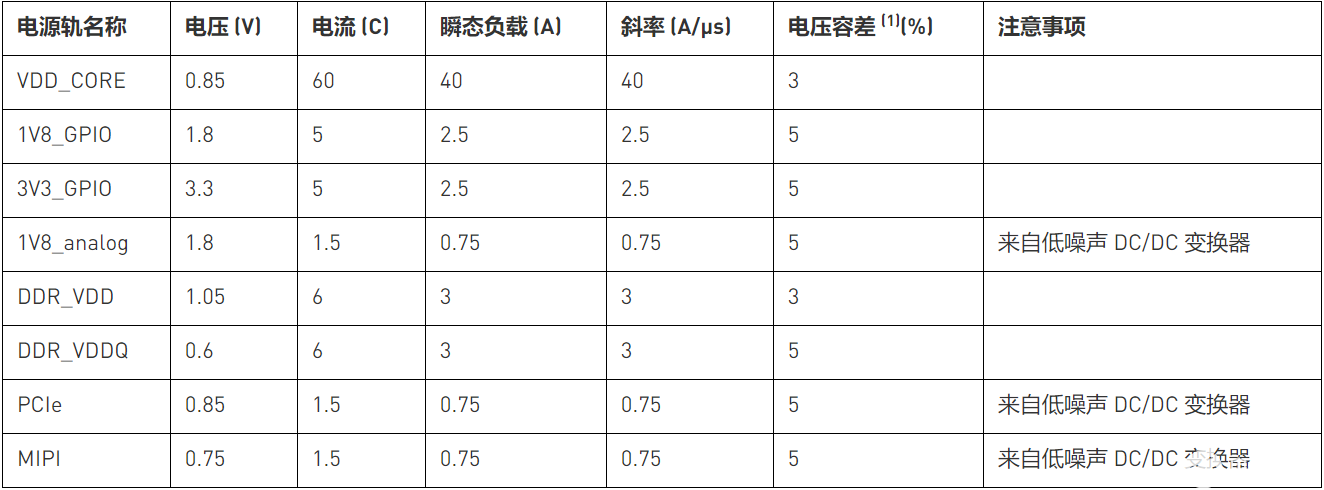

摘 要:本文分析了深亞微米下超大規模SoC的電源設計中存在的問題,給出了業界適用的設計、驗證方法,并以工程設計為例,給出層次性SoC設計中電源設計、驗證的適用流程。

引言

SoC(系統芯片)是現代微電子技術向前發展的必然趨勢。與工藝技術逐步先進的變化相適應,SoC芯片上的內核邏輯的供電電壓也逐步降低。供電電源電壓減小的一個顯著好處是使整個芯片的功耗降低,然而它同時也帶來了芯片噪聲容限降低的負面影響。芯片供電電源網絡上的一個很小的電壓波動或毛刺噪聲,都可能引起芯片邏輯功能的誤動作,或者影響芯片邏輯動作的速度,降低了芯片的性能。因此,電源設計顯得比以前更加重要和困難。隨著半導體工藝向更高節點發展,由于電源設計的問題所導致的整個芯片性能達不到預期要求甚至完全失敗的比例越來越高。據不完全統計:在目前的0.18um和更精細的工藝下,有79%的集成電路設計會遇到電源設計問題,而有高達54%的設計會因此而失敗。可靠的電源設計已經成為SoC設計成功與否的關鍵因素之一而加以考慮。

SoC中的電源設計與分析

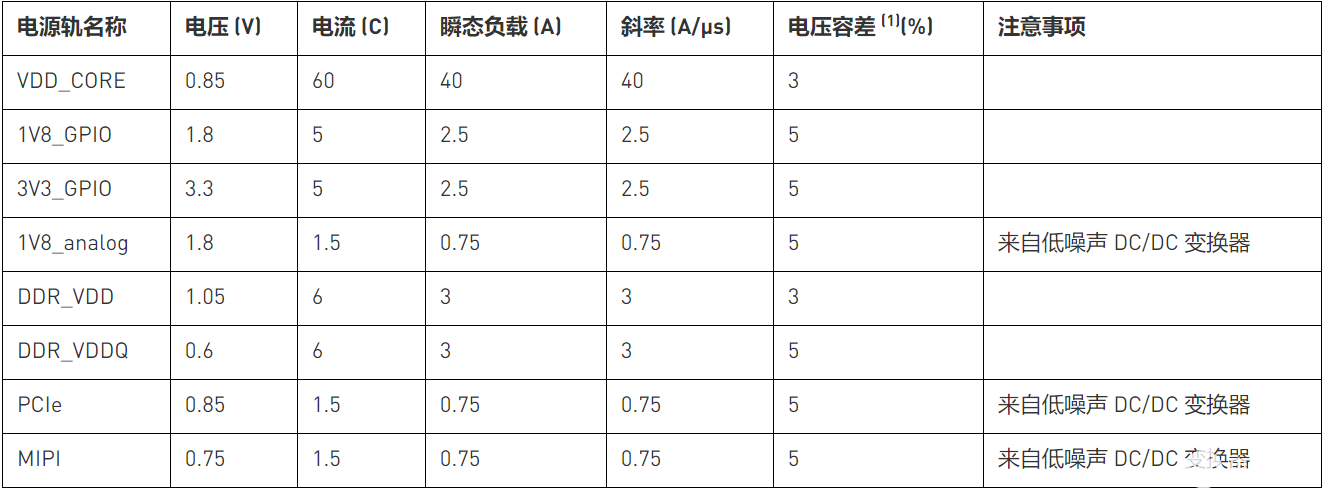

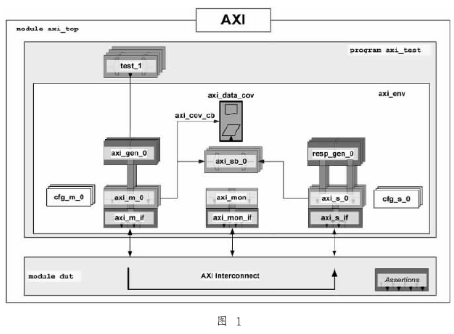

通常,在SoC模塊的布局階段(信號布線之前)完成整個SoC芯片的電源設計,然后根據后續的分析驗證結果加以修正。首先,根據SoC芯片的面積和功耗要求,確定所需的電源凸點(PAD)的數目。然后,在選定的用作電源布線的金屬層上(一般是最上面兩層)每隔一定的間距做一個電源的分支(power-trunk),這樣最終形成一個上下兩層縱橫交錯的網格結構,我們稱之為電源網格power-grid。典型的電源網格設計如圖1所示(以六層金屬工藝為例)。

在0.25mm工藝以前,一般都將芯片上的電源網格(包括電源信號和地信號)當作理想網絡,芯片上任何地方的電源線的電壓都是相等的、穩定的,其大小等于SoC芯片外部所供給的電源電壓,而電流的大小可以為任何值。對于地線,也是同樣的假定。實際上,尤其當集成電路工藝演進到今天的0.18um及以下的超深亞微米時,包括電源網絡在內的所有互連線的阻抗特性表現的就非常明顯了。用集總參數的電路觀點來看,芯片上的互連線就是各種電阻R、電容C和電感L的組合。從而導致了互連線的時序延遲以及導致了電源網絡上的電壓波動,電壓值將不再是穩定不變的單一值了,這就是我們要討論的電源電壓降(IRdrop)和地電壓上升或者反彈(ground-bounce)。(簡單起見,以下的“電源”包括電源信號VDD和地信號VSS;“IRdrop”包括VDD上的電壓降和VSS上的電壓反彈。)

除了電壓波動以外,電源網絡連線上所能承受的電流能力也是電源設計中必須加以考慮的問題。對于作為互連線的金屬層來說,在一定的制造工藝下,在它上面所能允許流過的最大電流是有一定的限度的,否則過大的電流將會導致金屬連線熔斷,導致芯片失效。這種現象我們稱之為電遷移EM(electromigration)。

圖1 典型的SoC電源網格

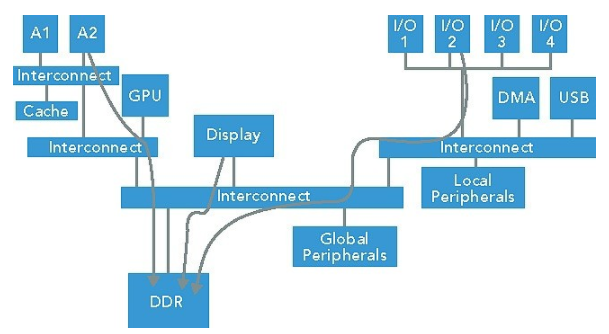

圖2 SoC設計中典型的電源網絡

圖3 電源分析中的等效模型

圖4 基于宏模塊的層次性電源網格驗證流程

電壓降IRdrop

IRdrop是指出現在集成電路中電源和地網絡上電壓下降的一種現象。集成電路通常會假設在芯片內的電源為理想電源,它能在瞬間給芯片上的所有門單元(也包括宏單元)提供足夠大的電流從而使芯片上的電壓保持為統一的值。實際上,由于金屬連線的寬度越來越窄,導致它的電阻值上升,所以在整個芯片范圍內將存在一定的IRdrop。IRdrop的大小將依賴于從電源凸點到所計算的邏輯門單元之間的等效電阻的大小。

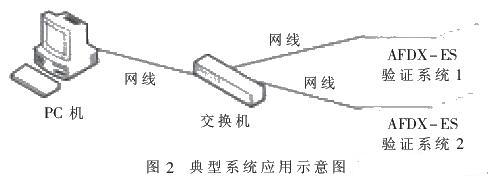

如圖2所示,外部電壓源連接到SoC芯片的電源凸點上,R11到R14是電源網格VDD上的等效電阻值,R21到R24是電源網格VSS上的等效電阻值,G1到G4是連接在電源和地之間的邏輯門單元。理想情況下,當對這些邏輯門單元進行仿真時,V1到V4都被認為等于VDD,地電壓等于VSS。

實際上,電源網格上的真實的電阻值并不是0。例如當有開關動作時,邏輯門單元G4的電壓在任何時候都要比VDD值小。從外部電源流到G4的電流一定流過整個電源分布網絡,導致產生V=IR的電壓降。地信號VSS上的IRdrop是指邏輯門單元G1到G4處地(VSS)電壓的上升。

圖2同時也說明了電源網格和IRdrop的復雜性。假設邏輯門單元G4的電源凸點處的電壓為VDD,G4所消耗的電流為I4安培,而其它邏輯門單元的電流都為0,電流I4通過電源網格從外部電源流向G4。那么邏輯門單元G4處的VDD上的IRdrop就是:

IRdropG4=I4×(R11+R12+R13+R14) (1)

同樣,邏輯門單元G2的 VDD上的IRdrop為:

IRdropG4=I4×(R11+R12) (2)

因此SoC設計中的每一個邏輯門單元的電流都會對設計中的其它邏輯門單元造成不同程度的IRdrop。如果連接到金屬連線上的邏輯門單元同時有翻轉動作,那么因此而導致的IRdrop將會很大。假定圖2中G1到G4的瞬態電流分別為I1到I4,那么在G4處的IRdrop就是I1、I2、I3和I4在相應網格電阻產生的電壓降之和。

IRdrop可能是局部性的,也可能是全局性的。當相鄰位置的一定數量的邏輯門單元同時有邏輯翻轉動作時,就引起局部的IRdrop現象。而當芯片某一區域內的邏輯動作導致其它區域的IRdrop時,稱之為全局現象。一般來說,當電源網絡中的電流大致相等時,從芯片中央到芯片的邊緣,各個潛在的IRdrop會構成一圈圈的圓環,而芯片中心部分的潛在IRdrop最大。流過芯片的電流越大,這些不同IRdrop環的范圍就會越大。

IRdrop的公式說明了設計中的不同的邏輯門單元在不同時間進行邏輯翻轉的重要性。芯片上任何地方的峰值IRdrop要比均值IRdrop可能大得多。但隨著SoC芯片的面積的逐步增大,峰值IRdrop與均值IRdrop的比率正逐步趨于一致,因為在一個很大的SoC中很多門單元同時翻轉的概率在急劇減小。同步翻轉導致IRdrop噪聲的主要因素是時鐘、總線信號、信號引腳的翻轉,它們可能會有很多的門單元同步翻轉從而產生了IRdrop問題。

IRdrop的問題表現在常常類似一些時序甚至可能是信號完整性問題,集中顯現在如下方面:1) 功能故障:在芯片工作時,如果全局IRdrop過高,則邏輯門就出現功能故障。2) 間歇性的或隨數據變化的功能失效:局部IRdrop是比較敏感的,它在一些特定的條件下可能會引起邏輯功能失效。3) 邏輯時序不正常:如果全局IRdrop變化,但還不至于導致系統的邏輯錯誤,則表現為系統的時序問題。

電遷移EM

金屬電遷移是一個通用詞匯,表示導致芯片上金屬互連線斷裂、熔化等的一些失效原因。導致金屬電遷移問題的主要原因是金屬的長期損耗和金屬本身的焦耳熱原理。從某種特定意義上來說,電遷移是芯片金屬互連線長期損耗的結果。焦耳發熱是一種同電遷移相關聯的特定問題。焦耳發熱是指由于很高的交流電流而導致金屬連線某一特定段發熱過大。為了減小電遷移的影響,某一特定層的金屬連線常常用多層不同材料的金屬線以一種三明治的結構加以構造。一般額外的連線層,通常是三明治結構中的最上層和最下層,有更強的抗電遷移能力,能夠幫助整個金屬連線不至于全部斷掉。由于電遷移是一個長期損耗的累積結果,那么一段金屬連線的電遷移的危險程度常常用流過這段連線的一定時間內的平均電流來加以測量。

電遷移常常表現出經過一段時間后芯片有時序或功能性的錯誤。如果芯片中的某一根連線是唯一的,那么當發生電遷移問題以后,會導致整個芯片的功能失效。如果一些連線本來就有冗余設計的考慮,例如電源網絡,當發生電遷移問題后,其中的一部分連線會斷開,而其它部分的連線就會承受較大的IRdrop問題。如果因為電遷移而導致了線路間的短路,那就是整個芯片的失效。

電源驗證工具和流程

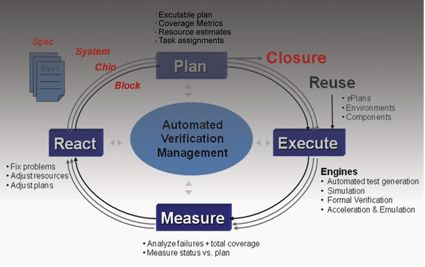

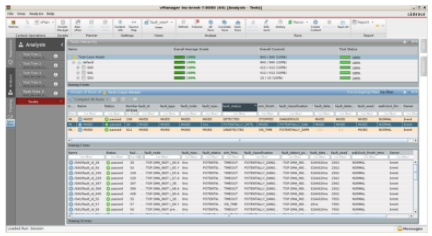

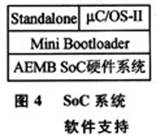

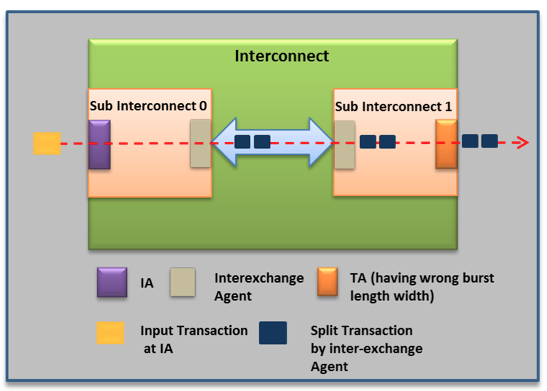

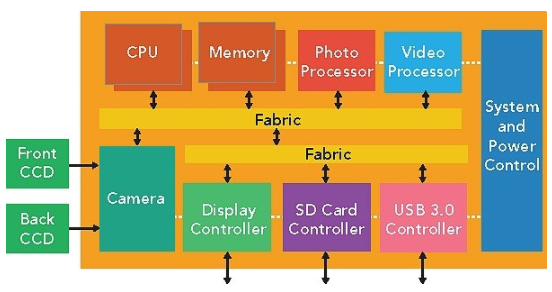

Simplex公司提供了一整套電源分析、驗證的工具VoltageStorm,能夠幫助設計工程師可靠地完成整個電源設計。例如,提取電源網格上的寄生參數,并將設計中的每一個MOSFET等效為一個電流源,如圖4所示。計算出每個MOSFET的分流電流(tap-current),然后用VoltageStorm對電源網格做IRdrop和EM方面的分析驗證,并產生最后分析的結果以備工程師檢查所設計的電源網格是否符合預期要求。

VoltageStorm同時支持層次性的設計,對某一模塊分析后的結果可以產生VoltageStorm的格式庫,直接作為下一級設計的輸入,這樣可以節省下一級設計的分析時間。一般流程如圖4所示。VoltageStorm支持命令格式文件流程,設定好相關參數,例如分析需要的庫文件,設計中每個元件的功率文件,所需要分析的電源網絡名字及其電壓大小等等,就可以運用VoltageStorm完成整個分析驗證。

結語

當IC工藝越來越精細,SoC的規模越來越大時,對電源設計的要求就越高。SoC設計必須考慮到可能出現的IRdrop和EM的問題,在具體工藝參數的要求下,精心設計,并運用適當的電子設計自動化(EDA)工具進行全面的分析驗證,以確保最后生產的硅芯片能夠按設計的預期要求那樣可靠、穩定、正確地工作。

- SoC中(4996)

相關推薦

Incisive 12.2版本融入Cadence驗證IP,SoC驗證效率提高50%

1437

1437

設計和驗證技術如何確保汽車SoC的功能安全

3256

3256

汽車SoC電源架構設計

641

641

SoC芯片設計驗證詳解

832

832

2015高品質開關電源設計驗證技術分享!

SOC設計與驗證流程是什么?

SoC驗證平臺的FPGA綜合怎么實現?

SoC驗證未來將朝什么方向發展?

SoC系統級芯片

SoC設計中的功耗管理問題

SoC設計中遇到的難題急需解決

SoC設計與驗證整合

Altera Cyclone V SoC 電源

Arm CoreSight SoC-600技術參考手冊

Job: SOC實現技術專家(Leader)1名 + IC Layout leader 1名

LED驅動電源中的電容降壓原理分析

Veloce平臺在大規模SOC仿真驗證中的應用

【華為海思成都】招聘數字IC設計/驗證工程師

一個優秀的SOC驗證環境應該具備哪些功能呢

什么是SoC驗證平臺自動化電路仿真偵錯功能?

以FPGA為基礎的SoC驗證平臺 自動化電路仿真偵錯功能

利用RC1000和SoC設計展示評估平臺RC200搭建一個原型驗證系統的樣機?

基于ARM IP的SoC中電源管理討論

基于VHDL語言的IP核驗證

如何縮短SoC的仿真時間?

如何設計和驗證SoC

怎樣用C語言去啟動SOC驗證環境呢

晶片驗證測試及失效分析pdf

求一種基于ADSP-BF537的SOC驗證方案

給Altera Arria 10 FPGA和Arria 10 SoC供電:經過測試和驗證的電源管理解決方案

集成柔性功率器件在FPGA或SoC電源中的應用

一種數模混合SoC 設計協同仿真的驗證方法

19

19一種數模混合SoC 設計協同仿真的驗證方法

5

5各種驗證技術在SoC設計中的應用

27

27SoC芯片驗證技術的研究

24

24結合覆蓋率驅動技術的RVM驗證方法學在SOC驗證中的應用

15

15在SoC設計中采用ESL設計和驗證方法

33

33SoC驗證環境搭建方法的研究

22

22基于SOC的USB主設備的軟硬件協同驗證

15

15一種基于事務的SoC功能驗證方法

8

8基于ARM9的AFDX-ES SoC驗證平臺的構建與實現

56

56設計與驗證復雜SoC中可綜合的模擬及射頻模型

557

557AEMB軟核處理器設計的SoC系統驗證平臺

801

801

用于SoC驗證的(UVM)開源參考流程使EDA360的SoC

2240

2240AFDX-ES SoC驗證平臺的構建與實現

1027

1027

SoC系統知識與設計測試

SoC多語言協同驗證平臺技術研究

12

12基于FPGA的驗證平臺及有效的SoC驗證過程和方法

13137

13137

利用FPGA軟硬件協同系統驗證SoC系統的過程和方法

3769

3769

基于可重用激勵發生機制的虛擬SoC驗證平臺

0

0SoC設計的可擴展驗證解決方案

743

743

基于片上系統的SOC設計驗證方案

1367

1367PADS分析工具可以進行仿真和驗證的原因分析

10642

10642

SoC設計中的互連驗證中遇到的問題

2299

2299

基于VMM構建的驗證平臺在AXI總線協議SoC中的應用研究

1151

1151

智能跟蹤SoC驗證進度的方法

3291

3291

SOC電源管理系統

14

14可支持18億門SoC全芯片驗證的英諾達硬件驗證云平臺

1771

1771適用于復雜SoC的軟件定義驗證和驗證環境

1033

1033設計和驗證技術如何確保汽車SoC的功能安全

1177

1177

SoC互連的功能和性能驗證

1692

1692

通過場景模型驗證管理SoC復雜性

682

682

驗證SoC功能、時序和功耗的最快解決方案

769

769汽車SoC電源架構設計

1810

1810

搞定緩存一致性驗證,多核SoC設計就成功了一半

589

589為什么SoC驗證一定需要FPGA原型驗證呢??

854

854為什么SoC驗證一定需要FPGA原型驗證呢?

905

905

一文淺談SoC功能驗證中的軟件仿真

492

492

移動SoC的時鐘驗證

433

433

fpga驗證及其在soc驗證中的作用有哪些

597

597 電子發燒友App

電子發燒友App

評論