芯片設計驗證是一個長期存在的障礙,通常會阻礙產品按時交付。一個統一的支持軟件的驗證和確認環境可能是打破硬件設計團隊和軟件開發人員之間依賴關系的方式。

有了統一的環境,驗證可以在早期通過模型進行,隨著開發過程中出現不同的部分來構建系統。驗證將從一開始就開始,最后的硅前測試只關注最后一分鐘的改進和完整的系統驗證、快速流片、降低重新設計風險并簡化硅后驗證。

罪魁禍首正在增加芯片中硬件和軟件的復雜組合,這是持續“數字化”的結果。系統的這兩個基本方面的開發通常按不同的時間表進行。例如,硬件設計可以比軟件早兩年開始。

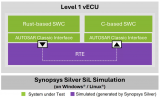

復雜性迫使硬件驗證和驗證包括證明預期軟件在硬件上正常工作的證據,當軟件遠遠落后時,這是一項艱巨的任務。支持軟件的驗證和驗證方法允許通過早期工作負載分析進行早期硬件驗證,從而打破硬件對系統軟件的依賴。

以前,通用硬件塊被組裝成一個可以執行軟件的系統。在那個過時的范例中,硬件設計在沒有考慮應用軟件的情況下進行,因為硬件被設計為通用的,托管任意數量的可能類型的軟件并且沒有針對它們進行優化。

設計人員現在采用片上系統 (SoC) 方法實現硬件系統。過去,該硬件系統可能已由系統集成商組裝成一個獨立的硅芯片,以處理大部分計算工作。現在,對整個系統 SoC 的驗證必須關注底層硬件和它將執行的軟件之間的連接。

像這樣的 SoC 將為特定應用程序處理特定的數據工作負載。與早期的通用處理器不同,處理架構必須非常適合它將處理的數據的性質。指令集、總線架構和內存/高速緩存結構可以進行定制,以最大限度地提高性能、降低功耗和提高效率。

這需要硬件工程師在設計周期的早期訪問軟件工作負載。甚至架構本身也需要針對要執行的工作進行驗證。這種對軟件的依賴對項目進度有重大影響,當企業試圖“左移”以更快地將產品推向市場時尤其困難。

那不是全部。其他功能和日程安排注意事項:

業務經理希望他們的產品不會受到電池壽命差等問題的影響,并且仍然會進入市場窗口

工程管理希望加快進度并在預算范圍內完成項目,盡可能利用通用方法

設計團隊面臨在 12 到 18 個月內完成日益復雜的設計的壓力

驗證組,尤其是那些使用硬件仿真的驗證組,希望將系統的不同方面分配給不同的組,以便更快地進行并行子系統驗證

擁有如此多的利益相關者和優先事項正在推動迫切需要一種更好的方法來完成 SoC 驗證。軟件定義的驗證和驗證環境和方法將使工程團隊能夠交付復雜的 SoC,滿足上市時間,提供更徹底的檢查,并降低風險和成本。

審核編輯:郭婷

-

芯片

+關注

關注

463文章

54010瀏覽量

466020 -

soc

+關注

關注

40文章

4576瀏覽量

229137 -

電池

+關注

關注

85文章

11525瀏覽量

143399

發布評論請先 登錄

RDMA設計36:驗證環境設計

RDMA設計35:基于 SV 的驗證平臺

電能質量在線監測裝置精度等級劃分標準適用于哪些場景?

如何驗證電能質量在線監測裝置支持的通信協議是否適用于特定設備?

在Linux ubuntu上使用riscv-formal工具驗證蜂鳥E203 SoC的正確性

開芯院采用芯華章P2E硬件驗證平臺加速RISC-V驗證

新思科技如何驗證更安全的智能汽車軟件

Veloce Primo補全完整的SoC驗證環境

適用于復雜SoC的軟件定義驗證和驗證環境

適用于復雜SoC的軟件定義驗證和驗證環境

評論