PL通過NoC讀寫DDR4實驗

實驗VIvado工程為“pl_rw_ddr”

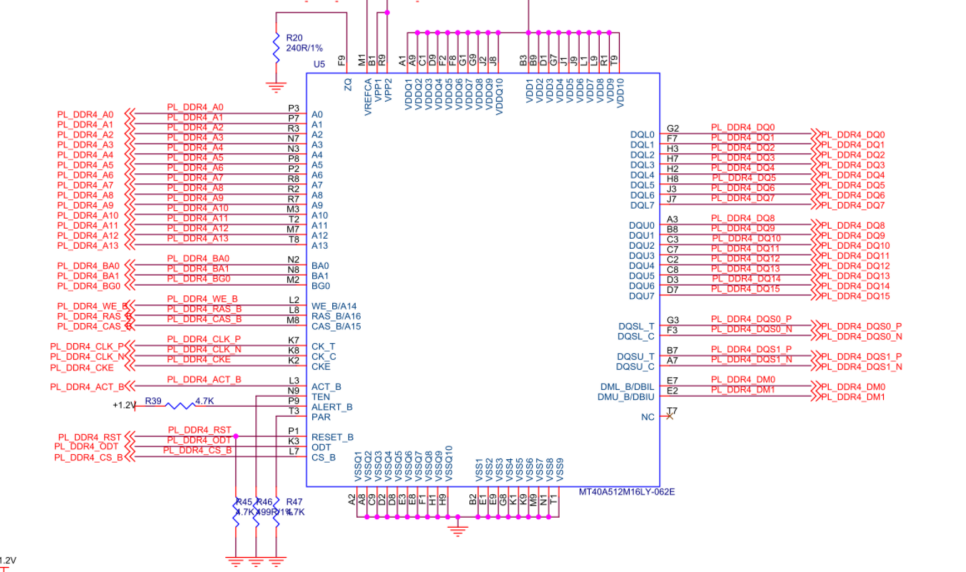

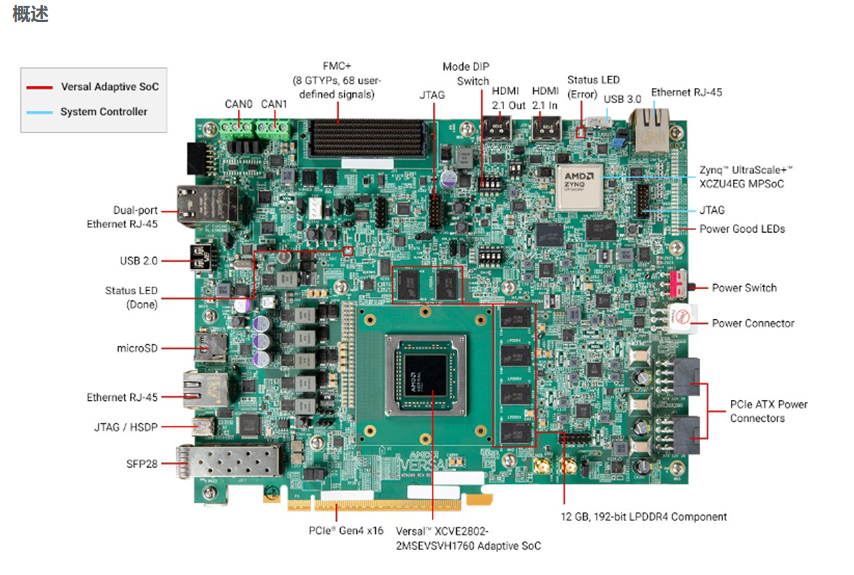

1.1硬件介紹

開發板的PL端有4顆16bit ddr4

1.2Vivado工程建立

Versal的DDR4是通過NoC訪問,因此需要添加NoC IP進行配置。

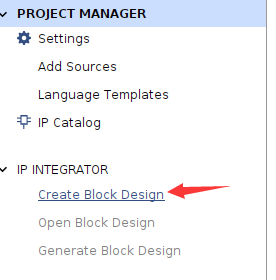

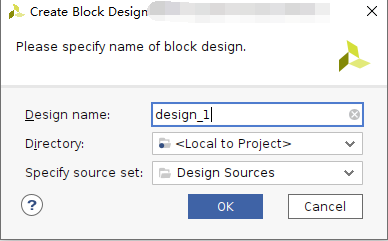

1.2.1創建一個Block design并配置NoC

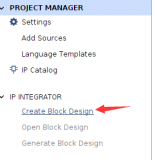

1)選擇Create Block Design

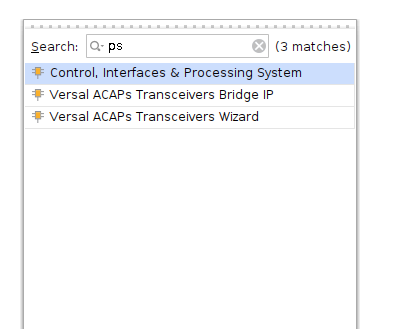

2)添加CIPS

? ?

? ?

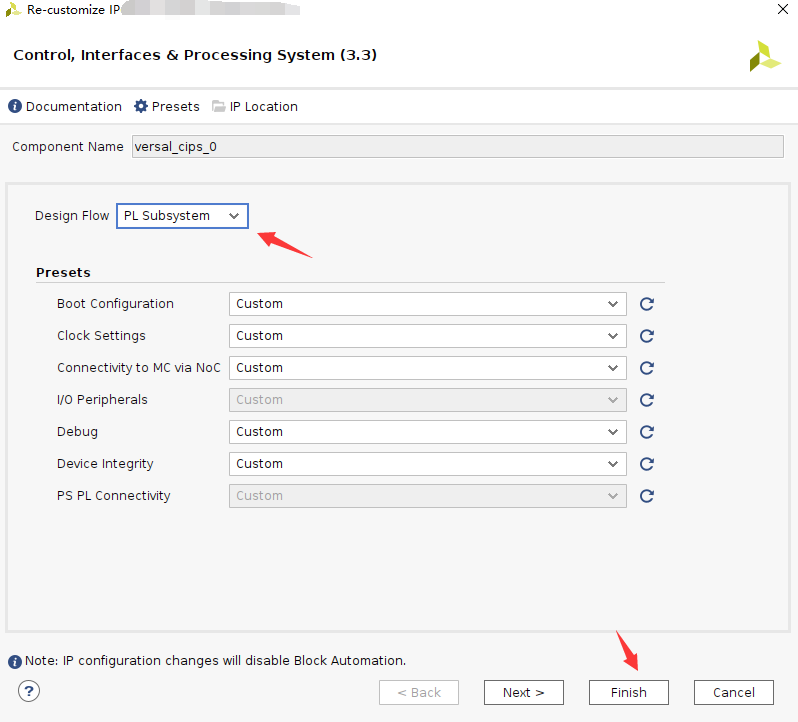

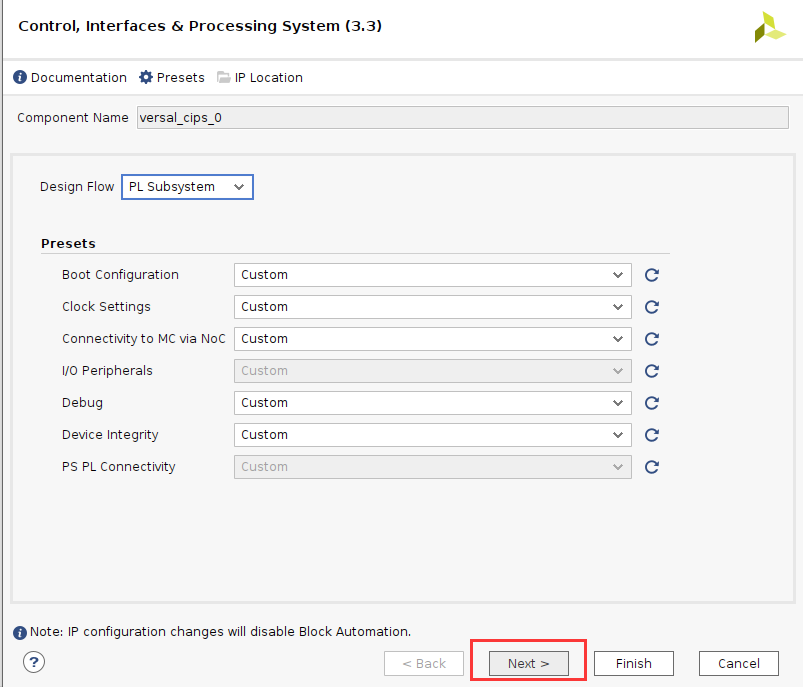

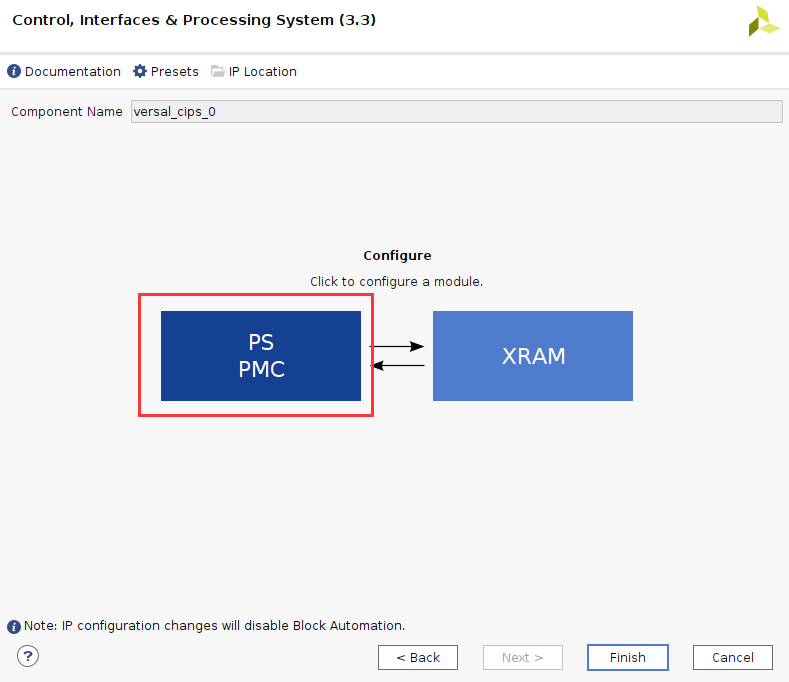

3)雙擊CIPS,選擇PL_Subsystem,只有PL端的邏輯

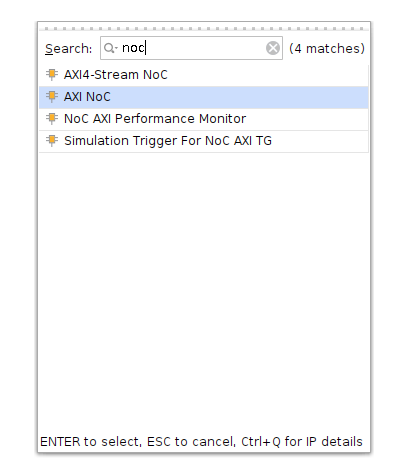

4)添加NoC IP

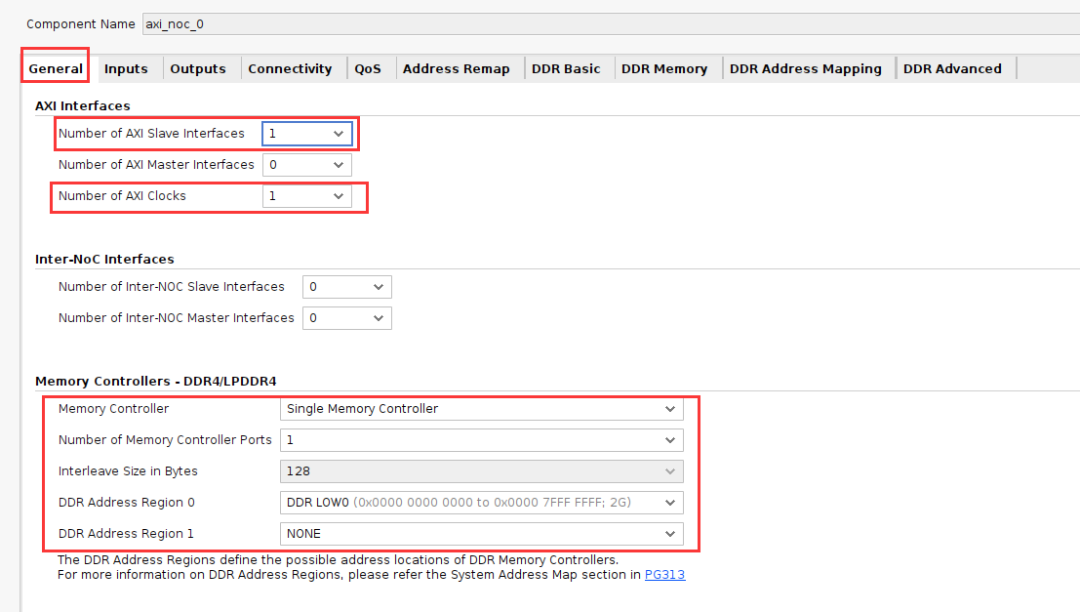

5)配置NoC

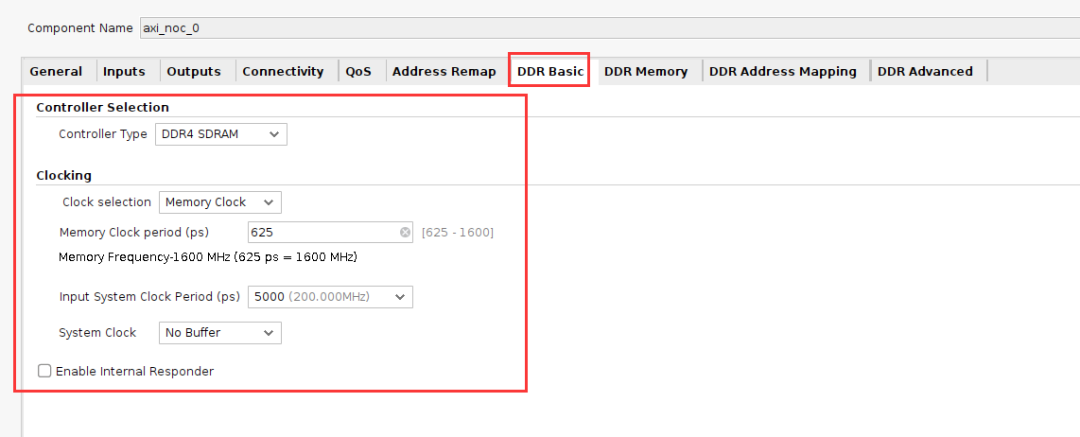

選擇一個AXI Slave和AXI Clock,選擇”Single Memory Controller”

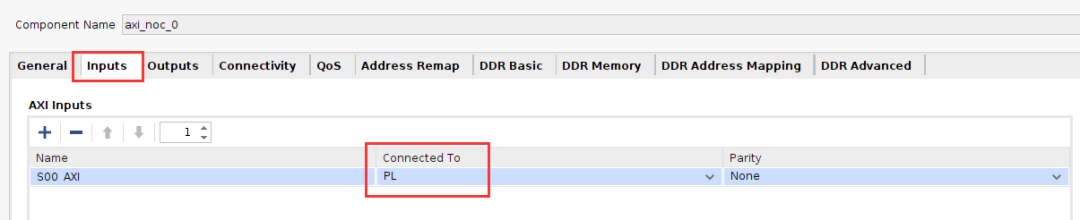

選擇Inputs為PL

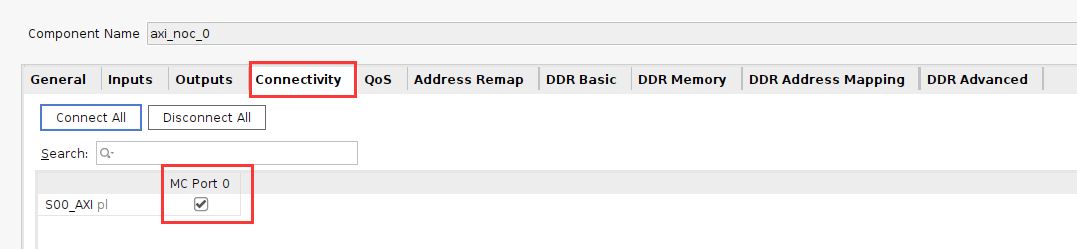

連接port

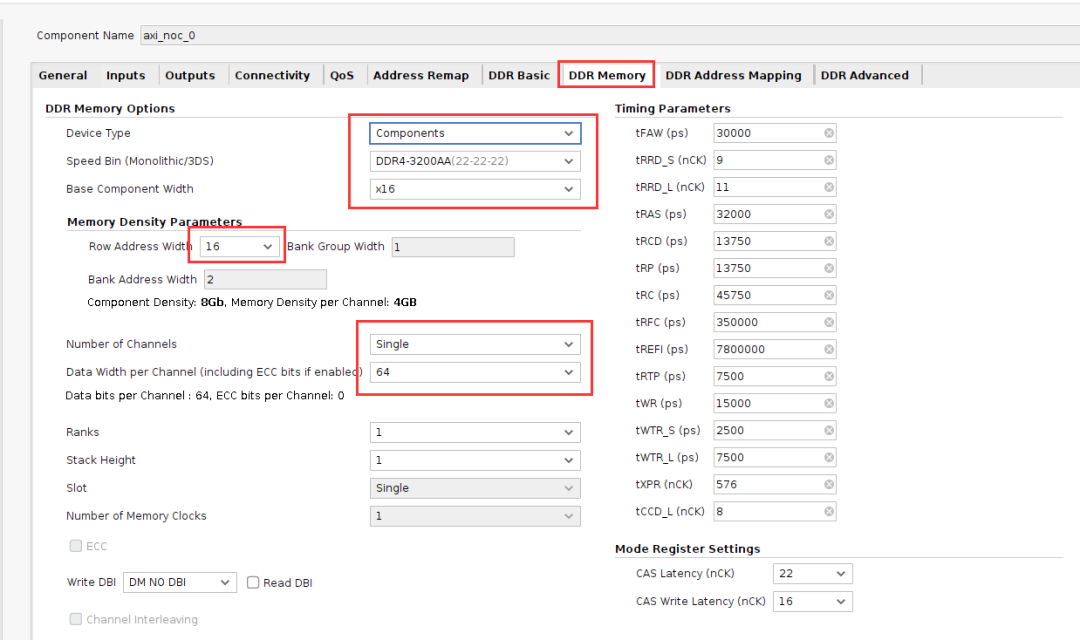

DDR4配置

配置完成,點擊OK

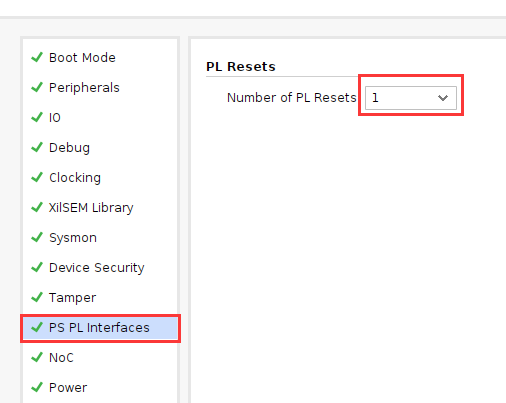

6)配置CIPS,添加復位

? ?

? ?

點擊Finish

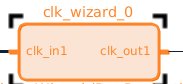

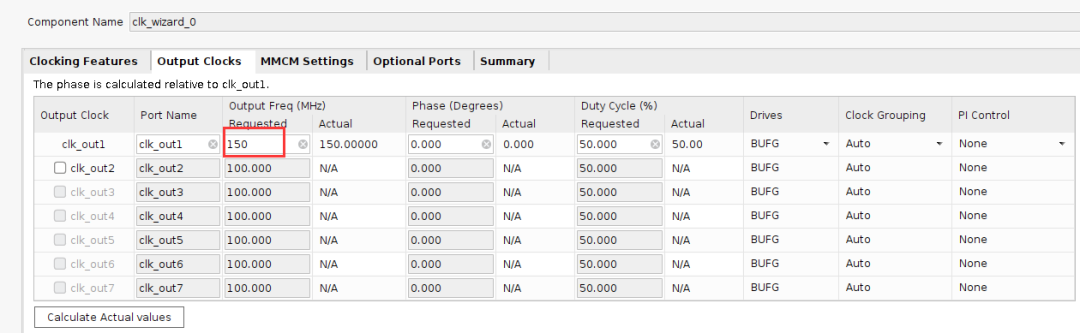

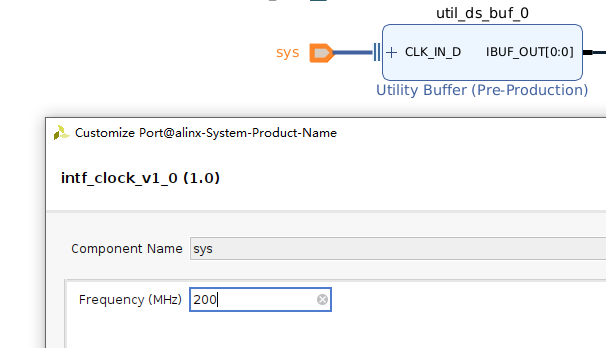

7)添加Clocking Wizard,配置輸出時鐘150MHz,作為PL端讀寫時鐘

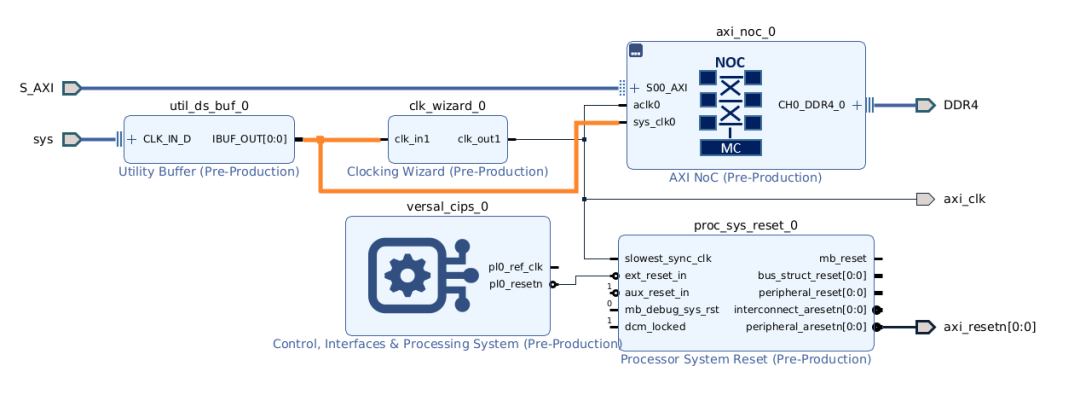

8)添加IBUFDS為NoC和Clocking Wizard提供參考時鐘,并導出S00_AXI,CH0_DDR4_0等總線,添加axi_clk,axi_resetn為PL端提供時鐘和復位。

雙擊參考時鐘引腳,并配置頻率為200MHz

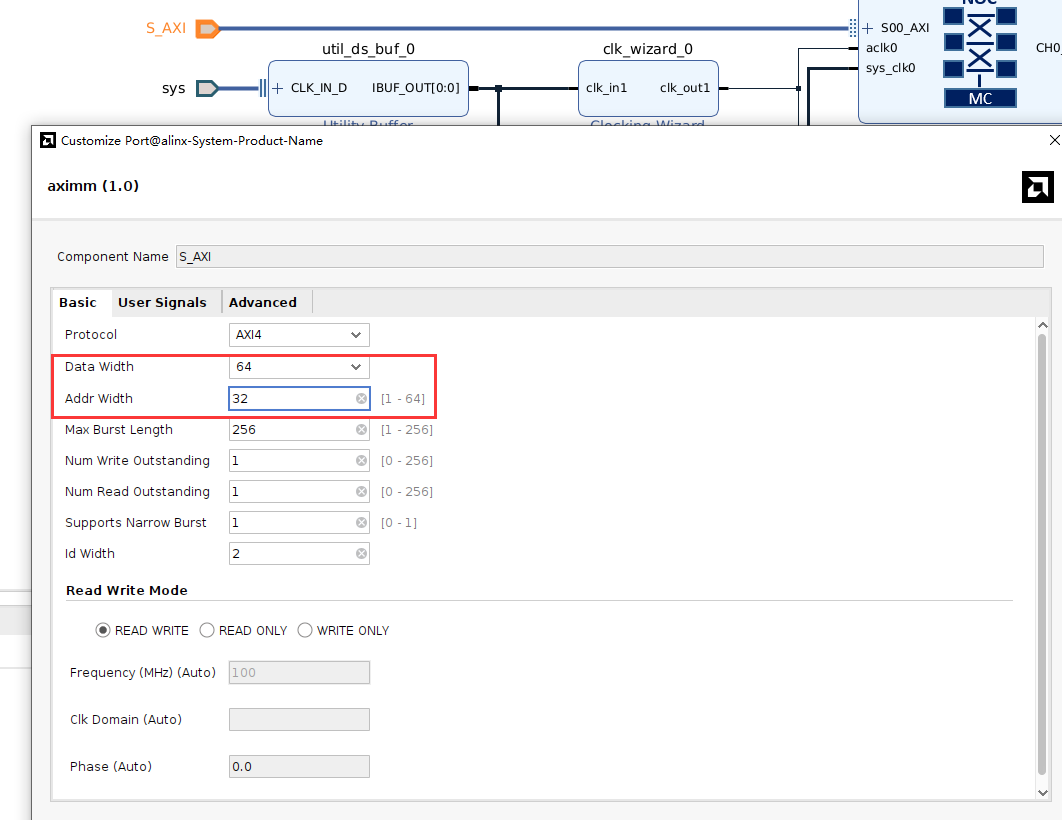

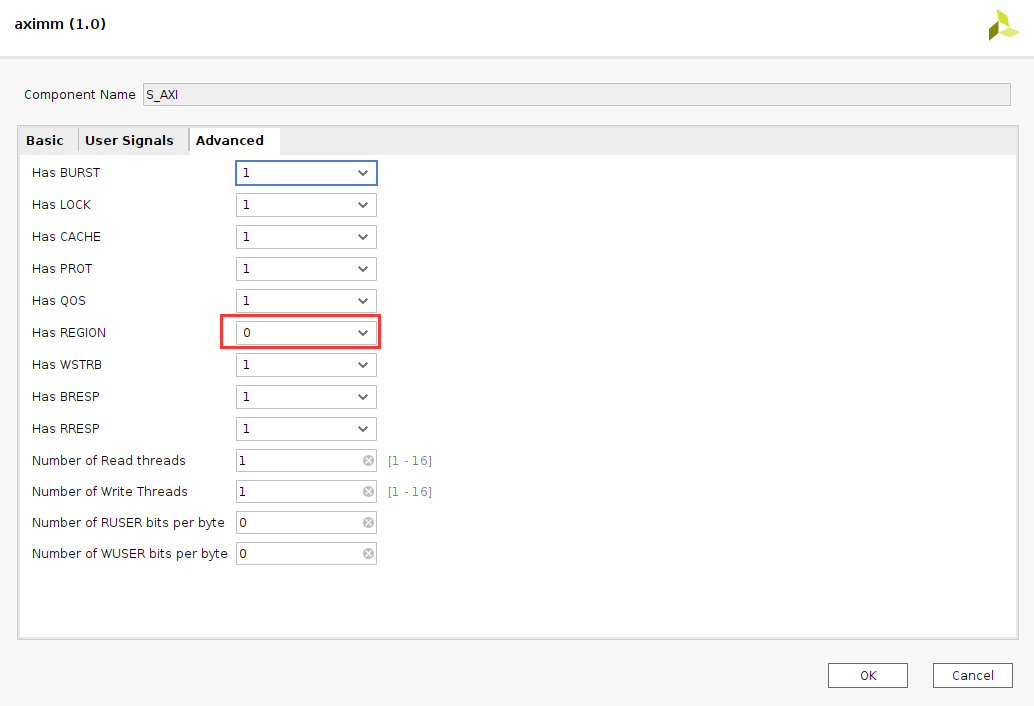

雙擊AXI總線,并配置

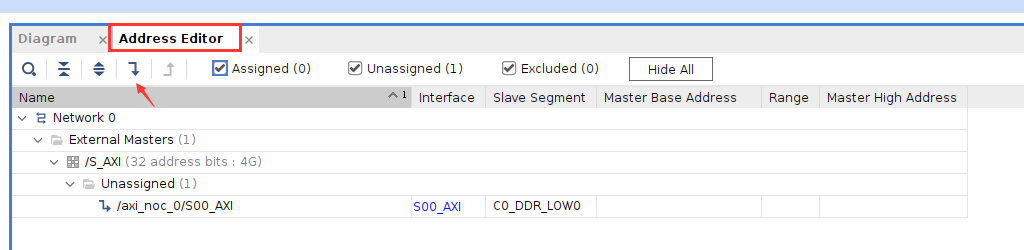

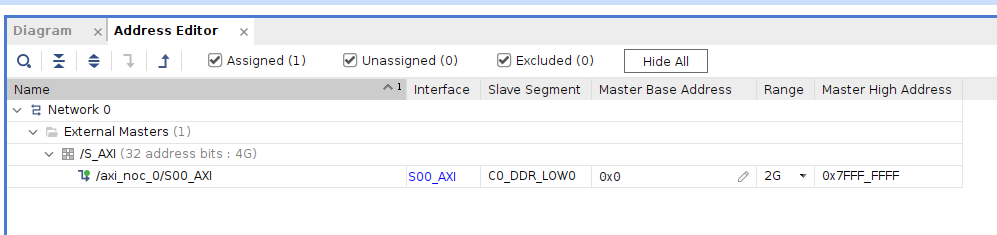

9)分配地址

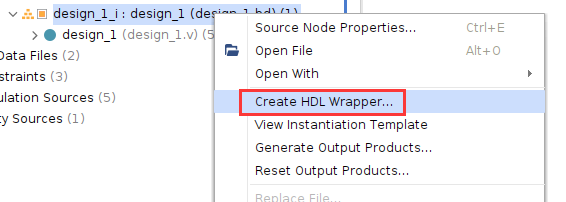

10)Create HDL

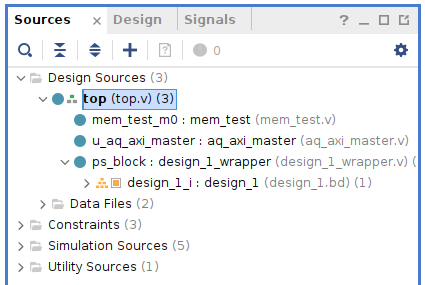

1.2.2添加其他測試代碼

其他代碼主要功能是讀寫ddr4并比較數據是否一致,這里不做詳細介紹,可參考工程代碼。

? ??

? ??

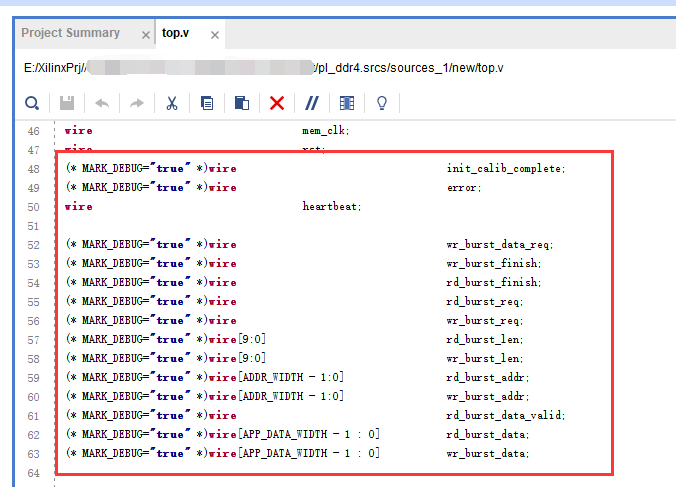

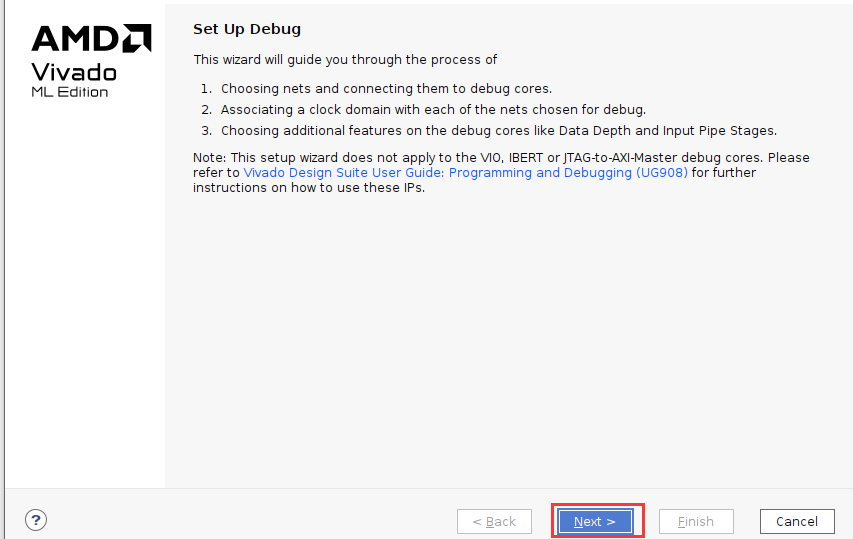

1)在mem_test.v中添加mark_debug調試

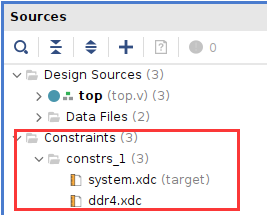

2)引腳綁定

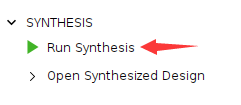

3)綜合

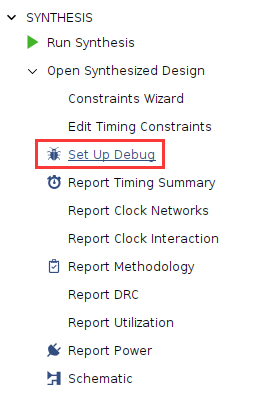

4)綜合完成后點擊Set up debug

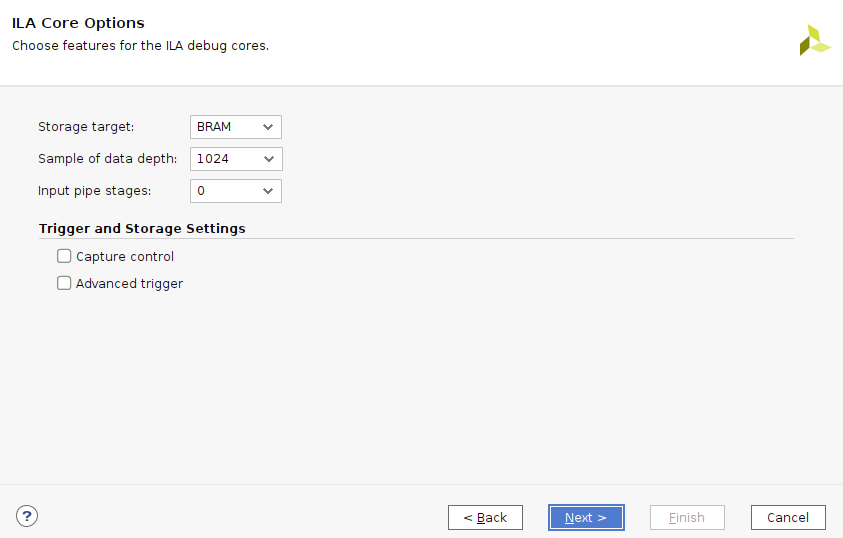

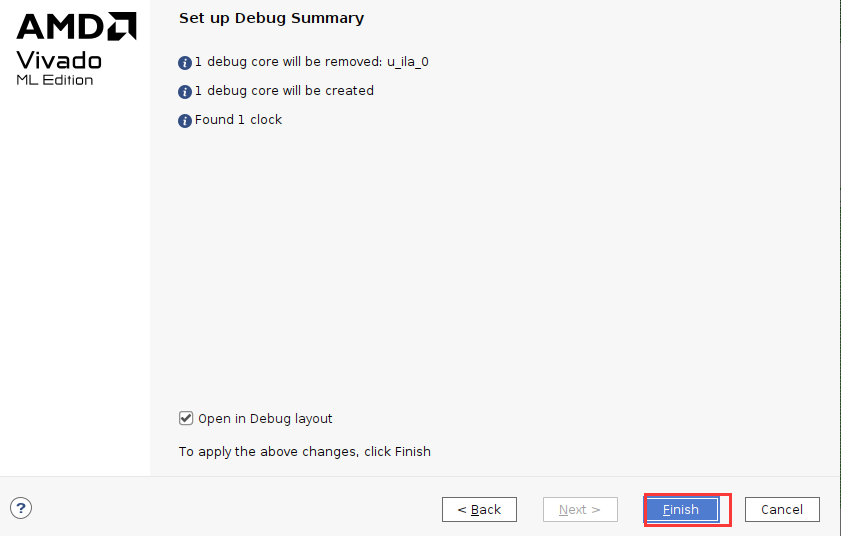

根據需求設置采樣點數

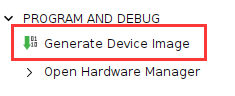

之后保存,并生成pdi文件

1.3下載調試

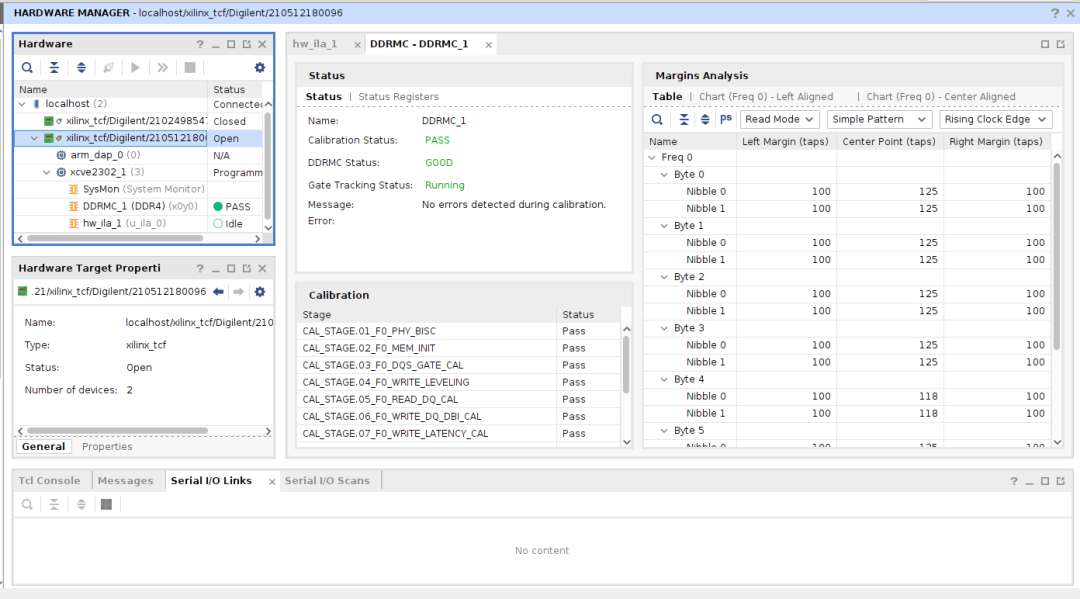

生成pdi文件以后,使用JTAG下載到開發板,在MIG_1窗口會顯示DDR4校準等信息

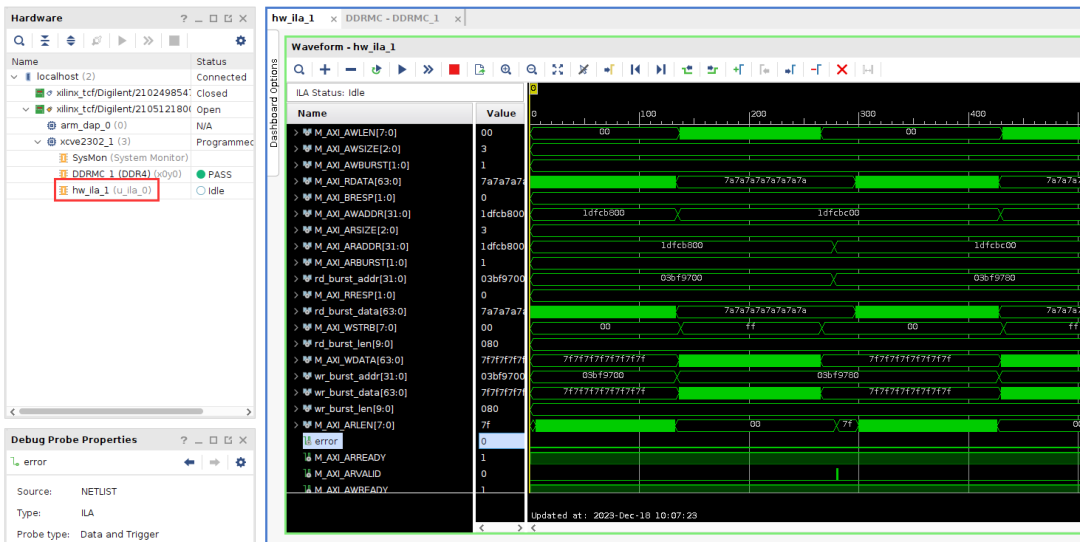

在hw_ila_1中可以查看調試信號

1.4實驗總結

本實驗通過PL端Verilog代碼直接讀寫ddr4,主要了解NoC的配置方法,如何通過NoC訪問DDR4,后續的實驗中都要用到此配置。

審核編輯:劉清

-

JTAG

+關注

關注

6文章

411瀏覽量

74649 -

DDR4

+關注

關注

12文章

343瀏覽量

42706 -

AXI總線

+關注

關注

0文章

68瀏覽量

14722 -

NoC

+關注

關注

0文章

43瀏覽量

12105 -

CLK

+關注

關注

0文章

132瀏覽量

17945

原文標題:【ALINX 技術分享】AMD Versal AI Edge 自適應計算加速平臺之PL通過NoC讀寫DDR4 實驗 (4)

文章出處:【微信號:ALINX,微信公眾號:ALINX】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

AMD Versal AI Edge自適應計算加速平臺之Versal介紹(2)

AMD Versal AI Edge自適應計算加速平臺PL LED實驗(3)

AMD Versal AI Edge自適應計算加速平臺之PL LED實驗(3)

AMD Versal AI Edge自適應計算加速平臺之體驗ARM,裸機輸出(7)

Xilinx推出Versal:業界首款自適應計算加速平臺,支持快速創新

賽靈思發布自適應計算加速平臺芯片系列Versal

賽靈思Versal自適應計算加速平臺指南

AMD發布第二代Versal自適應SoC,AI嵌入式領域再提速

ALINX受邀參加AMD自適應計算峰會

AMD Versal自適應SoC DDRMC如何使用Micron仿真模型進行仿真

面向AI與機器學習應用的開發平臺 AMD/Xilinx Versal? AI Edge VEK280

AMD Versal AI Edge自適應計算加速平臺之PL通過NoC讀寫DDR4實驗(4)

AMD Versal AI Edge自適應計算加速平臺之PL通過NoC讀寫DDR4實驗(4)

評論