在高速的PCB設(shè)計中,時鐘等關(guān)鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。##在高速的PCB設(shè)計中,時鐘等關(guān)鍵

2016-04-26 14:00:01 5836

5836

本文主要詳解PCB設(shè)計高速模擬輸入信號走線,首先介紹了PCB設(shè)計高速模擬輸入信號走線方法,其次闡述了九大關(guān)于PCB設(shè)計高速模擬輸入信號走線規(guī)則,具體的跟隨小編一起來了解一下。

2018-05-25 09:06:44 10092

10092

高速產(chǎn)品的輕薄化,PCB厚度限制了走線層數(shù),就有了高速線走在相鄰兩層上,為了減少相互的串?dāng)_,走線的方法有間距管控(DDR部分實現(xiàn)難度比較大),垂直走線(這種方法實現(xiàn)難度比較大),30度角走線。

2022-07-13 15:53:27 4071

4071

在某單板開發(fā)工作中,高速信號線非常多,為了保證單板的EMI性能,在PCB布線中,盡可能保證信號線走內(nèi)部信號層,防止因為過多表層高速信號線產(chǎn)生的EMC問題無法定位。但是該方案帶來的直接問題是高速信號線

2022-10-20 10:41:47 5678

5678

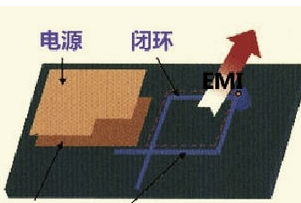

規(guī)則一:高速信號走線屏蔽規(guī)則在高速的PCB設(shè)計中,時鐘等關(guān)鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。圖1 高速

2018-11-28 11:14:18

高速PCB設(shè)計中,蛇形線沒有所謂濾波或抗干擾的能力,只可能降低信號質(zhì)量,所以只作時序匹配之用而無其它目的。7. 有時可以考慮螺旋走線的方式進行繞線,仿真表明,其效果要優(yōu)于正常的蛇形走線。

2017-07-07 11:45:56

布線(Layout)是PCB設(shè)計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統(tǒng)的性能,大多數(shù)高速的設(shè)計理論也要最終經(jīng)過Layout得以實現(xiàn)并驗證,由此可見,布線在高速PCB設(shè)計中

2019-08-05 06:40:24

控制標(biāo)準(zhǔn)是100Ω;誤差不能大于±10%; 走線避免直角,以免產(chǎn)生反射,影響高速傳輸性能; 參考層:MIPI信號線下方一定要有參考層(推薦用地層),且一定要保證參考層的連續(xù)性(即在MIPI信號

2023-04-12 15:08:27

的間距最好是0.5mm以上。這樣有助于避免交互干擾。另一種選擇達到90 ohm的差分阻抗的方法。可以在USB的差分信號線對加上6pF到地。因為有些設(shè)計需要這些,但是當(dāng)有些PCB設(shè)計達不到90 ohm

2023-04-13 16:09:54

夾雜在差分信號之間的非查份(單獨一條)走線方式有什么要求嗎?這就是要畫的連接線PCB高速差分信號線四層怎么弄,還要求阻抗,就是一個連接線

2023-04-07 17:46:45

1.1 PCB板上預(yù)劃分數(shù)字、模擬、DAA信號布線區(qū)域。1.2 數(shù)字、模擬元器件及相應(yīng)走線盡量分開并放置於各自的布線區(qū)域內(nèi)。1.3 高速數(shù)字信號走線盡量短。1.4 敏感模擬信號走線盡量短。1.5

2019-05-30 06:58:19

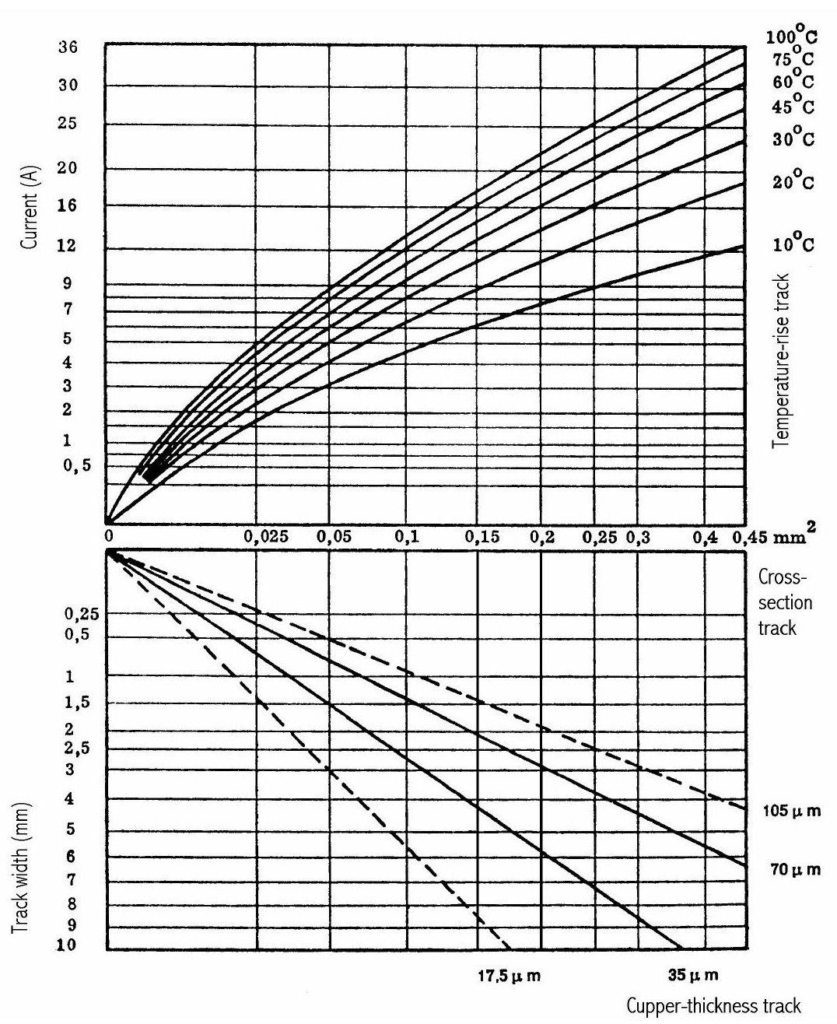

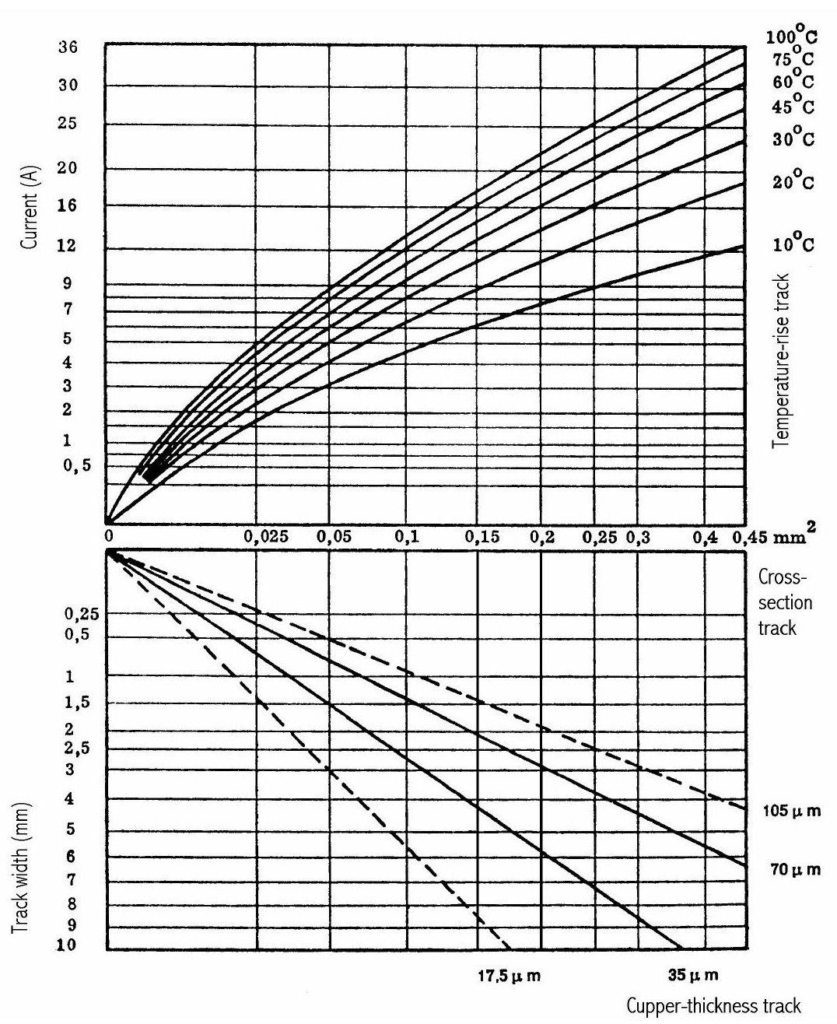

PCB設(shè)計走線的寬度與最大允許電流有何關(guān)系?PCB設(shè)計走線的寬度與銅厚有何關(guān)系?

2021-10-11 09:49:14

PCB設(shè)計走線的規(guī)則是什么

2021-03-17 06:36:28

減少布線層,降低PCB成本。 當(dāng)然,這樣做的代價是冒一些技術(shù)風(fēng)險,甚至犧牲一半成功率。 對于背板的層疊設(shè)計,鑒于常見背板很難做到相鄰走線互相垂直,不可避免地出現(xiàn)平面長距離布線。 對于高速背板

2023-04-12 15:12:13

硬件工程師做久了自然有自己處理電路板的一套方法,也許不是最好的辦法,自己卻能理解其中的意義。但是工作中還是要按照最完美的辦法進行操作,本期我們就來了解一下關(guān)于高速信號走線準(zhǔn)則到底有哪幾條是你不清楚的?

2020-10-30 08:33:48

請問大伙PCB設(shè)計中,常見的串口通訊線(TX、RX)是否屬于高速信號線?然后高速信號的標(biāo)準(zhǔn)到底是什么?在網(wǎng)上瀏覽了一些相關(guān)知識,感覺始終不太理解。

2023-01-26 20:39:13

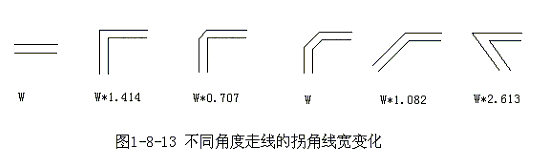

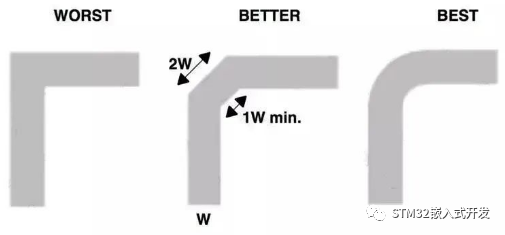

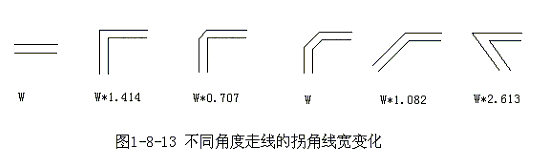

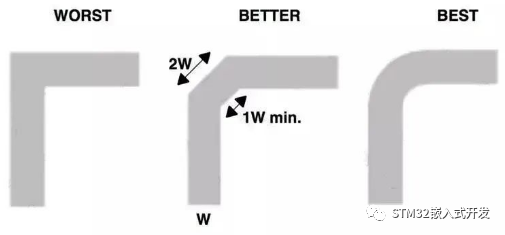

電容,反射,EMI等效應(yīng)在TDR測試中幾乎體現(xiàn)不出來,高速PCB設(shè)計工程師的重點還是應(yīng)該放在布局,電源/地設(shè)計,走線設(shè)計,過孔等其他方面。當(dāng)然,盡管直角走線帶來的影響不是很嚴(yán)重,但并不是說我們以后都可以

2018-09-17 17:31:52

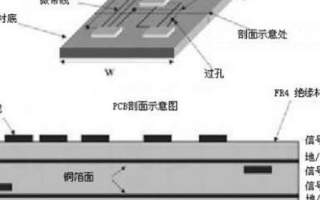

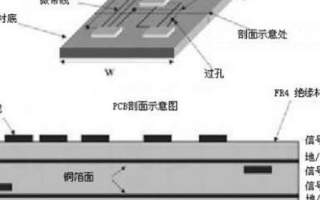

區(qū)域。如果Tr≤2Tpd,信號落在問題區(qū)域。對于落在不確定區(qū)域及問題區(qū)域的信號,應(yīng)該使用高速布線方法。(四)、什么是傳輸線 PCB板上的走線可等效為下圖所示的串聯(lián)和并聯(lián)的電容、電阻和電感結(jié)構(gòu)。串聯(lián)

2015-05-05 09:30:27

高速信號區(qū)域相應(yīng)的電源平面或地平面盡可能保持完整(11)建議布線分布均勻,大面積無布線的區(qū)域需要輔銅,但要求不影響阻抗控制(12)建議所有布線需倒角,倒角角度推薦45度(13)建議防止信號線在相鄰層

2017-02-16 15:06:01

。(8)建議布線到板邊的距離大于2MM(9)建議信號線優(yōu)先選擇內(nèi)層布線(10)建議高速信號區(qū)域相應(yīng)的電源平面或地平面盡可能保持完整(11)建議布線分布均勻,大面積無布線的區(qū)域需要輔銅,但要求不影響阻抗

2017-02-10 10:42:11

/0.86mm 的過孔,也可以嘗試非穿導(dǎo)孔;對于電源或地線的過孔則可以考慮使用較大尺寸,以減小阻抗;2.PCB 上的信號走線盡量不換層,也就是說盡量減少過孔;3.電源和地的管腳要就近做過孔,過孔和管腳之間

2016-12-20 15:51:03

。 問:在高速PCB設(shè)計中,串?dāng)_與信號線的速率、走線的方向等有什么關(guān)系?需要注意哪些設(shè)計指標(biāo)來避免出現(xiàn)串?dāng)_等問題? 答:串?dāng)_會影響邊沿速率,一般來說,一組總線傳輸方向相同時,串?dāng)_因素會使邊沿速率變慢

2019-01-11 10:55:05

高速PCB設(shè)計的疊層問題

2009-05-16 20:51:30

本期講解PCB設(shè)計中高速信號關(guān)鍵信號的布線要求。一、時鐘信號布線要求在數(shù)字電路設(shè)計中,時鐘信號是一種在高態(tài)與低態(tài)之間振蕩的信號,決定著電路的性能。時鐘電路在數(shù)字電路中點有重要地位,同時又是產(chǎn)生

2017-10-19 14:25:36

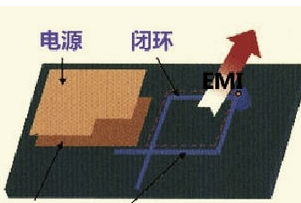

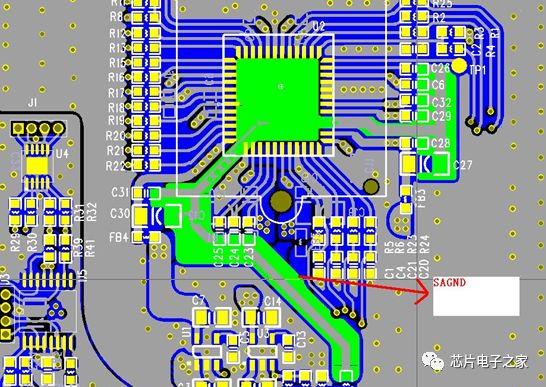

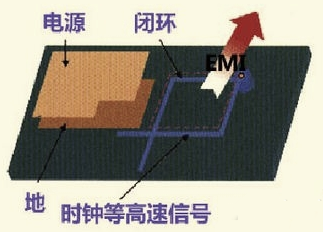

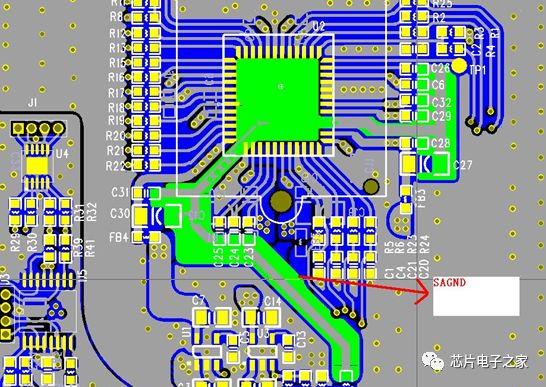

規(guī)則一:高速信號走線屏蔽規(guī)則 在高速的PCB設(shè)計中,時鐘等關(guān)鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地

2016-01-19 22:50:31

。 而絕對的要求是控制兩個器件之間的走線延遲為某一個值,比如器件A、B之間的延遲為Ins,而這樣的要求往往由高速電路設(shè)計者提出,而由PCB工程師去實現(xiàn)。要滿足這個要求,就必須知道信號的傳播速度c但需要

2018-11-27 15:22:54

、PCB的可靠性設(shè)計4、電磁兼容性和PCB設(shè)計約束三、1、改進電路設(shè)計規(guī)程提高可測性2、混合信號PCB的分區(qū)設(shè)計3、蛇形走線的作用4、確保信號完整性的電路板設(shè)計準(zhǔn)則四、1、印制電路板的可靠性設(shè)計五、1

2012-07-13 16:18:40

比如射頻走線或者一些高速信號線,必須走多層板外層還是內(nèi)層也可以走線

2023-10-07 08:22:18

PCB設(shè)計時,有時候需要在不增加PCB走線寬度的情況下提高該走線通過大電流的能力(載流能力),通常的方法是給該導(dǎo)線鍍錫(或者上錫);下面以在PCB頂層走線鍍錫為例,使用AD09軟件,簡單介紹如何走線上錫處理:1、?選擇TopLayer層,確定需要走線的地方,畫一條導(dǎo)線;(圖文詳解見附件)

2019-09-06 15:57:30

PCB Layout中的走線策略布線(Layout)是PCB設(shè)計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統(tǒng)的性能,大多數(shù)高速的設(shè)計理論也要最終經(jīng)過Layout得以實現(xiàn)并驗證,由此可見

2009-08-20 20:58:49

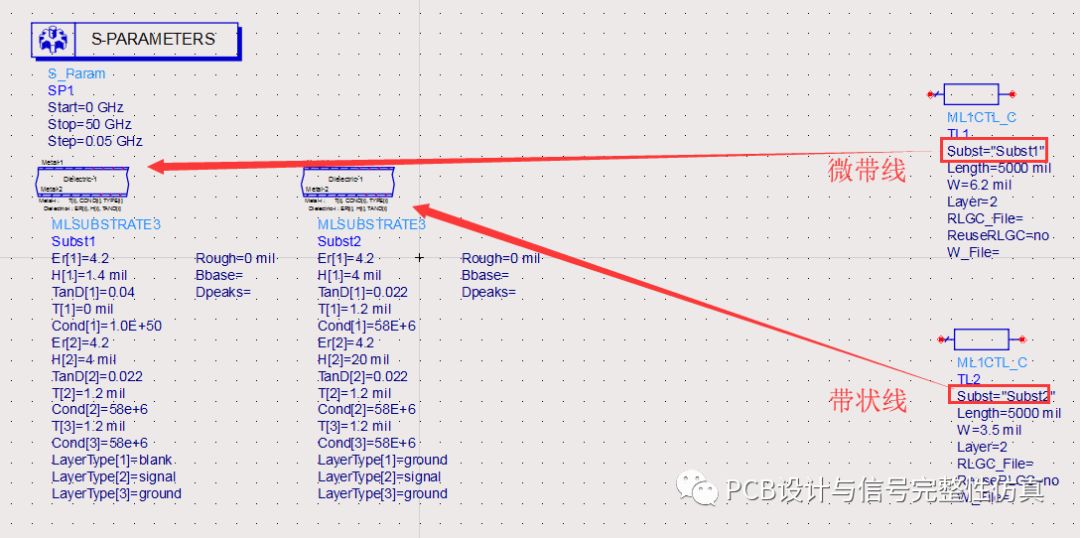

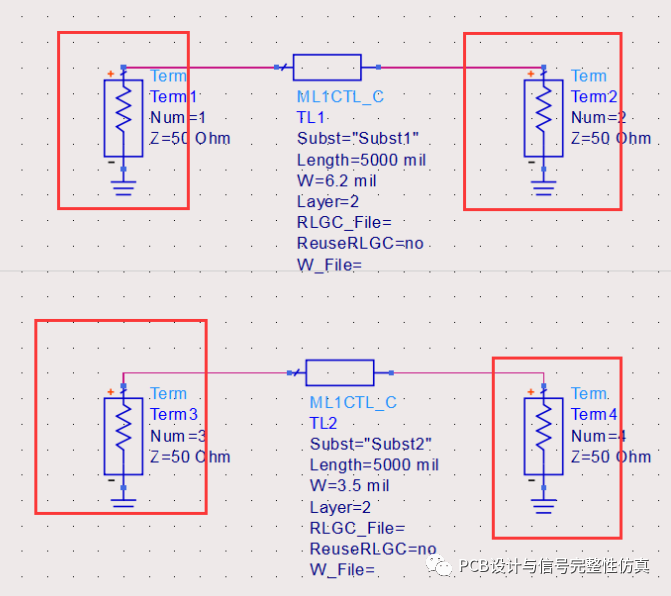

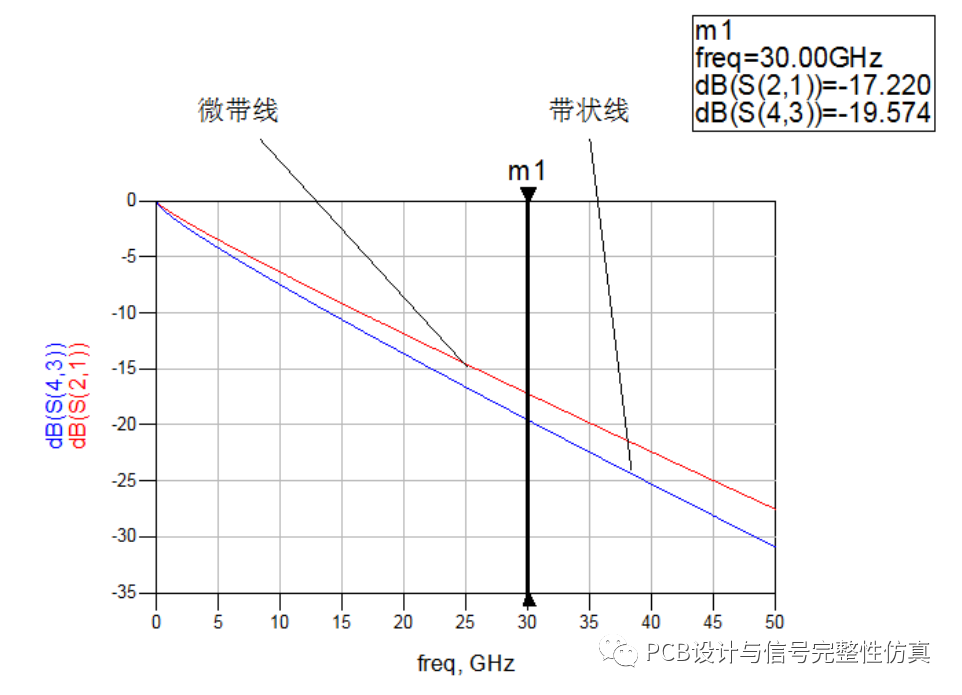

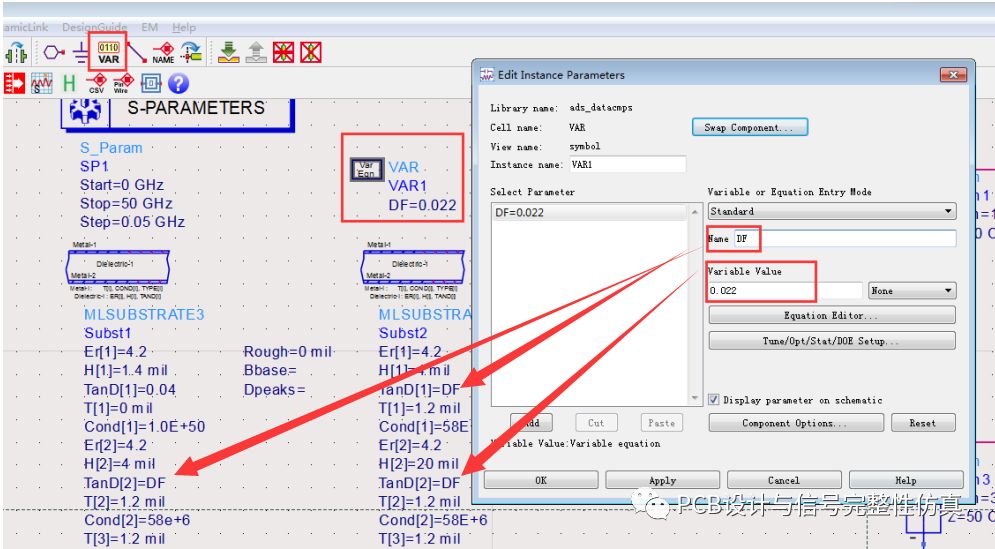

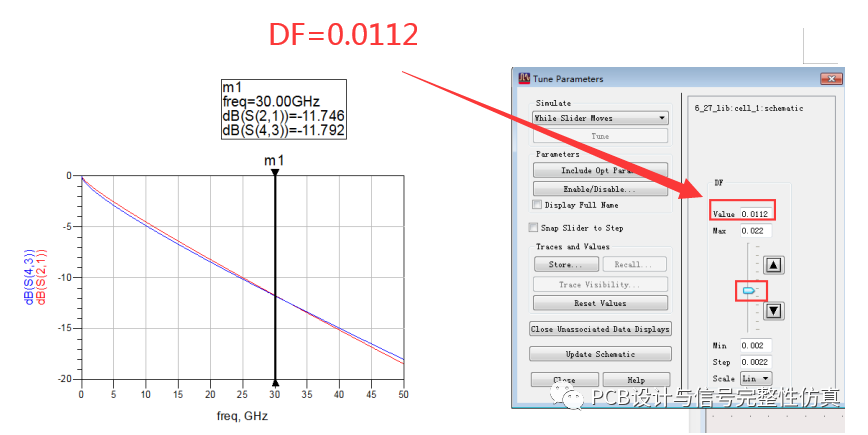

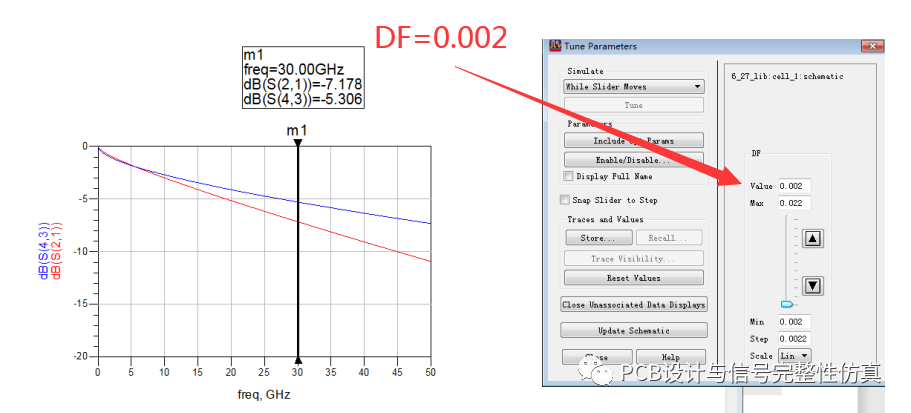

過多損失掉,因此在布線前期就需要規(guī)劃選擇一個合適的走線層。這里我們通過仿真軟件來對比表層走線與內(nèi)層走線,誰更適合用于高速信號的傳輸。首先搭建疊層模板,分別是表層走線模板和內(nèi)層走線的層疊模板:為了更接近

2020-03-09 10:57:00

高速PCB設(shè)計是一個相對復(fù)雜的過程,由于高速PCB設(shè)計中需要充分考慮信號、阻抗、傳輸線等眾多技術(shù)要素,常常成為PCB設(shè)計初學(xué)者的一大難點,本文提供的幾個關(guān)于高速PCB設(shè)計的基本概念及技術(shù)要點

2023-04-19 16:05:28

高速先生成員--黃剛

一些通用的PCB設(shè)計經(jīng)驗以及高速信號理論,都告訴我們PCB上的信號最好都以地平面為參考,尤其是高速走線,建議上下參考平面都是地平面是最好的方法。但是產(chǎn)品類型千千萬萬,導(dǎo)致疊層

2025-11-11 17:46:12

大小和走線粗細決定銅箔厚度,如電源板一般使用2-3OZ銅箔,普通信號板一般選擇1OZ的銅箔,走線較細的情況還可能會使用1/3QZ銅箔以提高良品率;同時避免在內(nèi)層使用兩面銅箔厚度不一致的芯板。5、PCB板

2017-01-16 11:40:35

高速信號區(qū)域相應(yīng)的電源平面或地平面盡可能保持完整(11)建議布線分布均勻,大面積無布線的區(qū)域需要輔銅,但要求不影響阻抗控制(12)建議所有布線需倒角,倒角角度推薦45度(13)建議防止信號線在相鄰層

2017-01-23 16:04:35

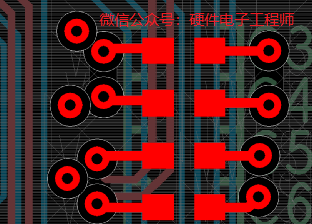

。(3)遵守緊耦合的原則,當(dāng)兩條差分信號線距離很近時,電流傳輸方向相反,其磁場相互抵消,電場相互耦合,電磁輻射也要小得多。為減少損耗,高速差分線換層時可以在換層孔的附近添加地過孔。(4)走線盡可能地短而

2017-07-18 10:57:28

形成邊長超過200MIL的自環(huán)(14)建議相鄰層的布線方向成正交結(jié)構(gòu)說明:相鄰層的布線避免走成同一方向,以減少層間串?dāng)_,如果不可避免,特別是信號速率較高時,應(yīng)考慮用地平面隔離各布線層,用地信號隔離各信號線。更多技術(shù)干貨可關(guān)注【快點PCB學(xué)院】公眾號

2017-01-23 09:36:13

通用的高速信號PCB設(shè)計處理原則有:(1)層面的選擇:處理高速信號優(yōu)先選擇兩邊是GND的層面處理(2)處理時要優(yōu)先考慮高速信號的總長(3)高速信號Via數(shù)量的限制:高速信號允許換一次層,換層時加

2017-02-07 09:40:04

圖解在高速的PCB設(shè)計中的走線規(guī)則

2021-03-17 07:53:30

在高速PCB設(shè)計過程中,由于存在傳輸線效應(yīng),會導(dǎo)致一些一些信號完整性的問題,如何應(yīng)對呢?

2021-03-02 06:08:38

解決高速PCB設(shè)計信號問題的全新方法

2021-04-25 07:56:35

作為一名合格的、優(yōu)秀的PCB設(shè)計工程師,我們不僅要掌握高速PCB設(shè)計技能,還需要對其他相關(guān)知識有所了解,比如高速PCB材料的選擇。這是因為,PCB材料的選擇錯誤也會對高速數(shù)字電路的信號傳輸性能造成不良影響。

2021-03-09 06:14:27

。 6. 高速PCB設(shè)計中,蛇形線沒有所謂濾波或抗干擾的能力,只可能降低信號質(zhì)量,所以 只作時序匹配之用而無其它目的。 7. 有時可以考慮螺旋走線的方式進行繞線。

2014-12-16 09:47:09

電源布局、網(wǎng)口電路、音頻走線的PCB設(shè)計

2021-03-04 06:10:24

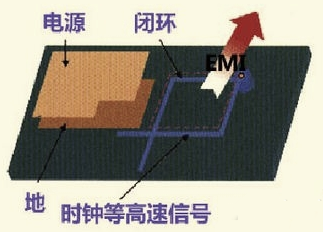

網(wǎng)絡(luò),在多層的PCB走線的時候一旦產(chǎn)生了開環(huán)的結(jié)果,將產(chǎn)生線形天線,增加EMI的輻射強度。 圖3 開環(huán)規(guī)則 規(guī)則四:高速信號的特性阻抗連續(xù)規(guī)則 高速信號,在層與層之間切換的時候必須保證特性阻抗

2018-09-20 10:38:01

。規(guī)則四:高速信號的特性阻抗連續(xù)規(guī)則高速信號,在層與層之間切換的時候必須保證特性阻抗的連續(xù),否則會增加EMI的輻射。也就是說,同層的布線的寬度必須連續(xù),不同層的走線阻抗必須連續(xù)。規(guī)則五:高速PCB設(shè)計

2017-11-02 12:11:12

什么是高速pcb設(shè)計高速線總體規(guī)則是什么?

2019-06-13 02:32:06

和方式要符合所用的探棒。11、在高速 PCB 設(shè)計中,信號層的空白區(qū)域可以敷銅,而多個信號層的敷銅在接地和接電源上應(yīng)如何分配?一般在空白區(qū)域的敷銅絕大部分情況是接地。 只是在高速信號線旁敷銅時要注意敷

2017-01-20 10:29:29

高速PCB設(shè)計的疊層問題

2009-05-16 20:06:45 0

0 PCB走線策略

布線(Layout)是PCB設(shè)計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統(tǒng)的性能,大多數(shù)高速的設(shè)計理論也要最終經(jīng)過Layout得

2006-09-25 14:11:02 7284

7284 高速信號走線規(guī)則教程

隨著信號上升沿時間的減小,信號頻率的提高,電子產(chǎn)品的EMI問題,也來越受到電子工程師的關(guān)注。高速PCB設(shè)計的成功,對EMI

2009-04-15 08:49:27 3220

3220

在電路板PCB設(shè)計時,有時候需要在不增加PCB走線寬度的情況下提高該走線通過大電流的能力,通常是在PCB走線上鍍錫(或叫上錫),下面以在PCB底層走線鍍錫為例,使用Protel DXP2004軟件

2011-10-31 15:00:27 0

0 PCB設(shè)計與走線PCB設(shè)計與走線layout對PCB走線與擺件規(guī)則全面了解和 掌握提升走線和擺件技能。

2016-07-21 16:33:13 0

0 開關(guān)電源的PCB設(shè)計(布局、排版、走線)規(guī)范,感興趣的小伙伴們可以看看。

2016-07-26 14:09:33 0

0 開關(guān)電源的PCB設(shè)計(布局、排版、走線)規(guī)范

2016-09-06 16:03:47 0

0 PCB設(shè)計布線中的3種特殊走線技巧,學(xué)習(xí)資料,感興趣的可以看看。

2022-05-12 10:34:20 0

0 在高速的PCB設(shè)計中,時鐘等關(guān)鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

2017-08-25 15:35:24 2566

2566

PADS可提供強大且易于使用的多走線高速布線功能,幫助您應(yīng)對這些挑戰(zhàn)。讓您可以根據(jù)PCB設(shè)計定義的規(guī)則選擇并完成多走線布線。以及根據(jù)需要選擇要完成的走線數(shù)量。如果采用PADS多走線HSDRouter,一切盡在您的掌握之中。

2017-09-19 11:41:38 29

29 規(guī)則一:高速信號走線屏蔽規(guī)則 在高速的PCB設(shè)計中,時鐘等關(guān)鍵的高速信號線,走線需要進行屏蔽處理,如果沒有

2017-11-25 07:43:00 8707

8707

布線(Layout)是PCB設(shè)計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統(tǒng)的性能,大多數(shù)高速的設(shè)計理論也要最終經(jīng)過Layout得以實現(xiàn)并驗證,由此可見,布線在高速PCB設(shè)計中是至關(guān)重要的。下面將針對實際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優(yōu)化的走線策略。

2018-04-14 11:06:00 4042

4042

本文主要介紹的是pcb開窗,首先介紹了PCB設(shè)計中的開窗和亮銅,其次介紹了如何實現(xiàn)PCB走線開窗上錫,最后闡述了PCB設(shè)計怎樣設(shè)置走線開窗的步驟,具體的跟隨小編一起來了解一下。

2018-05-04 15:37:30 40670

40670

學(xué)習(xí)高速PCB設(shè)計,首先要知道什么是傳輸線。信號會產(chǎn)生反射,就是因為PCB上的走線具有一定的阻抗,線上阻抗與輸出端的阻抗不匹配,就會導(dǎo)致信號反射。信號在PCB中傳輸會有延時,如果時序沒有匹配,系統(tǒng)就會罷工。這些都是因為傳輸線產(chǎn)生的問題。

2019-12-16 07:59:00 7828

7828

布線(Layout)是PCB設(shè)計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統(tǒng)的性能,大多數(shù)高速的設(shè)計理論也要最終經(jīng)過Layout得以實現(xiàn)并驗證,由此可見,布線在高速PCB設(shè)計中是至關(guān)重要的。

2019-02-05 08:49:00 4772

4772

在高速的PCB設(shè)計中,時鐘等關(guān)鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

2019-03-15 14:05:42 5826

5826

直角走線一般是PCB布線中要求盡量避免的情況,也幾乎成為衡量布線好壞的標(biāo)準(zhǔn)之一,那么直角走線究竟會對信號傳輸產(chǎn)生多大的影響呢?從原理上說,直角走線會使傳輸線的線寬發(fā)生變化,造成阻抗的不連續(xù)。其實不光是直角走線,頓角,銳角走線都可能會造成阻抗變化的情況。

2019-07-24 15:12:01 1967

1967

布線(Layout)是PCB設(shè)計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統(tǒng)的性能,大多數(shù)高速的設(shè)計理論也要最終經(jīng)過Layout得以實現(xiàn)并驗證,由此可見,布線在高速PCB設(shè)計中

2019-04-30 08:00:00 0

0 在高速的PCB設(shè)計中,時鐘等關(guān)鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

2019-05-06 18:08:15 4913

4913 布線(Layout)是PCB設(shè)計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統(tǒng)的性能,大多數(shù)高速的設(shè)計理論也要最終經(jīng)過Layout得以實現(xiàn)并驗證,由此可見,布線在高速PCB設(shè)計中

2019-07-01 15:24:50 6358

6358 本文主要分析一下在高速PCB設(shè)計中,高速信號與高速PCB設(shè)計存在一些理解誤區(qū)。 誤區(qū)一:GHz速率以上的信號才算高速信號? 提到高速信號,就需要先明確什么是高速,MHz速率級別的信號算高速、還是

2019-11-05 11:27:17 12570

12570

在高速的PCB設(shè)計中,時鐘等關(guān)鍵的高速信號線,走需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會造成EMI的泄漏。

2019-12-16 14:52:30 3830

3830

規(guī)則一:高速信號走線屏蔽規(guī)則 如上圖所示: 在高速的PCB設(shè)計中,時鐘等關(guān)鍵的高速信號線,走需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會造成EMI的泄漏。 建議屏蔽線,每1000mil,打孔

2020-02-14 11:53:40 13255

13255 除了精心選擇PCB絕緣體材料和走線布局外,還可以通過包括可編程差分輸出電壓,預(yù)加重和接收器均衡來降低信號衰減。差分輸出電壓的增加有助于改善接收器處的信號。預(yù)加重是僅通過增加第一個發(fā)射符號的電平來增強高頻信號分量的方法。接收器均衡電路衰減低頻信號分量,以覆蓋傳輸線損耗。

2020-09-17 15:42:24 2720

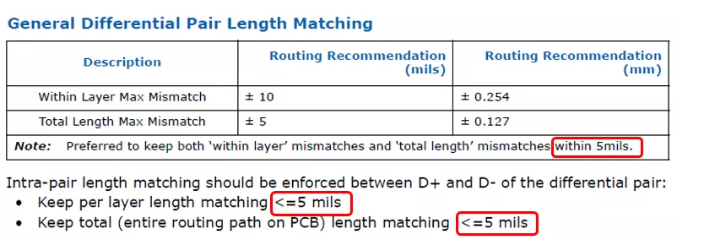

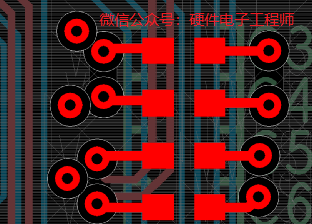

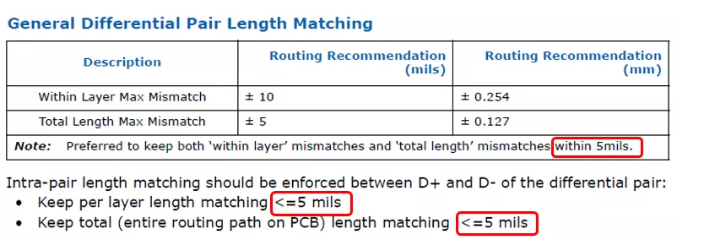

2720 在PCB設(shè)計中,等長走線主要是針對一些高速的并行總線來講的。 由于這類并行總線往往有多根數(shù)據(jù)信號基于同一個時鐘采樣,每個時鐘周期可能要采樣兩次(DDRSDRAM)甚至4次,而隨著芯片運行頻率的提高

2020-10-24 09:29:38 10834

10834 在 PCB 設(shè)計中,等長走線主要是針對一些高速的并行總線來講的。由于這類并行總線往往有多根數(shù)據(jù)信號基于同一個時鐘采樣,每個時鐘周期可能要采樣兩次(DDR SDRAM)甚至 4 次,而隨著芯片運行

2020-11-22 11:54:17 20854

20854 表層走線與內(nèi)層走線更為規(guī)范的說法應(yīng)該是微帶線與帶狀線。兩種走線方式因為介質(zhì)和參考面不同,會存在比較明顯的差異。

2020-12-19 10:23:13 7579

7579

PCB設(shè)計 的具體內(nèi)容 建議 PCB 設(shè)計用4或者6層 4層定義: 第一層(頂層) - 走線和地 第二層( 內(nèi)層 ) - 走線和 電源層 第三層(內(nèi)層) -完整的地層(可能有模擬地和數(shù)字地) 第四層

2021-08-30 11:00:43 30345

30345

布線(Layout)是pcb設(shè)計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統(tǒng)的性能,大多數(shù)高速的設(shè)計理論也要最終經(jīng)過Layout得以實現(xiàn)并驗證,由此可見,布線在高速pcb設(shè)計中

2022-02-10 12:11:07 40

40 布線(Layout)是PCB設(shè)計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統(tǒng)的性能,大多數(shù)高速的設(shè)計理論也要最終經(jīng)過 Layout 得以實現(xiàn)并驗證,由此可見,布線在高速 PCB 設(shè)計中

2022-02-11 15:24:33 30

30 蛇形走線是PCB設(shè)計中會遇到的一種比較特殊的走線形式(如下圖所示),很多人不理解蛇形走線的意義,下面對蛇形走線的作用進行簡單介紹。

2023-03-30 18:14:23 6216

6216 現(xiàn)在但凡打開SoC原廠的PCB Layout Guide,都會提及到高速信號的走線的拐角角度問題,都會說高速信號不要以直角走線,要以45度角走線,并且會說走圓弧會比45度拐角更好。

2023-04-03 16:29:17 3062

3062

設(shè)計 PCB 變得非常容易, 由于可用的工具負載。對于正在接觸PCB設(shè)計的初學(xué)者來說, 他可能不太關(guān)心PCB中使用的走線特性。然而,當(dāng)你爬上梯子時,注意PCB走線是非常重要的。在本文中,我們匯總了一些您應(yīng)該了解的有關(guān)PCB走線以及如何為您的PCB設(shè)計正確走線的重要事項。

2023-05-13 15:15:46 6741

6741

解決。 高速信號走線屏蔽規(guī)則 如上圖所示:在高速的PCB設(shè)計中,時鐘等關(guān)鍵的高速信號線,則需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會造成EMI的泄漏。 建議屏蔽線每1000mil打孔接地 。 高速信號的走線閉環(huán)規(guī)則 由于PCB板的密度越來越高,很多PCB

2023-05-22 09:15:58 2337

2337

串?dāng)_可能發(fā)生在單個PCB層上的相鄰走線之間,也可能發(fā)生在兩層PCB之間相互平行和垂直的走線之間。當(dāng)這種情況發(fā)生時,來自一條走線的信號會蓋住另一條走線,因為它的振幅比另一條走線更大。

2023-10-12 09:25:00 1726

1726 高速PCB設(shè)計的疊層問題

2022-12-30 09:22:17 43

43 PCB設(shè)計中常見的走線等長要求

2023-11-24 14:25:36 6535

6535

在高速PCB設(shè)計中,信號層的空白區(qū)域可以敷銅,而多個信號層的敷銅在接地和接電源上應(yīng)如何分配? 在高速PCB設(shè)計中,信號層的空白區(qū)域可以敷銅,而多個信號層的敷銅在接地和接電源上應(yīng)該經(jīng)過合理分配。接地

2023-11-24 14:38:21 1850

1850 PCB設(shè)計的時候采用哪種走線形式更好? 在PCB設(shè)計中,采用合適的走線形式對電路的性能和可靠性都有著重要的影響。以下是幾種常見的走線形式,它們各有優(yōu)勢,根據(jù)具體的設(shè)計需求選擇合適的形式會更有利于提高

2023-12-07 14:24:46 1728

1728 差分線pcb走線原則? 差分線是PCB設(shè)計中非常重要的一個部分,它的設(shè)計和走線原則可以直接影響到電路性能的穩(wěn)定性和可靠性。在以下文章中,我將詳盡、詳實、細致地探討差分線的設(shè)計原則及其在PCB走線中

2023-12-07 18:09:37 7616

7616 由于 PCB 板的密度越來越高,許多 PCB LAYOUT 工程師在走線的過程中,較容易出現(xiàn)一種失誤,即時鐘信號等高速信號網(wǎng)絡(luò),在多層的 PCB 走線的時候產(chǎn)生了閉環(huán)的結(jié)果,這樣的閉環(huán)結(jié)果將產(chǎn)生環(huán)形天線,增加 EMI 的輻射強度。

2024-01-08 15:33:04 2544

2544

在高速的 PCB 設(shè)計中,時鐘等關(guān)鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成 EMI 的泄漏。

2024-01-10 16:03:05 1828

1828

PCB走線是將電路設(shè)計中的電氣信號通過導(dǎo)線連接到PCB板上而形成的電路。這些導(dǎo)線被稱為“走線”,通常由銅或其他導(dǎo)電材料制成。今天捷多邦小編帶大家一起了解pcb走線厚度對線路板的影響 在PCB的制作

2024-04-15 17:43:36 2287

2287 : 高速電路PCB設(shè)計EMI方法與技巧 一、信號走線規(guī)則 屏蔽規(guī)則: 關(guān)鍵高速信號線(如時鐘線)需進行屏蔽處理,可在信號線周圍設(shè)置接地的屏蔽層,或?qū)?b class="flag-6" style="color: red">高速線布置在內(nèi)部信號層,上下層鋪銅接地作為屏蔽。 建議屏蔽線每1000mil打孔接地,確保屏蔽有效性。 閉環(huán)與開環(huán)規(guī)則: 避

2025-11-10 09:25:22 429

429

電子發(fā)燒友App

電子發(fā)燒友App

評論