在FPGA調試過程中,除了邏輯代碼本身的質量之外,FPGA板子上PCB走線、接插件質量等因素的影響也非常重要。在剛上板調試不順利的時候,不妨拿示波器看一下信號的質量,比如時鐘信號的質量、差分信號

2020-11-20 12:11:30 6311

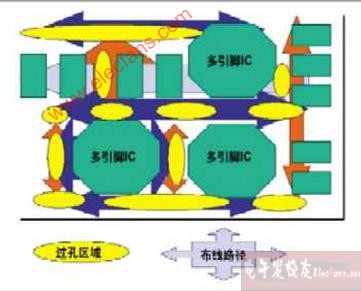

6311 在集成電路應用設計中,項目原理圖設計完成之后,就需要進行PCB布板的設計。 PCB設計是一個至關重要的環節。 設計結果的優劣直接影響整個設計功能。 因此,合理高效的PCB Layout是芯片電路設計調試成功中至關重要的一步。 本次我們就來簡單講一講PCB Layout的設計要點。

2023-05-22 10:59:17 1676

1676

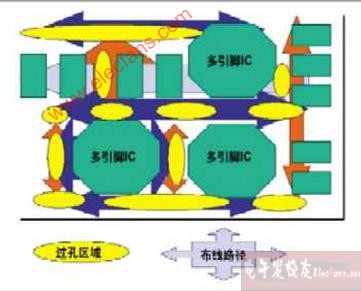

在集成電路應用設計中,項目原理圖設計完成之后,就需要進行PCB布板的設計。PCB設計是一個至關重要的環節。設計結果的優劣直接影響整個設計功能。因此,合理高效的PCB Layout是芯片電路設計調試成功中至關重要的一步。本次我們就來簡單講一講PCB Layout的設計要點。

2023-05-31 10:52:56 1637

1637

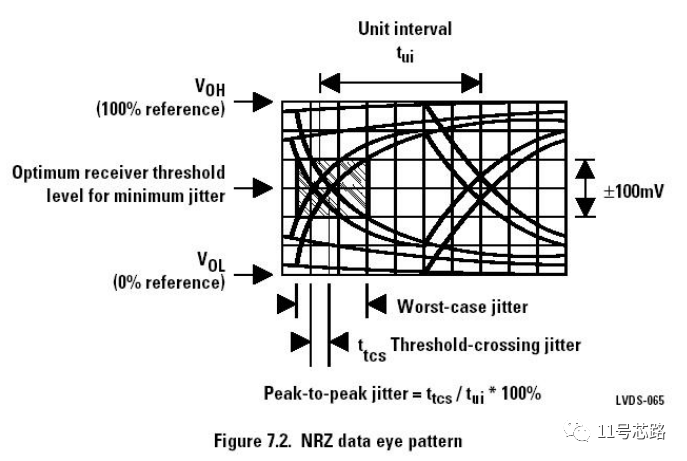

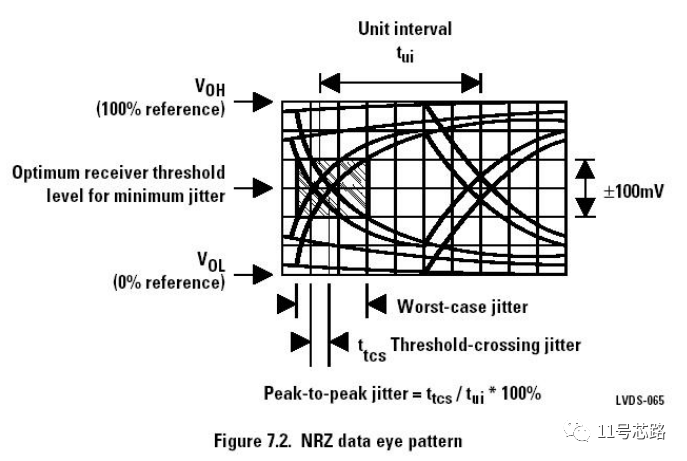

LVDS是一種低擺幅的差分信號技術,它使得信號能在差分PCB線對或平衡電纜上以幾百Mbps的速率傳輸,其低壓幅和低電流驅動輸出實現了低噪聲和低功耗。

2023-10-02 16:44:00 2571

2571

,如果轉接板特性阻抗也設計100Ω的話,信號機的LVDS信號到液晶模組的特性阻抗是不是就200Ω了,匹配電阻在液晶模組上,如果是這樣計算200Ω不等于100Ω也就不匹配了。2,如上情況轉接板的走線還有控制特性阻抗100Ω嗎?串聯連接的特性阻抗怎么理解,怎么計算?

2018-12-16 16:55:27

本帖最后由 eehome 于 *** 編輯

我的單色屏,視頻信號是LVDS現在我換成了彩屏,彩屏僅支持AV輸入我想在彩屏上顯示以前單色屏的內容所以就得把LVDS信號轉為AV信號求大神幫忙啊!!!

2012-09-23 13:44:52

技術。LVDS即低電壓差分信號,這種技術的核心是采用極低的電壓擺幅高速差動傳輸數據,可以實現點對點或一點對多點的連接,具有低功耗、低誤碼率、低串擾和低輻射等特點,其傳輸介質可以是銅質的PCB連線,也可 以是平衡

2016-04-15 16:13:33

一、LVDS連接器:高速傳輸的關鍵組件

在現代設計電子中,數據傳輸的速度和穩定性至關重要。LVDS(低電壓差分信號)連接器憑借其高速、低功耗、抗干擾能力強等特點,成為眾多應用領域的首選連接方案

2025-02-18 18:18:36

盡管現在的EDA工具很強大,但隨著PCB尺寸要求越來越小,器件密度越來越高,PCB設計的難度并不小。如何實現PCB高的布通率以及縮短設計時間呢?本文介紹PCB規劃、布局和布線的設計技巧和要點。

2021-01-22 06:44:11

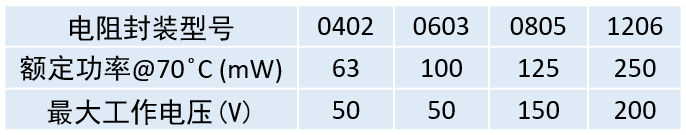

pcb設計在整個電路板中非常重要,它決定著整個pcb的基礎。本文總結了在PCB設計中一些需要注意的要點,以供參考。 1、選擇PCB板材 選擇PCB板材必須在滿足設計需求和可量產性及成本中間

2018-11-28 11:35:36

晶振電源電路原理圖設計要點PCB設計要點

2021-02-25 08:25:34

- lcdd19 對應的是LVDS1信號通過復用表可以查到,LVDS的信號都是Function 3,所以在配置port時要配置成功能如:lcdd10 = port:PD10

2022-01-04 06:57:34

我的AD9446的工作在LVDS模式下,請問對于AD9446(100MHz),LVDS信號線的PCB走線的差分對間等長有沒有要求?(PS:16對差分線,都做等長好復雜)謝謝!

2023-12-18 06:26:51

親愛的Xilinx人,我有一些簡單的問題要問。我正在使用Virtex 6 SX475T進行PCB設計。我正在考慮添加一個擴展端口,它有2對CML和6對LVDS信號。從用戶指南,我認為一個GTX銀行

2020-06-13 08:38:27

開關電源PCB排版與數字電路PCB排版的區別在哪里?開關電源PCB排版技術要點有哪些?

2021-04-25 09:38:28

利用高速FPGA設計PCB的要點及相關指導原則有哪些?

2021-04-25 08:17:55

你好,我試圖在Kintex7評估板上以不同的速度生成兩個LVDS信號。信號發送到一個XM105調試卡,連接到HPC連接器上的電路板。要生成LVDS信號,請使用下面發布的代碼并生成所需的IP內核。但是

2020-07-20 16:10:47

大家好我正在使用Xilinx Spartan 3e芯片。我可以在嚴格的輸入信號或嚴格的輸出上使用LVDS。但有沒有人知道如何編碼verilog在雙向信號上使用LVDS標準?非常感謝你花時間陪伴。以上

2019-01-08 10:17:47

實現PCB高效自動布線的設計技巧和要點有哪些?

2021-04-26 06:25:00

差分線對的PCB設計要點

2012-08-20 14:52:39

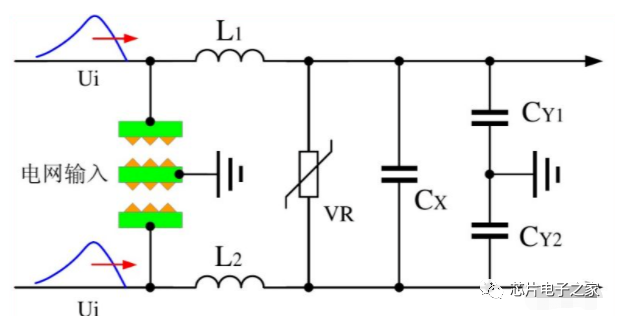

開關電源PCB 排版基本要點(經典)開關電源PCB 排版是開發電源產品中的一個重要過程。許多情況下,一個在紙上設計得非常完美的電源可能在初次調試時無法正常工作,原因是該電源的PCB 排版存在著許多問題。詳細討論了開關電源PCB 排版的基本要點,并描述了一些實用的PCB 排版例子

2012-08-20 12:33:08

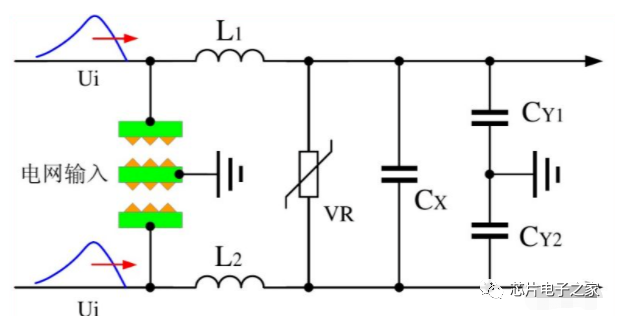

的寄生并聯電容應盡量小,電感引腳焊盤之間的距離越遠越好;要點3、避免在地層上放置任何功率或信號走線;要點4、高頻環路的面積應盡可能減小;要點5、過孔放置不應破壞高頻電流在地層上的路徑;要點6、系統板上一小

2016-07-15 11:41:38

開關電源的PCB布線設計技巧開關電源PCB排版的8個要點

2021-04-26 06:59:36

深入探討DFM在PCB設計中的注意要點,大家說自己的經驗,交流交流,學習學習。

2014-10-24 15:15:34

控制設備的輸出可能連接到噪聲很大而且功率高的機電設備上;另外一種情況就是在PCB的布局受到特定限制時。 在混合信號PCB板上通常有獨立的數字和模擬電源,能夠而且應該采用分割電源面。但是緊鄰電源層的信號

2015-01-14 14:27:34

如何進行合理的PCB布板設計呢?簡單講一講PCB Layout的設計要點

2022-02-22 06:16:49

請教一下各位pcb板上電源部分布局和走線的有哪些要點哦,可以把主板電源做紋波和噪聲盡可能的小,最好能提供一下實物的參考layout板學習哦,謝謝各位了

2014-10-24 15:08:06

PCB熱設計的要點是什么,需要注意哪些內容啊?很多東西感覺都不知道如何下手

2019-05-30 05:35:31

@我的AD9446的工作在LVDS模式下,請問對于AD9446(100MHz),LVDS信號線的PCB走線的差分對的對間等長有沒有要求?(PS:16對差分線,都做等長好復雜)謝謝!

2018-09-19 09:47:36

你好,有人以前在PSoC 5LP上使用LVDS嗎?或者有人做了一些可以用在PSoC 5LP上實現LVDS的東西嗎?至少有一些建議是很好的。謝謝大家, 以上來自于百度翻譯 以下為原文Hello

2019-07-29 14:48:38

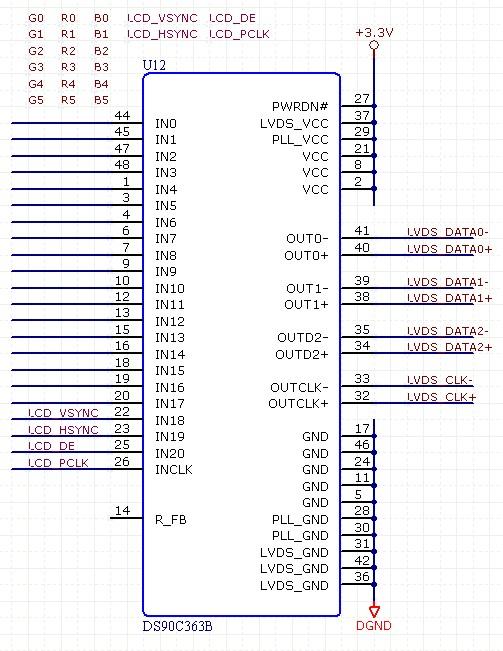

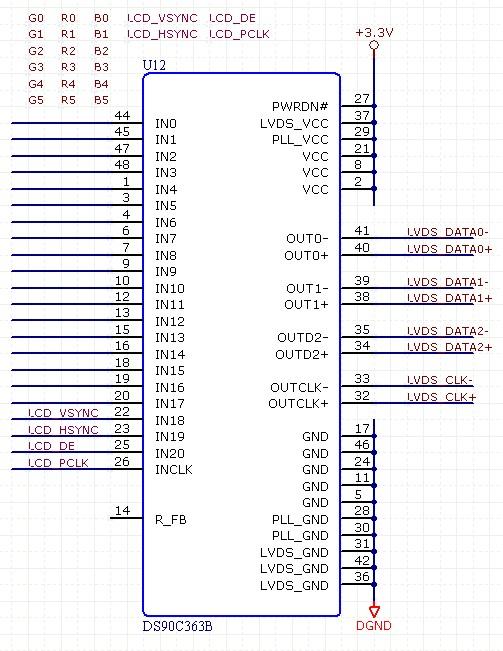

CPU需要外接lvds接口的屏,方案就是先用芯片將并行的RGB數據轉換成lvds差分對,然后接到LCD上。在轉換芯片的手冊上看到這樣的典型應用原理圖:這讓我產生了疑惑,因為我在網上看到:在PCB

2017-11-20 10:21:31

實現PCB高效自動布線的設計技巧和要點有哪些?

2021-04-21 07:02:16

摘要:介紹了LVDS(Low Voltage Differential Signals)技術的原理及其典型應用,并討論了在實際電路設計中使用LVDS接口時應注意的問題。關鍵詞:LVDS 接口 PCB

2010-05-14 09:29:00 61

61 LVDS(低壓差分信號)標準ANSI/TIA /E IA26442A22001廣泛應用于許多接口器件和一些ASIC及FPGA中。文中探討了LVDS的特點及其PCB (印制電路板)設計,糾正了某些錯誤認識。應用傳輸線理論分

2010-09-22 08:28:18 0

0 基于低電壓差分信號(LVDS)的高速信號傳輸

2010-12-17 17:21:46 40

40 什么是lvds信號

LVDS:Low Voltage Differential Signaling,低電壓差分信號。LVDS傳輸支持速率一般在155Mbps(大約為77MHZ)以上。LVDS是一種低擺幅的差分信號

2008-10-16 13:49:11 9059

9059 LVDS信號電平特性

LVDS物理接口使用1.2V偏置電壓作為基準,提供大約400mV擺幅。LVDS驅動器由一個驅動差分線對的電流源組成(通常電

2008-10-16 13:50:25 17544

17544 LVDS信號的PCB設計

1 LVDS信號的工作原理和特點 對于高速電路,尤其是高速數據總線,常用的器件一般有:ECL、BTL、GTL和GTL+等。這些器件的工藝成

2008-10-16 13:57:52 3732

3732 PCB高效自動布線的設計技巧和要點盡管現在的EDA工具很強大,但隨著PCB尺寸要求越來越小,器件密度越來越高,PCB設計的難度并不小。如何實

2009-03-25 11:26:12 1315

1315

摘 要: 介紹了LVDS(低電壓差分信號)技術的原理和應用,并討論了在單板和系統設計中應用LVDS時的布線技巧。

關鍵詞: LVDS PCB設計

2009-06-20 15:50:32 2235

2235

隨著數字電路數據量的提高,數據的傳輸速率也越來越快,LVDS(低壓差分信號)標準越來越多的應用在FPGA和ASIC器 件中。文章對LVDS信號的特點進行了分析,說明了PCB設計中差分走線的注意事項并結合實際應用設計了一塊LVDS接口板。 關鍵詞: LVDS; PCB設計;接口;阻抗

2011-02-23 09:54:03 341

341 文中以基于FPGA設計的高速信號下載器為例,從LVDS的PCB設計,約束設置和信號完整性仿真等多方面研究LVDS信號的實現。

2012-04-20 10:37:02 59

59 開關電源PCB 排版基本要點,更好的布局、布線

2015-12-02 09:47:55 0

0 開關電源PCB排版基本要點--設計開關電源必看

2016-03-11 15:35:22 0

0 DDR4 PCB設計規范&設計要點,DDR4 PCB設計規范&設計要點

2016-07-26 14:09:33 0

0 詳細的介紹了 開關電源的pcb設計要點

2016-09-06 16:03:47 0

0 開關電源PCB排版基本要點有參考價值

2016-12-16 21:20:06 0

0 PCB布線要點

2016-12-15 17:04:31 0

0 開關電源PCB布線要點

2017-07-21 14:37:58 52

52 在比較簡單的未大量使用過孔的四層或六層 PCB上,可能很難對 LVDS 或 LVPECL 這類差分信號布線。其原因是,驅動器上的正極引腳必須驅動接收器上的相應正極引腳,而負極引腳則必須驅動接收器的負極引腳。有時跡線以錯誤的方向結束,這實際上是向電路中添加了一個倒相器。

2019-05-23 08:09:00 2777

2777 共同設計在一塊PCB上。在此,通過透徹分析高密度、高性能、混合信號PCB的布局和布線設計,你可以掌握成功策略和技術。

2019-05-17 14:42:26 1365

1365 共同設計在一塊PCB上。在此,通過透徹分析高密度、高性能、混合信號PCB的布局和布線設計,你可以掌握成功策略和技術。

2019-09-27 14:46:26 2349

2349 現代混合信號PCB設計的另一個難點是不同數字邏輯的器件越來越多,比如GTL、LVTTL、LVCMOS及LVDS邏輯,每種邏輯電路的邏輯門限和電壓擺幅都不同,但是,這些不同邏輯門限和電壓擺幅的電路必須共同設計在一塊PCB上。

2019-12-10 15:28:16 1379

1379

LVDS信號不僅是差分信號,而且還是高速數字信號。因此LVDS傳輸媒質不管使用的是PCB線還是電纜,都必須采取措施防止信號在媒質終端發生反射,同時應減少電磁干擾以保證信號的完整性。

2020-03-08 13:14:00 2484

2484 在設計多層PCB電路板之前,設計者需要根據電路規模、電路板尺寸以及電磁兼容(EMC)要求來確定所采用的電路板結構,確定層數后,再確定內電層的放置位置以及如何在這些層上分布不同的信號,這就是多層PCB

2020-07-19 09:18:38 2515

2515 該參考設計展示了如何解決和優化信號完整性難題,通常在嘈雜環境中在同一個 PCB 上沿較長的距離發送 SPI 信號或從一個 PCB 向另一個電路板發送 SPI 信號(通過 LVDS 接口傳輸 SPI 信號)時會遇到這些難題。該概念具有高噪聲抗擾性、更低的 EMI 發射和更寬的共模輸入容差。

2020-08-10 08:00:00 89

89 來源:羅姆半導體社區 在高速PCB設計過程中,特殊元件是指高頻部分的關鍵部件,電路中的核心部件,易受干擾的元件,高壓元件,熱量大的元件,以及一些元件。 對于異性組件,需要仔細分析這些特殊組件的位置

2022-12-09 18:04:41 1831

1831 很多工程師在使用Xilinx開發板時都注意到了一個問題,就是開發板中將LVDS的時鐘輸入(1.8V電平)連接到了VCCO=2.5V或者3.3V的Bank上,于是產生了關于FPGA引腳與LVDS(以及

2020-10-10 09:25:37 13437

13437

,采集卡上使用DS90CR288進行并轉串處理,這種方式占用FPGA管腳資源多。當傳輸24bit RGB信號時,需要使用24(信號)+4(同步控制)+1(時鐘)=29個管腳,而使用lvds傳輸,使用altlvds_tx核,只需要5對lvds信號即可,共占用10個管腳。

2020-12-30 16:57:27 25

25 LVDS信號的電壓擺幅只有350MV, 為電流驅動的差分信號方式工作,最長的傳輸距離可以達到10米以上。為了確保信號在傳輸線當中傳播時,不受反射信號的影響,LVDS信號要求傳輸線阻抗受控,其中單線

2020-12-30 16:57:25 12

12 開關電源PCB排版基本要點(深圳核達中遠通電源技術有限公司項目)-開關電源PCB排版基本要點,電路會布板也要會!

2021-09-30 09:24:02 0

0 本文要點 接地噪聲是 PCB 上可能出現的多類信號干擾的總稱,所有這些干擾類型都會影響 PCB 的工作方式。 接地噪聲會帶來信號完整性問題和性能問題,最終會導致 PCB 出現故障。 采用新型基板和銅

2022-05-07 17:43:37 6107

6107 一站式PCBA智造廠家今天為大家講講PCB電路板設計中有哪些要點?PCB電路板設計中的12要點。

2022-11-03 10:00:58 4632

4632 很多工程師在使用Xilinx開發板時都注意到了一個問題,就是開發板中將LVDS的時鐘輸入(1.8V電平)連接到了VCCO=2.5V或者3.3V的Bank上,于是產生了關于FPGA引腳與LVDS(以及

2023-02-09 09:48:03 5306

5306 多層 PCB 上小信號分立器件的熱行為-AN11076

2023-02-16 20:02:32 0

0 在集成電路應用設計中,項目原理圖設計完成之后,就需要進行PCB布板的設計。PCB設計是一個至關重要的環節。設計結果的優劣直接影響整個設計功能。因此,合理高效的PCB Layout是芯片電路設計調試成功中至關重要的一步。本次我們就來簡單講一講PCB Layout的設計要點

2023-04-27 15:16:40 2238

2238

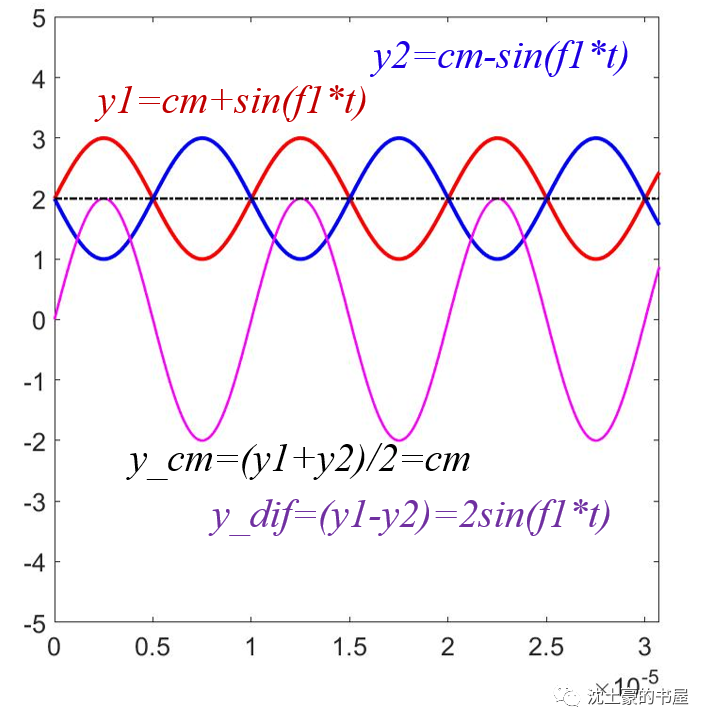

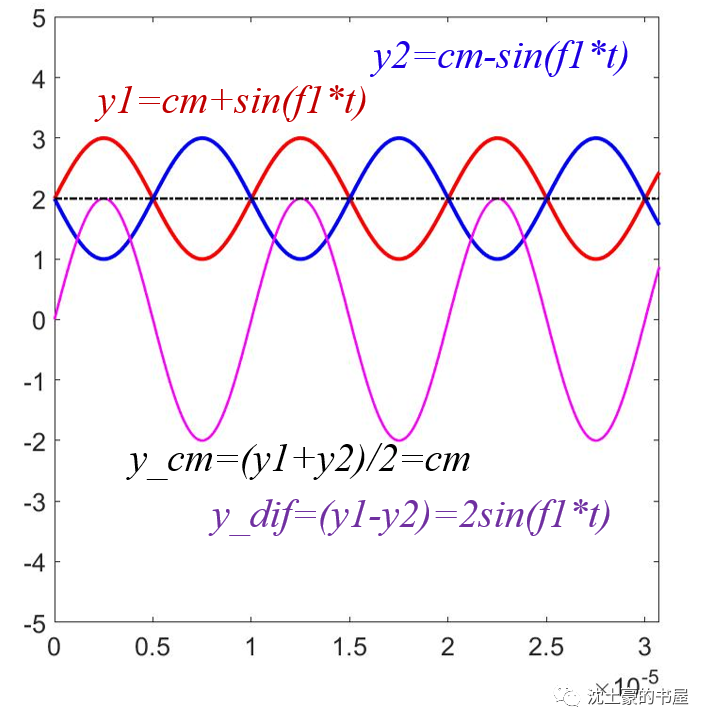

今天聽了下公司analog designer的介紹課程,有一些LVDS在信號上的觀點非常亮,我做了點筆記,跟大家分享一下。

2023-05-25 11:28:20 3046

3046

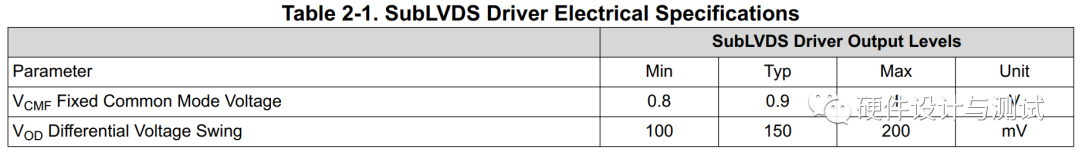

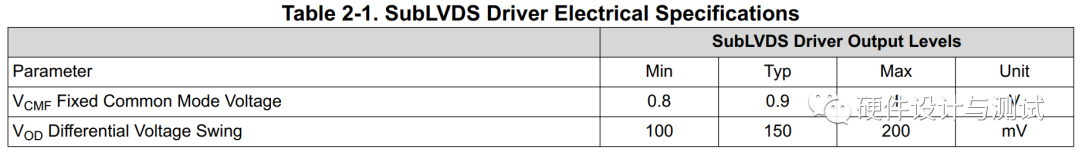

Sub-LVDS是一種低功耗、低誤碼率、低串擾和低輻射的差分信號技術,是LVDS技術在Camera接口上的一種應用。Sub-LVDS采用低擺幅電流模式傳輸系統,同傳統的電壓模式相比較,在達到幾乎相同

2023-09-15 14:47:10 7709

7709

電子發燒友網站提供《PCB布局布線設計要點.pdf》資料免費下載

2023-09-19 15:41:49 18

18 LVDS發送芯片的輸入信號來自主控芯片,輸入信號包含RGB數據信號、時鐘信號和控制信號三大類。

2023-10-17 17:28:13 2680

2680

LVDS傳輸的是什么信號?判斷LVDS信號正常的方法 一、LVDS傳輸的是什么信號? LVDS是一種低電壓差分信號,有兩種電壓狀態,即高電平和低電平,它類似于RS485協議。LVDS信號作為一種數字信號

2023-10-18 15:38:13 7367

7367 什么叫做LVDS信號?請問TTL信號與LVDS信號有什么區別? LVDS信號 LVDS(Low Voltage Differential Signaling)又稱低壓差分信號傳輸技術,是一種采用差分

2023-10-18 15:38:18 4101

4101 組成部分。 由于數據的傳輸速率越來越快,傳統的單端信號傳輸方式不再適用,因為它存在著信號失真、干擾和耗能等問題。而LVDS則是一種差分信號傳輸技術,通過將信號分為正負兩個信號同時傳輸,可以避免上述問題的出現。 在LVDS接口中,時鐘脈沖信號與數據信號是同時傳輸的。時鐘信號用來指示數據信號的

2023-10-18 15:38:20 2319

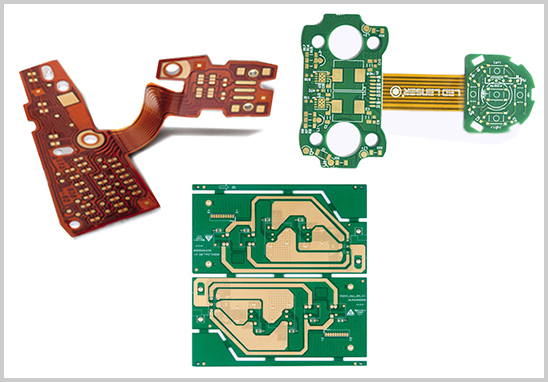

2319 特性與PCB特性的線路板。軟硬結合板在PCB設計上與軟板或者硬板有很多不同,接下來深圳PCBA廠家為大家介紹下軟硬結合板PCB設計要點。 軟硬結合板PCB設計要點 1、撓性區的線路設計要求: 1.1 線路要避免突然的擴大或縮小,粗細線之間采用淚形; 1.2 在符合

2023-11-21 09:35:42 4567

4567

防浪涌時,PCB布線有哪些要點?

2023-12-05 15:34:29 2032

2032

在高速PCB設計中,信號層的空白區域可以敷銅,而多個信號層的敷銅在接地和接電源上應如何分配? 在高速PCB設計中,信號層的空白區域可以敷銅,而多個信號層的敷銅在接地和接電源上應該經過合理分配。接地

2023-11-24 14:38:21 1850

1850 在PCB板上添加散熱孔的方法和要點 散熱孔在PCB板上起著非常重要的作用,它可以有效地提高電子器件的散熱能力,確保電子設備的正常工作。下面,我將詳細介紹在PCB板上添加散熱孔的方法和要點。 一、散熱

2023-12-08 11:42:37 5025

5025 電子發燒友網站提供《低壓差分信號(LVDS)在LED燈墻中的應用.pdf》資料免費下載

2024-08-30 09:23:24 0

0 在PCB設計中,布局是一個非常重要的環節,它直接影響到電路的性能、可靠性和成本。以下是關于PCB布局的一些要點,這些要點將幫助您設計出高質量的PCB。 確定設計目標和要求 在開始布局之前,首先需要

2024-09-02 14:48:49 1284

1284 接口)在多個方面存在顯著差異,同時LVDS接口電路設計也有其特定的技巧。 LVDS接口與HDMI的區別 信號傳輸方式 : LVDS接口采用低壓差分信號傳輸方式,通過兩條PCB走線或一對平衡電纜傳輸差分信號

2024-11-21 16:06:50 4096

4096 高速差分接收器SN65LVDS33和SN65LVDS34:特性、應用與設計要點 在當今高速數據傳輸的時代,差分信號傳輸技術因其抗干擾能力強、傳輸速率高等優點,被廣泛應用于各種電子系統中。德州儀器

2025-12-24 17:40:06 509

509 探索SN65LVDS95-EP LVDS SERDES發射器:特性、應用與設計要點 在電子設計領域,高速數據傳輸和可靠通信一直是工程師們關注的焦點。SN65LVDS95 - EP LVDS

2025-12-30 09:45:06 80

80 高速差分接收器SN65LVDS系列:特性、應用與設計要點 在高速數據傳輸領域,低電壓差分信號(LVDS)技術憑借其高速率、低功耗和抗干擾能力強等優勢,得到了廣泛應用。德州儀器(TI

2025-12-31 11:10:06 138

138 高速差分接收器SN65LVDS/T系列:特性、應用與設計要點 在高速數據傳輸領域,低電壓差分信號(LVDS)技術憑借其高速率、低功耗和抗干擾能力強等優勢,得到了廣泛應用。德州儀器(TI

2025-12-31 11:20:05 133

133 SN65LVDS1050高速差分線驅動器和接收器:特性、應用與設計要點 在高速數據傳輸的領域中,差分信號技術憑借其出色的抗干擾能力和高速傳輸特性,成為了眾多工程師的首選。今天,我們就來深入探討

2026-01-04 10:00:20 85

85 深入剖析SN65LVDS95 LVDS 串行器:特性、應用與設計要點 在高速數據傳輸領域,LVDS(低電壓差分信號)技術憑借其低功耗、高抗干擾能力和高速率傳輸的優勢,成為眾多工程師的首選。TI

2026-01-04 11:10:14 197

197 深入解析SN65LVDS93 LVDS串行器:特性、應用與設計要點 在電子工程師的日常工作中,選擇合適的芯片來實現高效的數據傳輸至關重要。今天,我們就來詳細探討一下德州儀器(TI

2026-01-04 11:15:02 183

183 SN65LVDS96 LVDS SERDES接收器:特性、應用與設計要點 在電子設計領域,數據傳輸的高效性和穩定性至關重要。LVDS(Low-Voltage Differential

2026-01-04 11:15:05 181

181 方案簡介:LVDS 是一種低擺幅的差分信號技術,利用非常低的電壓擺幅(約 350mV)在 2 條 PCB 走線或者一對平衡電纜上通過差分進行數據的傳輸,即低壓差分信號傳輸,采用 LVDS 接口,可以

2023-06-13 10:41:55

電子發燒友App

電子發燒友App

評論