本文轉(zhuǎn)載自: Cadence楷登PCB及封裝資源中心微信公眾號(hào)

本文要點(diǎn)

BGA 封裝尺寸緊湊,引腳密度高。

在 BGA 封裝中,由于焊球排列和錯(cuò)位而導(dǎo)致的信號(hào)串?dāng)_被稱(chēng)為 BGA 串?dāng)_。

BGA 串?dāng)_取決于入侵者信號(hào)和受害者信號(hào)在球柵陣列中的位置。

在多門(mén)和引腳數(shù)量眾多的集成電路中,集成度呈指數(shù)級(jí)增長(zhǎng)。得益于球柵陣列 (ball grid array ,即BGA) 封裝的發(fā)展,這些芯片變得更加可靠、穩(wěn)健,使用起來(lái)也更加方便。BGA 封裝的尺寸和厚度都很小,引腳數(shù)則更多。然而,BGA 串?dāng)_嚴(yán)重影響了信號(hào)完整性,從而限制了 BGA 封裝的應(yīng)用。下面我們來(lái)探討一下 BGA 封裝和 BGA 串?dāng)_的問(wèn)題。

球柵陣列封裝

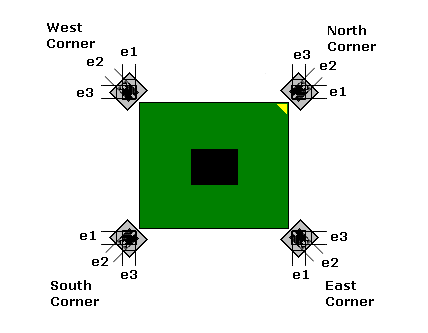

BGA 封裝是一種表面貼裝封裝,使用細(xì)小的金屬導(dǎo)體球來(lái)安裝集成電路。這些金屬球形成一個(gè)網(wǎng)格或矩陣圖案,排列在芯片表面之下,與印刷電路板連接。

球柵陣列 (ball grid array ,即BGA) 封裝。

使用 BGA 封裝的器件在芯片的外圍沒(méi)有引腳或引線(xiàn)。相反,球柵陣列被放置在芯片底部。這些球柵陣列被稱(chēng)為焊球,充當(dāng) BGA 封裝的連接器。

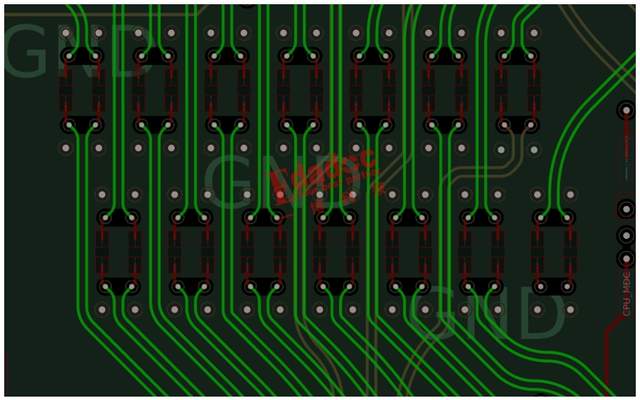

微處理器、WiFi 芯片和 FPGA 經(jīng)常使用 BGA 封裝。在 BGA 封裝的芯片中,焊球令電流在 PCB 和封裝之間流動(dòng)。這些焊球以物理方式與電子器件的半導(dǎo)體基板連接。引線(xiàn)鍵合或倒裝芯片用于建立與基板和晶粒的電氣連接。導(dǎo)電的走線(xiàn)位于基板內(nèi),允許電信號(hào)從芯片和基板之間的接合處傳輸?shù)交搴颓驏抨嚵兄g的接合處。

BGA 封裝以矩陣模式在芯片下分布連接引線(xiàn)。與扁平式和雙列式封裝相比,這種排列方式在 BGA 封裝中提供了更多的引線(xiàn)數(shù)。在有引線(xiàn)的封裝中,引腳被安排在邊界。BGA 封裝的每個(gè)引腳都帶有一個(gè)焊球,焊球位于芯片的下表面。這種位于下表面的排列方式提供了更多的面積,使得引腳數(shù)量增多,阻塞減少,引線(xiàn)短路也有所減少。與有引線(xiàn)的封裝相比,在 BGA 封裝中,焊球之間的排列距離最遠(yuǎn)。

BGA 封裝的優(yōu)點(diǎn)

BGA 封裝尺寸緊湊,引腳密度高。BGA 封裝電感量較低,允許使用較低的電壓。球柵陣列的排列間隔合理,使 BGA 芯片更容易與 PCB 對(duì)齊。

BGA 封裝的其他一些優(yōu)點(diǎn)是:

由于封裝的熱阻低,散熱效果好。

BGA 封裝中的引線(xiàn)長(zhǎng)度比有引線(xiàn)的封裝要短。引線(xiàn)數(shù)多加上尺寸較小,使 BGA 封裝的導(dǎo)電性更強(qiáng),從而提高了性能。

與扁平式封裝和雙列式封裝相比,BGA 封裝在高速下的性能更高。

使用 BGA 封裝的器件時(shí),PCB 的制造速度和產(chǎn)量都會(huì)提高。焊接過(guò)程變得更簡(jiǎn)單、更方便,而且 BGA 封裝可以方便地進(jìn)行返工。

BGA 串?dāng)_

BGA 封裝確實(shí)有一些缺點(diǎn):焊球不能彎曲、由于封裝密度高而導(dǎo)致的檢查難度大,以及大批量生產(chǎn)需要使用昂貴的焊接設(shè)備。BGA 串?dāng)_是另一項(xiàng)限制,會(huì)影響通過(guò) BGA 封裝傳輸?shù)男盘?hào)完整性。

要減少 BGA 串?dāng)_,低串?dāng)_的 BGA 排列至關(guān)重要。

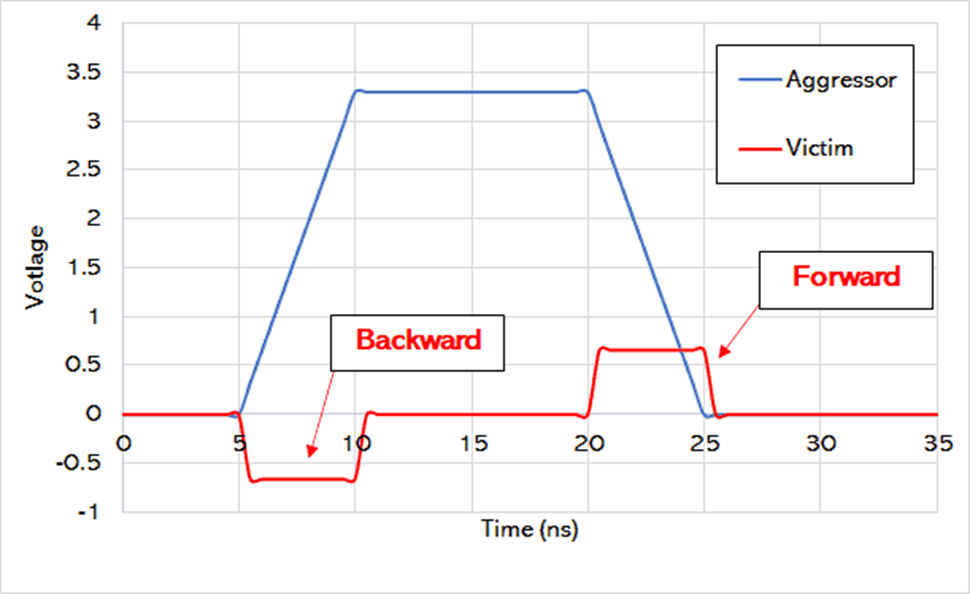

BGA 封裝經(jīng)常在大量 I/O 設(shè)備中使用。采用 BGA 封裝的集成芯片所傳輸和接收的信號(hào),可能會(huì)受到從一個(gè)引線(xiàn)到另一個(gè)引線(xiàn)的信號(hào)能量耦合的干擾。由 BGA 封裝中的焊球排列和錯(cuò)位而導(dǎo)致的信號(hào)串?dāng)_被稱(chēng)為 BGA 串?dāng)_。球柵陣列之間的有限電感是 BGA 封裝中產(chǎn)生串?dāng)_效應(yīng)的原因之一。當(dāng) BGA 封裝引線(xiàn)中出現(xiàn)高 I/O 電流瞬變(入侵信號(hào))時(shí),對(duì)應(yīng)于信號(hào)引腳和返回引腳的球柵陣列之間的有限電感會(huì)在芯片基板上產(chǎn)生電壓干擾。這種電壓干擾導(dǎo)致了信號(hào)突變,并以噪音的形式從 BGA 封裝中傳輸出去,導(dǎo)致串?dāng)_效應(yīng)。

在網(wǎng)絡(luò)系統(tǒng)等應(yīng)用中,具有使用通孔的厚 PCB,如果沒(méi)有采取措施屏蔽過(guò)孔,那么 BGA 串?dāng)_會(huì)十分常見(jiàn)。在這樣的電路中,放置在 BGA 下面的長(zhǎng)通孔會(huì)造成大量的耦合,并產(chǎn)生明顯的串?dāng)_干擾。

BGA 串?dāng)_取決于入侵者信號(hào)和受害者信號(hào)在球柵陣列中的位置。要減少 BGA 串?dāng)_,低串?dāng)_的 BGA 封裝排列至關(guān)重要。借助 Cadence Allegro Package Designer Plus 軟件,設(shè)計(jì)師能夠優(yōu)化復(fù)雜的單裸片和多裸片引線(xiàn)鍵合(wirebond)以及倒裝芯片(flip-chip)設(shè)計(jì);徑向、全角度推擠式布線(xiàn)可解決 BGA/LGA 基板設(shè)計(jì)的獨(dú)特布線(xiàn)挑戰(zhàn);特定的 DRC/DFM/DFA 檢查,更可保障BGA/LGA設(shè)計(jì)一次成功;同時(shí)提供詳細(xì)的互連提取、3D 封裝建模以及兼顧電源影響的信號(hào)完整性和熱分析。

審核編輯 黃宇

-

封裝

+關(guān)注

關(guān)注

128文章

9248瀏覽量

148614 -

Cadence

+關(guān)注

關(guān)注

68文章

1011瀏覽量

146907 -

BGA

+關(guān)注

關(guān)注

5文章

584瀏覽量

51525 -

串?dāng)_

+關(guān)注

關(guān)注

4文章

196瀏覽量

27834

發(fā)布評(píng)論請(qǐng)先 登錄

GT-BGA-2002高性能BGA測(cè)試插座

【EMC技術(shù)案例】顯示屏線(xiàn)束串擾導(dǎo)致CE電流法超標(biāo)的案例

EXCUSE ME,表層的AC耦合電容和PCB內(nèi)層的高速線(xiàn)會(huì)有串擾?

PWM停止輸出,什么原因會(huì)導(dǎo)致這種現(xiàn)象發(fā)生?

隔離地過(guò)孔要放哪里,才能最有效減少高速信號(hào)過(guò)孔串擾?

昊衡科技全新推出——偏振串擾分析儀OLI-P助力保偏光纖系統(tǒng)性能躍升

串擾如何影響信號(hào)完整性和EMI

技術(shù)資訊 I 哪些原因會(huì)導(dǎo)致近端和遠(yuǎn)端串擾?

高速AC耦合電容挨得很近,PCB串擾會(huì)不會(huì)很大……

高速AC耦合電容挨得很近,PCB串擾會(huì)不會(huì)很大……

你知道什么原因會(huì)導(dǎo)致安規(guī)電容損壞嗎?

NEXT(Near-End Crosstalk,近端串擾)

BGA失效分析原因-PCB機(jī)械應(yīng)力是罪魁禍?zhǔn)?/a>

OLI-P——分布式偏振串擾測(cè)量利器

哪些原因會(huì)導(dǎo)致 BGA 串?dāng)_?

哪些原因會(huì)導(dǎo)致 BGA 串?dāng)_?

評(píng)論