定義:信號完整性(Signal Integrity,簡稱SI)是指在信號線上的信號質量。差的信號完整性不是由某一單一因素導致的,而是板級設計中多種因素共同 引起的。當電路中信號能以要求的時序、持續時間和電壓幅度到達接收端時,該電路就有很好的信號完整性。當信號不能正常響應時,就出現了信號完整性問題。

2023-03-02 09:41:06 2281

2281

正式發布2023年10月13日Cadence15年間最具影響力的版本更新之一AllegroX/OrCADX23.1本文要點:掌握信號完整性基礎知識實現良好信號完整性的PCBlayout技術有助于提高

2023-10-21 08:13:07 2810

2810

如何解決信號完整性問題呢?是德科技在向您介紹信號完整性分析基礎知識的同時,我們還向您展示如何使用基本信號完整性(Signal Integrity - SI) 分析技術(例如眼圖、S參數、時域反射計(TDR) 和單脈沖響應)來解決信號完整性問題。

2024-12-25 16:51:35 2655

2655

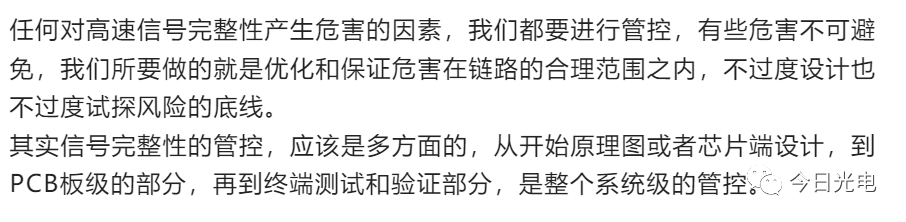

在當今快速發展的數字時代,高速傳輸已成為電子設備的基本要求。隨著數據傳輸速率的不斷提升,信號完整性(Signal Integrity,簡稱SI)問題變得越來越重要。信號完整性是高速互連系統設計的基石

2025-04-24 16:42:33 3620

3620

做了電路設計有一段時間,發現信號完整性不僅需要工作經驗,也需要很強的理論指導,壇友能提供一些信號完整性的視頻資料么?非常感謝!

2019-02-14 14:43:52

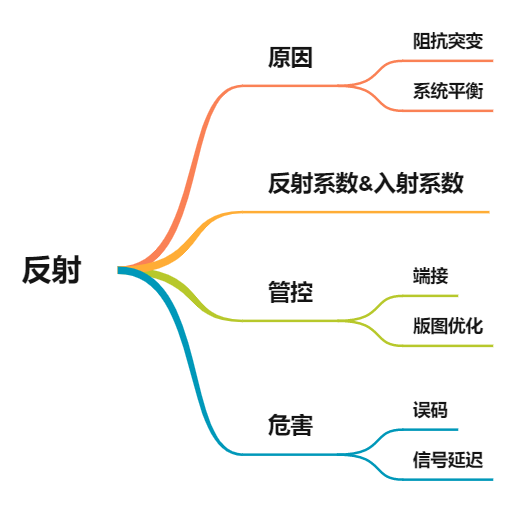

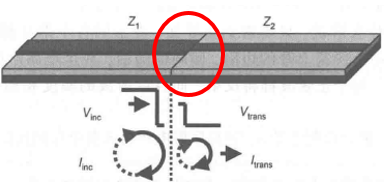

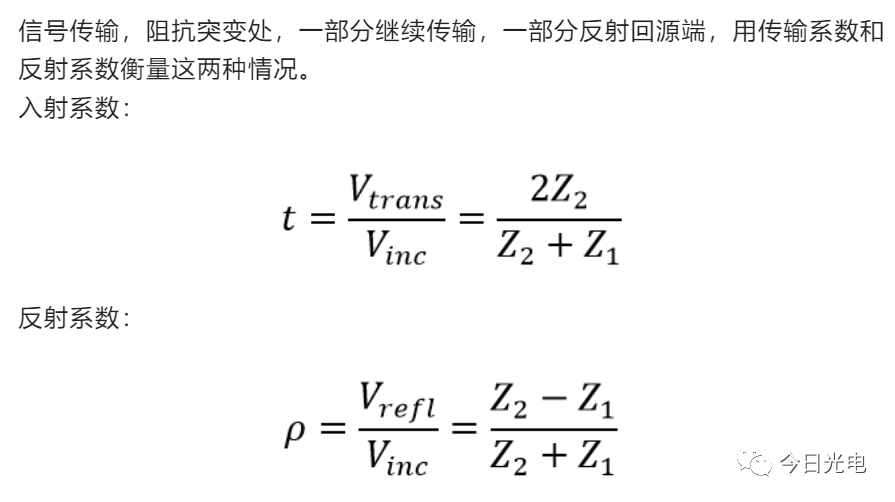

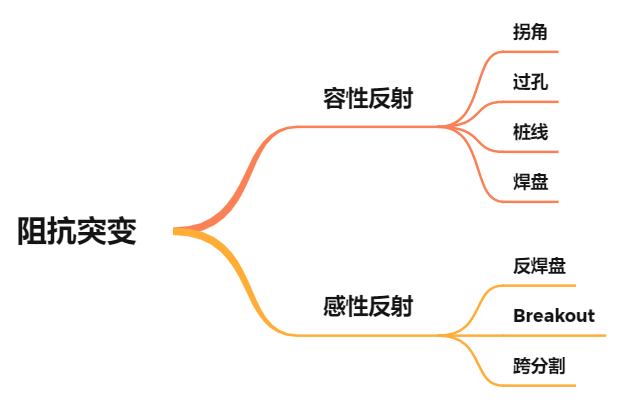

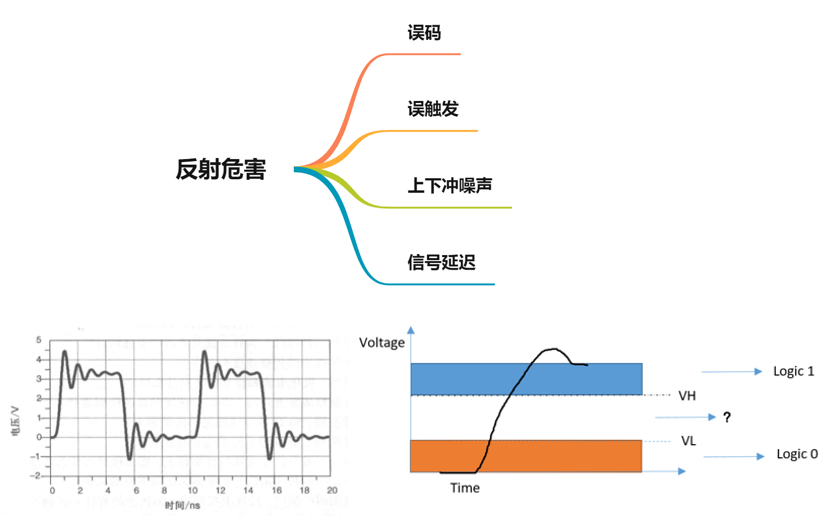

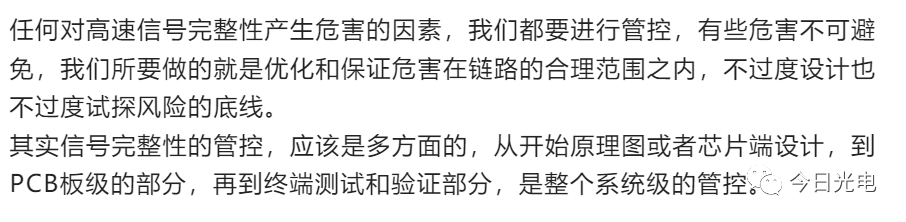

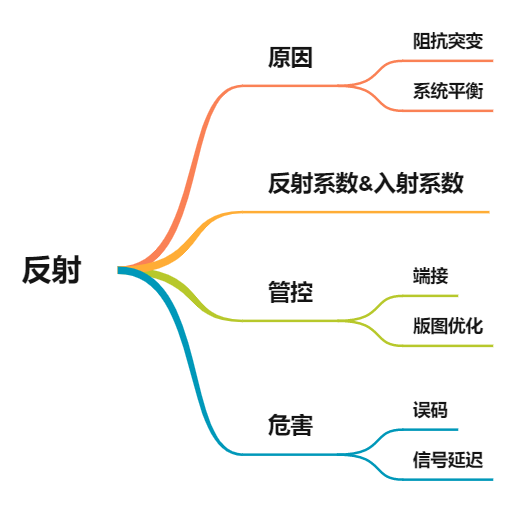

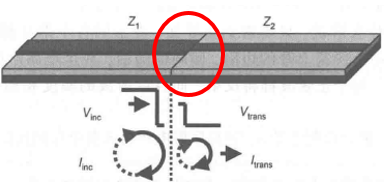

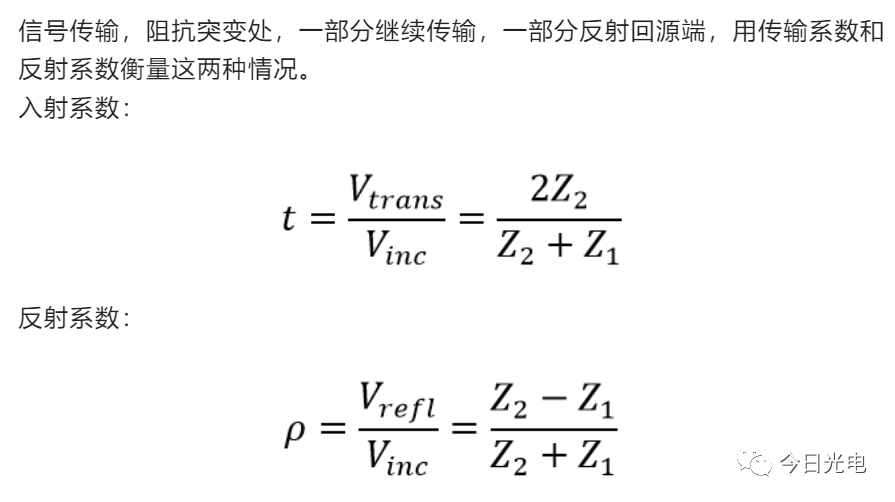

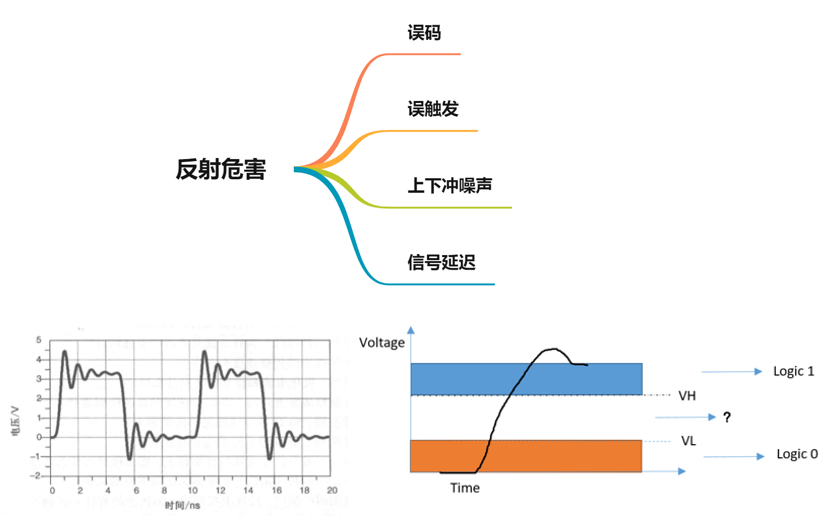

,信號傳播路徑中阻抗發生變化的點,其電壓不再是原來傳輸的電壓。這種反射電壓會改變信號的波形,從而可能會引起信號完整性問題。這種感性的認識對研究信號完整性及設計電路板非常重要,必須在頭腦中建立起這個概念。

2019-05-31 07:48:31

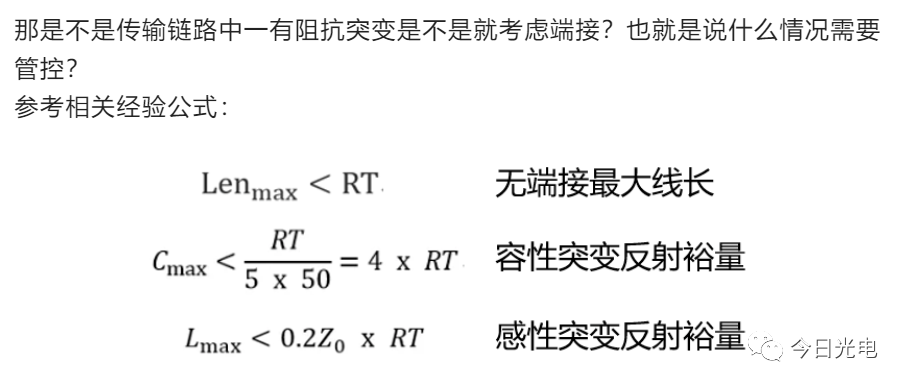

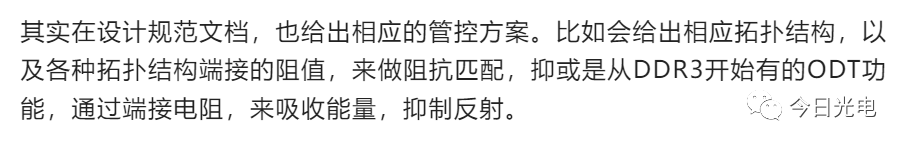

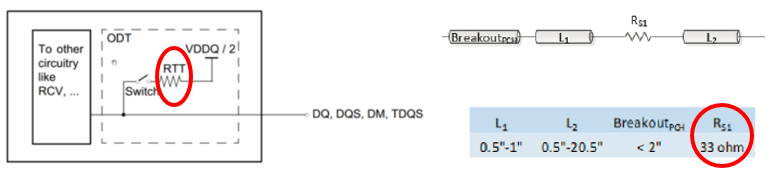

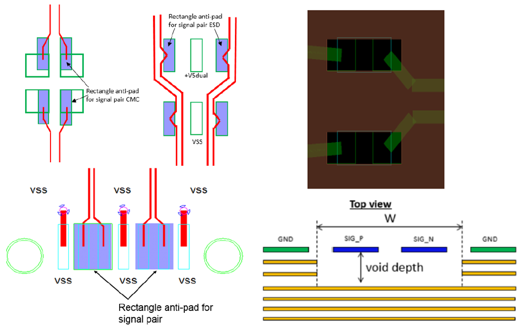

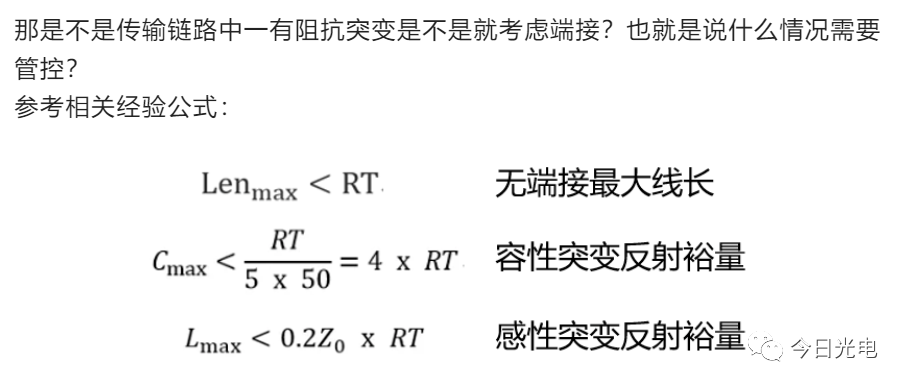

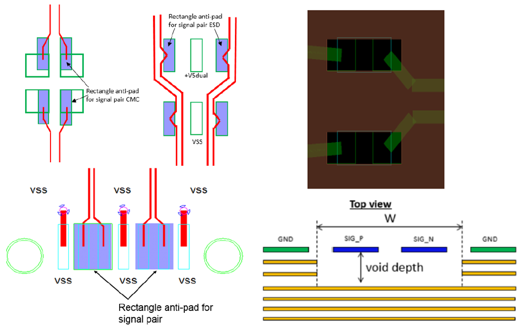

、EMI等問題。 圖1 反射問題示意圖 (2)什么時候需要考慮反射:只有當走線的長度達到高速信號定義時需要考慮反射(信號邊沿小于4~6倍的走線時延)。如果走線很短,產生的反射會被掩蓋在邊沿之中

2023-03-07 16:59:24

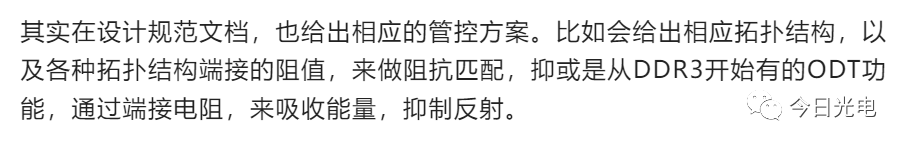

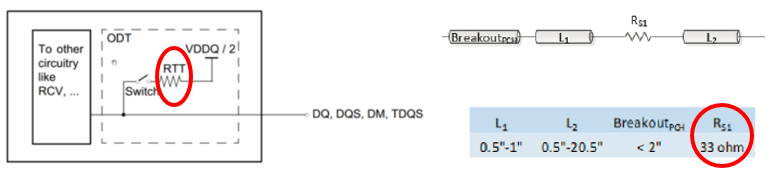

兩個電阻來吸收反射,可以獲得最快的電路性能,適用于高速信號。 a、配置電阻計算公式:Z0=(R1*R2)/(R1+R2) b、通過改變R1和R2的值可以使電壓上偏或者下偏。 c、因為有上下拉,會

2023-03-07 17:13:20

高速設計中的信號完整性和電源完整性分析

2021-04-06 07:10:59

信號完整性與電源完整性的仿真分析與設計,不看肯定后悔

2021-05-12 06:40:35

先說一下,信號完整性為什么寫電源完整性? SI 只是針對高速信號的部分,這樣的理解沒有問題。如果提高認知,將SI 以大類來看,SI&PI&EMI 三者的關系:所以,基礎知識系列里還是

2021-11-15 06:32:45

高速PCB設計有很多比較考究的點,包括常規的設計要求、信號完整性的要求、電源完整性的要求、EMC的要求、特殊設計要求等等。本文主要是針對高速電路信號總線做了一些比較常規的要求列舉了一些檢查要點,其實

2021-01-14 07:11:25

信號完整性資料

2015-09-18 17:26:36

信號完整性分析與設計信號完整性設計背景???什什么是信號完整D??信信號完整性設計內è??典典型信號完整性問題與對2現在數字電路發展的趨ê??速速率越來越???芯芯片集成度越來越高£PC板板越來越

2009-09-12 10:20:03

信號完整性的定義信號完整性包含哪些內容

2021-03-04 06:09:35

信號完整性基礎知識張士賢編寫

2019-04-11 11:28:15

本文主要介紹信號完整性是什么,信號完整性包括哪些內容,什么時候需要注意信號完整性問題?

2021-01-25 06:51:11

最新的高速電路設計與信號完整性分析技術要點;深入講解信號完整性的四類問題:反射(reflection);串擾(crosstalk);電源軌道塌陷(railcollapse);電磁干擾(EMI)。介紹

2010-05-29 13:29:11

高速信號的電源完整性分析在電路設計中,設計好一個高質量的高速PCB板,應該從信號完整性(SI——Signal Integrity)和電源完整性 (PI——Power Integrity )兩個方面來

2012-08-02 22:18:58

最新的高速電路設計與信號完整性分析技術要點;深入講解信號完整性的四類問題:反射(reflection);串擾(crosstalk);電源軌道塌陷(rail collapse);電磁干擾(EMI)。介紹的分析

2010-11-09 14:21:09

高速數字設計和信號完整性

2019-06-11 22:46:02

關于信號完整性與高速電路設計不可多得的好東西。

2015-04-16 19:19:52

高速電路信號完整性分析與設計—信號完整性仿真仿真中有兩類信號可稱之為高速信號:高頻率的信號(>=50M)上升時間tr很短的信號:信號上升沿從20%~80%VCC的時間,一般是ns級或

2009-09-12 10:31:31

高速IC(芯片)、PCB(電路印制板)和系統的核心技術就是微波背景下的互連設計與信號完整性分析。全世界高速高密度電路的發展表明:互連正在取代器件,躍升為高速電路設計的主角。信號完整性分析是高速互連

2010-04-21 17:11:35

。本篇介紹了高速數字硬件電路設計中信號完整性在通常設計的影響。這包括特征阻抗控制、終端匹配、電源和地平面、信號布線和串擾等問題。掌握這些知識,對一個數字電路設計者而言,可以在電路設計的早期,就注意到潛在

2009-10-14 09:32:02

高速數字硬件電路設計中信號完整性在通常設計的影響是什么?高速電路設計中信號完整性面臨的挑戰有哪些?怎么處理?

2021-04-22 06:26:55

高速PCB設計中的信號完整性概念以及破壞信號完整性的原因高速電路設計中反射和串擾的形成原因

2021-04-27 06:57:21

本文分析了高速電路設計中的信號完整性問題,提出了改善信號完整性的一些措施,并結合一個VGA視頻分配器系統的設計過程,具體分析了改善信號完整性的方法。

2021-06-03 06:22:05

本文分析了高速電路設計中的信號完整性問題,提出了改善信號完整性的一些措施,并結合一個VGA視頻分配器系統的設計過程,具體分析了改善信號完整性的方法。

2021-06-04 06:16:07

Cadenc高速電路設計SI PI 信號完整性電源完整性仿真視頻教程下載鏈接地址:鏈接:http://pan.baidu.com/s/1pJiPpzl密碼:3yjv

2015-07-30 21:44:10

確定該電路具有較好的信號完整性。反之,當信號不能正常響應時,就出現了信號完整性問題。 高速PCB的信號完整性問題主要包括信號反射、串擾、信號延遲和時序錯誤。 · 反射:信號在傳輸線上傳輸時,當高速

2018-11-27 15:22:34

VNA是如何測量高速器件的信號完整性(SI)?

2021-05-11 06:49:40

首先我們定義下什么是電源和信號完整性?信號完整性 信號完整性(SI)分析集中在發射機、參考時鐘、信道和接收機在誤碼率(BER)方面的性能。電源完整性(PI)側重于電源分配網絡 (PDN) 提供恒定

2021-12-30 06:33:36

何為信號完整性:信號完整性(Signal Integrity,簡稱SI)是指在信號線上的信號質量。差的信號完整性不是由某一單一因素導致的,而是板級設計中多種因素共同引起的。當電路中信號能以要求的時序

2021-12-30 08:15:58

中,采用Cadence軟件的高速仿真工具SPECCTRAQuest,并利用器件的 IBIS模型來分析信號完整性,對阻抗匹配以及拓撲結構進行優化設計,以保證系統正常工作。本文只對信號反射和串擾進行詳細

2015-01-07 11:30:40

本文介紹了一種基于信號完整性計算機分析的高速數字信號PCB板的設計方法。在這種設計方法中,首先將對所有的高速數字信號建立起PCB板級的信號傳輸模型,然后通過對信號完整性的計算分析來尋找設計的解

2018-08-29 16:28:48

本文介紹了一種基于信號完整性計算機分析的高速數字信號PCB板的設計方法。在這種設計方法中,首先將對所有的高速數字信號建立起PCB板級的信號傳輸模型,然后通過對信號完整性的計算分析來尋找設計的解

2008-06-14 09:14:27

如何保證脈沖信號傳輸的完整性,減少信號在傳輸過程中產生的反射和失真,已成為當前高速電路設計中不可忽視的問題。

2021-04-07 06:53:25

高速數字PCB設計信號完整性解決方法

2021-03-29 08:12:25

高速PCB頻發故障,使得信號完整性問題越來越受到工程師的重視。有關高速PCB信號完整性的相關內容網絡上有很多,這方面的知識點很容易找到資源學習,我本人也寫過一本拙作《信號完整性揭秘》。但是,學習理論知識

2017-06-23 11:52:11

高速電路信號完整性分析之應用篇

2006-05-28 01:00:47 0

0 摘要! 介紹了高速+,& 設計中的信號完整性概念以及破壞信號完整性的原因!從理論和計算的層面上分析了高速電路設計中反射和串擾的形成原因!并介紹了-&-. 仿真"關鍵詞!

2008-10-15 08:15:02 0

0 高速電路信號完整性分析與設計—阻抗控制:阻抗控制目的為了最小化反射的負面影響,一定要有解決辦法去控制它們。本質上,有三個方法可以減輕反射的負面影響。

2009-10-06 11:18:14 0

0 高速電路信號完整性分析與設計—信號完整性仿真:仿真信號仿真中有兩類信號可稱之為高速信號:高頻率的信號(>=50M)上升時間tr很短的信號:信號上

2009-10-06 11:19:50 0

0 高速數字電路信號完整性分析與設計:信號完整性概述 傳輸線理論 PCB阻抗控制 拓撲與端接技術 時序計算 串擾與對策

2009-10-06 11:25:17 0

0 高速并行總線信號完整性測試技術:隨著信號速度的顯著提高,信號完整性問題已經成為高速數字設計中的關鍵。本文介紹了一種新的信號完整性分析技術,通過集成邏輯分析儀和

2009-10-17 17:11:55 0

0 信號完整性原理分析

什么是“信號完整性”?在傳統的定義中“完整性(integrity)”指完整和末受損的意思。因此,具有良好完整性的數字信號應是干凈,

2009-11-04 12:07:06 212

212 什么是信號完整性

信號完整性(Signal Integrity):就是指電路系統中信號的

2009-06-30 10:23:18 5717

5717

為了使設計人員對信號完整性與電源完整性有個全面的了解,文中對信號完整性與電源完整性的問題進行了仿真分析與設計,也從系統的角度對其進行了探討。

2011-11-30 11:12:24 0

0 本專題詳細介紹了信號完整性各部分知識,包括信號完整性的基礎概述,信號完整性設計分析及仿真知識,還有具體應用中的一些小經驗分享等等,充分翔實的向大家描述了信號完整性。

2011-11-30 11:44:35

目錄 1. 緒論 1.1 問題的提出 1.2 國內外研究現狀及動態 1.3 本書主要內容 2. 高速信號完整性的基本理論 2.1 基本電磁理論 2.2 高速電路的基本知識 2.3 信號完整性的基本概念 3 高速邏輯電

2012-05-25 15:50:35 1346

1346 2.1 基本電磁理論 本書主要討論高速數字電路中信號完整性分析與高速電路設計的基本方法,而信號完整性分析是以電磁場理論作為基本理論,因此必須首先討論高速信號完整性所涉及

2012-05-25 16:26:07 102

102 2.1 基本電磁理論 本書主要討論高速數字電路中信號完整性分析與高速電路設計的基本方法,而信號完整性分析是以電磁場理論作為基本理論,因此必須首先討論高速信號完整性所涉及

2012-05-25 16:21:42 2037

2037 高速數字信號的反射是影響現代數字電路設計的重要因素之一,嚴重的反射將破壞信號的完整性,并引起過沖現象,從而出現錯誤的數字邏輯和毀壞器件。本章詳細分析了信號反射產生機理

2012-05-25 16:40:56 155

155 高速數字信號的反射是影響現代數字電路設計的重要因素之一,嚴重的反射將破壞信號的完整性,并引起過沖現象,從而出現錯誤的數字邏輯和毀壞器件。本章詳細分析了信號反射產生機理

2012-05-25 16:41:11 7556

7556 在電路設計中,設計好一個高質量的高速PCB板,應該從信號完整性(SISignal Integrity)和電源完整性 (PIPower Integrity )兩個方面來考慮。盡管從信號完整性上表現出來的結果較為直接,但是信

2012-05-29 14:12:10 0

0 在電路設計中,設計好一個高質量的高速PCB板,應該從信號完整性(SISignal Integrity)和電源完整性 (PIPower Integrity )兩個方面來考慮。盡管從信號完整性上表現出來的結果較為直接,但是信

2012-05-29 13:51:26 3033

3033 信號完整性分析基礎知識——很不錯的學習內容

2016-01-06 14:35:06 0

0 Avago Technologies信號完整性分析基礎知識

2016-06-01 17:48:06 0

0 介紹信號完整性的四個方面,EMI,串擾,反射,電源等。

2016-08-29 15:02:03 0

0 高速信號完整性測試和驗證技術

2017-01-14 02:53:59 26

26 描述了高速PCB電路板信號完整性設計方法。 介紹了信號完整性基本理論, 重點討論了如何采用高速PCB設計方法保證高速數采模塊的信號完整性

2017-11-08 16:55:13 0

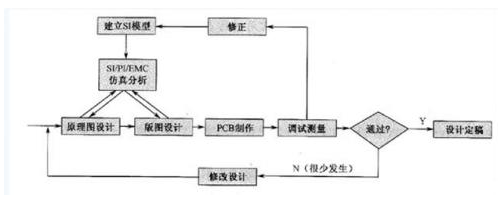

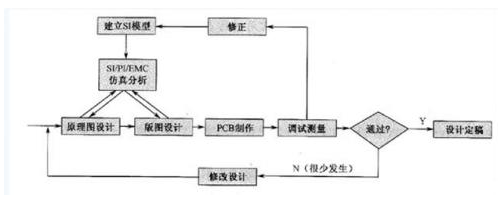

0 高速數字系統中,對于頻率達到百兆甚至CHz以上的信號,會由于系統的信號完整性的問題而導致信號質量不佳。甚至對于不到50 MHz的信號,由于其電平跳變時間在Ins甚至ps級,最終PCB產品中依然有可能會m現信號完整性問題。 為了縮短開

2017-11-09 16:24:32 13

13 信號完整性(Signal Integrity Signal Integrity,簡稱SI SI)是指在信號線上的信號質量。差的信號完整性不是由某一單一 因素導致的,而是板級設計中多種因素共同

2017-11-16 13:24:51 0

0 隨著第三代I/O技術的出現,人們開始步入高速傳輸的時代。在使用PCI Express、SATA等高速串行總線時,如何保持信號的完整性是一個挑戰。本文結合實例,介紹信號完整性驗證的基礎知識和方法。

2018-02-26 15:36:24 2784

2784

高速 PCB 信號完整性仿真分析.pdf

2018-05-07 14:52:31 52

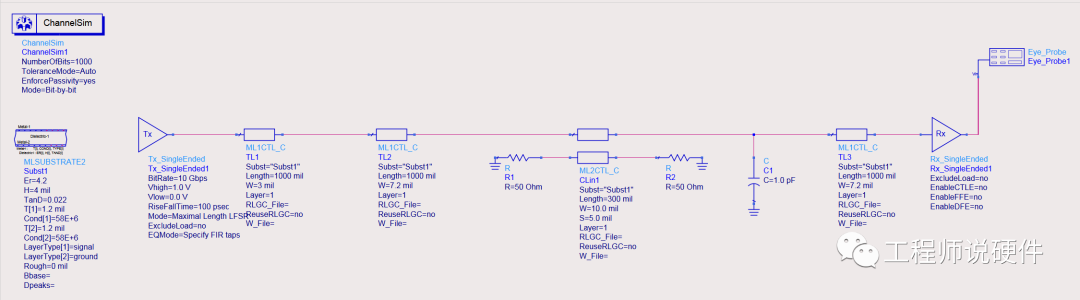

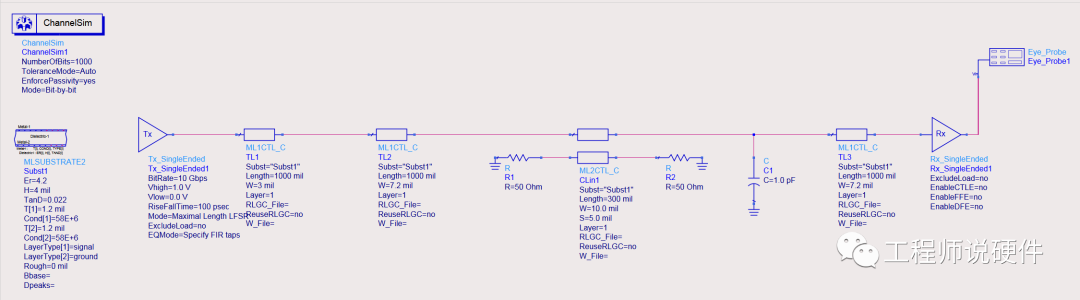

52 借助功能強大的Cadence公司SPEECTRAQuest仿真軟件,利用IBIS模型,對高速信號進行信號完整性仿真分析是一種高效可行的分析方法,可以發現信號完整性問題,根據仿真結果在信號完整性相關問題上做出優化的設計,從而達到提高設計質量,縮短設計周期的目的。

2019-05-20 15:25:37 1542

1542

(1)因為整個設計流程是基于信號完整性分析的,所以在進行PCB設計之前,必須建立或獲取高速數字信號傳輸系統各個環節的信號完整性模型。

(2)在設計原理圖過程中,利用信號完整性模型對關鍵網絡進行信號完整性預分析,依據分析結果來選擇合適的元器件參數和電路拓撲結構等。

2019-10-11 14:52:33 2515

2515

我們在介紹信號完整性的時候通常會說“當傳輸延時大于六分之一的信號的上升時間時,需要考慮信號完整性問題”,于是乎教科書里面都會配上一副類似于這樣表現上升時間或者傳輸延時與反射的圖片: 最開始的時候小陳

2021-04-13 09:46:29 3365

3365

本文主要介紹信號完整性是什么,信號完整性包括哪些內容,什么時候需要注意信號完整性問題?

2021-01-20 14:22:53 2344

2344

本文主要介紹信號完整性是什么,信號完整性包括哪些內容,什么時候需要注意信號完整性問題?

2021-01-23 08:45:50 28

28 本文主要介紹信號完整性是什么,信號完整性包括哪些內容,什么時候需要注意信號完整性問題?

信號完整性是指高速產品設計中由互連線引起的所有問題。包括以下幾部分:

時序

噪聲

電磁干擾(EMI

2021-01-26 09:28:30 12

12 電源分配網絡設計是高速數字系統設計的核心,其直接影響到了電源完整性、信號完整性和電磁完整性等系統的性能。本論文著重研究高速數字系統的電源分配網絡設計與電源完整性分析這一主題,并探討了與之緊密聯系

2021-04-21 09:58:06 0

0 信號完整性與電源完整性的仿真(5V40A開關電源技術參數)-信號完整性與電源完整性的仿真分析與設計!!!

2021-09-29 12:11:21 91

91 介紹了高速PCB設計中的信號完整性概念以及破壞信號完整性的原因,從理論和計算的層面上分析了高速電路設計中反射和串擾的形成原因,并介紹了IBIS仿真。

2021-12-17 13:47:07 1

1 高速電路信號完整性分析與設計—調試技巧

2022-02-10 13:56:45 7

7 高速電路信號完整性分析與設計 —阻抗控制

2022-02-10 16:36:42 0

0 高速電路信號完整性分析與設計—端接與拓撲

2022-02-10 16:38:28 0

0 高速電路信號完整性分析與設計—時序計算

2022-02-10 17:16:41 0

0 高速電路信號完整性分析與設計—串擾

2022-02-10 17:23:04 0

0 高速電路信號完整性分析與設計—信號完整性仿真

2022-02-10 17:29:52 0

0 高速電路信號完整性分析與設計—PCB設計1

2022-02-10 17:31:51 0

0 高速電路信號完整性分析與設計—PCB設計2

2022-02-10 17:34:49 0

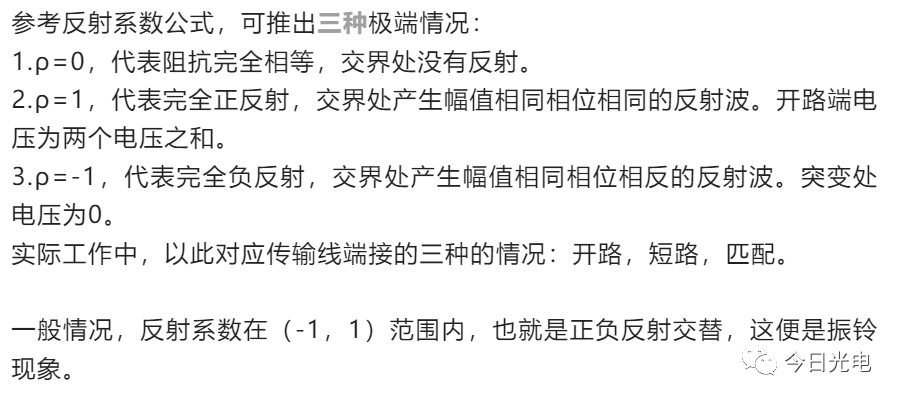

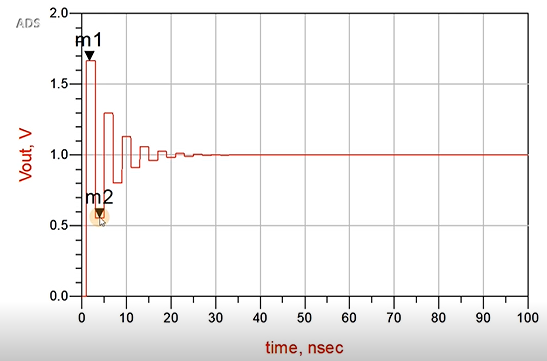

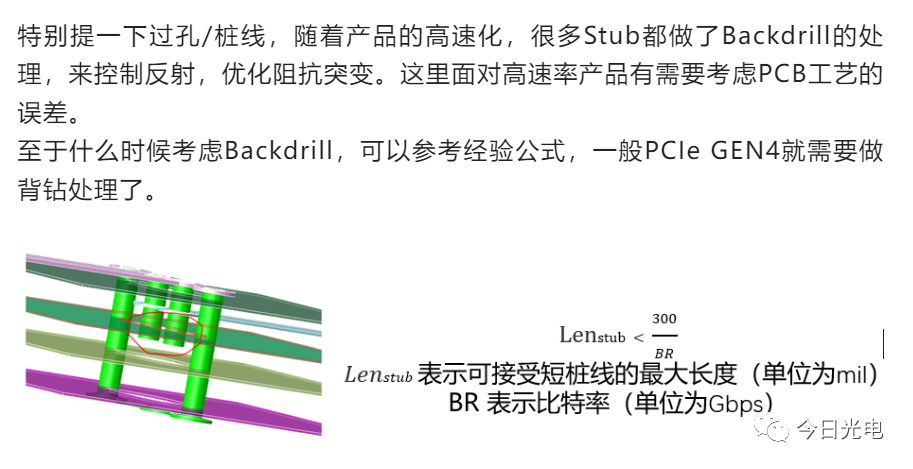

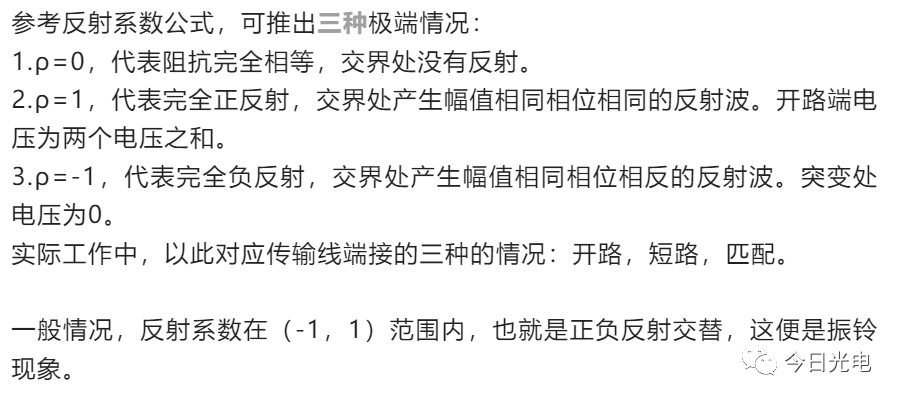

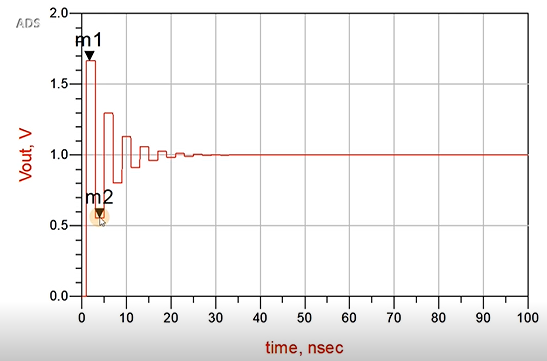

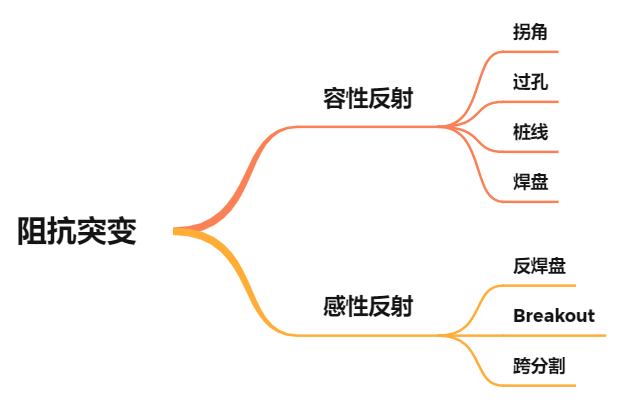

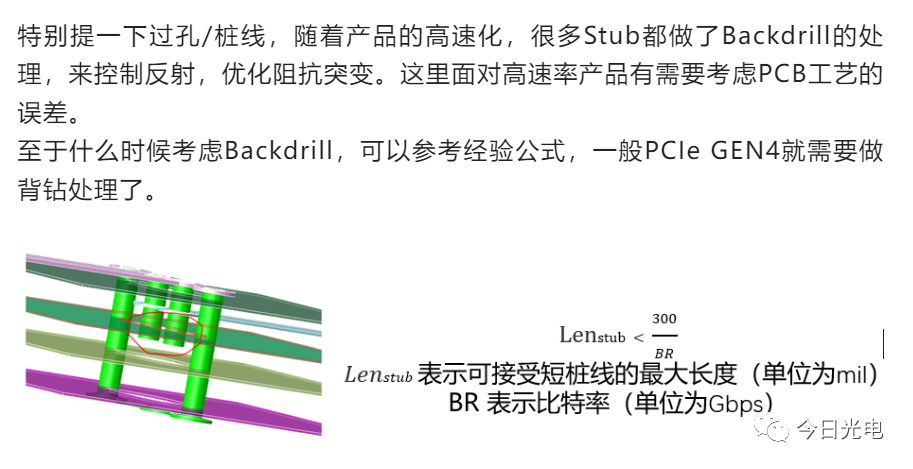

0 信號沿互連線傳播時,如果感受到的瞬態阻抗發生變化,則一部分信號被反射回源端,另一部分信號發生失真并且繼續向負載端傳輸過去。這是單一信號網絡中信號完整性主要的問題。反射和失真會導致信號質量下降,例如振鈴。過強的振鈴會超過邏輯電平的閾值,造成誤觸發。

2023-04-15 15:50:38 2978

2978

本章我們開始《信號完整性基礎》 系列第四章節S參數相關知識的講解。 S參數能反映在頻域范圍內傳輸信號、反射信號的特性,是我們在做PCB SI仿真時最常用的手段。

2023-05-05 12:26:59 8167

8167

隨著現代電子產品的快速發展,高速連接器LM393越來越廣泛地應用于各種領域。高速連接器的信號完整性分析是確保高速數據傳輸的關鍵之一。本文將介紹如何通過使用仿真工具和適當的測試方法來實現高速連接器信號完整性分析。

2023-06-04 14:30:00 2882

2882 小的成本,快的時間使產品達到波形完整性、時序完整性、電源完整性的要求;我們知道:電源不穩定、電源的干擾、信號間的串擾、信號傳輸過程中的反射,這些都會讓信號產生畸變,

2023-08-17 09:29:30 8717

8717

pcb信號完整性詳解 隨著電子領域技術日新月異的發展,高速電路已經成為了電路設計的重要領域之一。在高速電路中,信號完整性顯得尤為重要。在設計PCB電路時,信號完整性是一個必須考慮的因素。那么

2023-09-08 11:46:58 2269

2269 串擾和反射影響信號的完整性? 串擾和反射是影響信號傳輸完整性的兩個主要因素。在深入討論之前,首先需要了解信號傳輸的基本原理。 在通信系統中,信號通常被傳輸通過各種類型的傳輸媒介,例如電纜、光纖或

2023-11-30 15:21:55 1145

1145 ses信號完整性(SI)和電源完整性(PI)是PCB設計的關鍵,無論板速如何。仿真和指導原則雖有幫助,但難以覆蓋所有風險點。于博士的課程將系統化信號完整性設計,通過核心知識點和實際案例,提供清晰

2024-08-30 12:29:32 1092

1092

電子發燒友網站提供《高速PCB的信號完整性、電源完整性和電磁兼容性研究.pdf》資料免費下載

2024-09-19 17:37:43 1

1 電子發燒友網站提供《高速PCB信號完整性分析及應用.pdf》資料免費下載

2024-09-21 14:14:34 7

7 高速PCB信號完整性設計與分析

2024-09-21 11:51:47 4

4 的信號完整性設計已經成為系統設計能否成功的主要因素,同時電源完整性和電磁兼容問題對高速電路的設計影響很大甚至至關重要。本文研究了信號完整性的重要相關領域,其分析研究結果對高速電路系統的設計有重要的指導意義

2024-09-25 14:46:43 3

3 高速電路中的信號完整性和電源完整性研究

2024-09-25 14:44:38 0

0 高速高密度PCB信號完整性與電源完整性研究

2024-09-25 14:43:20 5

5 2024年12月20日14:00-16:00中星聯華科技將舉辦“高速信號完整性分析與測試”-“碼”上行動系列線上講堂線上講堂。本期會議我們將為大家介紹高速串行總線傳輸基本框架,什么是信號完整性?高速

2024-12-15 23:33:31 1134

1134

信號完整性揭秘-于博士SI設計手記4.4有限上升時間信號的反射波形從上一節討論中我們知道,阻抗不連續的點處,反射信號是人射信號的一個副本,并討論了上升時間為0的信號的反射情況。這些規律對于上升時間

2025-08-01 08:37:38 768

768

電子發燒友App

電子發燒友App

硬聲App

硬聲App

2281

2281

2810

2810

2655

2655

3620

3620

0

0 0

0 0

0 0

0 212

212 0

0

1346

1346 102

102 2037

2037 155

155 7556

7556 0

0 3033

3033 0

0 13

13 0

0 2784

2784

1542

1542

2515

2515

3365

3365

12

12 0

0 1

1 2978

2978

8167

8167

2882

2882 8717

8717

2269

2269 1145

1145 1092

1092

3

3 1134

1134

768

768

評論