電路板制板可測試性的定義可簡要解釋為:電路板測試工程師在檢測某種元件的特性時應該盡可能使用最簡單的方法來測試,以確定該元件能是否到達預期的功能需求

2010-07-10 10:27:39 1522

1522 可測試性定義為:產(chǎn)品能及時準確地確定其狀態(tài),隔離其內(nèi)部故障的設計特性,以提高產(chǎn)品可測試性為目的而進行的設計被稱為可測試性設計。

2014-12-18 16:31:25 932

932 專用 測試引線 配用

2024-03-14 23:23:28

現(xiàn)場測試 灌溉測試儀套件

2024-03-14 22:12:01

絕緣 電信 測試夾 塑料

2024-03-14 20:37:40

測試點/測試插座/測試插針

2023-03-30 17:34:49

測試環(huán) 磷青銅 鍍銀 綠色

2023-03-30 17:34:53

3 線電路測試器 測試3線電路和接地連通性

2024-03-14 20:33:47

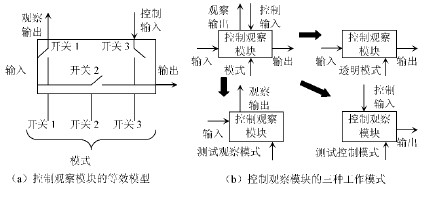

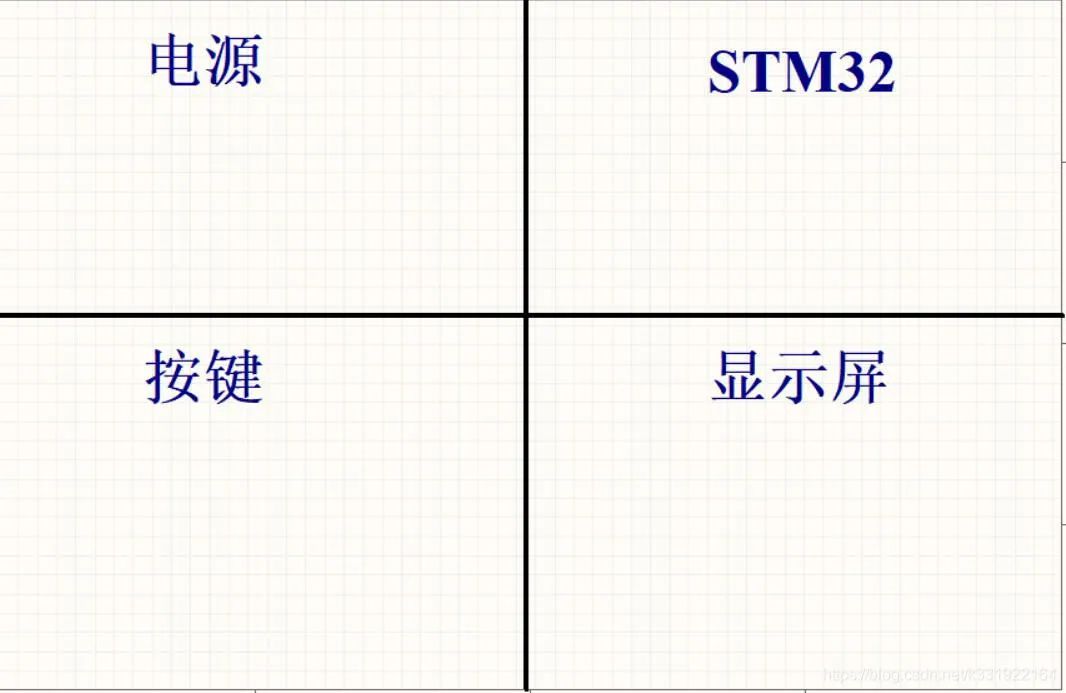

DFT:全稱是 Design for Test,可測性設計,通過在芯片原始設計中插入各種用于提高芯片可測試性(包括可控制性和可觀測性)的硬件邏輯,從而使芯片變得容易測試,大幅度節(jié)省芯片測試的成本

2021-07-23 07:28:32

DFT是什么?DFT在芯片設計領域的含義,即可測性設計(Design for Test), 可測試性設計(Design for Test,簡稱DFT)是電路和芯片設計的重要環(huán)節(jié),它通過在芯片原始

2012-01-11 14:33:22

DFT是什么?DFT在芯片設計領域的含義,即可測性設計(Design for Test), 可測試性設計(Design for Test,簡稱DFT)是電路和芯片設計的重要環(huán)節(jié),它通過在芯片原始

2012-01-11 14:28:06

多線纜 纜線測試器

2024-03-14 20:36:43

削弱以至于消失,電路和系統(tǒng)的可測試性急劇下降,測試成本在電路和系統(tǒng)總成本中所占的比例不斷上升,常規(guī)測試方法正面臨著日趨嚴重的測試困難。PCB可測試性設計技術要概述在電路的邏輯設計完成后,通常是以手工

2018-09-19 16:17:24

更多的附加價值。為了順利地實施這些措施,在產(chǎn)品科研開發(fā)階段,就必須有相應的考慮。1、什么是可測試性 可測試性的意義可理解為:測試工程師可以用盡可能簡單的方法來檢測某種元件的特性,看它能否滿足預期

2014-11-19 11:47:21

產(chǎn)品設計的可測試性(De sign For Testability. OFT) 也是產(chǎn)品可制造性的主要內(nèi)容從生產(chǎn)角度考慮也是設計的工藝性之一。它是指在設計時考慮產(chǎn)品性能能夠檢測的難易程度,也就是說

2016-07-28 10:08:06

測試引線和探針 壽命:10000次

2024-06-26 13:39:26

測試元件 LCR 測試儀

2024-03-14 21:39:21

測試元件 LCR 測試儀

2024-03-14 21:39:21

測試元件 LCR 測試儀

2024-03-14 21:39:21

測試點/測試插座/測試插針 4Pin H7.00mm 12.00 x 2.50mm 黃銅

2023-09-18 18:32:58

測試點/測試插座/測試插針 2Pin H9.50mm 6.65 x 2.50mm Brass

2023-09-18 18:32:58

dft可測試性設計,前言可測試性設計方法之一:掃描設計方法可測試性設計方法之二:標準IEEE測試訪問方法可測試性設計方法之三:邏輯內(nèi)建自測試可測試性設計方法之四:通過MBIST測試寄存器總結...

2021-07-22 09:10:42

可掃描觸發(fā)器的作用有哪些?標準IEEE測試訪問方法主要有哪些應用領域?可測試性設計方法有哪幾種?分別有哪些優(yōu)點?

2021-08-09 07:23:28

什么是可測試性?為什么要發(fā)展測試友好技術?如何去改進可測試性?

2021-04-13 06:54:39

如何改進電路設計規(guī)程來提高可測試性?

2021-04-26 06:49:51

什么是可測試性?就是你這個軟件模塊/函數(shù)接口寫完之后,可以較為方便、較為全面地進行自測 。

這里舉個簡單的例子,認識一下可測試性軟件。

有一個計算函數(shù)cal_func,其計算依賴于存在flash

2025-12-02 06:06:08

改進PCB電路設計規(guī)程提高可測試性隨著微型化程度不斷提高,元件和布線技術也取得巨大發(fā)展,例如BGA外殼封裝的高集成度的微型IC,以及導體之間的絕緣間距縮小到0.5mm,這些僅是其中的兩個

2017-11-06 09:11:17

改進PCB電路設計規(guī)程提高可測試性隨著微型化程度不斷提高,元件和布線技術也取得巨大發(fā)展,例如BGA外殼封裝的高集成度的微型IC,以及導體之間的絕緣間距縮小到0.5mm,這些僅是其中的兩個

2017-11-06 10:33:34

可接觸的電路節(jié)點越來越少;二是像在線測試( In-Circuit-Test )這些方法的應用受到限制。為了解決這些問題,可以在電路布局上采取相應的措施,采用新的測試方法和采用創(chuàng)新性適配器解決方案

2015-01-14 14:34:27

改進電路設計規(guī)程提高可測試性 隨著微型化程度不斷提高,元件和布線技術也取得巨大發(fā)展,例如BGA外殼封裝的高集成度的微型IC,以及導體之間

2009-05-24 23:01:19

This paper addresses testability considerations, both physical and logical, and focuses on both the new constraints and the new freedoms of modern manufacturing test in the ever-changing challenge.

2019-07-17 08:22:14

電路板制板可測試性的定義可簡要解釋為:電路板測試工程師在檢測某種元件的特性時應該盡可能使用最簡單的方法來測試,以確定該元件能是否到達預期的功能需求。進一步含義即: 1 檢測產(chǎn)品是否符合技術規(guī)范

2018-09-14 16:25:59

電路板改板設計中的可測試性技術電路板制板可測試性的定義可簡要解釋為:電路板測試工程師在檢測某種元件的特性時應該盡可能使用最簡單的方法來測試,以確定該元件能是否到達預期的功能需求。進一步含義即:麥|斯

2013-10-09 10:57:40

本帖最后由 gk320830 于 2015-3-4 13:43 編輯

電路板設計可測試性技術電路板制板可測試性的定義可簡要解釋為:電路板測試工程師在檢測某種元件的特性時應該盡可能使用最簡單

2013-10-08 11:26:12

本帖最后由 gk320830 于 2015-3-7 13:19 編輯

電路板設計可測試性技術電路板制板可測試性的定義可簡要解釋為:電路板測試工程師在檢測某種元件的特性時應該盡可能使用最簡單

2013-10-16 11:41:06

電路板制板可測試性的定義可簡要解釋為:電路板測試工程師在檢測某種元件的特性時應該盡可能使用最簡單的方法來測試,以確定該元件能是否到達預期的功能需求。進一步含義即: 1 檢測產(chǎn)品是否符合技術規(guī)范

2018-11-27 10:01:40

隨著電子電路集成度的提高,電路愈加復雜,要完成一個電路的測試所需要的人力和時間也變得非常巨大。為了節(jié)省測試時間,除了采用先進的測試方法外,另外一個方法就是提高設計本身的可測試性。其中,可測試性包括

2011-12-15 09:32:30

Discusses the impact of adding logic analysis testability to PCB's. Examples of today's logic analyzer probing solutions are presented and the advantages and disadvantages of each solution are discussed.

2019-07-26 17:04:50

近年來出現(xiàn)的離散事件系統(tǒng)(DES)理論為數(shù)模混合電路的測試提供了一種新的解決思路,本文對DES 理論在求取數(shù)模混合電路的可測試性和最小測試集中的應用進行了論述。該種方

2009-05-31 16:12:44 28

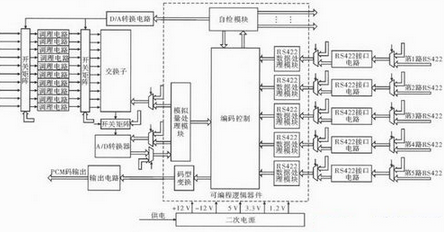

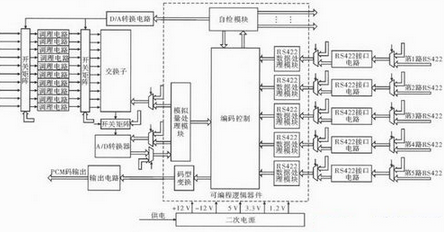

28 為解決某導彈自動測試系統(tǒng)軟件測試難度大的問題,介紹了常用提高軟件可測試性的方法和DLL技術。并運用COM技術設計出該系統(tǒng)的組件軟件,顯著提高了自動測試系統(tǒng)軟件的可測試

2009-06-01 11:55:43 9

9 從分析故障診斷與測試性的異同出發(fā),描述了可測試性設計的重要性及從設計角度而言的優(yōu)缺點,介紹了可測試性設計工作的目標和主要內(nèi)容,闡述了可測試性設計預計的基本原則

2009-12-12 15:08:56 16

16 摘 要 :可測試性設計(Design-For-Testability,DFT)已經(jīng)成為芯片設計中不可或缺的重要組成部分。它通過在芯片的邏輯設計中加入測試邏輯提高芯片的可測試性。在高性能通用CPU的設

2010-09-21 16:47:16 54

54 如何改進電路設計規(guī)程提高可測試性

隨著微型化程度不斷提高,元件和布線技術也取得巨大發(fā)展,例如BGA外殼封裝的高集成

2009-03-25 11:35:35 599

599 如何提高電路可測試性

隨著電子產(chǎn)品結構尺寸越來越小,目前出現(xiàn)了兩個特別引人注目的問題︰一是可接觸的電路節(jié)點越來越少;二是像

2009-04-07 22:25:31 935

935 什么是可測試性

可測試性的意義可理解為:測試工程師可以用盡可能簡單的方法來檢測某種元件的特性,看它能否滿足預期的

2009-05-16 20:40:26 3392

3392 電路板改板設計中的可測試性技術

電路板制板可測試性的定義可簡要解釋為:電路板測試工程師在檢測某種元件的特性時應該盡可能使用最簡單的方法來測試,以確定

2010-01-23 11:22:50 587

587 DFT:數(shù)字電路(fpga/asic)設計入門之可測試設計與可測性分析,離散傅里葉變換,(DFT)Direct Fouriet Transformer

可測試性技術(Design For Testability-

2010-06-07 11:00:48 31566

31566 本文在綜述基本的VLSI測試方法和可測試性設計技術的基礎上,對基于核的片上系統(tǒng)的可測試性設計和測試方法進行簡單介紹。最后,通過分析集成電路設計和制造工藝的發(fā)展給測試帶來

2011-05-28 16:19:29 44

44 本文將探討小器件CDM測試的難處,并提出一些已經(jīng)嘗試用于使用場致CDM測試方法改善小器件可測試性的構想。

2011-09-08 10:55:31 2878

2878 現(xiàn)今流行的可測試性設計(DFT:Design For Testability)為保證芯片的良品率擔任著越來越重要的角色。

2012-04-20 09:39:05 8138

8138

可測試設計(DFT)是適應集成電路的發(fā)展要求所出現(xiàn)的一種技術,主要任務是對電路的結構進行調(diào)整,提高電路的可測性,即可控制性和可觀察性。

2012-04-27 11:11:59 3787

3787

本內(nèi)容介紹了DFT可測試性設計的相關知識,并列舉了3中常見的可測性技術供大家學習

2012-05-30 16:42:27 9453

9453 產(chǎn)品可測試性設計是否滿足測試性要求需要進行測試性分析和評估,基于模型的測試性分析評估方法因為它獨特的優(yōu)勢被廣泛用于產(chǎn)品測試性輔助分析之中。針對多層次系統(tǒng)產(chǎn)品的結構

2013-01-18 17:32:32 0

0 2013-03-14 09:56:29 0

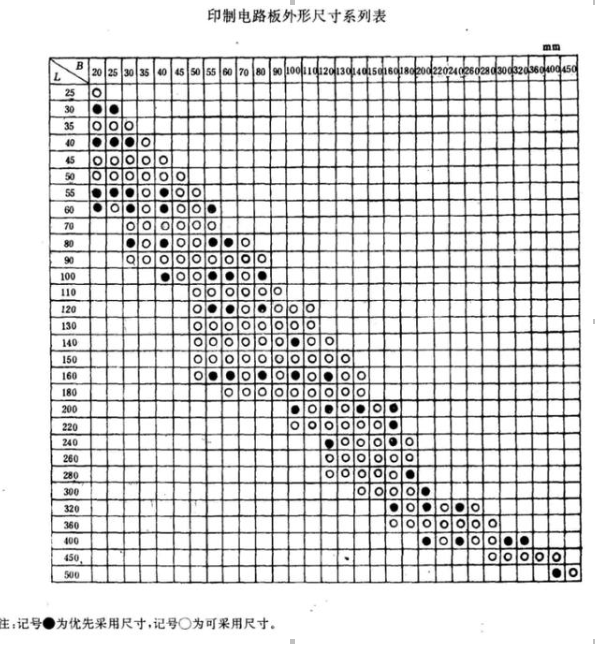

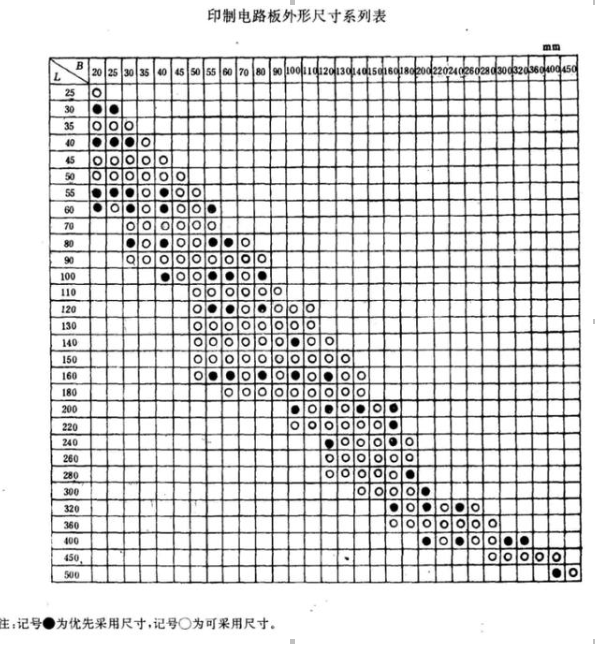

0 規(guī)范產(chǎn)品的 PCB 工藝設計,規(guī)定 PCB 工藝設計的相關參數(shù),使得 PCB 的設計滿足可生產(chǎn)性、可測試性、安規(guī)、EMC、EMI 等的技術規(guī)范要求,在產(chǎn)品設計過程中構建產(chǎn)品的工藝、技術、質(zhì)量、成本優(yōu)勢

2016-06-14 15:37:01 0

0 幾年前,筆者在自動測試設備 (ATE) 領導者 Teradyne 工作時,經(jīng)常會碰到一個根本性的兩難抉擇:在生產(chǎn)/測試車間,是通過一件不合格的器件比較好,還是剔除一件合格器件比較好?顯然,這兩個

2017-11-28 10:48:22 0

0 可測試性定義為:產(chǎn)品能及時準確地確定其狀態(tài),隔離其內(nèi)部故障的設計特性,以提高產(chǎn)品可測試性為目的而進行的設計被稱為可測試性設計。可測試性是同可靠性、維修性相并列的一門新型學科,其發(fā)展和應用對于提高

2017-12-13 17:47:59 7241

7241

產(chǎn)品設計的可測試性 也是產(chǎn)品可制造性的主要內(nèi)容從生產(chǎn)角度考慮也是設計的工藝性之一。

2018-01-23 16:19:36 4681

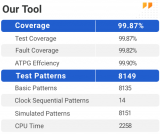

4681 基于仿真器的傳統(tǒng)驗證速度太慢,而且可能需要DFT工程師成為設計的關鍵路徑,即設計的最慢的一環(huán)節(jié),更糟糕的是,他們可能會在流片前實施會降低DFT設計可信度的策略。理想情況下,客戶希望在流片之前驗證DFT。但由于上市時間方面的壓力,芯片在流片前只進行了極少的DFT驗證,因此在芯片制造的過程中甚至在其返回到實驗室之后,必須繼續(xù)進行DFT驗證。因此,我們需要的是一個硬件加速流程,從而可大幅縮短執(zhí)行完整驗證作業(yè)所需的仿真周期。

2018-03-01 11:13:33 1

1 集成電路的生產(chǎn)成本以測試開發(fā)、測試時間以及測試設備為主。模擬電路一般只占芯片面積的10%左右,測試成本卻占總測試成本的主要部分。所以,削減模擬部分的測試成本將有利于芯片的設計與生產(chǎn)。

2019-06-08 09:32:00 2787

2787

電子組裝測試包括兩種基本類型:裸板測試和加載測試。裸板測試是在完成線路板生產(chǎn)后進行,主要檢查短路、開路、網(wǎng)表的導通性。在工藝過程中還有許多其它的檢查和驗證方法。加載測試在組裝工藝完成后進行,它比裸板測試復雜。

2019-08-09 15:32:38 1448

1448

通過遵守一定的規(guī)程(DFT-Design for Testability,可測試的設計),可以大大減少生產(chǎn)測試的準備和實施費用。這些規(guī)程已經(jīng)過多年發(fā)展,當然,若采用新的生產(chǎn)技術和元件技術,它們也要

2019-04-25 15:02:40 1021

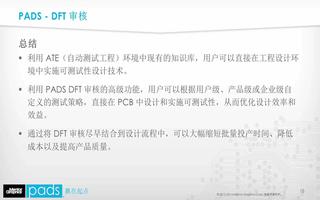

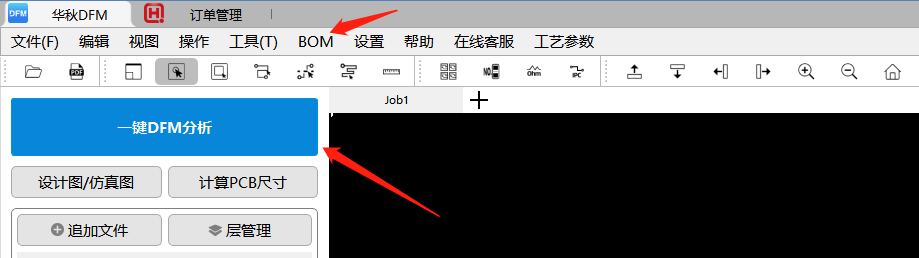

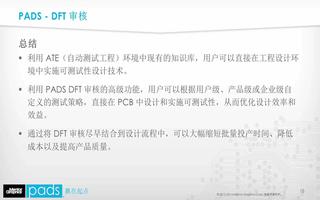

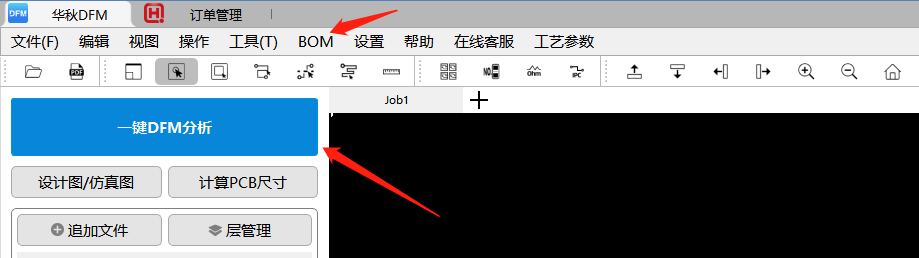

1021 通過此視頻可快速瀏覽 PADS DFT 審核的一些主要功能、優(yōu)點和易用性。在設計流程的早期使用 PADS DFT 審核可大幅降低 PCB 的批量投產(chǎn)時間,確保 100% 的測試點覆蓋和制造前所有網(wǎng)絡的可測試性。

2019-05-21 08:06:00 3979

3979 PADS 可測試性設計 (DFT) 審核可以縮短上市時間。了解如何盡早在設計流程中利用 PCB 測試點和 DFT 審核優(yōu)化設計。

2019-05-14 06:26:00 4767

4767

可測試性分析工具可以幫助您實施經(jīng)濟高效的快速測試策略,其中包含X射線和光學檢測以及整體PCB測試策略的在線測試部分。

2019-08-14 15:48:00 2757

2757 成功的關鍵是說服設計師將測試作為設計的一部分,而不是事后的想法。

2019-08-14 15:49:00 1182

1182 隨著技術進入超大規(guī)模集成(VLSI)時代,VLSI電路的高度復雜性及多層印制板、表面封裝(SMT)、圓片規(guī)模集成(WSI)和多模塊(MCM)技術在電路系統(tǒng)中的運用

2019-08-27 17:02:19 2556

2556 電路板測試工程師在檢測某種元件的特性時應該盡可能使用最簡單的方法來測試,以確定該元件能是否到達預期的功能需求。

2019-09-03 10:54:41 1029

1029 電路板制板可測試性的定義可簡要解釋為:電路板測試工程師在檢測某種元件的特性時應該盡可能使用最簡單的方法來測試,以確定該元件能是否到達預期的功能需求。

2020-03-27 14:23:46 2867

2867 隨著微型化程度不斷提高,元件和布線技術也取得巨大發(fā)展,例如BGA外殼封裝的高集成度的微型IC,以及導體之間的絕緣間距縮小到0.5mm,這些僅是其中的兩個例子。電子元件的布線設計方式,對以后制作流程中的測試能否很好進行,影響越來越大。下面介紹幾種重要規(guī)則及實用提示。

2020-05-05 16:03:00 2944

2944 VLSI測試技術導論, 可測試性設計, 邏輯與故障模擬,測試生成,邏輯自測試,測試壓縮,邏輯電路故障診斷,存儲器測試與BIST,存儲器診斷與BISR,邊界掃描與SOC測試,納米電路測試技術,復習及習題

2020-10-09 08:00:00 1

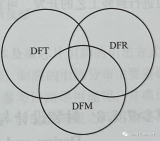

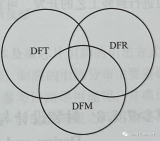

1 用元素和測試點補充您的操作設計以促進電路板的功能測試被稱為可測試性( DFT )設計。 DFT 與制造設計( DFM )不應混淆,盡管兩者都是基于 CM 設備和過程能力的設計人員活動。 DFM

2020-10-12 20:42:17 5282

5282 PCB的可測試性設計是產(chǎn)品可制造性的主要內(nèi)容之一,也是電子產(chǎn)品設計必須考慮的重要內(nèi)容之一。

2020-12-01 10:59:45 3262

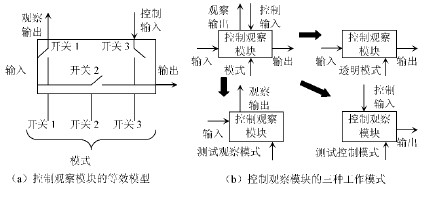

3262 在現(xiàn)代控制理論中,針對某些狀態(tài)變量不受控制的問題,建立離散時間控制系統(tǒng)方程,并給出求解可控制性的條件,同時必須從測量或觀測的結果中提取關于系統(tǒng)狀態(tài)的信息,在求解可控制性的條件下,得到可觀測性的理論結果。

2020-12-01 08:00:00 1

1 作為一名優(yōu)秀的PCB設計工程師,需要掌握一些必備的設計理念,這樣才能夠設計出更好的板子。

2021-05-03 10:53:35 3523

3523

DFM(Design for Manufacture)可制造性設計是硬件研發(fā)到生產(chǎn)過程中關鍵的步驟。良好的設計從研發(fā)階段開始就將設計和制造緊密聯(lián)系,這其中包括可制造性、可測試性、相關設計說明、生產(chǎn)指導等。

2022-04-12 16:16:03 3181

3181

所以要養(yǎng)成良好習慣,做個規(guī)范的原理圖。此外,一個優(yōu)秀的原理圖,還會考慮可測試性、可維修性、BOM表歸一化等。

2022-11-15 10:08:47 2145

2145 SOC是在同一塊芯片中集成了CPU、各種存儲器、總線系統(tǒng)、專用模塊以及多種I/O接口的系統(tǒng)級超大規(guī)模集成電路。ASIC是專用于某一方面的芯片,與SOC芯片相比較為簡單。

2023-04-03 16:04:16 9800

9800 養(yǎng)成良好習慣,做個規(guī)范的原理圖,會考慮可讀性、可測試性、可維修性、BOM表歸一化等。

2023-04-06 14:50:56 2078

2078

可制造性設計 (Design for Manufacturabiity, DFM)、可靠性設計 (Designfor Reliability, DFR)與可測試性設計 (Design

2023-05-18 10:55:54 5214

5214

在iOS開發(fā)中,采用合適的架構模式能夠提高代碼的可維護性和可測試性。

2023-06-06 14:55:18 1832

1832 可測試性設計(Design for Test,DFT)和可檢驗性設計(Design for Inspection,DFI)是兩種用于增強產(chǎn)品的測試和檢驗能力的設計方法。下面是它們的區(qū)別與聯(lián)系,包括

2023-06-26 14:43:19 1570

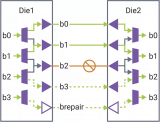

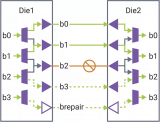

1570 近年來,隨著摩爾定律的放緩,多芯片系統(tǒng)(Multi-die)解決方案嶄露頭角,為芯片功能擴展提供了一條制造良率較高的路徑。

2023-08-16 14:43:45 2186

2186

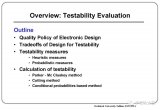

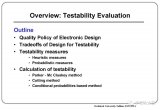

可測性設計(DFT)之可測試性評估詳解

可測試性設計的定性標準:

測試費用:

一測試生成時間

-測試申請時間

-故障覆蓋

一測試存儲成本(測試長度)

自動測試設備的一可用性

2023-09-01 11:19:34 2129

2129

隨著半導體技術的飛速發(fā)展,系統(tǒng)級芯片(SoC)設計已成為現(xiàn)代電子設備中的主流。在SoC設計中,可測試性設計(DFT)已成為不可或缺的環(huán)節(jié)。DFT旨在提高芯片測試的效率和準確性,確保產(chǎn)品質(zhì)量和可靠性。

2023-09-02 09:50:10 4357

4357 ? 9月20日,由EDA2主辦的首屆IDAS設計自動化產(chǎn)業(yè)峰會在武漢的中國光谷科技會展中心舉行,英諾達(成都)電子科技有限公司攜最新發(fā)布的EnAltius DFT Checker靜態(tài)驗證EDA工具亮相該峰會,副總經(jīng)理熊文發(fā)表了題為《搭建芯片驗證完整版圖——靜態(tài)驗證工具及流程》的演講。 峰會以“揚帆”為主題,設置1場主論壇+6場平行主題分論壇,來自半導體產(chǎn)業(yè)上下游頭部企業(yè)、高校、科研院所和專業(yè)機構等近1500多位專家、學者、來賓出席了本次峰會。本次峰會上,

2023-09-23 11:13:18 1897

1897 測試友好的PCB電路設計要費一些錢,然而,測試困難的電路設計費的錢會更多。測試本身是有成本的,測試成本隨著測試級數(shù)的增加而加大;從在線測試到功能測試以及系統(tǒng)測試,測試費用越來越大。

2023-10-31 15:11:43 608

608 西門子數(shù)字化工業(yè)軟件近日推出Tessent RTL Pro 創(chuàng)新軟件解決方案,旨在幫助集成電路(IC) 設計團隊簡化和加速下一代設計的關鍵可測試性設計(DFT) 任務。

2023-11-10 11:11:18 1403

1403 近日,芯來科技攜手杭州廣立微電子股份有限公司(以下簡稱“廣立微”)及上海億瑞芯電子科技有限公司(以下簡稱“億瑞芯”),共同建立在Design for Test(DFT)可測試性設計領域的戰(zhàn)略合作關系,以擴大三方合作的深度和廣度,為產(chǎn)業(yè)提供有競爭力的多元化設計方案。

2024-01-19 09:12:11 1466

1466

for Test(DFT)可測試性設計領域的戰(zhàn)略合作關系,以擴大三方合作的深度和廣度,為產(chǎn)業(yè)提供有競爭力的多元化設計方案。

2024-01-19 15:58:32 1853

1853 近日,杭州廣立微電子股份有限公司(簡稱“廣立微”)宣布與芯來智融半導體科技(上海)有限公司(簡稱“芯來”)以及上海億瑞芯電子科技有限公司(簡稱“億瑞芯”)建立戰(zhàn)略合作伙伴關系,共同致力于Design for Test(DFT)可測試性設計領域的發(fā)展。

2024-01-24 17:09:19 3062

3062

電子發(fā)燒友App

電子發(fā)燒友App

評論