認為差分信號不需要地平面作為回流路徑,或者認為差分走線彼此為對方提供回流途徑。造成這種誤區的原因是被表面現象迷惑,或者對高速信號傳輸的機理認識還不夠深入。雖然差分電路對于類似地彈以及其它可能存在于電源和地平面上的噪音信號是不敏感的。

2016-12-05 10:36:53 2139

2139

在高速PCB設計中,差分信號(DIFferential Signal)的應用越來越廣泛,電路中最關鍵的信號往往都要采用差分結構設計。為什么這樣呢?和普通的單端信號走線相比,差分信號有抗干擾能力強

2023-01-02 01:08:06 3315

3315

的本質。下面重點討論一下PCB差分信號設計中幾個常見的誤區。誤區一:認為差分信號不需要地平面作為回流路徑,或者認為差分走線彼此為對方提供回流途徑。造成這種誤區的原因是被表面現象迷惑,或者對高速信號傳輸

2015-01-12 14:53:57

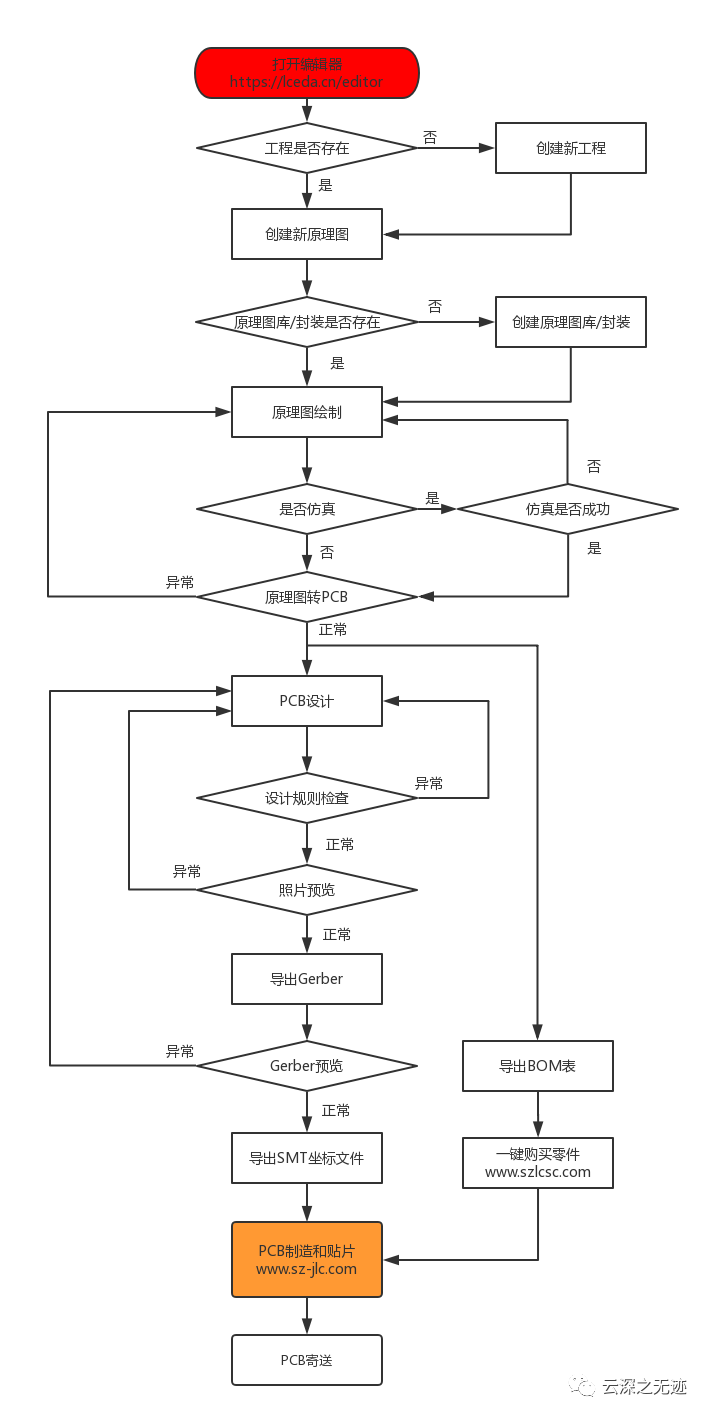

下面從直角走線、差分走線、蛇形線三個方面來闡述PCB LAYOUT的走線。

2021-03-17 07:25:46

分走線的要求之一。但所有這些規則都不是用來生搬硬套的,不少工程師似乎還不了解高速差分信號傳輸的本質。下面重點討論一下PCB差分信號設計中幾個常見的誤區。 誤區一:認為差分信號不需要地平面作為回流路徑

2019-06-10 10:11:23

。

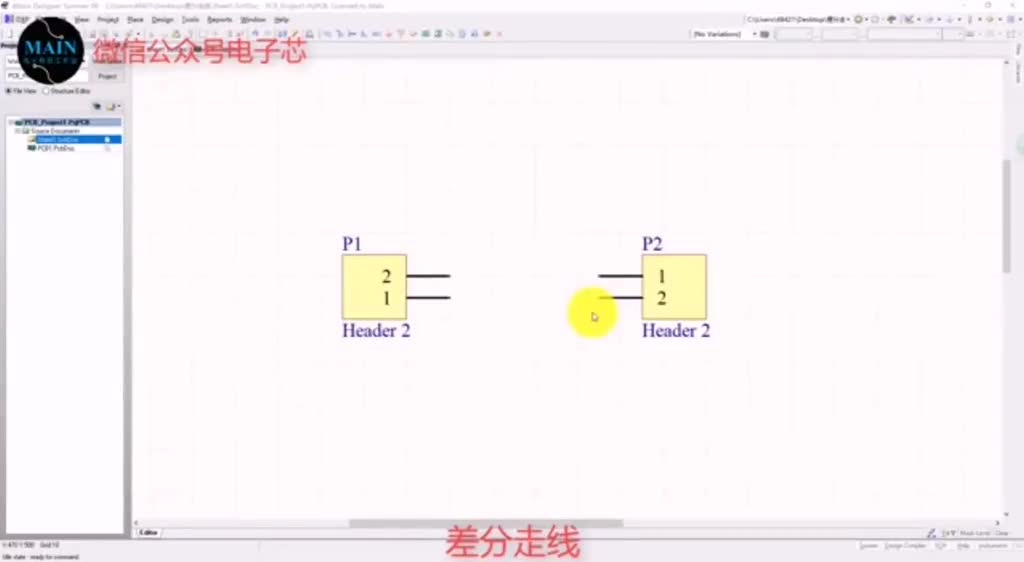

2. 差分走線差分信號(Differential Signal)在高速電路設計中的應用越來越廣泛,電路中最關鍵的信號往往都要采用差分結構設計,什么另它這么倍受青睞呢?在PCB設計中又如何能保證其良好

2025-03-13 11:35:03

分信號傳輸的本質。下面重點討論一下PCB差分信號設計中幾個常見的誤區。誤區一:認為差分信號不需要地平面作為回流路徑,或者認為差分走線彼此為對方提供回流途徑。造成這種誤區的原因是被表面現象迷惑,或者對高速

2014-08-13 15:44:05

布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中

2019-05-23 08:52:37

布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中

2019-08-05 06:40:24

”有時候也是差分走線的要求之一。但所有這些規則都不是用來生搬硬套的,不少工程師似乎還不了解高速差分信號傳輸的本質。下面重點討論一下PCB差分信號設計中幾個常見的誤區:誤區一:認為差分信號不需要

2017-07-07 11:45:56

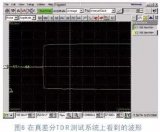

TDR測試,獲得最準確的特征阻抗信息。阻礙真實測試的主要原因有以下兩個:難以找到差分TDR探頭的接地點,高速PCB設計人員不會在設計高速差分走線時在走線的末端(即芯片引腳)附近放置固定間距的接地點;差

2019-05-29 07:49:26

了解高速差分信號傳輸的本質。下面重點討論一下PCB差分信號設計中幾個常見的誤區。 誤區一:認為差分信號不需要地平面作為回流路徑,或者認為差分走線彼此為對方提供回流途徑。造成這種誤區的原因是被表面現象迷惑

2017-09-03 13:25:35

規則都不是用來生搬硬套的,不少工程師似乎還不了解高速差分信號傳輸的本質。下面重點討論一下PCB差分信號設計中幾個常見的誤區。誤區一:認為差分信號不需要地平面作為回流路徑,或者認為差分走線彼此為對方提供

2019-08-21 07:30:00

PCB布線的直角走線、差分走線和蛇形線基礎理論

2015-05-21 11:48:54

PCB設計中差分線怎么設置,還有就是等長分析

2019-08-19 09:47:36

還不了解高速差分信號傳輸的本質。下面重點討論一下PCB差分信號設計中幾個常見的誤區。誤區一:認為差分信號不需要地平面作為回流路徑,或者認為差分走線彼此為對方提供回流途徑。造成這種誤區的原因是被表面現象

2017-11-13 08:45:52

中鋪銅的作用(ZT)

直角走線為什么不可取?差分走線的優勢是啥?蛇形走線如何走?——PCB設計走線的幾點專家建議(ZT)

……

?

BTW,這些分享不過癮,希望聽到你的分享,哪怕吐槽也行!來吧,吐

2018-08-13 08:14:18

注意的要點包括:差分走線、音頻走線、視頻走線、阻抗匹配等內容。通過培訓,學員可以在短短的一個月時間快速學會PCB設計并掌握重要的基本技巧(包教會)聯系方式:朱工電話:***QQ:1711395765地址:深圳市龍崗區坂田崗頭市場

2013-06-03 10:32:32

”有時候也是差分走線的要求之一。但所有這些規則都不是用來生搬硬套的,不少工程師似乎還不了解高速差分信號傳輸的本質。下面重點討論一下PCB差分信號設計中幾個常見的誤區:誤區一:認為差分信號不需要地平面作為

2021-06-17 16:53:35

所有這些規則都不是用來生搬硬套的,不少工程師似乎還不了解高速差分信號傳輸的本質。下面重點討論一下PCB差分信號設計中幾個常見的誤區。 誤區一:認為差分信號不需要地平面作為回流路徑,或者認為差分走線彼此

2019-05-20 04:21:21

。“盡量靠近原則”有時候也是差分走線的要求之一。但所有這些規則都不是用來生搬硬套的,不少工程師似乎還不了解高速差分信號傳輸的本質。下面重點討論一下PCB差分信號設計中幾個常見的誤區。 誤區一:認為差分信

2018-09-17 17:31:52

PCB設計的誤區

2021-01-26 07:34:49

的EMI,到10GHz以上的RF設計領域,這些小小的直角都可能成為高速問題的重點對象。 差分走線的幾個優勢(“等長、等距、參考平面”) 何為差分信號(Differential Signal)?通俗

2018-12-05 09:36:02

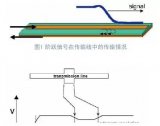

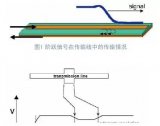

的回路進行回流,最大的區別在于差分線除了有對地的耦合之外,還存在相互之間的耦合,哪一種耦合強,那一種就成為主要的回流通路。在PCB 電路設計中,一般差分走線之間的耦合較小,往往只占10~20%的耦合度

2016-09-22 09:06:56

的回路進行回流,最大的區別在于差分線除了有對地的耦合之外,還存在相互之間的耦合,哪一種耦合強,那一種就成為主要的回流通路。在PCB 電路設計中,一般差分走線之間的耦合較小,往往只占10~20%的耦合度

2016-09-29 11:27:50

NXP的ARM9 LPC3250的DDR差分對時鐘信號的引腳怎么距離那么遠,還怎么做差分走線啊?

2022-08-09 14:23:48

用來生搬硬套的,不少工程師似乎還不了解高速差分信號傳輸的本質。下面重點討論一下PCB差分信號設計中幾個常見的誤區。 誤區一:認為差分信號不需要地平面作為回流路徑,或者認為差分走線彼此

2010-03-16 09:23:41

;<font face="Verdana">PCB Layout 中的直角走線、差分走線和蛇形線<br/>&

2009-05-31 10:08:49

;/p><p>誤區:認為差分走線一定要靠的很近。讓差分走線靠近無非是為了增強他們的耦合,既可以提高對噪聲的免疫力,還能充分利用磁場的相反極性來抵消對外界的電磁干擾

2009-05-31 10:43:01

,布線在高速PCB設計中是至關重要的。下面將針對實際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優化的走線策略。主要從直角走線,差分走線,蛇形線等三個方面來闡述。

2009-08-20 20:58:49

。“盡量靠近原則”有時候也是差分走線的要求之一。但所有這些規則都不是用來生搬硬套的,不少工程師似乎還不了解高速差分信號傳輸的本質。下面重點討論一下PCB差分信號設計中幾個常見的誤區。誤區一:認為差分信

2018-07-08 13:28:36

重點討論一下PCB差分信號設計中幾個常見的誤區。 誤區一:認為差分信號不需要地平面作為回流路徑,或者認為差分走線彼此為對方提供回流途徑。造成這種誤區的原因是被表面現象迷惑,或者對高速信號傳輸的機理認識

2018-09-21 11:53:08

是為了保證兩者差分阻抗一致,減少反射。“盡量靠近原則”有時候也是差分走線的要求之一。但所有這些規則都不是用來生搬硬套的,不少工程師似乎還不了解高速差分信號傳輸的本質。下面重點討論一下PCB差分信號設計中

2016-01-30 11:11:14

規則都不是用來生搬硬套的,不少工程師似乎還不了解高速差分信號傳輸的本質。下面重點討論一下PCB差分信號設計中幾個常見的誤區。誤區一:認為差分信號不需要地平面作為回流路徑,或者認為差分走線彼此為對方提供

2019-03-18 21:38:12

信號總是沿著電感最小的回路進行回流,最大的區別在于差分線除了有對地的耦合之外,還存在相互之間的耦合,哪一種耦合強,那一種就成為主要的回流通路。 在PCB 電路設計中,一般差分走線之間的耦合較小,往往只占

2023-04-12 15:15:48

來源:互聯網在高速PCB設計中,差分信號的應用越來越廣泛,這主要原因是和普通的單端信號走線相比,差分信號具有抗干擾能力強、能有效抑制EMI、時序定位精確的優勢。作為一名(準)PCB設計工程師,我們必須搞定差分信號,接下來我們了解下相關內容吧!

2020-10-23 08:36:50

的回路進行回流,最大的區別在于差分線除了有對地的耦合之外,還存在相互之間的耦合,哪一種耦合強,那一種就成為主要的回流通路。 在PCB電路設計中,一般差分走線之間的耦合較小,往往只占10~20

2018-09-18 15:55:05

討論一下PCB差分信號設計中幾個常見的誤區。 </br> </br>誤區一:認為差分信號不需要地平面作為回流路徑,或者認為差分走線彼此為對方提供回流途徑。造成這種誤區的原因是被表面現象迷惑,或者對高速

2021-06-11 19:17:59

生搬硬套的,不少工程師似乎還不了解高速差分信號傳輸的本質。下面重點討論一下PCB差分信號設計中幾個常見的誤區。 誤區一:認為差分信號不需要地平面作為回流路徑,或者認為差分走線彼此為對方提供回 流途徑。 誤區二:認為

2014-12-16 09:47:09

負載,減緩上升時間;二是阻抗不連續會造成信號的反射;三是直角尖端產生的EMI,到10GHz以上的RF設計領域,這些小小的直角都可能成為高速問題的重點對象。差分走線的幾個優勢(“等長、等距、參考平面

2013-11-13 21:42:25

。但這些規則都不是用來生搬硬套,所以不少工程師似乎還不了解高速差分信號傳輸的本質。下面重點討論一下PCB差分信號設計中幾個常見的誤區。誤區一:認為差分信號不需要地平面作為回流路徑,或者認為差分走線彼此

2018-07-20 16:48:38

請教一下大神在PCB中使用差分走線有什么好處啊?

2023-04-11 17:35:05

請問下AM26C32和AM26C31用在接口板中走線需要差分走線嗎?

2019-03-07 14:01:20

這種接受發送信號線是要差分走線嗎

2019-09-05 05:35:41

還有為什么要差分走線?

2019-05-28 00:57:48

沿著電感最小的回路進行回流,最大的區別在于差分線除了有對地的耦合之外,還存在相互之間的耦合,哪一種耦合強,哪一種就成為主要的回流通路。在 PCB 電路設計中,一般差分走線之間的耦合較小,往往只占 10

2020-09-29 09:12:19

沿著電感最小的回路進行回流,最大的區別在于差分線除了有對地的耦合之外,還存在相互之間的耦合,哪一種耦合強,哪一種就成為主要的回流通路。在 PCB 電路設計中,一般差分走線之間的耦合較小,往往只占 10

2022-06-07 14:26:13

誤區一:認為差分信號不需要地平面作為回流路徑,或者認為差分走線彼此為對方提供回流途徑。造成這種誤區的原因是被表面現象迷惑,或者對高速信號傳輸的機理認識還不夠深入。從圖1-8-15的接收端的結構可以

2012-12-18 12:03:00

誤區一:認為差分信號不需要地平面作為回流路徑,或者認為差分走線彼此為對方提供回流途徑。造成這種誤區的原因是被表面現象迷惑,或者對高速信號傳輸的機理認識還不夠深入。從圖1-8-15的接收端的結構可以

2012-12-19 16:52:38

高速PCB設計中的若干誤區與對策

2012-08-20 14:38:56

絡了。2、在物理規則下建立差分規則圖1-6在物理規則下創建差分規則如下圖1-7彈出命名對話框圖1-7差分規則命名因為電子規則約束在進行PCB設計布線時更優先,同時電氣規則可以設置更多的約束,推薦在電氣規則中設置差分走線的約束。

2017-01-06 09:46:41

差分信號就是驅動器端發送兩個等值、反相的信號,接收端通過比較這兩個電壓的差值來判斷邏輯狀態0還是1。而承載差分信號的那一對走線就稱為差分走線。 差分信號,有些也稱差動信號,用兩根完全一樣,極性相反的信號傳輸一路數據,依靠兩根信號電平差進行判決

2011-03-11 15:22:03 212

212 誤區一:認為差分信號不需要地平面作為回流路徑,或者認為差分走線彼此為對方提供回流途徑。造成這種誤區的原因是被表面現象迷惑,或者對高速信號傳輸的機理認識還不夠深入。

2011-11-16 17:03:14 0

0 本內容詳細介紹pcb layout學習中用Allegro幾個誤區

2011-11-23 13:49:41 4759

4759 差分信號PCB布局布線時的幾個常見誤區,很實用。

2015-10-29 11:39:14 0

0 Altium Design中差分走線的設置,包括添加網絡類與差分走線規則設置。

2015-10-29 14:08:33 0

0 PCBLayout,中的直角走線、差分走線和蛇形線

2016-12-16 21:58:19 0

0 【導讀】PCB 差分走線的設計中最重要的規則就是匹配線長,其它的規則都可以根據設計要求和實際應用進行靈活處理。同時為了彌補阻抗的匹配可以采用接收端差分線對之間加一匹配電阻。 其值應等于差分阻抗的值。這樣信號品質會好些。

2016-12-07 01:10:11 4261

4261 是至關重要的。下面將針對實際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優 化的走線策略。主要從直角走線,差分走線,蛇形線等三個方面來闡述。 1、直角走線 直角走線一般是PCB布線中要求盡量避免的情況,也幾乎成為衡量布線好壞的標準之一

2017-12-01 10:37:31 0

0 何為差分信號?通俗地說,就是驅動端發送兩個等值、反相的信號,接收端通過比較這兩個電壓的差值來判斷邏輯狀態0還是1。而承載差分信號的那一對走線就稱為差分走線。 差分信號和普通的單端信號走線相比,最明顯

2017-12-04 10:45:41 0

0 FireWire1394的幾百Mbps到今天的PCI-Express G1/G2、SATA G1/G2 、XAUI/2XAUI、XFI的幾個Gbps乃至10Gbps。計算機以及通信行業的PCB客戶對差分走線的阻抗控制

2017-12-22 13:53:24 8992

8992

由于注入DUT(被測設備)中的TDR階躍脈沖是差分信號,因此TDR設備可以直接測出差分走線的特征阻抗。使用差分階躍信號進行真差分TDR測試,給使用者帶來的最大好處就是可以實現虛擬接地。

2017-12-22 13:57:01 9075

9075

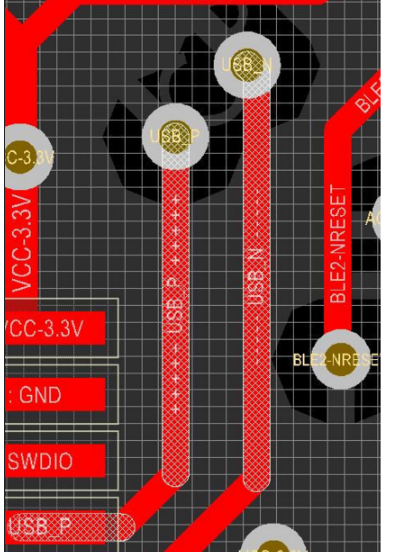

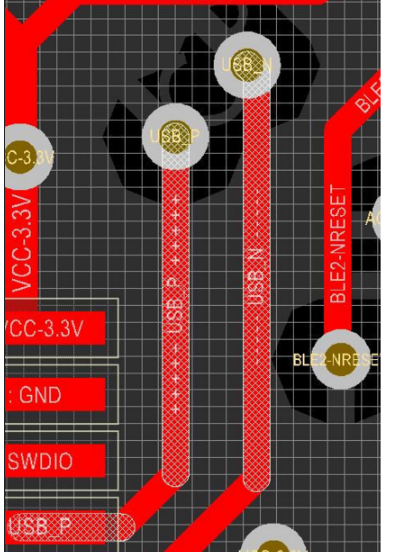

PCB layout之USB差分走線布線經驗教訓。USB是一種快速、雙向、同步傳輸、廉價、方便使用的可熱拔插的串行接口。由于數據傳輸快,接口方便,支持熱插拔等優點使USB設備得到廣泛應用。目前

2018-03-01 08:35:29 76975

76975 布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中是至關重要的。下面將針對實際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優化的走線策略。

2018-04-14 11:06:00 4042

4042

布線(Layout)是 PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過 Layout 得以實現并驗證,由此可見,布線在高速 PCB設計中

2018-07-06 15:28:18 6749

6749 本文檔的主要內容詳細介紹的是PCB高級應用之蛇行布線差分走線多層板層疊分析信號完整性分析概述。

2018-09-19 17:21:18 0

0 模分量;等距則主要是為了保證兩者差分阻抗一致,減少反射。“盡量靠近原則”有時候也是差分走線的要求之一。但所有這些規則都不是用來生搬硬套的,不少工程師似乎還不了解高速差分信號傳輸的本質。下面重點討論一下pcb差分信號設計中幾個常見的誤區。

下一頁

2018-09-20 18:18:30 1244

1244 差分信號線的布線通常(當然也有一些例外)差分信號也是高速信號,所以高速設計規則通常也都適用于差分信號的布線,特別是設計傳輸線這樣的信號線時更是如此。這就意味著我們必須非常謹慎地設計信號線的布線,以確保信號線的特征阻抗沿信號線各處連續并且保持一個常數。

2019-02-04 16:43:00 5796

5796

本文檔的主要內容詳細介紹的是PCB設計有哪些誤區PCB設計的十大誤區上部分。主要內容包括了:1.PCB設計中的那些誤區2.濾波電容設計的那些事3.一直在“死磕”的布線細節4.“萬能”的地5.總結

2019-01-07 08:00:00 0

0 本文檔的主要內容詳細介紹的是PCB設計有哪些誤區PCB設計的十大誤區下部分主要內容包括了:1.時序及等長設計概述,2.共同時鐘并行總線時序設計,3.源同步時鐘并行總線時序設計,4.高速串行總線時序設計,5.時序及等長設計總結

2019-01-07 08:00:00 0

0 誤區一:這板子的PCB設計要求不高,就用細一點的線,自動布吧。

點評:自動布線必然要占用更大的PCB面積,同時產生比手動布線多好多倍的過孔,在批量很大的產品中,PCB廠家降價所考慮的因素除了

2019-06-04 14:36:47 784

784 布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中是至關重要的。

2019-06-04 14:18:23 1676

1676 布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中

2019-04-30 08:00:00 0

0 布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中

2019-07-01 15:24:50 6358

6358 布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中

2019-07-19 16:47:50 0

0 在高速PCB設計中,差分信號(DIFferential Signal)的應用越來越廣泛,電路中最關鍵的信號往往都要采用差分結構設計。

2020-04-20 17:55:24 2141

2141 在高速PCB設計中,差分信號(DIFferential Signal)的應用越來越廣泛,電路中最關鍵的信號往往都要采用差分結構設計。

2020-01-10 17:55:47 2652

2652 對于PCB工程師來說,最關注的還是如何確保在實際走線中能完全發揮差分走線的這些優勢。也許只要是接觸過Layout的人都會了解差分走線的一般要求,那就是“等長、等距”。等長是為了保證兩個差分信號時刻保持相反極性,減少共模分量;等距則主要是為了保證兩者差分阻抗一致,減少反射。

2019-12-30 15:12:46 2112

2112 AD19 差分走 線出現網格Altium designer 差分走線出現網格,具體情況如下。 造成此類現象的原因在于我們的差分走線的線寬沒有按照我們的線寬的規則來進行走線所導致。 如圖是我們的差分

2020-09-30 10:43:34 17806

17806

來源:羅姆半導體社區? 在高速PCB設計中,差分信號(DIFferential Signal)的應用越來越廣泛,電路中最關鍵的信號往往都要采用差分結構設計。 為什么這樣呢?和普通的單端信號走線相比

2023-02-02 14:33:07 1275

1275 在高速PCB設計中,差分信號的應用越來越廣泛,這主要是因為和普通的單端信號走線相比,差分信號具有抗干擾能力強、能有效抑制EMI、時序定位精確的優勢。

2021-03-23 14:40:47 3833

3833 電子發燒友網為你提供PCB LAYOUT的直角走線、差分走線、蛇形線資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-31 08:41:16 17

17 電子發燒友網為你提供PCB三種特殊走線技巧:直角走線,差分走線,蛇形線資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-16 08:45:45 104

104 差分走線一般用于高速信號傳輸當中,可以有效減少干擾。

2021-11-28 17:29:27 4626

4626 長距離傳輸,網線,485,CAN等需要使用差分走線。如:485、CAN線,為了追求更遠的傳輸距離,通常在差分走線的情況下還會提高的傳輸電平(RS485:-7V至+12V之間 CAN 5V),但相應的也會降低傳輸速率(RS485:平均速度會小于10Mbps ;CAN:平均速度會小于1Mbps)。

2022-11-01 09:43:12 21783

21783 差分信號走線要耦合處理,就是2根信號線在PCB設計時是緊挨著的,不允許分開走線

2023-02-22 09:55:03 3487

3487

PCBA加工廠家為大家介紹下。 PCB設計差分布線要求 各類差分線的阻抗要求不同,根據PCB設計要求,通過阻抗計算軟件計算出差分阻抗和對應的線寬間距,并設置到約束管理器。 差分線通過互相耦合來減少共模干擾,在條件許可的情況下盡可能平行布線,兩根線中

2023-07-07 09:25:21 7692

7692

在PCB 電路設計中,一般差分走線之間的耦合較小,往往只占10~20%的耦合度,更多的還是對地的耦合,所以差分走線的主要回流路徑還是存在于地平面。當地平面發生不連續的時候,無參考平面的區域,差分走線之間的耦合才會提供主要的回流通路。

2023-11-23 15:36:38 926

926 為什么要走差分線?哪些地方需要用到差分走線?差分線與等長線的關系? 差分線是一種常見的高速布線技術,用于傳輸高頻信號。差分信號傳輸是指通過兩條物理線傳輸信號,其中一條線是信號的正向傳輸線,另一條線

2023-12-07 11:15:42 4385

4385 差分線pcb走線原則? 差分線是PCB設計中非常重要的一個部分,它的設計和走線原則可以直接影響到電路性能的穩定性和可靠性。在以下文章中,我將詳盡、詳實、細致地探討差分線的設計原則及其在PCB走線中

2023-12-07 18:09:37 7616

7616 抗干擾能力強,因為兩根差分走線之間的耦合很好,當外界存在噪聲干擾時,幾乎是同時被耦合到兩條線上,而接收端關心的只是兩信號的差值,所以外界的共模噪聲可以被完全抵消。

2023-12-13 15:52:23 690

690 差分走線是一種在高速PCB設計中常用的信號傳輸方式,它與射頻走線有一定的關聯,但也有其獨特的特點和應用場景。

2024-04-10 16:26:37 4160

4160 在PCB設計中,差分走線是一種常見的信號傳輸方式,它具有一系列的優點,使得設計師在處理高速信號時更傾向于使用差分信號而非單端信號。

2024-04-10 16:51:39 6569

6569 ad,cadense 阻抗匹配計算和差分走線設置

2024-10-17 16:59:48 2

2

電子發燒友App

電子發燒友App

評論