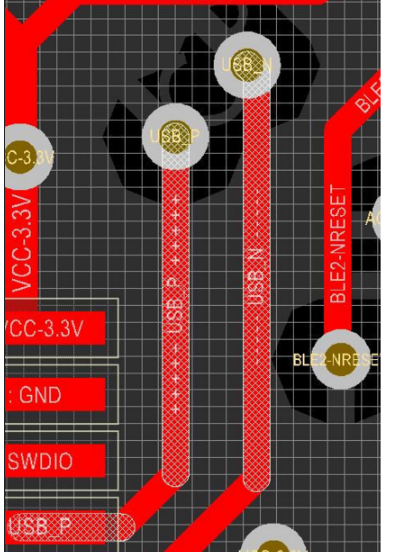

AD19差分走線出現(xiàn)網(wǎng)格Altium designer 差分走線出現(xiàn)網(wǎng)格,具體情況如下。

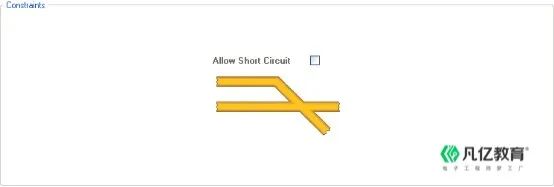

造成此類現(xiàn)象的原因在于我們的差分走線的線寬沒有按照我們的線寬的規(guī)則來進行走線所導(dǎo)致。

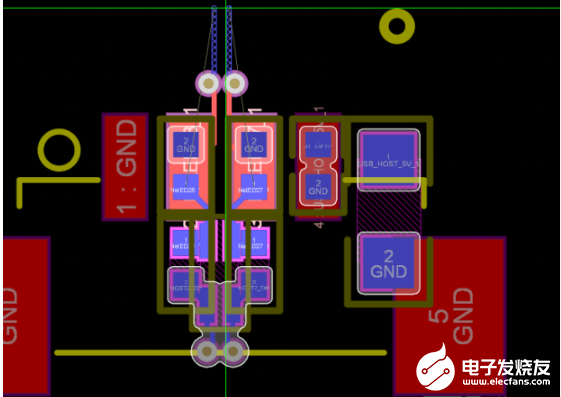

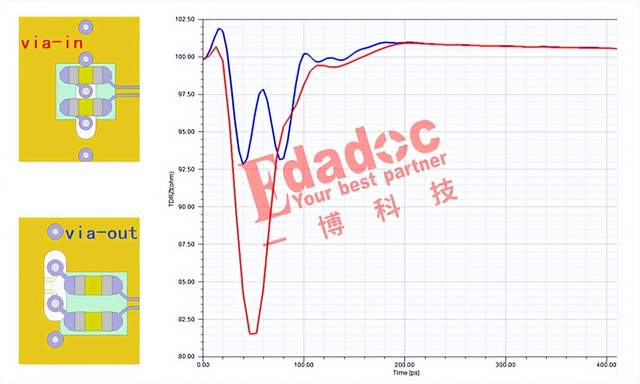

如圖是我們的差分的規(guī)則的線寬和間距走線,如果想要完成好,那么我們就進行相對應(yīng)的線寬的修改,使其走線滿足我們的規(guī)則要求的線寬來。

如圖所示我們的線寬和間距就不會對應(yīng)的顯示我們的白色框線。

編輯:hfy

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

PCB設(shè)計

+關(guān)注

關(guān)注

396文章

4930瀏覽量

95624 -

差分走線

+關(guān)注

關(guān)注

0文章

33瀏覽量

13149 -

線寬

+關(guān)注

關(guān)注

0文章

42瀏覽量

10692

發(fā)布評論請先 登錄

相關(guān)推薦

熱點推薦

【「Altium Designer 25 電路設(shè)計精進實踐」閱讀體驗】+設(shè)計實現(xiàn)之路

設(shè)計,Altium Designer提供了原理圖庫和PCB庫,從而可以快速展開設(shè)計。

對于任何先進的設(shè)計工具來說,它們都會給設(shè)計者提供極大的便利,然而用戶的需求是千差萬別的,也是毫無止

發(fā)表于 02-23 23:52

【「Altium Designer 25 電路設(shè)計精進實踐」閱讀體驗】+總覽篇

作為一名嵌入式開發(fā)工程師,掌握PCB設(shè)計與開發(fā)是必修課程,記得在很早之前要設(shè)計PCB板是用TANGO、SMART等軟件,那時有關(guān)的資料比較少,有本需要的書不容易,為了便于使用自己是復(fù)印一本TANGO

發(fā)表于 02-12 13:33

Altium Designer 26.1.1 版本發(fā)布,新功能詳解

? ?Altium Designer 26.1.1 發(fā)布時間:2025年12月3日 Altium Designer 26.1.1 離線包 15天免費試用

Altium Designer 25.7.1 版本發(fā)布,Altium Designer 25.7.1新功能說明

?Altium Designer 25.7.1 發(fā)布時間:2025年6月11日 Altium Designer 25.7.1 離線包 15天免費試用

[Fortior Tech] [FU6832S 演示板 Gerber 文件] [Altium Designer]幫助

的PCB板。當(dāng)我嘗試生成BOM和CPL文件時,在使用JLCPCB進行制造時會出現(xiàn)錯誤。

原因是Fortior Tech使用了其內(nèi)部組件庫來制作此PCB,但我們沒有該庫,因此

發(fā)表于 06-04 17:07

Altium Designer 22.11.1軟件安裝包下載

的是,AD 22 有帶來新功能,在Altium家官網(wǎng)的這個鏈接有詳細的新特性說明:https://www.altium.com/documentation/altium-designer/new-in-

發(fā)表于 05-22 16:47

?52次下載

Altium Designer 23 軟件下載

AD 22 到AD 23之間各個子版本更新的細節(jié),有興趣的小伙伴可以訪問嗷疼家的官網(wǎng)專題頁面了解:https://www.altium.com/altium-designer/whats-new通過

發(fā)表于 05-22 16:46

?6次下載

Altium Designer AD 25 軟件安裝包下載

Altium Designer 25 隆重登場!借助實時 PCB 協(xié)同設(shè)計、多板和線束功能、高級仿真和無縫 MCAD 集成等強大的新功能,徹底改變您的設(shè)計流程。 AD25 非常適合復(fù)雜

發(fā)表于 05-22 16:45

?58次下載

【搬運】Altium Designer的下載,安裝,漢化

?【Altium Designer】?點擊下方鏈接獲取:https://mp.weixin.qq.com/mp/appm ... 3421678165678915587

Altium Des

發(fā)表于 05-16 17:24

高頻PCB設(shè)計中出現(xiàn)的干擾分析及對策

隨著頻率的提高,將出現(xiàn)與低頻PCB設(shè)計所不同的諸多干擾,歸納起來,主要有電源噪聲、傳輸線干擾、耦合、電磁干擾(EM)四個方面。通過分析高頻PCB的各種干擾問題,結(jié)合工作中實踐,提出了有

發(fā)表于 04-29 17:39

KiCad 與 Altium Designer 圖紙互轉(zhuǎn)詳解

“ ?KiCad 和 Altium Designer是兩款主流的 PCB EDA 工具。AD 和 KiCad 的原理圖、PCB 文件是否可以互轉(zhuǎn)呢?答案是肯定的,但如果需要支持最新版本

Altium Designer PCB設(shè)計高級進階

對PCB設(shè)計的高級進階的內(nèi)容進行相關(guān)的介紹

純分享貼,有需要可以直接下載附件獲取完整資料!

(如果內(nèi)容有幫助可以關(guān)注、點贊、評論支持一下哦~)

發(fā)表于 04-27 16:40

Altium Designer中PCB設(shè)計規(guī)則設(shè)置

在使用 Altium Designer 進行PCB設(shè)計時,除了電氣間距(Clearance)等基礎(chǔ)規(guī)則外, 導(dǎo)線寬度、阻焊層、內(nèi)電層連接、銅皮敷設(shè)等規(guī)則也同樣重要 。這些設(shè)置不僅影響布線效率,還決定了成品板的可制造性與可靠性。

PCB設(shè)計:Altium designer差分走線出現(xiàn)網(wǎng)格的原因

PCB設(shè)計:Altium designer差分走線出現(xiàn)網(wǎng)格的原因

評論