方法一:真差分測(cè)試法如圖6所示:階躍信號(hào)A和階躍信號(hào)B是一對(duì)方向相反、幅度相等且同時(shí)發(fā)出的差分階躍信號(hào)。

我們不但在差分TDR設(shè)備上看到差分的階躍信號(hào),而且當(dāng)我們使用一臺(tái)實(shí)時(shí)示波器來(lái)觀測(cè)這對(duì)階躍信號(hào)時(shí)可以證實(shí)這是真正的差分信號(hào)。

由于注入DUT(被測(cè)設(shè)備)中的TDR階躍脈沖是差分信號(hào),因此TDR設(shè)備可以直接測(cè)出差分走線的特征阻抗。使用差分階躍信號(hào)進(jìn)行真差分TDR測(cè)試,給使用者帶來(lái)的最大好處就是可以實(shí)現(xiàn)虛擬接地,如圖7所示。

由于差分走線和差分信號(hào)是平衡的,差分信號(hào)的中心電壓點(diǎn)和地平面是等電勢(shì)的,因此在使用差分階躍信號(hào)進(jìn)行差分TDR測(cè)試時(shí),只要保證通道A和通道B共地,是不需要與DUT之間接地的。

方法二:“Super-Position”法(偽差分)如圖8所示,階躍信號(hào)A和階躍信號(hào)B不是同時(shí)打出的,且方向不是相反的,因此注入到DUT中的階躍信號(hào)完全不是差分信號(hào)。

在這種“偽差分TDR”設(shè)備自身的屏幕上,往往會(huì)經(jīng)過(guò)人為的軟件調(diào)整,令我們看到的階躍信號(hào)同時(shí)發(fā)出且方向相反的。

但是如果我們用一臺(tái)實(shí)時(shí)示波器來(lái)觀測(cè)這兩個(gè)階躍脈沖,我們可以看到如圖9所示的波形,我們可以看出兩個(gè)階躍脈沖之間的真實(shí)時(shí)序關(guān)系,存在著2us的時(shí)間差。也就是說(shuō)這兩個(gè)階躍信號(hào)不是差分信號(hào)。

這樣的TDR階躍脈沖稱為偽差分信號(hào),因?yàn)樗](méi)有真正實(shí)現(xiàn)一個(gè)高速差分信號(hào)的傳輸過(guò)程,即幅度相等,方向相反。因此這種方法不能直接測(cè)出DUT的差分阻抗,只能使用軟件計(jì)算的方法對(duì)差分阻抗測(cè)試進(jìn)行模擬計(jì)算。

在TDR設(shè)備上得到經(jīng)過(guò)計(jì)算后得到的2個(gè)幅度相等,極性相反階躍脈沖。這種差分TDR測(cè)試帶來(lái)的局限性是:差分信號(hào)之間同時(shí)的相互作用無(wú)法真實(shí)地獲得;無(wú)法實(shí)現(xiàn)虛擬接地,在進(jìn)行差分TDR測(cè)試時(shí)通道A和通道B的探頭都必須有各自獨(dú)立的接地點(diǎn)。但是在PCB板內(nèi)部的真實(shí)差分走線附近往往找不到接地點(diǎn),導(dǎo)致無(wú)法在PCB板子內(nèi)部對(duì)真實(shí)的差分走線進(jìn)行測(cè)量。

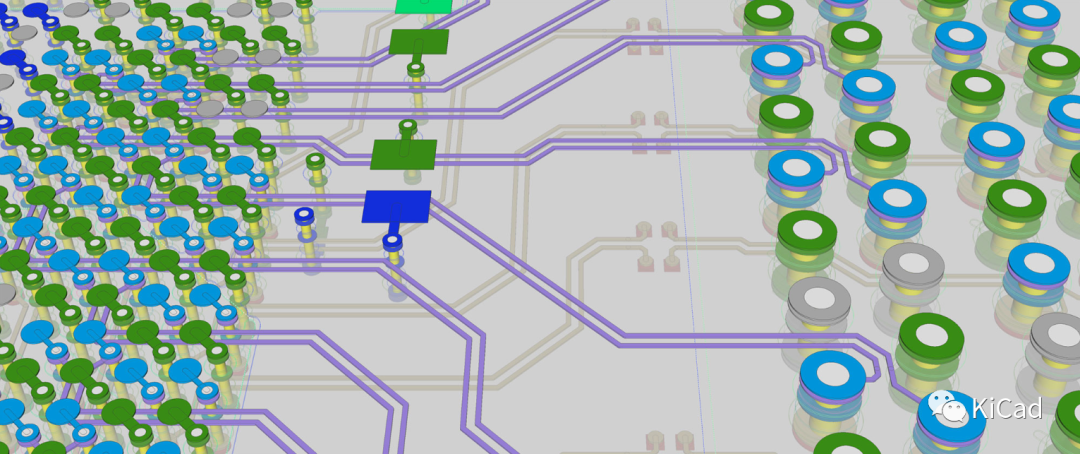

為了解決“偽差分”TDR設(shè)備難以實(shí)現(xiàn)對(duì)PCB板內(nèi)部真實(shí)走線進(jìn)行差分TDR測(cè)量的問(wèn)題,一般的PCB生產(chǎn)商都會(huì)在PCB板的周圍做上帶有接地點(diǎn)的差分走線測(cè)試條,稱之為“Coupon”,圖10就是一個(gè)典型的PCB板,上方是測(cè)試用的“Coupon”,下方是板子內(nèi)部的真實(shí)走線。為了方便探頭連接,測(cè)試點(diǎn)的間距一般做的很大,高達(dá)100mil(即2.54mm),已經(jīng)大大超過(guò)了差分走線的間距。同時(shí)還在測(cè)試點(diǎn)的旁邊會(huì)放置接地點(diǎn),間距同樣是100mil。

五、“Coupon”測(cè)試的局限性與差異

從圖10我們可以看到測(cè)試“coupon”和板內(nèi)真實(shí)走線之間的差別:

1 、雖然走線間距、走線寬度是一致的, 但是“coupon”測(cè)試點(diǎn)的間距固定為100mil(即最初的雙列直插式IC的引腳間距),而板內(nèi)真實(shí)走線的末端(即芯片的引腳)間距是不同的,隨著QFP、PLCC、BGA封裝的出現(xiàn),芯片的引腳間距都遠(yuǎn)小于雙列直插式IC封裝(即“coupon”測(cè)試點(diǎn)的間距)間距。

2、“coupon”走線是理想的直線,而板內(nèi)真實(shí)走線往往是彎曲的、多樣的。PCB設(shè)計(jì)人員和生產(chǎn)人員很容易將“coupon”的走線理想化,但是PCB板上的真實(shí)走線則會(huì)因?yàn)楦鞣N各樣的因素導(dǎo)致走線不規(guī)則化。

3、“coupon”和板內(nèi)真實(shí)走線在整個(gè)PCB板上的位置不同。“coupon”都位于PCB板邊沿,在PCB板出廠時(shí)往往會(huì)被生產(chǎn)商去掉。而板內(nèi)真實(shí)走線的位置則是多樣的,有的在靠近板子的邊沿,有的位于板子的中央。

由于上述幾個(gè)差異的存在,導(dǎo)致“coupon”的特征阻抗往往與板內(nèi)真實(shí)走線阻抗存在如下的幾個(gè)差異:

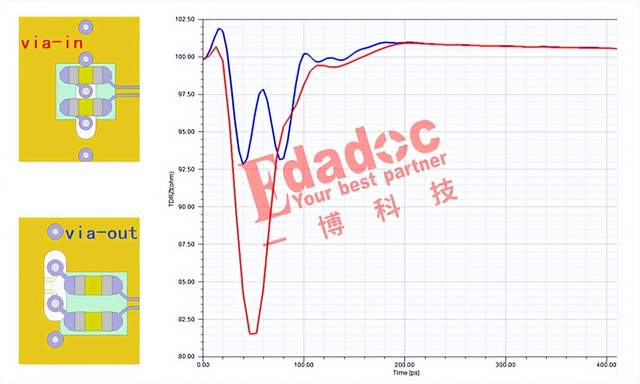

第一,“coupon”測(cè)試點(diǎn)間距“coupon”走線的間距不同,會(huì)導(dǎo)致測(cè)試點(diǎn)與走線之間帶來(lái)阻抗不連續(xù)。而PCB板內(nèi)的真實(shí)差分走線末端(即芯片的引腳)間距往往是與走線間距相等或者非常相近的。由此會(huì)帶來(lái)阻抗測(cè)試結(jié)果的不同。

第二,彎曲的走線與理想的走線所反映出來(lái)的阻抗變化是不一致的。在走線彎曲轉(zhuǎn)折的地方特征阻抗往往是不連續(xù)的,而“coupon”的理想化走線則不能反映由于走線彎曲所帶來(lái)的阻抗不連續(xù)現(xiàn)象。

第三,“coupon”與真實(shí)的走線在PCB板上的位置不同。目前的PCB板都采用多層走線的設(shè)計(jì),在生產(chǎn)時(shí)需要經(jīng)過(guò)壓制。當(dāng)PCB板壓制時(shí),板子不同的位置所受到的壓力不可能做到一致,這樣制成的PCB板在不同的位置上介電常數(shù)往往不相同,特征阻抗也當(dāng)然不同。可見(jiàn)僅僅對(duì)PCB板的“coupon”進(jìn)行TDR測(cè)試是不能完全反映PCB板內(nèi)真實(shí)走線的真實(shí)特征阻抗的。無(wú)論是PCB板的生產(chǎn)商還是高速電路設(shè)計(jì)者、制造者都希望能對(duì)PCB板內(nèi)的真實(shí)高速差分走線直接進(jìn)行TDR測(cè)試,獲得最準(zhǔn)確的特征阻抗信息。阻礙真實(shí)測(cè)試的主要原因有以下兩個(gè):

難以找到差分TDR探頭的接地點(diǎn),高速PCB設(shè)計(jì)人員不會(huì)在設(shè)計(jì)高速差分走線時(shí)在走線的末端(即芯片引腳)附近放置固定間距的接地點(diǎn);差分走線的末端(即芯片的引腳)間距是多變的,必需要一個(gè)間距可調(diào)的差分探頭來(lái)實(shí)現(xiàn)探測(cè)

六、真差分TDR測(cè)試的優(yōu)勢(shì)

我們之前討論差分TDR測(cè)試方法時(shí),我們了解到如果TDR設(shè)備發(fā)出的階躍信號(hào)是差分信號(hào),就可以實(shí)現(xiàn)虛擬接地,即差分TDR探頭無(wú)需與被測(cè)試的PCB板接地。只要測(cè)試者手中有一個(gè)間距可調(diào)的差分TDR探頭即可完成測(cè)試。

圖11是一個(gè)帶寬高達(dá)18GHz的差分TDR探頭在進(jìn)行差分TDR測(cè)試時(shí)的情況。它的探針間距可以在0.5mm~4.5mm之間連續(xù)可調(diào),即使在測(cè)試一個(gè)比圓珠筆尖還要微小的測(cè)試點(diǎn)時(shí)仍然可以非常從容地以單手完成操作。

由于探頭的帶寬高達(dá)18GHz,因此可以獲得很高的測(cè)試分辨率,圖12是對(duì)一塊“coupon”的差分走線進(jìn)行測(cè)試時(shí)獲得的結(jié)果。紅色波形是對(duì)“coupon”最初的測(cè)試結(jié)果,隨后在走線上貼上了一個(gè)很小的膠條(紅色圓圈所示部位)然后再進(jìn)行測(cè)試,獲得了如白色波形的測(cè)試結(jié)果。可見(jiàn)由于貼上小膠條所帶來(lái)的微小阻抗不連續(xù)也能夠通過(guò)高帶寬差分TDR探頭清晰地反映出來(lái)。

真差分的TDR設(shè)備配合高帶寬差分探頭進(jìn)行PCB差分特征阻抗測(cè)試時(shí),無(wú)需在PCB板內(nèi)苦苦的尋找接地點(diǎn),只要探針調(diào)整到合適的間距,即可輕松的對(duì)PCB板內(nèi)的真實(shí)差分走線進(jìn)行探測(cè)。

七、 本文小結(jié):

使用一臺(tái)真差分的TDR設(shè)備,利用差分信號(hào)可以實(shí)現(xiàn)虛擬接地的便利,配合間距可調(diào)的差分TDR探頭可以輕松實(shí)現(xiàn)對(duì)PCB板內(nèi)真實(shí)差分走線的特征阻抗測(cè)量。令高速PCB設(shè)計(jì)人員和PCB制造者在進(jìn)行PCB測(cè)試時(shí)獲得極高的測(cè)試效率和準(zhǔn)確的測(cè)試結(jié)果。

-

pcb

+關(guān)注

關(guān)注

4405文章

23878瀏覽量

424380

原文標(biāo)題:PCB差分走線的阻抗控制技術(shù)(二)

文章出處:【微信號(hào):mcugeek,微信公眾號(hào):MCU開(kāi)發(fā)加油站】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

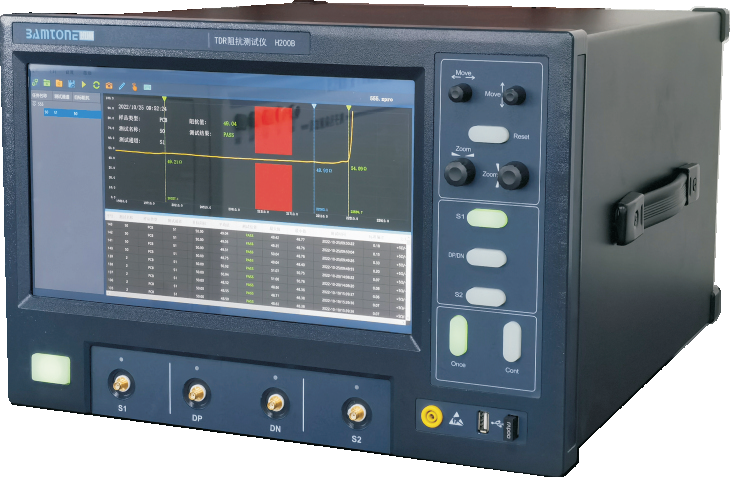

PCB阻抗測(cè)試設(shè)備怎么選?

國(guó)產(chǎn)PCB阻抗測(cè)試分析儀品牌:Bamtone班通

單片機(jī)的差分信號(hào)到底是什么?

USB 差分信號(hào)線 PCB 布線指南

技術(shù)資訊 I 信號(hào)完整性與阻抗匹配的關(guān)系

如何用TDR阻抗測(cè)量?jī)x快速定位PCB傳輸線故障?

PCB板為了節(jié)省AC電容打孔空間,你有沒(méi)動(dòng)過(guò)這個(gè)念頭?

別蒙我,PCB板上這幾對(duì)高速走線怎么看我都覺(jué)得一樣!

受控阻抗布線技術(shù)確保信號(hào)完整性

自學(xué)PCB差分走線的阻抗控制技術(shù)(下篇)

自學(xué)PCB差分走線的阻抗控制技術(shù)(下篇)

評(píng)論