現代集成電路芯片中,隨著設計規模的不斷擴大。一個系統中往往含有數個時鐘。多時鐘帶來的一個問題就是,如何設計異步時鐘之間的接口電路。異步 FIFO(First In First Out)是解決這個問題的一種簡便、快捷的解決方案。##異步FIFO的VHDL語言實現

2014-05-28 10:56:41 9221

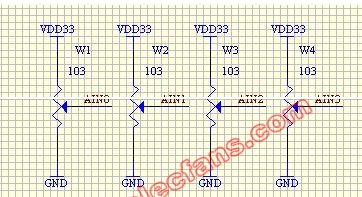

9221 本文將介紹一種基于ARM的高精度多路同步的數據采集與輸出控制系統的設計方法。本設計選用德州儀器公司生產的AD芯片ADS8556和DA芯片DAC8574,分別采用SPI接口和IIC接口與ARM9芯片S3C2440連接,闡明其硬件設計與軟件設計方法。##多路同步D/A設計。

2014-07-23 15:13:44 4318

4318

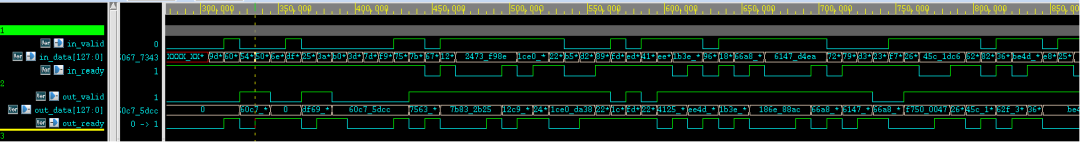

大家好,又到了每日學習的時間了,今天我們來聊一聊基于FPGA的異步FIFO的實現。 一、FIFO簡介 FIFO是英文First In First Out 的縮寫,是一種先進先出的數據緩存器,它與普通

2018-06-21 11:15:25 7148

7148

異步 FIFO 讀寫分別采用相互異步的不同時鐘。在現代集成電路芯片中,隨著設計規模的不斷擴大,一個系統中往往含有數個時鐘,多時鐘域帶來的一個問題就是,如何設計異步時鐘之間的接口電路。異步 FIFO

2020-07-16 17:41:46 1530

1530

按照正常的思路,在前文完成前向時序優化和后向時序優化后,后面緊跟的應該是雙向時序優化策略了,不過不急,需要先實現一下握手型同步FIFO。

2023-12-04 14:03:49 1474

1474

AXI接口FIFO是從Native接口FIFO派生而來的。AXI內存映射接口提供了三種樣式:AXI4、AXI3和AXI4-Lite。除了Native接口FIFO支持的應用外,AXI FIFO還可以用于AXI系統總線和點對點高速應用。

2025-03-17 10:31:11 1914

1914

用單片機為主控制器設計一個A/D和D/A轉換系統,將一路模擬信號從IN0輸入,連續采樣后將數據存入2450H開始的16個內存單元中,然后通過D/A轉換實現模擬電壓的輸出,通過電壓表或示波器觀察輸入、輸出信號的對應情況。

2011-06-29 00:08:22

ARM710a接口卡是ARM開發板(HBI-0016B)的處理器子板。

與該板配合使用,頭卡適用于ARM710a處理器的代碼開發和評估。

頭卡提供到高級微控制器總線體系結構(AMBA)高級系統總線(ASB)的接口

2023-08-21 06:15:44

技術教學的老師們作一交流。1 ARM系統及IDE 接口綜述ARM (A dvanced RS IC M ach ines) 是一種低功耗、高性能的32 位處理器。本文介紹的系統是基于Sam sung

2019-06-04 05:00:19

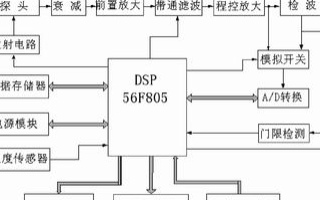

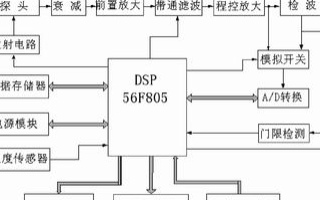

,用戶可自行開發應用軟件,利用采集板獲得數據進行處理,增加自己特有的功能和界面,集成到自己的系統之中,形成各種超聲波應用系統。該采集板能廣泛應用于各種超聲波測厚、超聲波探傷等領域。具有多通道、超高采樣

2020-09-07 10:50:31

在如何使用ARM-2D在小資源Cortex-M處理器芯片中實現圖形界面中,Arm-2D對LCD接口有要求嗎,比如8位8080-i接口還是24位RGB接口?

2022-10-21 14:08:39

在如何使用Arm-2D在小資源Cortex-M處理器芯片中實現圖形界面中,Arm-2D對LCD接口有要求嗎,比如8位8080-i接口還是24位RGB接口?

2022-09-28 10:19:08

僅使用硬宏單元的基于ARM架構的設備,如ARM7TDMI和ARM920T,使用標準的五線制JTAG接口。

但是,一些目標系統要求JTAG事件與系統中的時鐘同步。

DSTREAM的自適應時鐘功能滿足了

2023-08-21 06:51:13

用Labview如何實現A/D采集顯示

2017-03-03 20:14:35

也就是說用一個25M頻率的FIFO寫入數據,用另一個100M(或者不同頻)的FIFO讀出數據。該如何實現呢?不使用異步FIFO

2020-12-03 20:47:22

實現電子掃描,波束合成技術應用于聚焦換能器的聲束。波束合成的細節將在下一節中討論。與光學成像系統類似,超聲系統可在聚焦焦點處實現最佳空間分辨率。根據應用,一維(1D)陣列換能器包括線性陣列、彎曲

2020-02-12 16:45:19

測厚一定得用matlab編程嗎?求一份超聲波測厚的C51程序。

2023-11-09 06:52:29

現階段市場超聲測厚產品的測厚原理一般是閾值檢測或者峰峰值檢測,互相關法依然停留在理論探討或者仿真階段,還沒有走向市場化,這方面除了成本的問題,主要來自于互相關巨大的計算量問題,單片機等CPU無法快速實現測厚計算。那么市場產品的閾值或者峰值測厚原理如何實現高精度測量呢?

2017-08-07 11:28:50

詳細描述了 電磁超聲測厚原理及其應用,歡迎下載

2012-08-13 20:36:34

如題,Altiumdesigner中,將PCB導出成3D文件時,PCB板厚怎么設置??

2017-07-14 08:58:28

超聲波傳感器是0-10V,用NEC單片機的A/D采樣,用超聲波測距,根據距離的變化來控制電磁閥動作,,程序怎么編,求教大家!

2014-01-06 21:28:18

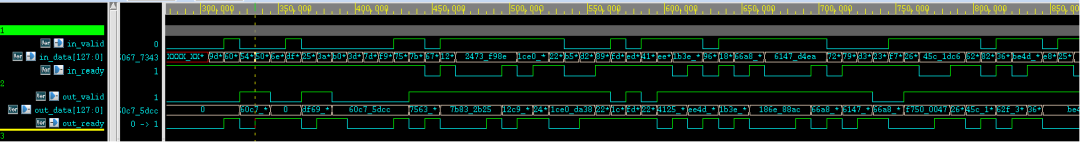

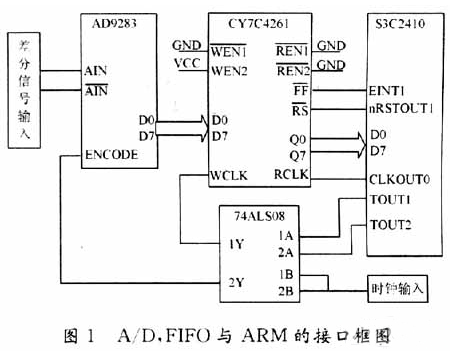

FPGA處理數據的時間,所以整個系統實現了流水線操作。1 系統的總體設計系統硬件主要由信號采集模塊、FIFO、FPGA和SEP3203處理器組成。信號采集模塊主要包括信號接收器和A/D轉換模塊。接收

2019-04-26 07:00:06

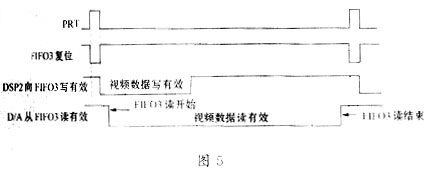

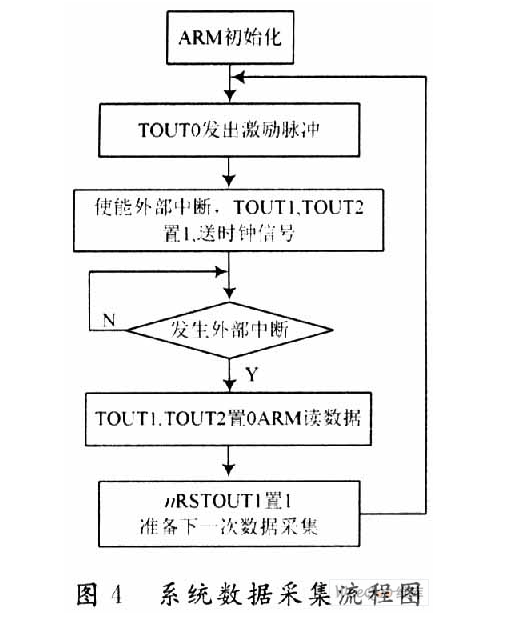

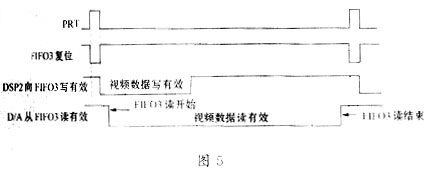

負責提供信號的A/D采樣頻率,并將A/D轉換后的數據存儲到一組FIFO中,待FIFO的FF(FullFlag)端口有效后,將FIFO中的數據讀回,同時使能另一組FIFO的寫時序,實現了信號不間斷的采樣

2018-12-05 10:13:09

本帖最后由 zj5635297 于 2019-10-23 11:07 編輯

現在已經設計了一個電磁超聲測厚的發射電路和接收電路,發射電路采用全橋設計的,沒有調試成功,想問下,有人設計過類似電磁超聲測厚的發射電路(高頻高壓大功率的電路)嗎?有圖最好,萬分感謝!

2019-10-22 22:23:33

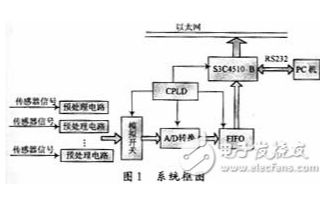

單元電路的測試要求。 這里以測試總線頻率40 MHz,數據寬度32 b的單元電路為例,介紹用單片機和FIFO實現的高速信號測試接口板方案,整個測試系統結構如圖1所示。1 系統概述整個系統主要由單片機

2019-04-29 07:00:07

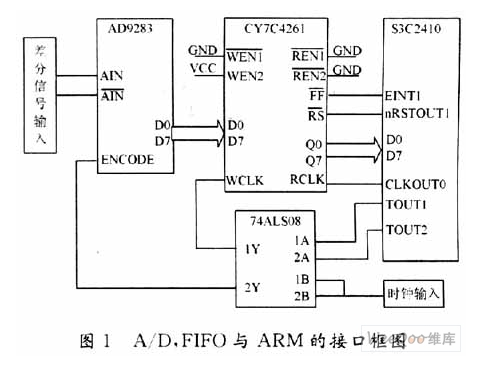

本文介紹了一個基于ARM的線性CCD高速采集系統,系統中選擇了高速線性CCD和高速ADC,因為ADC的采祥速度相對ARM的工作時鐘頻率較慢,所以使用CPLD和FIFO作為A/D和ARM之間的1/0

2023-09-26 07:41:28

,在檢測時,光線會照射在被攝物體表面,ARM控制面陣CMOS攝像頭采集圖像,再把獲得的圖像數據送入FIFO存儲器中緩沖一下,然后通過串口傳輸給電腦,也可通過SD卡接口將圖像存放入SD卡中。 2系統硬件

2018-12-18 09:52:31

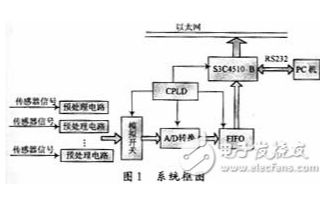

回波圖像和數據的能力,而且實現了遠程監控。 2 系統硬件結構 系統的硬件結構圖如圖1所示,由ARM中央處理器、FPGA、超聲模擬前端和一些外設接口組成。本系統采用S3C2410A是一個由三星公司

2012-12-06 15:46:44

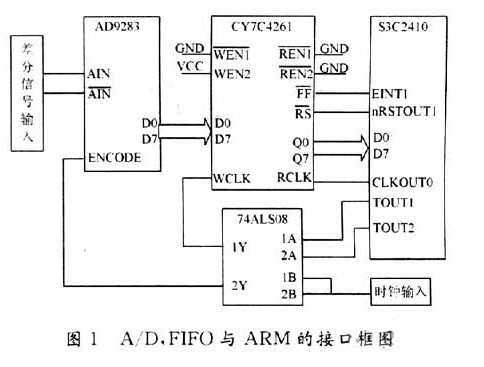

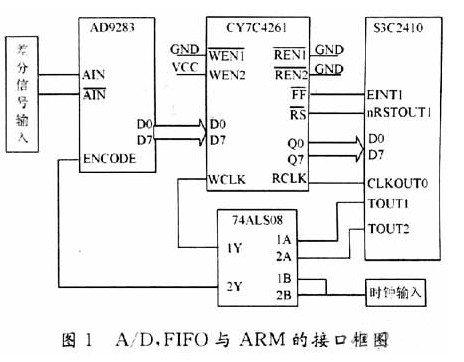

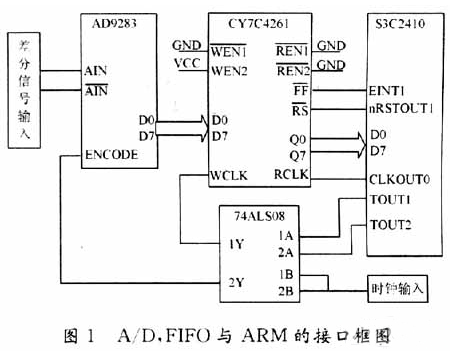

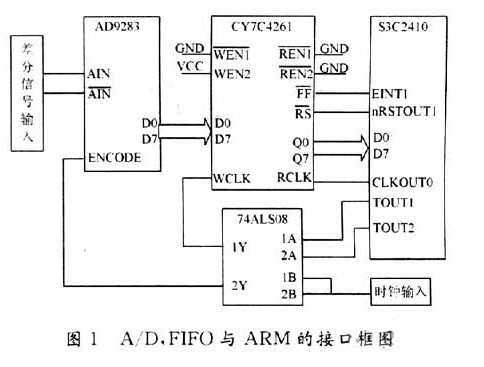

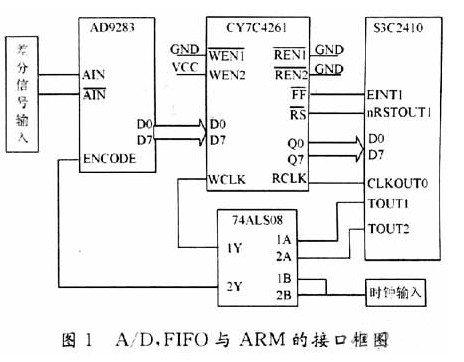

的超聲波測厚系統中,所用為1MHz以上的高頻超聲波探頭,測量數據經A/D轉換后頻率與ARM處理器的數據接收能力不匹配,因此需在A/D與ARM處理之間連接一個FIFO來解決以上問題。該設計選用AD公司的A

2020-12-28 06:55:06

。系統硬件電路包括ARM7處理器以及外圍的模擬、數字電路,并采用模塊化進行設計。這種思想大大簡化了系統硬件電路設計的復雜性,增強了系統的穩定性與可靠性。軟件部分根據超聲波信號的特點,選用新型的構造包絡

2023-09-26 07:08:07

在FPGA系統中,實現對外部A/D數據采集電路的控制接口邏輯,由于其邏輯功能不是很復雜,因此可采用自定義的方式。采用這種方法進行設計有兩種途徑。①從軟件上去實現。這種方案將NIOS處理器作為一個主控

2019-04-17 07:00:01

在FPGA系統中,實現對外部A/D數據采集電路的控制接口邏輯,由于其邏輯功能不是很復雜,因此可采用自定義的方式。采用這種方法進行設計有兩種途徑。①從軟件上去實現。這種方案將NIOS處理器作為一個主控

2019-04-25 07:00:02

在FPGA系統中,如何實現對外部A/D數據采集電路的控制接口邏輯?如何設計NIOS系統外設方面?

2021-04-12 07:16:31

嗨,伙計們,最近,我正在開發一個USB項目,其中CY7C68013A-128AXC被用來通過奴隸FIFO接口與FPGA通信,在68013中,EP2被配置為512字節雙緩沖Mulnual OFF

2019-03-01 14:17:46

首先介紹了多路數據采集系統的總體設計、FIFO芯片IDT7202。然后分別分析了FIFO與CPLD、AD接口的設計方法。由16位模數轉換芯片AD976完成模擬量至位數字量的轉換,由ATERA公司

2020-12-31 07:52:43

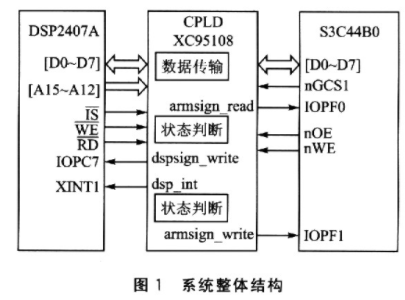

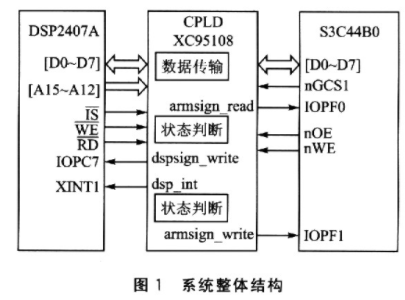

本文介紹了使用ARM和DSP雙CPU構成的雙核嵌入式系統的硬件平臺,以及源代碼開放的Linux作為嵌入式系統中操作系統的方法,給出了系統設計的總體框圖,詳細介紹了ARM和DSP通信接口的設計。

2021-05-26 06:21:39

、實時時鐘、A/D轉換器以及D/A轉換器等芯片的讀寫。本文根據實際工程中的應用需求,用ARM芯片LPC2378的GPIO來模擬SPI接口,以實現對外圍SPI接口器件的操作。其中,D/A轉換是系統中的一個

2019-08-15 06:32:58

超聲波測距原理是什么?怎么實現基于stm32最小系統的超聲波測距的設計?

2021-11-08 08:44:26

使用。完成物理上的連接更換后,我們接下來的是要明白超聲波的使用原理,和如何程序設計,使其實現。1.超聲波使用原理概括CT107D開發板上分別有發射聲波模塊和接收聲波模塊。發射模塊,通過P10(A

2021-12-10 07:29:32

最近要設計一個超聲波測厚儀,導師說超聲測厚的產品已經非常成熟,可以直接用市場上成套的超聲測厚芯片組,但是我沒有找到什么成套的芯片組。大神們,幫忙看看,真的有所謂的成套芯片組嗎?

2017-07-09 19:13:25

的更加形象的方式圖 4 超聲 A 、 B 、 C 掃描顯示方式四、基于 ARM實現方案ARM 后處理系統的硬件結構如下圖所示。 ARM 的高性能的處理能力和較強的內存管理技術能有效完成數據的后處理

2020-07-10 15:11:09

求助,哪位大哥做過超聲波側厚,求指導,小弟感激不盡

2015-05-28 18:30:06

求助,誰做過超聲波側厚或者測水位的,這個和測距有什么區別,求分享一個源碼

2019-06-17 02:37:49

怎么實現A/D數據采集接口的設計?

2021-04-20 07:19:20

FIFO芯片。芯片的存儲空間是2K×9 bit,讀寫時間最小是10ns。其主要的控制管腳功能如表1所示。3.接口電路的CPLD實現通過上面的介紹,可以大致歸納出接口電路需要實現的主要功能如下:(1)將A/D

2019-05-23 05:01:08

用A/D轉換器實現鉑電阻溫度計的非線性校正

A/D Converter Based Nonlinear Correction for Platinum-resistance Thermometer

2009-03-16 14:15:52 51

51 用簡單的D A轉換器電路來實現恒定線性速度的電機速度控制:

2009-06-12 15:52:10 14

14 介紹了串行A/D、D/A 芯片 MAX1270 和DAC7734E,對于DSP 上的串行接口McBSP(多通道緩沖串口)進行了細致的說明,給出了TMS320C6713 與串行A/D、D/A 接口芯片的硬件設計及軟件實現。關鍵詞:D

2009-08-11 09:16:45 33

33 提出了以工業級ARM9 芯片為核心的嵌入式控制系統設計實現方案。分析一般工業控制器需求,給出了控制系統總體方案,詳細設計了A/D、D/A、CAN、USB 和網絡等硬件電路及模塊化軟

2009-08-13 14:12:05 19

19 A7105 Reference code for FIFO mode:1. 簡介這文件系對 RF chip -A7105 FIFO mode 做一簡單的應用范程序,供使用者能夠快速應用這 RF chip。2. 系統概述本范程序使用簡單的跳頻(frequency hop

2009-09-29 10:22:17 37

37 用MC68HC705J1A實現超聲波汽車倒泊防撞報警器的設計MC68HC705J1A單片機的特點和性能,給出了超聲波汽車倒泊防撞報介紹了警器的設計方法和思路,并分析了超聲波測距的原理,討論了

2009-10-01 22:06:41 16

16 介紹了PCI 9054 接口芯片的性能及數據傳輸特點,提出了一種基于PCI 9054 外擴異步FIFO(先進先出)的FPGA(現場可編程門陣列)實現方法。由于PCI 9054 內部FIFO存儲器主要用于數據

2010-01-06 15:20:10 44

44 本文主要研究了用FPGA 芯片內部的EBRSRAM 來實現異步FIFO 設計方案,重點闡述了異步FIFO 的標志信號——空/滿狀態的設計思路,并且用VHDL 語言實現,最后進行了仿真驗證。

2010-01-13 17:11:58 40

40 基于SRAM 和DRAM 結構的大容量FIFO 的設計與實現作者:楊奇 楊瑩摘要:本文分別針對Hynix 公司的兩款SRAM 和DRAM 器件,介紹了使用CPLD 進行接口連接和編程控制,來構成低成本

2010-02-06 10:41:10 45

45 在NIOS-II 系統中A/D 數據采集接口的設計與實現摘要:進行 SOPC 開發,很有必要學習一下定制NIOS 外設的方法和技巧。本文就是基于這種目的,詳細的論述了在NIOS 系統中A/D 數據

2010-02-08 09:55:43 23

23 介紹了異步FIFO在Camera Link接口中的應用,將Camera Link接口中的幀有效信號FVAL和行有效信號LVAL引入到異步FIFO的設計中。分析了FPGA中設計異步FIFO的難點,解決了異步FIFO設計中存在的兩

2010-07-28 16:08:06 32

32 以CPLD為邏輯控制核心實現了ADS8323與高速FIFO的接口電路,該電路具有可靠性高、通用性強、易于移植等特點。在設計過程中,以QuartusII作為開發環境,采用圖形輸入和Verilog HDL語言輸

2010-08-06 14:25:53 22

22 介紹一種以ARM處理器LPC2138為核心,采用超聲波回波信號的A/D采樣檢測原理,實時測距,液晶屏顯示的便攜式系統。該系統利用ARM處理器處理速度快的優點,自行處理A/D采樣速度。系統

2010-12-27 10:14:19 44

44 1 前言在使用CCD對非透明薄板厚度的測量系統設計中,筆者采用高速A/D和DSP等器件設計信號采集和處理電路來確

2006-03-13 14:17:13 1891

1891

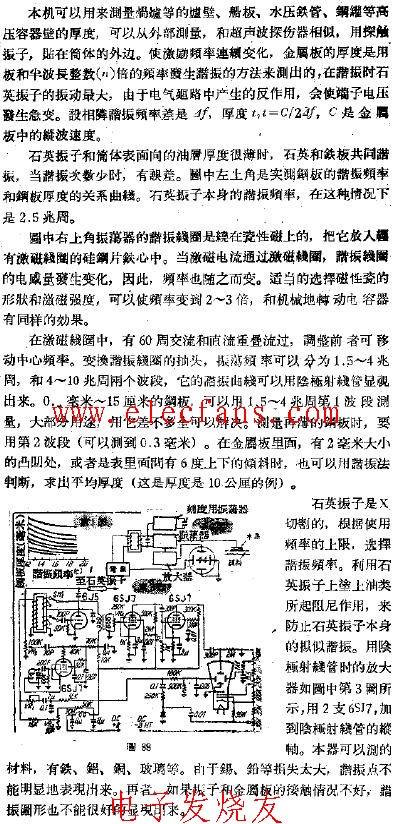

超聲波測厚計電路

超聲波測厚計電路

2008-04-30 23:49:55 1648

1648

ARM的A/D接口實驗

一、 實驗目的1.熟悉ARM 本身自帶的八路十位A/D 控制器及相應寄存器。2.編程實現ARM 系統的A/D 功能。3.掌

2008-12-25 23:45:19 3418

3418

【摘 要】 針對某脈沖警戒雷達設計了一種新的基于單倍FIFO存儲空間的乒乓存儲電路,實現了DSP與A/D、D/A之間的數據交換。 &

2009-05-10 20:02:41 1014

1014

高速異步FIFO的設計與實現

引言

現代集成電路芯片中,隨著設計規模的不斷擴大.一個系統中往往含有數個時鐘。多時鐘帶來的一個問題就是,如何設

2010-04-12 15:13:08 3176

3176

FPGA設計的高速FIFO電路技術

本文主要介紹高速FIFO電路在數據采集系統中的應用,相關電路主要有高速A/D轉換器、FPGA、SDRAM存儲器等。圖1為本方案的結構框圖。在大容量

2010-05-27 09:58:59 2978

2978

1 FIFO概述

FIFO芯片是一種具有存儲功能的高速邏輯芯片,可在高速數字系統中用作數據緩存。FIFO通常利用雙口RAM和讀寫地址產生模塊來實現其功能。FIFO的接口信號包括異步

2010-08-06 10:22:04 5679

5679

超聲波電纜測厚系統 在日益激烈的市場競爭中,如何降低成本是每個企業亟待解決的問題,而原材料的節省無疑是首要考慮的因素。 對于電纜生產企業而言,在降低成本的同時,保證企業產品質量顯得尤為重要,CMEASURE超聲波測量厚系統的出現正好滿足了市場對兩者

2011-02-28 16:41:36 67

67 基于ARM的智能導航盲杖系統設計_本文介紹了一種ARM硬盤接口應用知識新的實現方法。

2011-09-21 15:24:26 2559

2559

詳細介紹了TMS320C6205讀取FIFO中數據的速度以及如何設置EMIF的CExCTL寄存器的接口時序。

2011-11-30 11:45:00 4609

4609

自定義fifo接口控制器,利用sopc builder實現。

2016-03-22 14:09:34 1

1 DSP 相連, DSP 通過脈沖觸發模式從FIFO 中讀取數據塊。介紹如何使用SN74ALVC7806 FIFO 實現TMS320C6201 與模數轉換器的接口。 DSP 已經廣泛應用在數字信號處理系統里

2017-05-31 16:09:36 3

3 本文將介紹一種基于 ARM 的高精度多路同步的數據采集與輸出控制系統的設計方法。本設計選用德州儀器公司生產的AD芯片ADS8556和DA芯片DAC8574,分別采用SPI接口和IIC接口與ARM

2017-10-16 16:20:58 3

3 基于FIFO的高速A_D和DSP接口設計

2017-10-19 14:10:23 9

9 在現代的集成電路芯片中,隨著設計規模的不斷擴大,一個系統中往往含有數個時鐘。多時鐘域帶來的一個問題就是,如何設計異步時鐘之間的接口電路。異步FIFO(Firstln F irsto ut)是解決這個

2018-02-07 14:22:54 0

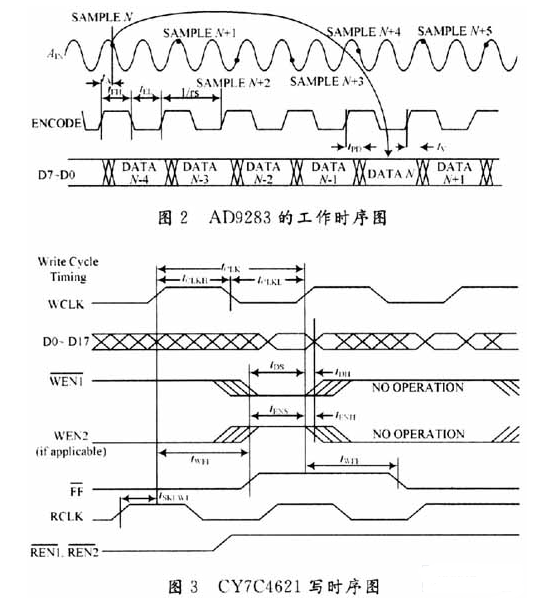

0 在超聲波無損檢測系統中,超聲波探頭的頻率一般是2~10 MHz。取探頭頻率為5 MHz,根據采樣定理,采樣頻率最好是探頭頻率的5~8倍,因此A/D芯片選用AD公司的AD9283,它的最大采樣速率達100 MHz,可以滿足系統要求。

2019-02-15 14:01:43 2362

2362

S3C2410處理器是Samsung公司基于ARM公司的ARM920T處理器核,采用0.18μm制造工藝的32位微控制器。該處理器擁有:獨立的16 KB指令Cache和16 KB數據CACHE

2019-02-20 15:25:09 2226

2226

實驗內容與任務:根據所學知識,設計一套基于單片機控制的智能超聲波測厚系統。基本要求為:(1)產生振動頻率為 20 kHz 的超聲波脈沖。(2)通過產生階梯波和小斜波,獲得步進系統的取樣信號,經 A

2019-06-14 16:35:43 6591

6591 在高頻超聲波數據采集系統中,很多高速A/D轉換器往往不能直接與處理器相連接,這時就需要使用FIFO在處理器與A/D轉換器之間架一座橋梁,FIFO的先入先出特性可以方便緩存大量的數據塊。

2019-11-05 15:54:54 2965

2965

7從FIFO中讀出,然后通過ARM7的以太網接口或者RS232送給上位機。考慮到要監控的設備可能會很多,所以設計了多路采集通道,他們經過模擬開關后再進入A/D轉換器。CPLD是整個系統的控制核心,他控制

2020-03-07 10:19:07 758

758

本文討論了一種基于32位微處理器ARM9E和嵌入式Linux的便攜式超聲診斷儀的解決方案。系統以CMOS圖像通道為診斷網像的傳輸通道,將采集的超聲圖像信息送人系統總線,在嵌入式Linux操作系統平臺

2020-03-11 09:20:52 2273

2273 無損檢測在工程領域應用越來越廣,超聲波檢測是無損檢測的主要方法之一,主要應用在測距、探傷、測厚等領域。超聲波具有方向性集中、振幅小、加速度大等特點,可產生較大能量,并且在不同的媒質介面,超聲波的大部分能量會反射。利用該特性,可以實現超聲測距和超聲探傷。

2021-03-26 09:33:56 7526

7526

A/D與D/A轉換接口教程說明分享。

2021-03-30 10:01:58 9

9 基于ARM和FPGA的嵌入式超聲探傷系統,進行數字信號處理,利用TCP/IP協議實現C/S模式下的數據傳輸,實現了超聲探傷的跨

2021-06-12 21:57:00 2441

2441

在現代汽車電子中,一般有多個微控制器共同協調工作。DSP控制器采用哈佛結構,運算速度快,所以在汽車電子中廣泛采用DSP芯片來實現汽車動力系統的控制。ARM是一種32位微控制器,有豐富的外擴接口

2021-06-23 14:43:16 5602

5602

ARM與FPGA的接口實現的解析(應廣單片機)-該文檔為ARM與FPGA的接口實現的解析詳述資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-22 09:47:55 14

14 FIFO的分類根均FIFO工作的時鐘域,可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時鐘和寫時鐘為同一個時鐘。在時鐘沿來臨時同時發生讀寫操作。異步FIFO是指讀寫時鐘不一致,讀寫時鐘是互相獨立的。

2022-11-01 09:57:08 2859

2859 同步FIFO的意思是說FIFO的讀寫時鐘是同一個時鐘,不同于異步FIFO,異步FIFO的讀寫時鐘是完全異步的。同步FIFO的對外接口包括時鐘,清零,讀請求,寫請求,數據輸入總線,數據輸出總線,空以及滿信號。

2022-11-01 09:58:16 2461

2461 簡單的一種,其特點是輸入和輸出都與時鐘信號同步,當時鐘到來時,數據總是處于穩定狀態,因此容易實現數據的傳輸和存儲。 而異步FIFO則是在波形的上升沿和下降沿上進行處理,在輸入輸出端口處分別增加輸入和輸出指針,用于管理數據的讀寫。異步FIFO的輸入和輸出可同時進行,中間可以

2023-10-18 15:23:58 2603

2603

電子發燒友App

電子發燒友App

評論