鎖相環(huán)電路

鎖相環(huán)

2009-09-25 14:28:39 7723

7723

本文采用一種基于比例積分(PI)控制算法的環(huán)路濾波器應(yīng)用于帶寬自適應(yīng)的全數(shù)字鎖相環(huán),建立了該鎖相環(huán)的數(shù)學(xué)模型

2010-10-14 10:03:25 1792

1792

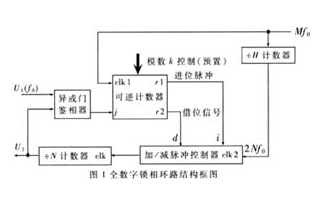

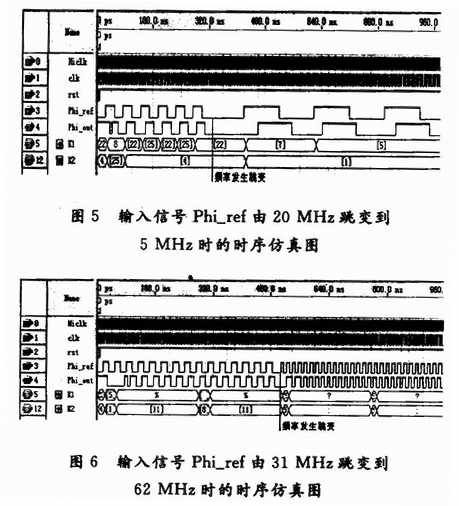

本文在說(shuō)明全數(shù)字鎖相環(huán)的基礎(chǔ)上,提出了一種利用FPGA設(shè)計(jì)一階全數(shù)字鎖相環(huán)的方法,并給出了關(guān)鍵部件的RTL可綜合代碼,并結(jié)合本設(shè)計(jì)的一些仿真波形詳細(xì)描述了數(shù)字鎖相環(huán)的工作過(guò)程,最后對(duì)一些有關(guān)

2018-10-25 09:17:13 9370

9370 大家都知道鎖相環(huán)很重要,它是基石,鎖相環(huán)決定了收發(fā)系統(tǒng)的基礎(chǔ)指標(biāo),那么如此重要的鎖相環(huán)選型原則有哪些呢?

2023-08-01 09:37:05 7303

7303

本文設(shè)計(jì)了一種寬頻率范圍的CMOS鎖相環(huán)(PLL)電路,通過(guò)提高電荷泵電路的電流鏡鏡像精度和增加開(kāi)關(guān)噪聲抵消電路,有效地改善了傳統(tǒng)電路中由于電流失配、電荷共享、時(shí)鐘饋通等導(dǎo)致的相位偏差問(wèn)題。設(shè)計(jì)了

2019-07-08 07:37:37

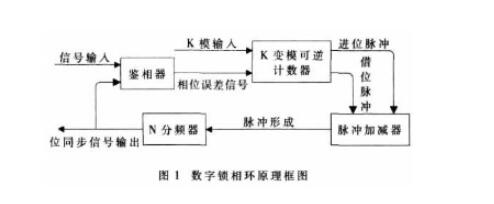

全數(shù)字鎖相環(huán)的設(shè)計(jì)及分析 1 引 言 鎖相環(huán)是一種能使輸出信號(hào)在頻率和相位上與輸入信號(hào)同步的電路,即系統(tǒng)進(jìn)入鎖定狀態(tài)(或同步狀態(tài))后,震蕩器的輸出信號(hào)與系統(tǒng)輸入信號(hào)之間相差為零,或者保持為常數(shù)

2010-03-16 10:56:10

本文按照數(shù)字鎖相環(huán)設(shè)計(jì)的步驟,采用手把手的方式講述設(shè)計(jì)過(guò)程和原理,旨在給數(shù)字鎖相環(huán)初次設(shè)計(jì)者提供一個(gè)思路,縮短開(kāi)發(fā)的時(shí)間。 有關(guān)數(shù)字鎖相環(huán)的帖子不斷出現(xiàn),但大多沒(méi)有講述其原理。翻開(kāi)有關(guān)鎖相環(huán)的書(shū)總是

2012-01-12 15:29:12

數(shù)字鎖相環(huán)設(shè)計(jì)源程序PLL是數(shù)字鎖相環(huán)設(shè)計(jì)源程序, 其中, Fi是輸入頻率(接收數(shù)據(jù)), Fo(Q5)是本地輸出頻率.目的是從輸入數(shù)據(jù)中提取時(shí)鐘信號(hào)(Q5), 其頻率與數(shù)據(jù)速率一致, 時(shí)鐘上升沿鎖定在數(shù)據(jù)的上升和下降沿上;頂層文件是PLL.GDF

2009-12-18 10:37:37

電荷泵鎖相環(huán)的基本原理是什么?電荷泵鎖相環(huán)的噪聲模型與相位噪聲特性是什么?電荷泵鎖相環(huán)的相位噪聲與環(huán)路帶寬關(guān)系是什么?

2021-06-07 06:57:53

LabVIEW鎖相環(huán)(PLL) 鎖相環(huán)是一種反饋電路,其作用是使得電路上的時(shí)鐘和某一外部時(shí)鐘的相位同步。PLL通過(guò)比較外部信號(hào)的相位和由壓控晶振(VCXO)的相位來(lái)實(shí)現(xiàn)同步的,在比較的過(guò)程中,鎖相環(huán)

2022-05-31 19:58:27

摘要:數(shù)字三相鎖相環(huán)中含有大量乘法運(yùn)算和三角函數(shù)運(yùn)算,占用大量的硬件邏輯資源。為此,提出一種數(shù)字三相鎖相環(huán)的優(yōu)化實(shí)現(xiàn)方案,利用乘法模塊復(fù)用和CORDIC算法實(shí)現(xiàn)三角函數(shù)運(yùn)算,并用Vetilog

2019-06-27 07:02:23

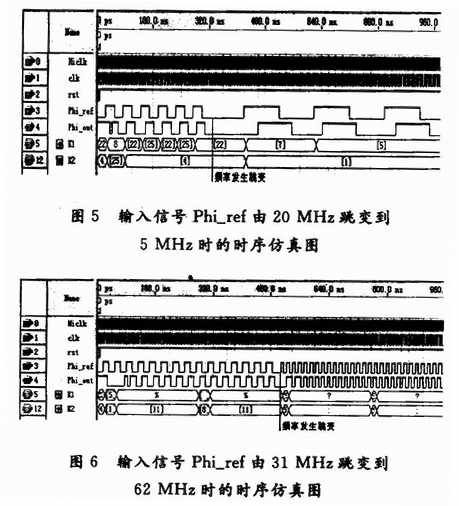

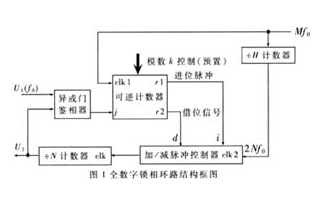

隨著集成電路技術(shù)的不斷進(jìn)步,數(shù)字化應(yīng)用逐漸普及,在數(shù)字通信、電力系統(tǒng)自動(dòng)化等方面越來(lái)越多地運(yùn)用了數(shù)字鎖相環(huán)。它的好處在于免去了模擬器件的繁瑣,而且成本低、易實(shí)現(xiàn)、省資源。本文綜合以上考慮,在一片F(xiàn)PGA中以Quartus II為平臺(tái)用VHDL實(shí)現(xiàn)了一個(gè)全數(shù)字鎖相環(huán)功能模塊,構(gòu)成了片內(nèi)鎖相環(huán)。

2019-10-10 06:12:52

DLL架構(gòu)和工作原理是什么?如何設(shè)計(jì)一種新延時(shí)鎖相環(huán)架構(gòu)OSDLL?

2021-05-07 06:17:59

鎖相環(huán)系統(tǒng)是什么工作原理?傳統(tǒng)電荷泵電路存在的不理想因素有哪些?設(shè)計(jì)一種高性能CMOS電荷泵鎖相環(huán)電路

2021-04-09 06:38:45

全數(shù)字鎖相環(huán)由那幾部分組成?數(shù)字鎖相環(huán)的原理是什么?如何采用VHDL實(shí)現(xiàn)全數(shù)字鎖相環(huán)電路的設(shè)計(jì)?

2021-05-07 06:14:44

控制用微處理器的主要性能有哪些?處理器在調(diào)頻(FM)調(diào)諧器中的應(yīng)用是什么?數(shù)字調(diào)諧系統(tǒng)有哪些性質(zhì)?怎樣去設(shè)計(jì)一種基于PLL(鎖相環(huán))合成器的數(shù)字調(diào)諧系統(tǒng)?

2021-08-17 07:03:36

模擬鎖相環(huán)與數(shù)字鎖相環(huán)的主要區(qū)別在哪里?

2023-04-24 10:48:52

經(jīng)典數(shù)字鎖相環(huán)路結(jié)構(gòu)及工作原理是什么?改進(jìn)的數(shù)字鎖相環(huán)結(jié)構(gòu)及工作原理是什么怎樣對(duì)改進(jìn)的數(shù)字鎖相環(huán)進(jìn)行仿真?

2021-04-20 06:47:12

求一種新型WCDMA直放站PA的設(shè)計(jì)方案

2021-05-26 06:14:52

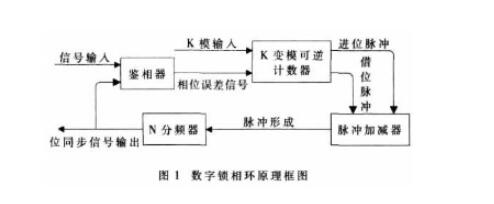

求一種基于FPGA的鎖相環(huán)位同步提取電路的設(shè)計(jì)方案。

2021-04-29 06:52:21

數(shù)字鎖相環(huán)頻率合成系統(tǒng)的工作原理CPU控制數(shù)字鎖相環(huán)頻率合成系統(tǒng)FPGA實(shí)現(xiàn)

2021-04-09 06:20:37

本文主要研究了一種基于FPGA、自頂向下、模塊化、用于提取位同步時(shí)鐘的全數(shù)字鎖相環(huán)設(shè)計(jì)方法。

2021-05-06 08:00:46

怎么設(shè)計(jì)一種用于多路輸出時(shí)鐘緩沖器中的鎖相環(huán)?鎖相環(huán)主要結(jié)構(gòu)包括哪些?

2021-04-20 06:27:26

怎樣去設(shè)計(jì)一種自適應(yīng)軟件鎖相環(huán)?如何對(duì)自適應(yīng)軟件鎖相環(huán)進(jìn)行測(cè)試?

2021-06-08 07:07:17

怎樣去設(shè)計(jì)一種COMS集成鎖相環(huán)電路?

2021-06-22 07:37:23

本文針對(duì)一款應(yīng)用于大規(guī)模集成電路的CMOS高頻鎖相環(huán)時(shí)鐘發(fā)生器,提出了一種可行的測(cè)試方案,重點(diǎn)講述了鎖相環(huán)的輸出頻率和鎖定時(shí)間參數(shù)的測(cè)試,給出了具體的測(cè)試電路和測(cè)試方法。對(duì)于應(yīng)用在大規(guī)模電路系統(tǒng)中的鎖相環(huán)模塊,該測(cè)試方案既可用于鎖相環(huán)的性能評(píng)測(cè),也可用于鎖相環(huán)的生產(chǎn)測(cè)試。

2021-04-21 06:28:15

智能全數(shù)字鎖相環(huán)的設(shè)計(jì)

摘要: 在FPGA片內(nèi)實(shí)現(xiàn)全數(shù)字

2008-08-14 22:12:51 56

56 根據(jù)虛擬無(wú)線電技術(shù)的特點(diǎn)和鎖相環(huán)的基本原理,提出一種適于計(jì)算機(jī)軟件化實(shí)現(xiàn)的鎖相環(huán)數(shù)學(xué)模型,分析不同參數(shù)對(duì)鎖相環(huán)捕獲和跟蹤性能的影響,得出不同情況下參數(shù)設(shè)定的基

2008-08-15 12:36:19 101

101 智能全數(shù)字鎖相環(huán)的設(shè)計(jì):在FPGA片內(nèi)實(shí)現(xiàn)全數(shù)字鎖相環(huán)用途極廣。本文在集成數(shù)字鎖相環(huán)74297的基礎(chǔ)上進(jìn)行改進(jìn),設(shè)計(jì)了鎖相狀態(tài)檢測(cè)電路,配合CPU對(duì)環(huán)路濾波參數(shù)進(jìn)行動(dòng)態(tài)智能配

2009-06-25 23:32:57 72

72 基于FPGA的全數(shù)字鎖相環(huán)設(shè)計(jì):

2009-06-26 17:30:59 145

145 一種FPGA時(shí)鐘網(wǎng)絡(luò)中鎖相環(huán)的實(shí)現(xiàn)方案:摘 要:本文闡述了用于FPGA 的可優(yōu)化時(shí)鐘分配網(wǎng)絡(luò)功耗與面積的時(shí)鐘布線結(jié)構(gòu)模型。并在時(shí)鐘分配網(wǎng)絡(luò)中引入數(shù)字延遲鎖相環(huán)減少時(shí)鐘偏差,探

2009-08-08 09:07:22 25

25 本文在介紹了經(jīng)典全數(shù)字鎖相環(huán)(all digital PLL, ADPLL)的基礎(chǔ)上,提出了具有捕獲鎖定未知輸入信號(hào)頻率功能的ADPLL,使用方便,應(yīng)用廣泛。本文詳盡的描述了系統(tǒng)的工作原理和關(guān)

2009-08-29 10:07:08 43

43 鎖相環(huán)設(shè)計(jì)舉例:鎖相環(huán)設(shè)計(jì)主要包括:確定所需環(huán)的類(lèi)型,選擇適當(dāng)?shù)?b class="flag-6" style="color: red">帶寬,指出希望的穩(wěn)定度。下面將舉例說(shuō)明要滿足這些設(shè)計(jì)要求而常用的基本方法。

2009-09-05 08:51:42 105

105 該文簡(jiǎn)要討論了環(huán)路性能(建立時(shí)間,相位噪聲和雜散信號(hào))和環(huán)路參數(shù)(帶寬,相位裕度等)的相互關(guān)系。提出并分析了一種自適應(yīng)的具有快速建立時(shí)間的鎖相環(huán)結(jié)構(gòu)及其關(guān)鍵模塊(鑒相

2010-04-23 08:33:53 20

20 鎖相環(huán)被廣泛應(yīng)用于電力系統(tǒng)的測(cè)量和控制中。介紹了一種新型的基于比例積分控制邏輯的全數(shù)字鎖相環(huán)。通過(guò)對(duì)其數(shù)學(xué)模型的分析,闡述了該鎖相環(huán)的各項(xiàng)性能指標(biāo)與設(shè)計(jì)參數(shù)的

2010-07-02 16:54:10 30

30 本文在分析商用全數(shù)字鎖相環(huán)的常用技術(shù)和低頻信號(hào)的特點(diǎn)后,提出一種適用于低頻信號(hào)的基于CPLD的鎖相環(huán)實(shí)現(xiàn)方法。

2010-08-06 14:39:19 118

118 介紹了應(yīng)用VHDL技術(shù)設(shè)計(jì)嵌入式全數(shù)字鎖相環(huán)路的方法。詳細(xì)描

2010-09-19 10:09:14 68

68 數(shù)字三相鎖相環(huán)中含有大量乘法運(yùn)算和三角函數(shù)運(yùn)算,占用大量的硬件邏輯資源。為此,提出一種數(shù)字三相鎖相環(huán)的優(yōu)化實(shí)現(xiàn)方案,利用乘法模塊復(fù)用和CORDIC算法實(shí)現(xiàn)三角函數(shù)運(yùn)算

2010-09-30 16:35:54 35

35

利用鎖相環(huán)進(jìn)行載波跟蹤是獲取本地載波的一種重要方法,針對(duì)鎖相環(huán)的噪聲性能和跟蹤速度不能同時(shí)達(dá)到最優(yōu)的限制,在鎖相環(huán)PLL中引入自適應(yīng)模塊,根據(jù)環(huán)路所處

2010-11-25 17:19:33 29

29 針對(duì)交通系統(tǒng)中十字路口處車(chē)輛的分道行駛管理,提出一種利用鎖相環(huán)技術(shù)提高感測(cè)裝置靈敏度及抗干擾能力的設(shè)計(jì)方案。該設(shè)計(jì)方案通過(guò)檢測(cè)鎖相環(huán)失鎖來(lái)判定是否有車(chē)量經(jīng)過(guò),具

2010-12-22 17:16:43 0

0 鎖相環(huán)原理

鎖相環(huán)路是一種反饋電路,鎖相環(huán)的英文全稱(chēng)是Phase-Locked Loop,簡(jiǎn)稱(chēng)PLL。其作用是使得電路上的時(shí)鐘和某一外部時(shí)鐘的相位同步。因鎖相環(huán)可以

2007-08-21 14:46:04 5484

5484 實(shí)驗(yàn)五? 數(shù)字鎖相環(huán)與位同步

一、?實(shí)驗(yàn)?zāi)康?

??? 1. 掌握數(shù)字鎖相環(huán)工作原理以及觸發(fā)式數(shù)字鎖

2009-04-01 09:27:45 6242

6242

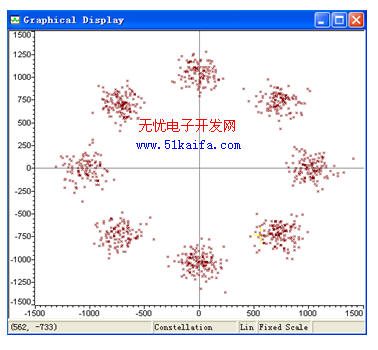

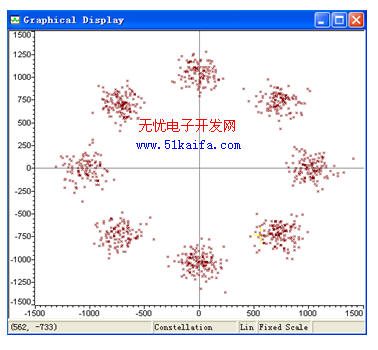

基于DSP的高階COSTAS鎖相環(huán)的設(shè)計(jì)

COSTAS環(huán)是一種閉環(huán)自適應(yīng)系統(tǒng),用于提取相干載波。本文主要介紹了一種用于載波同步的高階COSTAS環(huán)路,用于完成MPSK的相干解調(diào)中的載

2009-05-25 18:15:36 1619

1619

摘要: 在FPGA片內(nèi)實(shí)現(xiàn)全數(shù)字鎖相環(huán)用途極廣。本文在集成數(shù)字鎖相環(huán)74297的基礎(chǔ)上進(jìn)行改進(jìn),設(shè)計(jì)了鎖相狀態(tài)檢測(cè)電路,配合CPU對(duì)環(huán)路濾波參數(shù)進(jìn)行動(dòng)態(tài)智

2009-06-20 12:39:32 1760

1760

鎖相環(huán)(PLL),鎖相環(huán)(PLL)是什么意思

PLL的概念

我們所說(shuō)的PLL。其

2010-03-23 10:47:48 6368

6368 數(shù)字鎖相環(huán)(DPLL),數(shù)字鎖相環(huán)(DPLL)是什么?

背景知識(shí):

隨著數(shù)字電路技術(shù)的發(fā)展,數(shù)字鎖相環(huán)在調(diào)制解調(diào)、頻率合成、FM 立體聲解碼、彩色副

2010-03-23 15:06:21 6110

6110 模擬鎖相環(huán),模擬鎖相環(huán)原理解析

背景知識(shí):

鎖相技術(shù)是一種相位負(fù)反饋控制技術(shù),它利用環(huán)路的反饋原理來(lái)產(chǎn)生新的頻率點(diǎn)。它的主要

2010-03-23 15:08:20 6264

6264 本文鑒于 數(shù)字鎖相環(huán) 在實(shí)際應(yīng)用中對(duì)信號(hào)頻率的準(zhǔn)確度和穩(wěn)定度有較為嚴(yán)格的要求,設(shè)計(jì)一種應(yīng)用于數(shù)字鎖相環(huán)的數(shù)控振蕩器(NCO,Number Controlled Oscillator)。基于直接數(shù)字頻率合成(

2011-08-05 14:51:05 79

79 針對(duì)擴(kuò)頻通信系統(tǒng)的載波同步,提出一套完善的數(shù)字鎖相環(huán)設(shè)計(jì)方案. 該方案利用新穎的可控根法完成1~3階模擬鎖相環(huán)(APLL)環(huán)路參數(shù)設(shè)計(jì),并實(shí)現(xiàn)從模擬域到數(shù)字域的轉(zhuǎn)換,得到的數(shù)字鎖相

2011-08-26 16:10:38 122

122 針對(duì)傳統(tǒng)的全數(shù)字鎖相環(huán)只能鎖定已知信號(hào)和鎖頻范圍較小的問(wèn)題, 提出了一種自動(dòng)變模控制的寬頻帶全數(shù)字鎖相環(huán)。對(duì)比分析了各類(lèi)全數(shù)字鎖相環(huán)鎖頻、鎖相的工作機(jī)理, 提出了一種新

2011-09-14 15:22:22 79

79 鎖相環(huán)英文為PLL,即PLL鎖相環(huán)。可以分為模擬鎖相環(huán)和數(shù)字鎖相環(huán)。兩種分類(lèi)的鎖相環(huán)原理有較大區(qū)別,通過(guò)不同的鎖相環(huán)電路實(shí)現(xiàn)不同的功能。

2011-10-26 12:40:28

研究了一種利用corid 算法的矢量及旋轉(zhuǎn)模式對(duì)載波同步中相位偏移進(jìn)行估計(jì)并校正的方法.設(shè)計(jì)并實(shí)現(xiàn)了基于corid 算法的數(shù)字鎖相環(huán).通過(guò)仿真驗(yàn)證了設(shè)計(jì)的有效性和高效性.

2012-02-09 16:48:30 18

18 利用鎖相環(huán)的等效噪聲模型,重點(diǎn)分析電荷泵鎖相環(huán)系統(tǒng)的相位噪聲特性,得出系統(tǒng)噪聲特性的分布特點(diǎn)以及與環(huán)路帶寬的關(guān)系。

2012-11-22 10:44:47 23975

23975 有關(guān)鎖相環(huán)的部分資料,對(duì)制作鎖相環(huán)有一定的幫助。

2015-10-29 14:16:55 70

70 基于FPGA的數(shù)字鎖相環(huán)設(shè)計(jì)與實(shí)現(xiàn)技術(shù)論文

2015-10-30 10:38:35 9

9 一種用于鎖相環(huán)的壓控振蕩器的設(shè)計(jì),參考資料。

2016-05-06 10:25:52 0

0 一種用于鎖相環(huán)的環(huán)形壓控振蕩器設(shè)計(jì),參考資料。

2016-05-06 10:25:52 0

0 一種用于光伏并網(wǎng)逆變器的高性能鎖相環(huán)設(shè)計(jì)_江燕興

2017-01-05 15:34:14 3

3 一種改進(jìn)的無(wú)鎖相環(huán)FBD諧波電流檢測(cè)方法_王清亮

2017-01-05 15:24:15 2

2 一種基于bang_bang鑒頻鑒相器的全數(shù)字鎖相環(huán)設(shè)計(jì)_陳原聰

2017-01-07 20:49:27 11

11 一種超高頻RFID閱讀器中的雙環(huán)鎖相環(huán)_粟恒智

2017-01-08 10:30:29 3

3 一、設(shè)計(jì)目標(biāo) 基于鎖相環(huán)的理論,以載波恢復(fù)環(huán)為依托搭建數(shù)字鎖相環(huán)平臺(tái),并在FPGA中實(shí)現(xiàn)鎖相環(huán)的基本功能。 在FPGA中實(shí)現(xiàn)鎖相環(huán)的自動(dòng)增益控制,鎖定檢測(cè),鎖定時(shí)間、失鎖時(shí)間的統(tǒng)計(jì)計(jì)算,多普勒頻偏

2017-10-16 11:36:45 19

19 為了能夠有效地治理諧波,提高電力系統(tǒng)中諧波信息的檢測(cè)精度,提出了自適應(yīng)鎖相環(huán)的分次諧波檢測(cè)優(yōu)化算法。首先,研究了改進(jìn)自適應(yīng)鎖相環(huán)的設(shè)計(jì)方法,并且構(gòu)造了相應(yīng)的數(shù)學(xué)模型;其次,設(shè)計(jì)了分次諧波檢測(cè)優(yōu)化算法

2017-10-30 16:16:15 11

11 鎖相環(huán)在通信、雷達(dá)、測(cè)量和自動(dòng)化控制等領(lǐng)域應(yīng)用極為廣泛,已經(jīng)成為各種電子設(shè)備中必不可少的基本部件。隨著電子技術(shù)向數(shù)字化方向發(fā)展,需要采用數(shù)字方式實(shí)現(xiàn)信號(hào)的鎖相處理。因此,對(duì)全數(shù)字鎖相環(huán)的研究和應(yīng)用得

2017-11-24 20:03:04 14190

14190

針對(duì)傳統(tǒng)數(shù)字鎖相環(huán)存在的反饋滯后造成系統(tǒng)動(dòng)、靜態(tài)性能退化的問(wèn)題,提出一種消除反饋滯后一拍的方法,以無(wú)反饋滯后理想數(shù)字鎖相環(huán)為參考模型,利用數(shù)字鎖相環(huán)當(dāng)前輸出與上一時(shí)刻輸出,計(jì)算得到與理想數(shù)字鎖相環(huán)

2018-01-02 10:30:41 9

9 ,也就是所謂的對(duì)電網(wǎng)電壓進(jìn)行鎖相。單相鎖相環(huán)( Single-phase Phase Locked Loop,SPLL)技術(shù)是目前應(yīng)用最廣泛的單相鎖相技術(shù)。 單相電網(wǎng)電壓信息的提取通常要比三相平衡電力系統(tǒng)更困難,這是因?yàn)樵谌嘞到y(tǒng)中,三相電網(wǎng)電壓可以通過(guò)坐

2018-03-14 14:37:57 0

0 對(duì)全數(shù)字控制的UPS系統(tǒng),結(jié)合鎖相環(huán)原理,提出了1種基于DSP T MS320F2808的高精度數(shù)字鎖相控制方案。

2018-04-08 15:44:34 16

16 是兩個(gè)非常重要的性能參數(shù),二者均取決于環(huán)路帶寬但是不能同時(shí)達(dá)到最優(yōu)。傳統(tǒng)鎖相環(huán)往往根據(jù)估算預(yù)先確定一個(gè)帶寬值,因而當(dāng)噪聲環(huán)境發(fā)生變化時(shí),該值可能不是最優(yōu)值,甚至不適

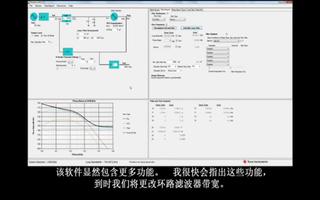

2018-10-07 11:27:27 3506

3506 EngineerIt-鎖相環(huán)應(yīng)用中的環(huán)路帶寬

2019-04-15 06:07:00 13946

13946

隨著集成電路技術(shù)的不斷進(jìn)步,數(shù)字化應(yīng)用逐漸普及,在數(shù)字通信、電力系統(tǒng)自動(dòng)化等方面越來(lái)越多地運(yùn)用了數(shù)字鎖相環(huán)。它的好處在于免去了模擬器件的繁瑣,而且成本低、易實(shí)現(xiàn)、省資源。本文綜合以上考慮,在一片F(xiàn)PGA中以Quartus II為平臺(tái)用VHDL實(shí)現(xiàn)了一個(gè)全數(shù)字鎖相環(huán)功能模塊,構(gòu)成了片內(nèi)鎖相環(huán)。

2020-07-16 09:16:08 3430

3430

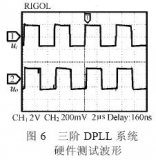

技術(shù)的發(fā)展,不僅能夠制成頻率較高的單片集成鎖相環(huán)路,而且可以把整個(gè)系統(tǒng)集成到一個(gè)芯片上去,實(shí)現(xiàn)所謂片上系統(tǒng)SOC(System on a chip)。因此,可以把全數(shù)字鎖相環(huán)路作為一個(gè)功能模塊嵌入SOC,構(gòu)成片內(nèi)鎖相環(huán)。下面介紹采用VHDL技術(shù)設(shè)計(jì)DPLL的一種方案。

2020-07-23 16:23:25 1784

1784

鎖相環(huán)路是一種反饋控制電路,簡(jiǎn)稱(chēng)鎖相環(huán)( PLL)。鎖相環(huán)的特點(diǎn)是:利用外部輸入的參考信號(hào)控制環(huán)路內(nèi)部振蕩信號(hào)的頻率和相位。因鎖相環(huán)可以實(shí)現(xiàn)輸出信號(hào)頻率對(duì)輸入信號(hào)頻率的自動(dòng)跟蹤, 所以鎖相環(huán)通常

2020-08-06 17:58:25 26

26 本文提出了一種適用范圍廣泛的全數(shù)字鎖相環(huán)(ADPLL)實(shí)現(xiàn)方法.在鎖相環(huán)輸入頻率未知的情況下,實(shí)現(xiàn)鎖相鎖頻功能。本文從全數(shù)字鎖相環(huán)的基本實(shí)現(xiàn)方式入手.進(jìn)行改進(jìn),并使用VH DL語(yǔ)言建模,使用FPGA進(jìn)行驗(yàn)證。

2021-01-26 15:03:00 66

66 本文提出了一種適用范圍廣泛的全數(shù)字鎖相環(huán)(ADPLL)實(shí)現(xiàn)方法.在鎖相環(huán)輸入頻率未知的情況下,實(shí)現(xiàn)鎖相鎖頻功能。本文從全數(shù)字鎖相環(huán)的基本實(shí)現(xiàn)方式入手.進(jìn)行改進(jìn),并使用VH DL語(yǔ)言建模,使用FPGA進(jìn)行驗(yàn)證。

2021-01-26 15:03:00 20

20 為了提高全數(shù)字鎖相環(huán)的系統(tǒng)運(yùn)行速度、降低系統(tǒng)功耗,同時(shí)提高鎖相系統(tǒng)的動(dòng)態(tài)性能與穩(wěn)態(tài)性能,提出一種基于流

2021-04-01 11:53:12 2635

2635

基于FPGA的高性能全數(shù)字鎖相環(huán)

2021-06-08 11:09:01 46

46 一種用MATLAB仿真鎖相環(huán)的方法資料分享。

2021-06-17 17:16:58 31

31 鎖相環(huán)路是一種反饋控制電路,簡(jiǎn)稱(chēng)鎖相環(huán)(PLL,Phase-Locked Loop)。鎖相環(huán)的特點(diǎn)是:利用外部輸入的參考信號(hào)控制環(huán)路內(nèi)部振蕩信號(hào)的頻率和相位。

2022-03-29 09:54:55 15826

15826 模擬鎖相環(huán)和數(shù)字鎖相環(huán)的主要區(qū)別在于它們的控制方式不同。模擬鎖相環(huán)是通過(guò)模擬電路來(lái)控制頻率和相位,而數(shù)字鎖相環(huán)是通過(guò)數(shù)字信號(hào)處理技術(shù)來(lái)控制頻率和相位。此外,模擬鎖相環(huán)的精度較低,而數(shù)字鎖相環(huán)的精度較高。

2023-02-15 13:47:53 6625

6625 pll鎖相環(huán)倍頻的原理? PLL鎖相環(huán)倍頻是一種重要的時(shí)鐘信號(hào)處理技術(shù),廣泛應(yīng)用于數(shù)字系統(tǒng)、通信系統(tǒng)、計(jì)算機(jī)等領(lǐng)域,具有高可靠性、高精度、快速跟蹤等優(yōu)點(diǎn)。PLL鎖相環(huán)倍頻的原理涉及到鎖相環(huán),倍頻器

2023-09-02 14:59:24 4879

4879 鎖相環(huán)是如何實(shí)現(xiàn)倍頻的?? 鎖相環(huán)(Phase Locked Loop, PLL)是一種電路,用于穩(wěn)定和恢復(fù)輸入信號(hào)的相位和頻率。它可以廣泛應(yīng)用于通信、計(jì)算機(jī)、音頻等領(lǐng)域中。其中一個(gè)重要的應(yīng)用就是

2023-09-02 14:59:37 5118

5118 pll鎖相環(huán)的作用 pll鎖相環(huán)的三種配置模式? PLL鎖相環(huán)是現(xiàn)代電子技術(shù)中廣泛應(yīng)用的一種電路,它的作用是將一個(gè)特定頻率的輸入信號(hào)轉(zhuǎn)換為固定頻率的輸出信號(hào)。PLL鎖相環(huán)的三種配置模式分別為

2023-10-13 17:39:48 5284

5284 什么是鎖相環(huán)?PLL和DLL都是鎖相環(huán)區(qū)別在哪里? 鎖相環(huán)(Phase Locked Loop,PLL)是一種基于反饋的控制系統(tǒng),用于提供穩(wěn)定的時(shí)鐘信號(hào)。它可以將參考信號(hào)的相位與輸出信號(hào)的相位進(jìn)行

2023-10-13 17:39:53 3088

3088 頻繁地開(kāi)關(guān)鎖相環(huán)芯片的電源會(huì)對(duì)鎖相環(huán)有何影響? 鎖相環(huán)(PLL)是一種被廣泛應(yīng)用在現(xiàn)代電子技術(shù)中的集成電路,它是一種反饋控制系統(tǒng),可以將輸入信號(hào)和本地參考信號(hào)同步。鎖相環(huán)可用于電子時(shí)鐘、數(shù)字信號(hào)處理

2023-10-30 10:16:40 1291

1291 電子發(fā)燒友網(wǎng)站提供《基于VHDL的全數(shù)字鎖相環(huán)的設(shè)計(jì).pdf》資料免費(fèi)下載

2023-11-10 09:47:34 0

0 V CO 輸出本地參考頻率。由于V CO 采用模擬電路, 這將帶來(lái)元件 飽和、直流漂移、非線性等問(wèn)題。因此, 全數(shù)字鎖相環(huán)得到了越來(lái)越廣泛的應(yīng)用。

本文介紹一種 DD S(D irect D igital Syn thesizer) 與 PLL (Phase L ocked L oop ) 技術(shù)

2023-11-09 08:31:40 2

2 數(shù)字鎖相環(huán)(DigitalPhase-LockedLoop,簡(jiǎn)稱(chēng)DPLL)是一種基于反饋控制的技術(shù),用于實(shí)現(xiàn)精確的時(shí)序控制和相位同步。通過(guò)相位比較、頻率差計(jì)算、頻率控制、濾波和循環(huán)控制,它能夠完成

2024-01-02 17:20:25 3358

3358

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論