在把射頻芯片或模塊集成到典型的嵌入式系統中時,設 計人員必須面臨的一項常見任務是追蹤和消除噪聲和雜 散信號。潛在的噪聲來源包括:開關電源、來自系統其 它部分的數字噪聲

2012-11-13 10:09:43 1619

1619 鎖相環 (PLL) 和壓控振蕩器 (VCO) 輸出特定頻率的RF信號,理想情況下此信號應當是輸出中的唯一信號。但事實上,輸出中存在干擾雜散信號和相位噪聲。本文討論最麻煩的雜散信號之一——整數邊界雜散,它如何仿真與消除,你真的搞清楚了?

2023-05-22 11:10:35 10630

10630

在整個PCBA生產制造過程中, PCB 設計是至關重要的一部分,今天主要是關于 PCB 雜散電容、影響PCB 雜散電容的因素,PCB 雜散電容計算,PCB雜散電容怎么消除。

2023-09-11 09:41:20 2916

2916

雖然目前的高分辨率SAR ADC和Σ-Δ ADC可提供高分辨率和低噪聲,但系統設計師們可能難以實現數據手冊上的額定SNR性能。而要達到最佳SFDR,也就是在系統信號鏈中實現無雜散的干凈噪底,可能

2019-02-14 14:18:45

大家好,問一個問題,在做一個測介電常數的系統,需要先測得電容,下午測試了一下雜散電容,然后對信號做頻譜分析發現里面的噪聲有工頻干擾,還有是信號頻率整數倍的噪聲,比如我的有用信號時100Hz的話,夾雜的噪聲有200、300、400Hz....請問什么情況下會有這類的噪聲產生,如何有效地去消除。謝謝。

2016-04-11 19:48:19

在把射頻芯片或模塊集成到典型的嵌入式系統中時,設計人員必須面臨的一項常見任務是追蹤和消除噪聲和雜散信號。潛在的噪聲來源包括:開關電源、來自系統其它部分的數字噪聲、以及外部噪聲來源。在考慮噪聲時,還應

2019-06-10 07:08:32

在大型數字波束合成天線中,人們非常希望通過組合來自分布式波形發生器和接收器的信號這一波束合成過程改善動態范圍。如果關聯誤差項不相關,則可以在噪聲和雜散性能方面使動態范圍提升10logN。這里的N

2021-05-08 07:30:00

嵌入式射頻系統基本上今天的每一個電子產品都是一個嵌入系統,小到電子表,大到各種復雜的控制系統。嵌入式系統實際上是專用的計算機系統,它的特征包括非PC,以應用為中心,以計算機技術為基礎,適用于應用系統對功能、可靠性、成本、體積、功耗有嚴格要求等。

2019-08-19 06:42:46

嵌入式射頻系統基本上今天的每一個電子產品都是一個嵌入系統,小到電子表,大到各種復雜的控制系統。嵌入式系統實際上是專用的計算機系統,它的特征包括非PC,以應用為中心,以計算機技術為基礎,適用于應用系統

2019-06-05 06:32:21

各位大神,我想請問嵌入式系統開發還要學習信號系統,DSP嗎?

2012-06-18 17:53:40

在嵌入式系統設計過程中,系統的掉電保護越來越受到重視。本文介紹的方法是在用ARM7系列芯片S3C4510B和μClinux構建的嵌入式平臺上實現的。整個掉電保護實現的基本思路是:產生掉電信號,捕捉掉電信號和處理掉電信號。重點介紹這個過程的具體實現。

2019-11-01 08:00:11

嵌入式系統中語音算法的基本原理是什么?嵌入式系統中語音算法有何功能?

2021-12-23 08:49:46

嵌入式系統EMC(Electro Magnetic Compatibility)即嵌入式系統電磁兼容性,指嵌入式系統在復雜電磁環境中抵抗其他系統所產生的電磁干擾同時本身產生的電磁干擾又不影響其他系統

2019-08-20 08:08:59

。由于嵌入式系統應用中,對象系統的廣泛性與單片機的獨主發展道路,使嵌入式系統應用在客觀上存在兩種模式,從學科建設上,可統一成嵌入式系統應用的高低端。 關鍵詞:嵌入式系統發展史 嵌入式系統定義 應用模式

2019-06-18 06:53:07

嵌入式系統的知識體系嵌入式系統的學習誤區嵌入式系統基礎階段的學習建議

2021-02-19 07:06:43

嵌入式系統和組件技術嵌入式系統組件的設計原則面向嵌入式組件的系統開發過程

2021-04-23 06:08:06

嵌入式系統設計調試的挑戰是什么?如何測試射頻信號與總線信號及控制信號的定時關系?

2021-05-11 06:50:22

惱人的雜散問題怎么破?雜散來源如何確定?...請參考本帖中列舉的相關實戰問題!在此版主將整理發布有關雜散的一問一答專題帖,將理論聯系到實際應用總結出可行方案!包括AD9914、HMC833...當然

2019-01-16 12:27:07

惱人的雜散問題怎么破?雜散來源如何確定?...請參考本帖中列舉的相關實戰問題!在此版主將整理發布有關雜散的一問一答專題帖,將理論聯系到實際應用總結出可行方案!當然鼓勵跟帖向大家分享你的實戰經驗~Q

2017-04-27 15:58:16

出現一個與基帶信號相關的雜散點幅度-50dBm左右,影響了射頻輸出的Sfdr。具體現象:

輸出2.2ghz點頻時,雜散點在2.6GHz

輸出2.3ghz點頻時,雜散在2.5ghz

輸出2.4ghz點頻

2023-12-04 07:39:16

各位大牛,請教一下。我現在用AD9467-250,采樣時鐘用AD9517-3出的200MHz,采集70M、0dBm單音信號。頻譜上出現較多的雜散。ADC前端電路按照AD9467手冊推薦的設計。ADC

2019-01-25 08:21:14

各位大牛,請教一下。我現在用AD9467-250,采樣時鐘用AD9517-3出的200MHz,采集70M、0dBm單音信號。頻譜上出現較多的雜散。ADC前端電路按照AD9467手冊推薦的設計。ADC

2023-12-08 06:52:03

我使用ADF4351,其輸出在中心頻率偏移184k附近有雜散輸出,通過減小環路帶寬,減小充電電流等,雜散有一定的降低, 此時帶來靠近中心頻率出的噪聲升高,通過對比不同的板卡,都存在類似的現象,環路

2018-10-12 09:24:23

當前DTRU產品中使用了DAC3482,故障率達到12%,從FPGA側IQ數據到達DAC3482,從3482出口處測量到的信號,發現近端存在雜散。具體見下圖所示。

另外做了如下實驗:

1、將

2024-12-16 06:23:44

FPGA在嵌入式測試系統中的優勢是什么?FPGA在嵌入式測試系統中的不足是什么?

2021-05-06 07:19:22

什么是嵌入式系統中的外設嵌入式系統的各種常見外設總結

2021-04-02 07:06:08

什么是嵌入式系統?嵌入式處理器可分為哪幾類?嵌入式操作系統有哪幾類?

2021-04-25 06:35:32

什么是嵌入式操作系統?常見的嵌入式操作系統有哪幾種?嵌入式操作系統有何功能?

2021-12-24 07:07:38

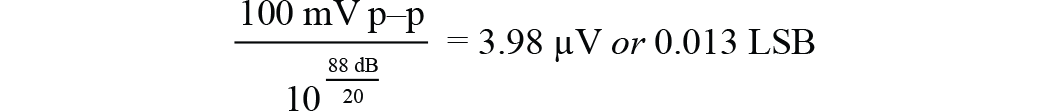

噪聲對這些參數的影響是優化電源噪聲規格的第一步。無雜散動態范圍(SFDR)電源噪聲可耦合到任何模擬信號處理系統的載波信號中。電源噪聲的影響取決于其相對于頻域中載波信號的強度。一種測量方法是SFDR,它

2021-06-16 09:18:18

在把無線電芯片或模塊集成到典型的嵌入式系統中時,設計人員必須面臨的一項常見任務是追蹤和消除噪聲和雜散信號。潛在的噪聲來源包括:開關電源、來自系統其它部分的數字噪聲、以及外部噪聲來源。在考慮噪聲

2011-10-18 09:40:50

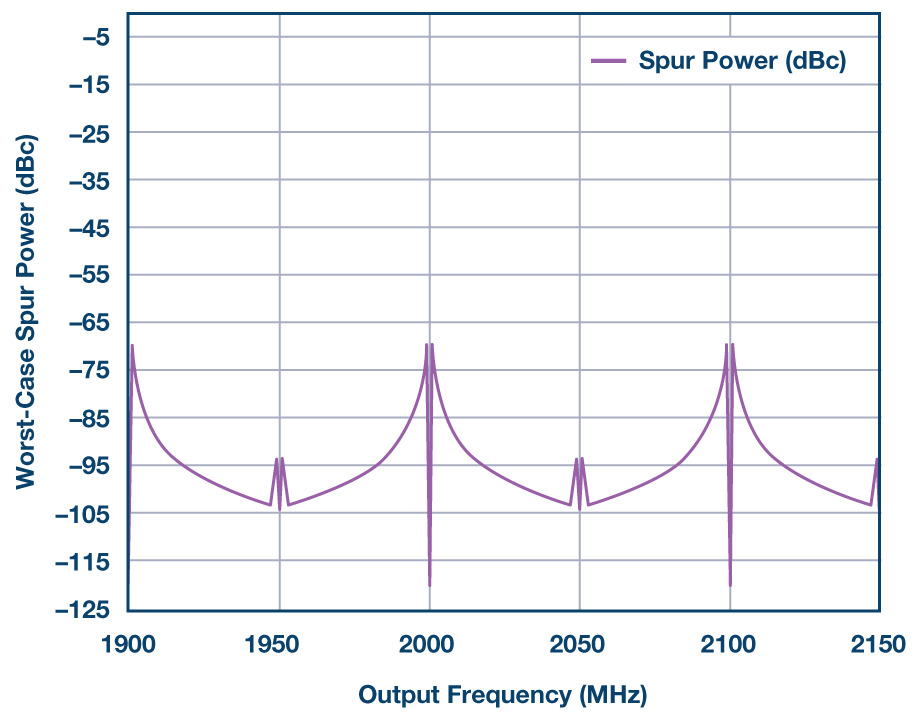

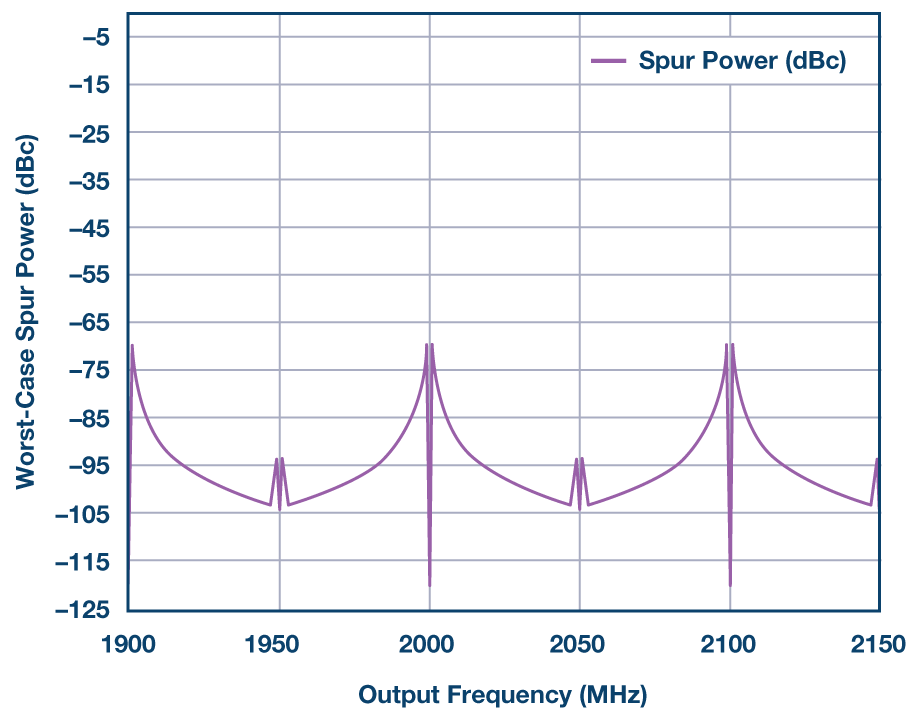

鎖相環 (PLL) 和壓控振蕩器 (VCO) 輸出特定頻率的RF信號,理想情況下此信號應當是輸出中的唯一信號。但事實上,輸出中存在干擾雜散信號和相位噪聲。本文討論最麻煩的雜散信號之一——整數邊界雜散

2019-10-11 08:30:00

在一個發射系統中,有很多射頻接口,那么究竟哪個接口是測試者所關心的呢?讓我們通過下圖來討論各測試點對系統雜散測試的意義。由多工器的無源互調所產生的雜散端口1和端口2具有同等地位,從端口1(或2)可以

2017-11-15 10:35:09

應用所需的高計算能力。但是,此類嵌入式應用需要進行高頻切換,這將導致功耗較大、芯片溫度過高,以及電源接地噪聲。開發人員可以通過本文找出改進現代嵌入式系統節能效果的機會,并了解實現電源效率最大化的可行方案。 [/td]

2021-03-09 06:36:52

都說嵌入式很難,即使去嵌入式培訓機構做系統訓練,其實只是沒有掌握正確的學習嵌入式的方法,學習講究的是一個循序漸進的過程,誰也不能一口吃出一個大胖子,從基礎到專業,從簡單到高深,下面達內講解一下系統學習嵌入式培訓的基本步驟:

2021-03-09 06:23:10

整數邊界雜散不受歡迎的原因有哪些?如何改變PFD頻率?怎樣將ADIsimFrequencyPlanner應用到寬帶VCO里?

2021-04-12 06:28:29

DDS的工作原理是什么?如何抑制DDS輸出信號中雜散問題?

2021-05-26 07:15:37

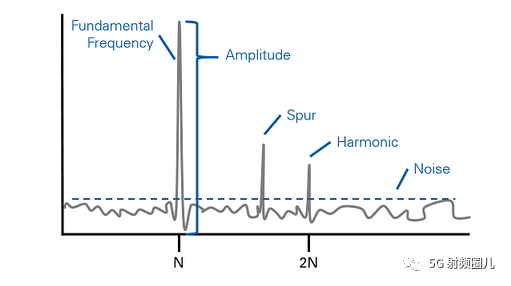

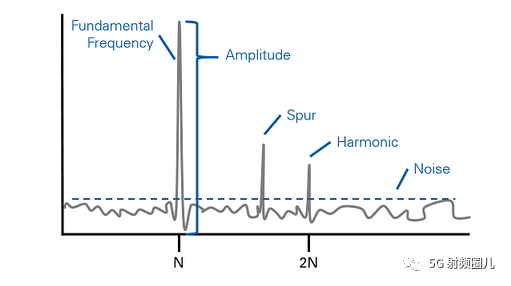

(Attenuator)、選擇開關(Switch)是不會產雜散信號的,然而含有混頻動作的器件像變頻器(Conversion,包括上變頻下變頻,總之很貧)就會產生雜散信號。雜散信號有什么危害呢?雜散信號如果落入系統

2019-11-14 10:59:39

是在系統時鐘頻率的基波與任何內部分諧波時鐘(例如,ADI直接數字頻率合成器提供的SYNC_CLK)之間產生的混頻產物。

上述雜散噪聲的全部已知來源都可根據相對于DDS/DAC輸出處基波信號的頻率偏移

2023-12-15 07:38:37

在嵌入式系統設計過程中,系統的掉電保護越來越受到重視。如何設計嵌入式系統掉電保護方案?這個問題急需解決。

2019-08-09 07:48:28

請問怎么利用混合域示波器查找出無線嵌入式系統中的噪聲來源?

2021-04-15 06:44:05

本文闡述了基于信號處理和嵌入式應用的音頻處理系統的設計和實現。

2021-06-08 07:07:19

經常容易搞錯AM,FM或PM,他們很難區分呢?時鐘相位噪聲圖中的雜散信號為什么會影響時鐘的總抖動?

2021-03-05 08:06:14

小弟正在調試一款X波段(9.6-10.8GHz)的鎖相環,采用的是內部集成VCO的HMC778LP6CE芯片。在調試中,我發現在距中心頻率50Hz整數倍的頻率處有很多雜散,請問各位大神這些雜散

2014-07-21 15:47:54

和PCB布局過程中,對寄生電容、雜散電容和分布電容的考慮和處理是至關重要的。特別是在處理高頻信號如晶振時鐘信號時,通過上述措施可以有效減小這些電容效應對電路性能的影響,提高系統的穩定性和可靠性。設計師們應充分了解這些電容特性,為電路設計提供有力保障。

2024-09-26 14:49:27

在把無線電芯片或模塊集成到典型的嵌入式系統中時,設計人員必須面臨的一項常見任務是追蹤和消除噪聲和雜散信號。潛在的噪聲來源包括:開關電源、來自系統其它部分的數字噪聲、以及外部噪聲來源。在考慮噪聲時,還應考慮無線電產生的任何可能的干擾,這是避免干擾其它無線電及滿足法規要求的一項重要考慮因素。

2019-08-14 07:51:55

的其余部分。此類不希望有的輸出信號被稱為 “雜散脈沖”。假如這些雜散脈沖的功率足夠高,那就會在射頻設計中引發很多問題,例如:發送器中相鄰通道的污染、接收器中的靈敏度損失、或期望信號自身的失真。視系統

2019-07-23 08:17:34

(ENOB)、輸入帶寬、無雜散動態范圍(SFDR)以及微分或積分非線性度等。對于GSPS ADC,最重要的一個交流性能參數可能就是SFDR。簡單而言,該參數規定了ADC以及系統從其他噪聲或者任何其他雜散頻率中

2018-11-01 11:31:37

大家好,如下圖所示,輸出的1GHz信號近端有小數分頻雜散,后發現有的頻點沒有,有的頻點會更多,小數分頻的分子分母是計算出來可以正好輸出1GHz整數頻率;

相關配置:環路濾波器是用的參考設計中

2024-11-11 06:05:42

UML引入到嵌入式系統中的可行性一種改進的通用嵌入式系統UML方案如何使用UML來設計嵌入式系統?

2021-04-23 06:12:34

標準化指標為圖2中從最小值增加的百分比。雜散與相位噪聲指標為圖2中從最小值增加的分貝。 圖 2:環路帶寬對標準化性能的影響如圖1所預測,環路帶寬為140kHz左右時,最優抖動確實為最佳。環路帶寬超出

2018-08-29 16:02:55

最近調試遇到個問題,40W功放輸出功率時在225K左右會有雜散,抑制在-50dB左右,初步認為是由于風扇引起的,如過是風扇引起的話,該如何解決

2014-03-28 09:58:41

雖然目前的高分辨率SAR ADC和Σ-Δ ADC可提供高分辨率和低噪聲,但系統設計師們可能難以實現數據手冊上的額定SNR性能。而要達到最佳SFDR,也就是在系統信號鏈中實現無雜散的干凈噪底,可能就更加困難了。雜散信號可能源于ADC周圍的不合理電路,也有可能是因惡劣工作環境下出現的外部干擾而導致。

2019-08-12 06:51:54

Steven Xie雖然目前的高分辨率SAR ADC和Σ-Δ ADC可提供高分辨率和低噪聲,但系統設計師們可能難以實現數據手冊上的額定SNR性能。而要達到最佳SFDR,也就是在系統信號鏈中實現無雜散

2018-10-19 10:38:17

本文系統介紹了雜散電流的產生及危害及嵌入式TCP/IP 協議單片機系統接入Internet 網絡的方法,并組建了基于嵌入式TCP/IP 協議單片機的雜散電流監測系統,并對整個系統進行了通

2009-09-05 08:20:36 21

21 分析了地鐵雜散電流的形成及危害, 闡述了地鐵雜散電流監測控制系統的功能,設計了基于CAN 總線的地鐵雜散電流的監測系統。論文對該系統的下位機軟硬件結構,PC-CAN接口卡以及

2010-01-20 15:29:54 21

21 直接數字頻率合成(DDS)技術推動了頻率合成領域的高速發展,但固有的雜散特性極大的限制了其應用發展。在分析DDS工作原理及雜散噪聲來源的基礎上,介紹了幾種雜散抑制的方法,

2010-07-31 10:36:19 32

32 無雜散動態范圍(SFDR)

SFDR(無雜散動態范圍)衡量的只是相對于轉換器滿量程范圍(dBFS)或輸入信號電平(dBc)的最差頻譜偽像。比較ADC時

2011-01-01 12:14:56 14336

14336 本文對OAEs檢測算法進行了研究,在嵌入式聽力診斷系統中綜合運用了目前的信號處理方法,在偽跡消除方面取得很好的效果。

2011-07-29 11:10:06 1119

1119

直接數據頻率合成器(DDS)因能產生頻率捷變且殘留相位噪聲性能卓越而著稱。另外,多數用戶都很清楚DDS輸出頻譜中存在的雜散噪聲,比如相位截斷雜散以及與相位-幅度轉換過程相關的

2012-02-02 10:41:21 44

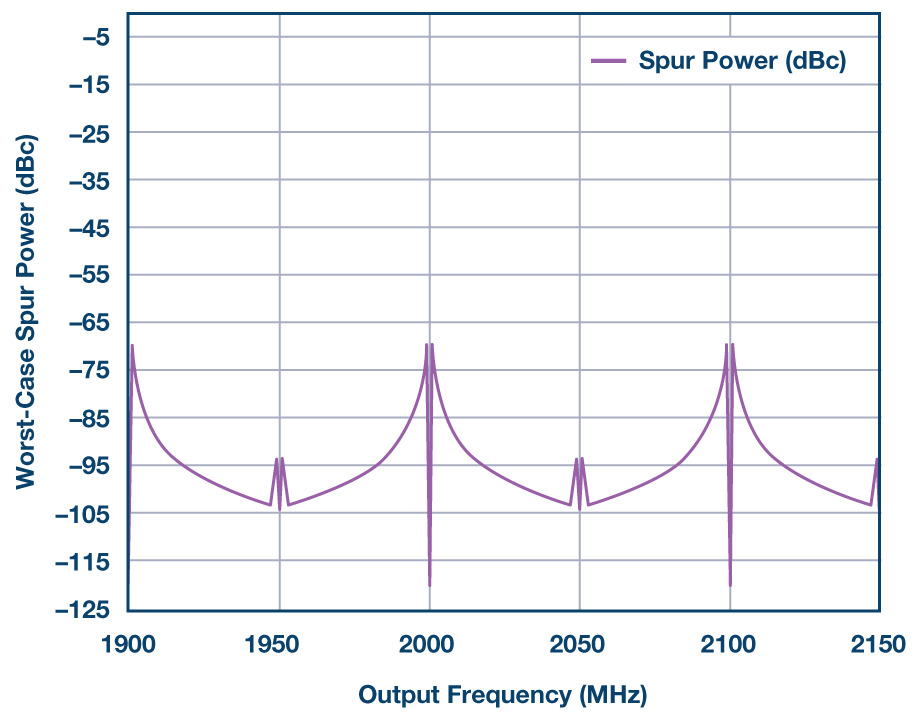

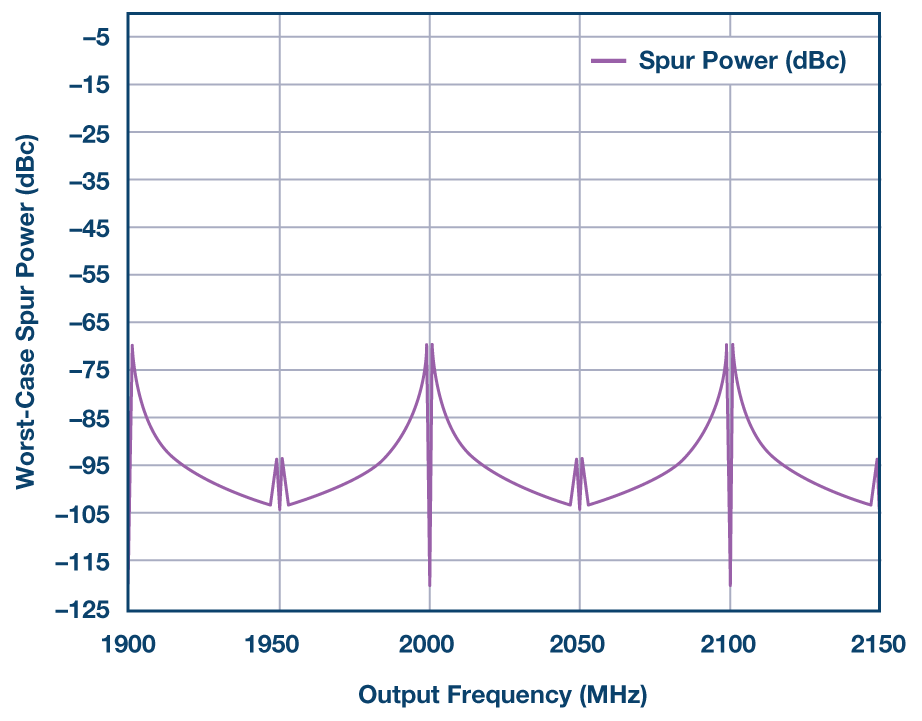

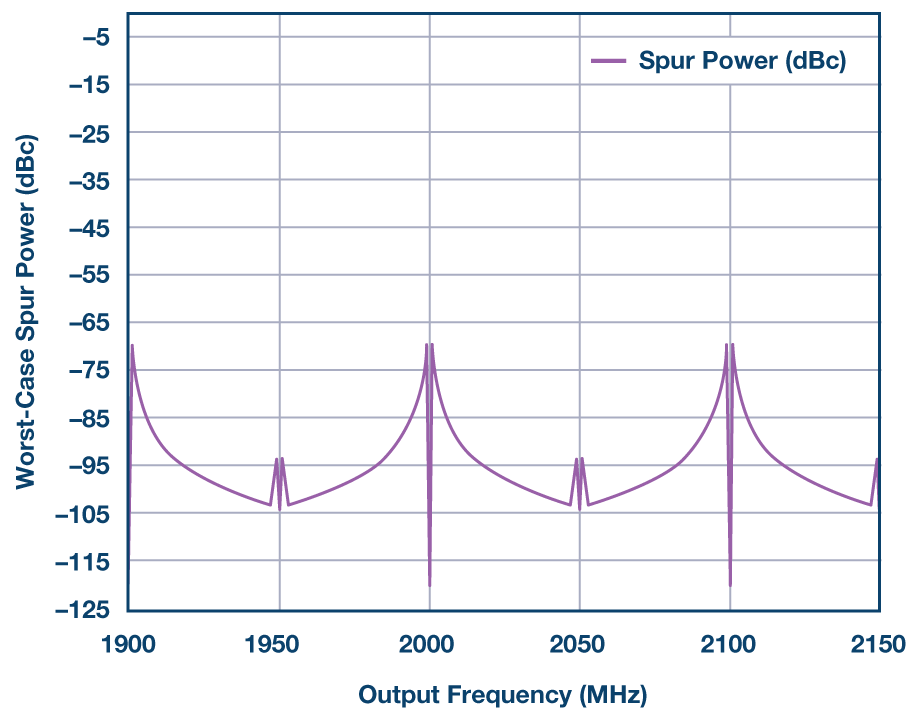

44 LMX2531 系列產品被廣泛應用于無線通訊基站系統,相比較整數分頻,采用小數分頻可以獲得更好的相位噪聲性能,但是小數分頻會導致雜散問題,特別是整數邊界雜散尤為突出。本文介紹一種在盡可能保證相位噪聲性能的基礎上,改善整數邊界雜散達10dB。

2013-04-27 15:51:04 3492

3492 介紹使用MDO4000 系列混合域示波器系列查找噪聲來源的技術和技巧,在把射頻芯片或模塊集成到典型的嵌入式系統中時,設計人員必須面臨的一項常見任務是追蹤和消除噪聲和雜散信號。潛在的噪聲來源包括

2015-05-27 20:29:33 275

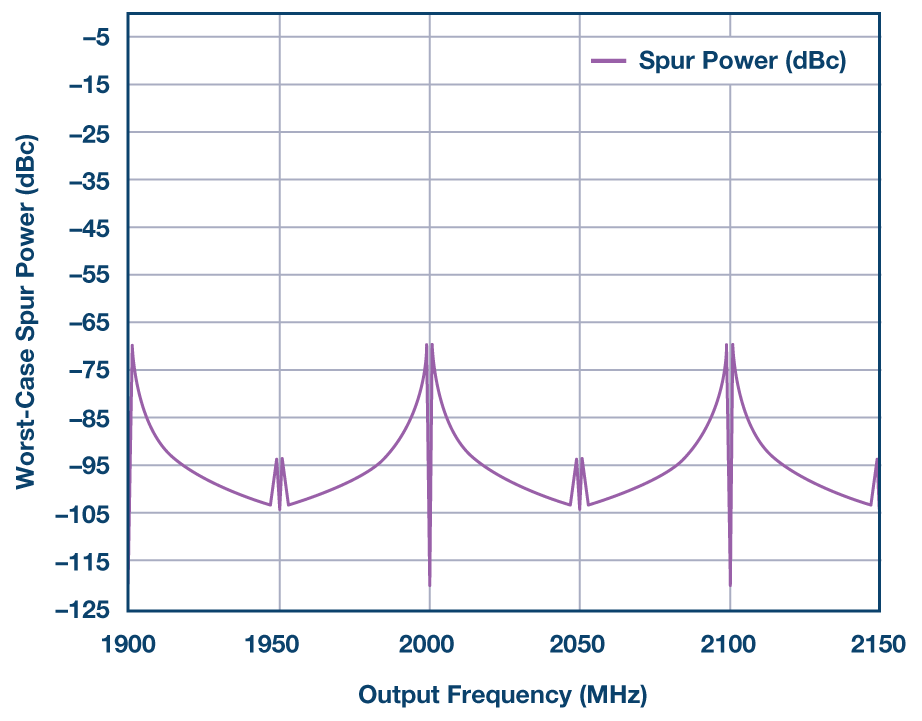

275 v分析、優化和消除帶VCO的鎖相環在高達13.6 GHz處的整數邊界雜散

2016-01-07 14:50:35 0

0 寬帶雷達信號的低雜散采樣系統研究_王龍

2017-01-08 10:47:21 0

0 雖然目前的高分辨率SAR ADC和Σ-Δ ADC可提供高分辨率和低噪聲,但系統設計師們可能難以實現數據手冊上的額定SNR性能。而要達到最佳SFDR,也就是在系統信號鏈中實現無雜散的干凈噪底,可能

2018-06-30 10:03:00 7246

7246 在每一個無線系統中,幾乎每一根線都成為天線或接收器,而它們無意中接收或傳輸的雜散信號會降低射頻子系統的整體性能。

2017-06-26 15:21:53 11

11 在把射頻芯片或模塊集成到典型的嵌入式系統中時,設計人員必須面臨的一項常見任務是追蹤和消除噪聲和雜散信號。潛在的噪聲來源包括:開關電源、來自系統其它部分的數字噪聲、以及外部噪聲來源。在考慮噪聲時,還應

2017-09-12 15:48:23 6

6 在把射頻芯片或模塊集成到典型的嵌入式系統中時,設計人員必須面臨的一項常見任務是追蹤和消除噪聲和雜散信號。

2017-09-18 09:44:38 10

10 在把射頻芯片或模塊集成到典型的嵌入式系統中時,設計人員必須面臨的一項常見任務是追蹤和消除噪聲和雜散信號。潛在的噪聲來源包括:開關電源、來自系統其它部分的數字噪聲、以及外部噪聲來源。在考慮噪聲時,還應

2017-12-07 20:37:43 1003

1003

在把射頻芯片或模塊集成到典型的嵌入式系統中時,設計人員必須面臨的一項常見任務是追蹤和消除噪聲和雜 散信號。潛在的噪聲來源包括:開關電源、來自系統其 它部分的數字噪聲、以及外部噪聲來源。在考慮噪聲

2019-03-20 15:31:37 928

928

雖然目前的高分辨率SAR ADC和E-A ADC可提供高分辨率和低噪聲,但系統設計師們可能難以實現數據手冊上的額定SNR性能。而要達到最佳SFDR,也就是在系統信號鏈中實現無雜散的干凈噪底,可能就更加困難了。雜散信號可能源于ADC周圍的不合理電路,也有可能是因惡劣工作環境下出現的外部干擾而導致。

2018-03-07 14:15:46 4

4 在把射頻芯片或模塊集成到典型的嵌入式系統中時,設計人員必須面臨的一項常見任務是追蹤和消除噪聲和雜散信號。潛在的噪聲來源包括:開關電源、來自系統其它部分的數字噪聲、以及外部噪聲來源。在考慮噪聲時,還應

2018-03-14 10:44:28 5

5 鎖相環 (PLL) 和壓控振蕩器 (VCO) 輸出特定頻率的RF信號,理想情況下此信號應當是輸出中的唯一信號。但事實上,輸出中存在干擾雜散信號和相位噪聲。本文討論最麻煩的雜散信號之一——整數邊界雜散——的仿真與消除。

2019-04-12 08:32:00 13125

13125

在第二部分中,我們將側重于詳細考察與PLL相關的兩個關鍵技術規格:相位噪聲和參考雜散。導致相位噪聲和參考雜散的原因是什么,如何將其影響降至最低?討論將涉及測量技術以及這些誤差對系統性能的影響。我們還將考慮輸出漏電流,舉例說明其在開環調制方案中的重要意義。

2019-04-04 08:10:00 25343

25343

ADI公司開發出一種頻率規劃技術,與鎖相環(PLL)設備結合使用時,可以消除輸出頻譜中的干擾雜散信號。了解該技術的詳情、優勢以及如何使用。

2019-06-28 06:09:00 4322

4322 通過演示簡要介紹鎖相環(PLL)中可實現的領先相位噪聲和雜散性能。

2019-05-21 06:23:00 6527

6527 在大型數字波束合成天線中,人們非常希望通過組合來自分布式波形發生器和接收器的信號這一波束合成過程改善動態范圍。如果關聯誤差項不相關,則可以在噪聲和雜散性能方面使動態范圍提升10logN。這里的N

2020-09-08 10:47:00 0

0 鎖相環 (PLL) 和壓控振蕩器 (VCO) 輸出特定頻率的RF信號,理想情況下此信號應當是輸出中的唯一信號。但事實上,輸出中存在干擾雜散信號和相位噪聲。本文討論最麻煩的雜散信號之一——整數邊界雜散——的仿真與消除。

2020-09-09 10:09:56 4998

4998

換流回路中的雜散電感會引起波形震蕩,EMI或者電壓過沖等問題。因此在電路設計的時候需要特別留意。本文給出了電路雜散電感的測量方法以及模塊數據手冊中雜散電感的定義方法。 圖1為半橋電路的原理電路以及

2021-10-13 15:36:13 5840

5840

眾所周知,無雜散動態范圍(SFDR)表示可以與大干擾信號區分開來的最小功率信號。對于當前的高分辨率、精密ADC,SFDR通常由基波頻率與目標基頻的二次或三次諧波之間的動態范圍決定。但是,由于系統的其他方面,可能會出現雜散并限制性能。

2023-01-04 15:20:49 4256

4256

鎖相環(PLL)和壓控振蕩器(VCO)以特定頻率輸出RF信號,理想情況下,該信號將是輸出端存在的唯一信號。實際上,輸出端存在不需要的雜散信號和相位噪聲。本文討論如何仿真和消除一種更麻煩的雜散信號——整數邊界雜散。

2023-01-08 15:40:42 3309

3309

假設某個調制方案指出整數邊界雜散功率高于–80 dBc的通道不可用;那么圖10中大約1%的通道不再可用。為了克服這個問題,ADIsimFrequencyPlanner可以優化PLL/VCO配置,以減少并在大多數情況下消除整數邊界雜散。

2023-02-01 11:54:50 3036

3036

雜散干擾主要是由于接收機的靈敏度不高造成的。 發射機輸出信號通常為大功率信號,在產生大功率信號的過程中會在發射信號的頻帶之外產生較高的雜散。 如果雜散落入某個系統接收頻段內的幅度較高,則會導致接收

2023-05-08 16:18:38 3278

3278

-本文要點理解電路中的雜散電容。了解雜散電容如何影響電子電路。探索減少電路中雜散電容的策略。雜散電容就像被遺棄的寵物流浪在街道和巷子里一樣,它們潛伏在電路中。本文將了解電子電路中的雜散電容是如何產生

2023-01-05 15:45:29 4611

4611

一站式PCBA智造廠家今天為大家講講如何減少PCB雜散電容的影響?減少PCB雜散電容的PCB設計方法。當提到PCBA上的電子電路時,經常使用的術語是雜散電容。PCB上的導體、無源器件的預制電路板

2023-08-24 08:56:32 1437

1437 什么是無雜散動態范圍 (SFDR)?為什么SFDR很重要? 無雜散動態范圍(SFDR)是指模擬信號中最大的無雜散動態范圍。它是在硬件設備中測量的。它是指能夠測量的模擬信號的最大幅度范圍,其中沒有雜散

2023-10-31 09:34:29 10716

10716 如何使用頻譜分析儀來觀察和分析雜散信號? 頻譜分析儀是一種廣泛應用于電子領域的儀器,用于觀察和分析信號的頻譜特性。它可以幫助工程師們檢測和排除信號中的雜散信號,確保設備的正常工作和無干擾的信號傳輸

2023-12-21 15:37:16 3460

3460 說到射頻的難點不得不提雜散,雜散也是射頻被稱為“玄學”的來源。雜散也是學習射頻必經的一個難點。本篇文章就來講一下雜散。

2024-11-05 09:59:34 6929

6929

電子發燒友App

電子發燒友App

評論