ADI公司開(kāi)發(fā)出一種頻率規(guī)劃技術(shù),與鎖相環(huán)(PLL)設(shè)備結(jié)合使用時(shí),可以消除輸出頻譜中的干擾雜散信號(hào)。了解該技術(shù)的詳情、優(yōu)勢(shì)以及如何使用。

聲明:本文內(nèi)容及配圖由入駐作者撰寫(xiě)或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

ADI

+關(guān)注

關(guān)注

151文章

46104瀏覽量

277196 -

pll

+關(guān)注

關(guān)注

6文章

981瀏覽量

138161 -

頻率

+關(guān)注

關(guān)注

4文章

1585瀏覽量

62066

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

羅德與施瓦茨 (R&S) FSW8 頻譜與信號(hào)分析儀

噪聲電平可通過(guò)選擇使用噪聲消除功能而進(jìn)一步改善13dB。用戶(hù)可確認(rèn)之前隱藏在噪底之下的極小雜散信號(hào)從而有效地優(yōu)化發(fā)射機(jī)系統(tǒng)。 * 內(nèi)置高通濾

發(fā)表于 02-26 15:01

技術(shù)資訊 I 容性耦合噪聲抑制方法如何減少串?dāng)_

本文要點(diǎn)容性耦合噪聲取決于電路中的電壓變化和耦合電容的值,其中耦合電容受兩個(gè)電路之間距離的影響。雜散電容會(huì)增大耦合電容值。如果減少或消除雜

遠(yuǎn)距離無(wú)線芯動(dòng)力,穿透干擾穩(wěn)連接——深入解讀LoRa擴(kuò)頻技術(shù)

一、什么是LoRa擴(kuò)頻?LoRa擴(kuò)頻技術(shù)是一種基于直接序列擴(kuò)頻(DSSS)的先進(jìn)無(wú)線通信技術(shù),通過(guò)將信號(hào)頻譜擴(kuò)展至更寬的帶寬,在低功耗條件下實(shí)現(xiàn)遠(yuǎn)距離、高穿透、強(qiáng)抗

發(fā)表于 12-19 11:06

ADC采樣中如何消除電源紋波對(duì)微弱信號(hào)(<10mV)的干擾?

ADC采樣中,如何消除電源紋波對(duì)微弱信號(hào)(<10mV)的干擾?

發(fā)表于 11-24 06:10

什么是晶振的雜散電容?

什么是晶振的雜散電容?晶振的雜散電容,也叫做寄生電容,是指電路中非人為設(shè)計(jì)、由物理結(jié)構(gòu)自然產(chǎn)生的、有害的隱藏電容。它為什么重要?(影響)雜

電壓擊穿試驗(yàn)儀中微電流檢測(cè)電路的抗干擾設(shè)計(jì)與精度保證

的工頻電磁場(chǎng)、無(wú)線電信號(hào)等,通過(guò)空間輻射或線路傳導(dǎo)干擾電路。如高壓設(shè)備電磁場(chǎng)會(huì)在導(dǎo)線感應(yīng)雜散電壓,開(kāi)關(guān)脈沖干擾會(huì)破壞電路穩(wěn)定。 (二)電路內(nèi)

LoRa設(shè)備發(fā)射和接收的信號(hào)相互干擾怎么辦

當(dāng)LoRa設(shè)備發(fā)射和接收的信號(hào)相互干擾時(shí),可以采取以下措施來(lái)減少或消除這種干擾,從而提高通信的可靠性和穩(wěn)定性: 1. 頻率

是德頻譜分析儀對(duì)微波信號(hào)頻率穩(wěn)定性的測(cè)量與分析

內(nèi)置的高精度頻率合成器產(chǎn)生測(cè)試信號(hào),利用其卓越的頻譜分析功能,對(duì)微波信號(hào)的頻率穩(wěn)定性進(jìn)行評(píng)估。測(cè)量過(guò)程中

IGBT功率模塊動(dòng)態(tài)測(cè)試中夾具雜散電感的影響

在IGBT功率模塊的動(dòng)態(tài)測(cè)試中,夾具的雜散電感(Stray Inductance,Lσ)是影響測(cè)試結(jié)果準(zhǔn)確性的核心因素。雜散電感由測(cè)試夾具的

無(wú)雜散、50 MHz 至 2.1 GHz 單通道小數(shù) N 分頻頻率合成器 skyworksinc

電子發(fā)燒友網(wǎng)為你提供()無(wú)雜散、50 MHz 至 2.1 GHz 單通道小數(shù) N 分頻頻率合成器相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有無(wú)雜散、50 M

發(fā)表于 05-23 18:30

ADC采樣率與信號(hào)頻率:關(guān)鍵概念與設(shè)計(jì)要點(diǎn)

系統(tǒng)能在保持高采樣率的同時(shí),降低對(duì)數(shù)字接口的速度要求。實(shí)際應(yīng)用建議l 對(duì)于射頻中頻接收等高頻應(yīng)用,優(yōu)先關(guān)注ADC帶寬指標(biāo)l 對(duì)于傳感器信號(hào)采集,重點(diǎn)考慮采樣率與信號(hào)帶寬的關(guān)系l 使用頻率規(guī)劃

發(fā)表于 05-13 09:53

雜散電感對(duì)IGBT開(kāi)關(guān)過(guò)程的影響(2)

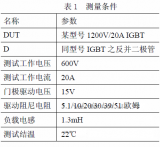

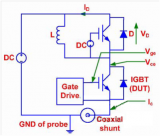

為驗(yàn)證對(duì)主回路雜散電感效應(yīng)的分析并考察不同電感量以及門(mén)極驅(qū)動(dòng)情況下的實(shí)際情況,我們?nèi)藶閷?duì)Lp 大小進(jìn)行了干預(yù),其具體方法是在D 的陰極與電路PCB 之間(即Lp2 與Lc1之間)加入長(zhǎng)度可調(diào)的導(dǎo)線,用試湊辦法得到期望的附加電感量。

雜散電感對(duì)IGBT開(kāi)關(guān)過(guò)程的影響(1)

的結(jié)構(gòu)如主回路雜散電感會(huì)影響IGBT的開(kāi)關(guān)特性,進(jìn)而影響開(kāi)關(guān)損耗,任何對(duì)其開(kāi)關(guān)性能的研究都必然建立在實(shí)驗(yàn)測(cè)試基礎(chǔ)之上,并在實(shí)際設(shè)計(jì)中盡量?jī)?yōu)化以降低變流回路雜

開(kāi)關(guān)電源的共模干擾抑制技術(shù)-開(kāi)關(guān)電源共模電磁干擾(EMI)對(duì)策詳解

開(kāi)關(guān)電源的共模干擾抑制技術(shù)|開(kāi)關(guān)電源共模電磁干擾(EMI)對(duì)策詳解 0 引言 由于MOSFET及IGBT和軟開(kāi)關(guān)技術(shù)在電力電子電路中的廣泛

發(fā)表于 03-27 15:07

開(kāi)關(guān)電源的共模干擾抑制技術(shù)|開(kāi)關(guān)電源共模電磁干擾(EMI)對(duì)策詳解

電流的耦合路徑示意圖

圖2 提出的共模噪聲消除方法

本文以單端反激電路為例,介紹基于補(bǔ)償原理的共模干擾抑制技術(shù)在功率變換器中的應(yīng)用。圖3給出了典型單端反激變換器的拓?fù)浣Y(jié)構(gòu),并加入了

發(fā)表于 03-08 10:18

頻率規(guī)劃技術(shù)可消除頻譜中的干擾雜散信號(hào)

頻率規(guī)劃技術(shù)可消除頻譜中的干擾雜散信號(hào)

評(píng)論