延時和建立時間與電源電壓的關系

- 電源(262167)

- 延時(26276)

- 建立時間(6724)

相關推薦

熱點推薦

補償放大器如何提供更高的壓擺率和更快的建立時間

/μs 壓擺率、0.1ns 的 26ns 建立時間、10 Hz 時的 2nV/√Hz 1/f 噪聲、1nV/√Hz 寬帶噪聲和 ?72 dBc 2MHz 無雜散動態范圍。 采用 3V 至 10V 電源供電, 每個放大器的靜態電流為3 mA。

2023-01-30 16:22:26 2857

2857

2857

2857

靜態時序之建立時間和保持時間分析

靜態時序分析包括建立時間分析和保持時間分析。建立時間設置不正確可以通過降低芯片工作頻率解決,保持時間設置不正確芯片無法正常工作。

2022-08-22 10:38:24 5382

5382

5382

5382芯片設計進階之路—從CMOS到建立時間和保持時間

建立時間(setup time)和保持時間(hold time)是時序分析中最重要的概念之一,深入理解建立時間和保持時間是進行時序分析的基礎。

2023-06-21 10:44:01 2768

2768

2768

2768

FPGA時序分析-建立時間和保持時間裕量都是inf怎么解決呢?

今天有個小伙伴遇到一個問題,就是在vivado里面綜合后看到的建立時間和保持時間裕量都是inf,我們來看看怎么解決這個問題。

2023-07-30 10:26:02 2193

2193

2193

2193

淺析D觸發器的建立時間和保持時間物理含義

我理解這個D觸發正常運轉要滿足四個約束,第一個是建立時間,第二個是保持時間,第三個是對于最后一個傳輸門的關斷時間的控制,第四個是[時鐘周期]() 約束。

2023-12-04 15:44:02 3183

3183

3183

3183

建立時間和保持時間討論

是一條路徑上的相連的兩個寄存器,數據輸入到 T1 經過1 個 clk 之后,傳輸到 T2;Tco 為經過寄存器 T1 的傳輸延時;Tdelay 為經過組合邏輯的傳輸延時;Tsetup 為 T2 的建立時間

2015-03-10 23:19:03

建立時間非常重要

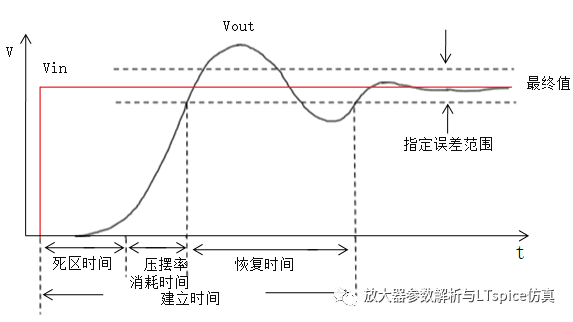

作者: TI專家 Bruce Trump翻譯: TI信號鏈工程師 Michael Huang (黃翔) 建立時間是運放階躍響應進入和停留在最終值的特定誤差范圍內的所需時間。它在一些應用中十分重要

2018-09-20 16:32:36

AD7195交流激勵建立時間怎樣計算?

Hi,All AD7195數據手冊中講,當選擇Sinc(4)濾波(禁用斬波,禁用零延時),在通道切換或單個通道上進行轉換且輸入發生階躍變化時,ADC建立時間為4/fadc。 我的問題時,如果使用了

2018-11-06 09:08:07

DAC7811想要實現持續1us的100mA電流源,但DAC建立時間都有1us,如何解決?

要給一個阻性(幾十歐)元件施加一個20~80mA的電流,測量電壓,計算出準確的阻值,由于功耗限制,電流只允許持續1us,本打算使用DAC+運放+晶體管實現電流源,但找了一圈,發現DAC的建立時間通常都在1us以上,再算上運放的建立時間,肯定>1us,請教該如何實現?

2024-11-28 06:37:30

DAC81408的建立時間為12uS,如何理解數據手冊中的12uS建立時間這個參數呢?

在數據手冊中,DAC81408的建立時間為12uS

而爬升速率0~5V為1V/uS,如果控制輸出從0V跳變至5V,以此時間計算,時間為5uS,小于12uS的建立時間典型值

如上圖所示為數據手冊

2024-12-09 08:33:21

DC綜合建立時間的關鍵路徑分析的問題?

有沒有人遇到在DC綜合后分析建立時間時序,關鍵路徑時序違例是因為起始點是在時鐘的下降沿開始驅動的,但是設計中都是時鐘上升沿觸發的。在線等待各位大牛解惑!很急 求大神幫忙!

2015-01-04 15:17:16

FPGA實戰演練邏輯篇51:建立時間和保持時間

不確定,那么隨后的reg3out值也會處于一個不確定狀態。比如第一個時鐘周期,原本reg3in應該是穩定的低電平,但是由于整個路徑上的延時時間過長,導致了reg3in在clk_r3的建立時間內數據還未

2015-07-17 12:02:10

I2C數據建立時間少于300ns,如何解決

幾天前量測了下intel 南橋發出到一個電源控制器的I2C信號,發現數據建立時間(hold time)只有150ns左右,I2C協議里面所說至少300ns,這個問題該怎么解決啊 求大神指導建立時間有

2013-12-08 00:38:24

PGA281建立時間過長怎么解決?

我的PGA281增益由1變128時,建立時間Settling time過長有800uS左右(增益切換后延時1ms也沒用),可數據手冊明明是40us

2024-08-22 06:14:39

VGA驅動接口時序設計數據的建立時間和保持時間

簡單的來分析一下數據的建立時間和保持時間應該滿足怎樣的關系才能保證被時鐘lcd_clk穩定的鎖存到ADV7123芯片中。首先,我們需要來看看這個實例的時鐘launch edge和latch edge

2019-04-10 06:33:34

ad8067如何才能知道階躍響應誤差達到0.01%時的建立時間?

在為ad7610選擇一個單電源的驅動放大器,手冊中推薦的ad8021是雙電源,建立時間參數為:Settling Time to 0.01% VO = 1 V step, RL = 500 Ω 23

2023-11-17 06:22:37

為什么ADS1298在初始化過程中START引腳的建立時間會有延遲?

關于 ADS1298,我想澄清下列問題:

1. 為什么 ADS1298 在初始化過程中 START 引腳的建立時間會有延遲?如果輸入信號在該建立時間過程中 (tsettle) 發生變化,會出

2025-02-17 07:15:00

為什么ADS1298在初始化過程中START引腳的建立時間會有延遲?

關于 ADS1298,我想澄清下列問題:1. 為什么 ADS1298 在初始化過程中 START 引腳的建立時間會有延遲?如果輸入信號在該建立時間過程中 (tsettle) 發生變化,會出現什么情況

2019-05-30 14:50:14

為什么觸發器要滿足建立時間和保持時間

什么是同步邏輯和異步邏輯?同步電路和異步電路的區別在哪?為什么觸發器要滿足建立時間和保持時間?什么是亞穩態?為什么兩級觸發器可以防止亞穩態傳播?

2021-08-09 06:14:00

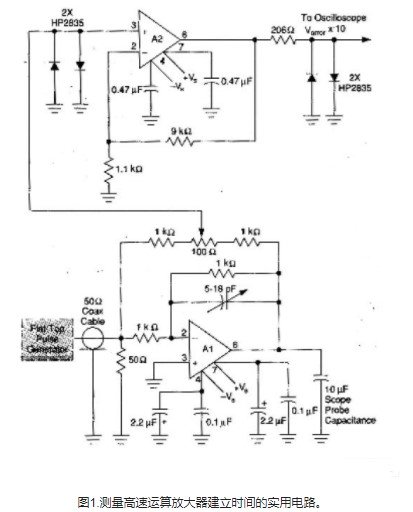

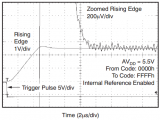

使用采樣保持技術實現運算放大器建立時間測定

作者:Roger Liang,德州儀器 (TI) 系統工程師引言 現代高速運算放大器 (op amps) 的建立時間都為幾納秒左右。這個時間是如此的短暫。因此,要想在某個合理誤差范圍內對其進行測定

2012-07-30 17:36:20

保持時間與建立時間

如圖,建立時間和保持時間都是針對的時鐘沿,如圖所示,時鐘沿有一個上升的過程,圖中虛線與clk上升沿的交點是什么?幅值的50%?還是低電平(低于2.5V)往高電平(高于2.5V)跳轉的那個點?

2018-11-29 00:20:02

如何優化多通道數據采集系統?從了解輸入建立時間的門道開始

多路復用器輸入端的建立瞬變(由多路復用器輸出端的大尺度開關瞬變引起)導致需要較長采集時間,使得多通道數據采集系統的整體吞吐量顯著降低。然后,文中將著重闡述使輸入建立時間最小化以及提高數據吞吐量和系統

2018-10-29 17:06:48

如何最大程度縮短輸入建立時間?

密度。本文將說明多路復用器輸入端的建立瞬變(由多路復用器輸出端的大尺度開關瞬變引起)導致需要較長采集時間,使得多通道數據采集系統的整體吞吐量顯著降低。然后,本文將著重闡述使輸入建立時間最小化以及提高數據吞吐量和系統效率所需的設計權衡。

2020-12-28 07:30:52

對于一塊確定的ADF芯片,其穩態建立時間精度能到什么級別?

對于一個ADF芯片,比如手上有一塊ADF4016,如果外圍條件穩定,外圍觸發信號的時刻及幅度都能確定,內部器件穩態建立時間是否每次都有區別?如果不是,穩態建立需要的時間精度能到什么級別?我看說明書上只寫了T1-T6的穩態所需最小時間,沒有精度說明,有沒有相關的資料?

2018-10-29 09:13:25

數字 IC 筆試面試必考點(9)建立時間以及保持時間 精選資料分享

建立時間(Setup Time)是指觸發器的時鐘信號上升沿到來之前,數據保持穩定不變的時間。 輸入信號應該提前時鐘上升沿(如上升沿有效)Tsu時間到達芯片,這個 Tsu就是建立時間。如果不滿足建立時間

2021-07-26 07:36:01

數字電路中,建立時間和保持時間對于觸發器的時鐘信號有

請問,對于觸發器的時鐘信號,建立時間和保持時間有要求嗎?剛看到一個門控時鐘產生毛刺的反例,(如下圖)想到了這個問題。若此時鐘信號毛刺極小,有沒有可能被觸發器忽略呢?為什么呢?如果有可能小到什么程度會被忽略呢?

2012-01-27 18:44:58

數模轉換器的壓擺率與建立時間

作者:Kevin Duke德州儀器今天,我們將介紹兩種相關的動態參數 — 壓擺率與建立時間。如欲了解更多有關靜態和動態參數的不同之處,敬請參閱本文。什么是壓擺率?TI退休員工模擬專家 Bruce

2018-09-13 09:56:17

求助,關于INA333波形建立時間的疑問求解

示波器測量的是INA333的輸出波形

信號的輸入是應變片全橋電路,應變片和INA333采用PWM的波形間歇性上電。輸入信號建立時間ina333電源的波形建立時間是300us左右,但是輸出信號的建立時間在1ms的時候還沒有穩定。規格書里的輸出信號建立時間小于400us。是電路哪里有問題嗎?

2024-08-13 07:45:40

請教關于AD8021建立時間問題

AD8021的建立時間具體是多少,在Datasheet上The AD8021 is a well-behaved amplifier that settles to 0.01% in 23 ns

2018-07-30 06:55:57

請問ADE7880有效值采集中的建立時間是指從上電到有效值穩定的時間嗎?

1.有效值采集問題1)有效值采集中的建立時間(settling time)是指從上電到有效值穩定的時間嗎?兩次讀取有效值的最小時間間隔與建立時間有關系嗎?2)有效值中建議過零點的時候進行有效值的讀取

2019-03-05 14:30:09

請問兩級運算放大器的建立時間如何估算?

一般運算放大器的datasheet都會給出0.01%建立時間(有的給出0.1%建立時間),比如ADA4897,給出2V階躍測試時0.01%建立時間為90 ns。

因此對于單運放電路來說,建立時間

2023-11-27 06:54:56

請問兩級運算放大器的建立時間如何估算?

一般運算放大器的datasheet都會給出0.01%建立時間(有的給出0.1%建立時間),比如ADA4897,給出2V階躍測試時0.01%建立時間為90 ns。因此對于單運放電路來說,建立時間可以

2018-11-13 15:08:15

請問使用ad8067如何才能知道階躍響應誤差達到0.01%時的建立時間?

在為ad7610選擇一個單電源的驅動放大器,手冊中推薦的ad8021是雙電源,建立時間參數為:Settling Time to 0.01% VO = 1 V step, RL = 500 Ω 23

2018-08-01 09:25:24

請問如何增加ESP32-S2以太網SPI接口的CS建立時間?

如何增加ESP32-S2 以太網SPI接口的CS建立時間?(1)問題現象:偶爾出現_[0;31mE (6321) dm9051.mac: buffer size too small, needs

2023-02-15 06:55:16

請問如何增加ESP32-S2以太網SPI接口的CS建立時間?

詳細描述,請參考:https://blog.csdn.net/weichushun/articl ... /123128016

如何增加ESP32-S2 以太網SPI接口的CS建立時間?

(1

2024-06-18 07:31:22

請問如何確認dac7811的電壓建立時間是否滿足0.2us?

我們對dac7811進行了仿真,目的想確認dac7811的電壓建立時間是否滿足0.2us,仿真結果有些疑問。

(1)、下圖是仿真模型

(2)下圖是仿真結果,

序號1是輸入模擬電壓給的時間點

2024-11-14 06:22:34

計算開關電容ADC的建立時間

計算開關電容ADC的建立時間:很多C8051F器件具有片內模/數轉換器ADC這些ADC使用一個采樣電容該電容被充電到輸入信號電壓由SAR邏輯進行數據轉換由于存在ADC采樣電容輸入阻抗和外部輸

2008-10-30 18:25:08 24

24

24

24快速建立時間的自適應鎖相環

該文簡要討論了環路性能(建立時間,相位噪聲和雜散信號)和環路參數(帶寬,相位裕度等)的相互關系。提出并分析了一種自適應的具有快速建立時間的鎖相環結構及其關鍵模塊(鑒相

2010-04-23 08:33:53 20

20

20

20精確測算ADC驅動電路建立時間

常估算運算放大器建立時間的方法受示波器分辨率或電路寄生的制約,而且這些方法都未考慮模數轉換器(ADC)的采樣電路、封裝寄生電容和電感等因素。對此給出了一個精

2010-12-20 17:51:37 39

39

39

39線與邏輯、鎖存器、緩沖器、建立時間、緩沖時間的基本概念

基本概念:線與邏輯、鎖存器、緩沖器、建立時間、緩沖時間

基本概念:線與邏輯、鎖存器、緩沖器、建立時間、緩沖時間

標簽/分類:

2007-08-21 15:17:27 1607

1607

1607

1607時延和建立時間在ADC電路中的區別

時延和建立時間setup在ADC電路中的區別:對于大多數 ADC 用戶來說,“時延”和“建立時間”這兩個術語有時可以互換。但對于 ADC 設計人員而言,他們非常清楚

2007-11-22 23:33:07 1941

1941

1941

1941使用采樣保持技術實現運算放大器建立時間測定

本文將介紹一種新方法,其經過證明可以有效地完成這些測量工作。它是一種相對低成本、簡單的建立時間測量方法。這種方法把準確性和精確度建立在波形生成器和采樣保持電路的相

2012-07-27 10:25:16 1810

1810

1810

1810

建立時間和保持時間(setup time 和 hold time)

建立時間和保持時間貫穿了整個時序分析過程。只要涉及到同步時序電路,那么必然有上升沿、下降沿采樣,那么無法避免setup-time 和 hold-time這兩個概念。 1. 什么是setup-time

2017-02-08 14:48:11 7009

7009

7009

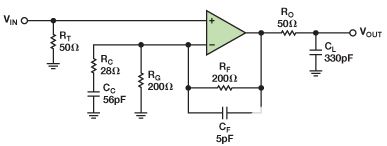

7009用于測試運算放大器建立時間的設備設計

用于測試運算放大器建立時間的基本設備包括:一個高品質(且昂貴)的“平頂”脈沖發生器用作DUT的輸入;一個DUT測試夾具,在運算放大器插口電源引腳處具有電源和旁路電容;以及一個示波器,用于處理和顯示測試輸出。

2019-06-06 08:14:00 3202

3202

3202

3202

詢問應用工程師:建立時間

運算放大器建立時間是保證數據采集系統性能的關鍵參數。為了實現精確的數據采集,運算放大器輸出必須在A/D轉換器能夠準確數字化數據之前建立。然而,建立時間通常不是一個容易測量的參數。

2023-06-17 10:37:54 1635

1635

1635

1635

到底什么是建立時間/保持時間?

在時序電路設計中,建立時間/保持時間可以說是出現頻率最高的幾個詞之一了,人們對其定義已經耳熟能詳,對涉及其的計算(比如檢查時序是否正確,計算最大頻率等)網上也有很多。

2023-06-27 15:43:55 18883

18883

18883

18883

PCB傳輸線建立時間、保持時間、建立時間裕量和保持時間裕量

信號經過傳輸線到達接收端之后,就牽涉到建立時間和保持時間這兩個時序參數,它們表征了時鐘邊沿觸發前后數據需要在鎖存器的輸入持續時間,是接收器本身的特性。簡而言之,時鐘邊沿觸發前,要求數據必須存在一段時間,這就是器件需要的建立時間;

2023-09-04 15:16:19 1610

1610

1610

1610

UPS電源的備用延時時間指什么?

UPS電源的備用延時時間指什么? UPS電源的備用延時時間是指在停電或電網故障情況下,UPS電池能夠提供電能的持續時間。它是UPS電源系統性能的重要指標之一,對于保證設備正常運行和數據的安全性

2023-11-09 16:53:36 2484

2484

2484

2484關于建立時間和保持時間的測量方法

文件提到兩種setup/hold測量方式:10% push-up和pass/fail,按照TSMC說法,前者會更樂觀一些,因此如果是采用前者(10% push-up)的測量方式得到建立時間和保持時間,需要十份小心時序裕量是否足夠,最好人為添加margin。

2023-12-05 11:19:38 3630

3630

3630

3630

電子發燒友App

電子發燒友App

評論