靜態(tài)時(shí)序分析包括建立時(shí)間分析和保持時(shí)間分析。建立時(shí)間設(shè)置不正確可以通過降低芯片工作頻率解決,保持時(shí)間設(shè)置不正確芯片無法正常工作。

2022-08-22 10:38:24 5380

5380 建立時(shí)間(setup time)和保持時(shí)間(hold time)是時(shí)序分析中最重要的概念之一,深入理解建立時(shí)間和保持時(shí)間是進(jìn)行時(shí)序分析的基礎(chǔ)。

2023-06-21 10:44:01 2768

2768

今天有個(gè)小伙伴遇到一個(gè)問題,就是在vivado里面綜合后看到的建立時(shí)間和保持時(shí)間裕量都是inf,我們來看看怎么解決這個(gè)問題。

2023-07-30 10:26:02 2193

2193

不論數(shù)字信號的上升沿是抖還是慢,在信號跳變時(shí),總會有一段過渡時(shí)間處于邏輯判斷閾值的上限和下限之間,從而造成邏輯的不確定狀態(tài),更糟糕的是,通常的數(shù)字信號都不止一路,可能是多路信號一起傳輸來代表一些邏輯

2023-11-29 16:36:16 2159

2159

我理解這個(gè)D觸發(fā)正常運(yùn)轉(zhuǎn)要滿足四個(gè)約束,第一個(gè)是建立時(shí)間,第二個(gè)是保持時(shí)間,第三個(gè)是對于最后一個(gè)傳輸門的關(guān)斷時(shí)間的控制,第四個(gè)是[時(shí)鐘周期]() 約束。

2023-12-04 15:44:02 3182

3182

分析時(shí)鐘與地址信號一樣,如果DQ與DQS之間等長做的不好,DQS的時(shí)鐘邊沿就不會保持在DQ的中間位置,這樣建立時(shí)間或者保持時(shí)間的裕量就會變小。先簡單的來看一張圖 圖9 延時(shí)偏差對時(shí)

2018-09-19 16:21:47

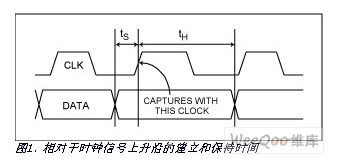

如圖,建立時(shí)間和保持時(shí)間都是針對的時(shí)鐘沿,如圖所示,時(shí)鐘沿有一個(gè)上升的過程,圖中虛線與clk上升沿的交點(diǎn)是什么?幅值的50%?還是低電平(低于2.5V)往高電平(高于2.5V)跳轉(zhuǎn)的那個(gè)點(diǎn)?

2018-11-29 00:20:02

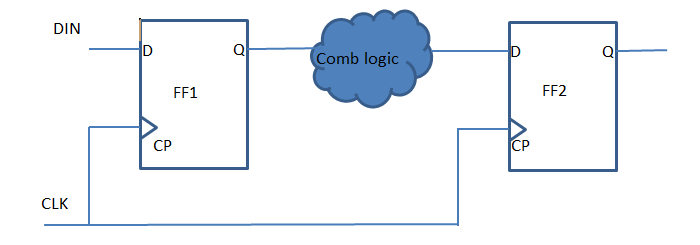

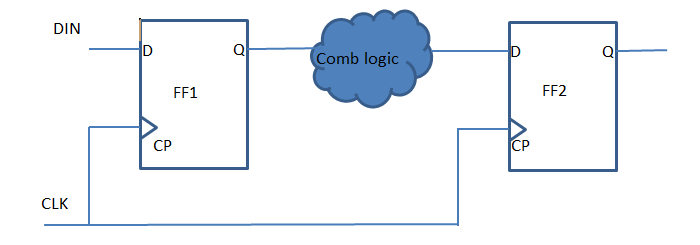

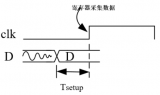

是一條路徑上的相連的兩個(gè)寄存器,數(shù)據(jù)輸入到 T1 經(jīng)過1 個(gè) clk 之后,傳輸到 T2;Tco 為經(jīng)過寄存器 T1 的傳輸延時(shí);Tdelay 為經(jīng)過組合邏輯的傳輸延時(shí);Tsetup 為 T2 的建立時(shí)間

2015-03-10 23:19:03

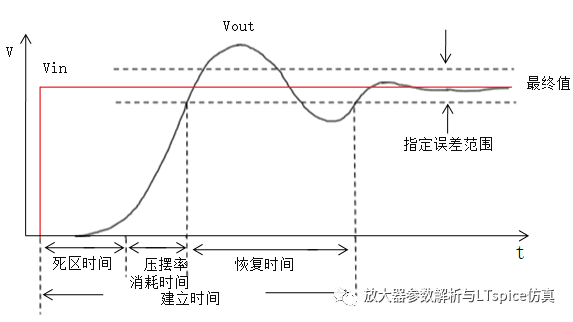

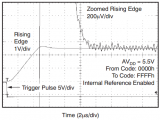

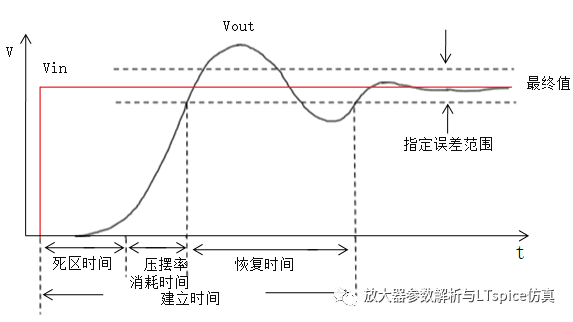

作者: TI專家 Bruce Trump翻譯: TI信號鏈工程師 Michael Huang (黃翔) 建立時(shí)間是運(yùn)放階躍響應(yīng)進(jìn)入和停留在最終值的特定誤差范圍內(nèi)的所需時(shí)間。它在一些應(yīng)用中十分重要

2018-09-20 16:32:36

Hi,All AD7195數(shù)據(jù)手冊中講,當(dāng)選擇Sinc(4)濾波(禁用斬波,禁用零延時(shí)),在通道切換或單個(gè)通道上進(jìn)行轉(zhuǎn)換且輸入發(fā)生階躍變化時(shí),ADC建立時(shí)間為4/fadc。 我的問題時(shí),如果使用了

2018-11-06 09:08:07

ADC時(shí)延和建立時(shí)間的區(qū)別是什么?以及ADC時(shí)延和建立時(shí)間將會如何影響您的應(yīng)用電路?

2021-04-12 07:19:18

在數(shù)據(jù)手冊中,DAC81408的建立時(shí)間為12uS

而爬升速率0~5V為1V/uS,如果控制輸出從0V跳變至5V,以此時(shí)間計(jì)算,時(shí)間為5uS,小于12uS的建立時(shí)間典型值

如上圖所示為數(shù)據(jù)手冊

2024-12-09 08:33:21

有沒有人遇到在DC綜合后分析建立時(shí)間時(shí)序,關(guān)鍵路徑時(shí)序違例是因?yàn)槠鹗键c(diǎn)是在時(shí)鐘的下降沿開始驅(qū)動的,但是設(shè)計(jì)中都是時(shí)鐘上升沿觸發(fā)的。在線等待各位大牛解惑!很急 求大神幫忙!

2015-01-04 15:17:16

8.11 建立時(shí)間違規(guī)的情況我們再來看看保持時(shí)間違規(guī)的情況,如圖8.12所示,這次是數(shù)據(jù)傳輸得太快了,原本應(yīng)該下一個(gè)時(shí)鐘周期到達(dá)clk_r3的數(shù)據(jù)竟然在clk_r3的前一個(gè)時(shí)鐘周期的保持時(shí)間還未過去

2015-07-17 12:02:10

幾天前量測了下intel 南橋發(fā)出到一個(gè)電源控制器的I2C信號,發(fā)現(xiàn)數(shù)據(jù)建立時(shí)間(hold time)只有150ns左右,I2C協(xié)議里面所說至少300ns,這個(gè)問題該怎么解決啊 求大神指導(dǎo)建立時(shí)間有

2013-12-08 00:38:24

我的PGA281增益由1變128時(shí),建立時(shí)間Settling time過長有800uS左右(增益切換后延時(shí)1ms也沒用),可數(shù)據(jù)手冊明明是40us

2024-08-22 06:14:39

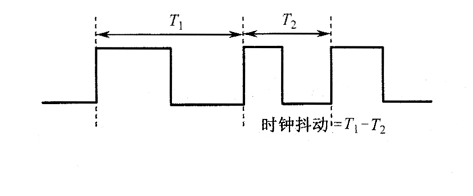

PLL jitter 對建立時(shí)間和保持時(shí)間有什么樣的影響?哪位大神給解答下

2015-10-30 11:16:30

簡單的來分析一下數(shù)據(jù)的建立時(shí)間和保持時(shí)間應(yīng)該滿足怎樣的關(guān)系才能保證被時(shí)鐘lcd_clk穩(wěn)定的鎖存到ADV7123芯片中。首先,我們需要來看看這個(gè)實(shí)例的時(shí)鐘launch edge和latch edge

2019-04-10 06:33:34

在為ad7610選擇一個(gè)單電源的驅(qū)動放大器,手冊中推薦的ad8021是雙電源,建立時(shí)間參數(shù)為:Settling Time to 0.01% VO = 1 V step, RL = 500 Ω 23

2023-11-17 06:22:37

請問,建立時(shí)間裕量為負(fù)值該怎么處理。

2013-12-02 10:38:55

現(xiàn)什么情況?

2. 對于連續(xù)模式和單次模式,建立時(shí)間是否可保持一樣?

3. 有沒有在轉(zhuǎn)換時(shí)間為 500 毫秒的情況下實(shí)現(xiàn)每秒 500 次采樣的可能性?

2025-02-17 07:15:00

?2. 對于連續(xù)模式和單次模式,建立時(shí)間是否可保持一樣? 3. 有沒有在轉(zhuǎn)換時(shí)間為 500 毫秒的情況下實(shí)現(xiàn)每秒 500 次采樣的可能性?

2019-05-30 14:50:14

什么是同步邏輯和異步邏輯?同步電路和異步電路的區(qū)別在哪?為什么觸發(fā)器要滿足建立時(shí)間和保持時(shí)間?

2021-09-28 08:51:33

什么是同步邏輯和異步邏輯?同步電路和異步電路的區(qū)別在哪?為什么觸發(fā)器要滿足建立時(shí)間和保持時(shí)間?什么是亞穩(wěn)態(tài)?為什么兩級觸發(fā)器可以防止亞穩(wěn)態(tài)傳播?

2021-08-09 06:14:00

什么叫建立時(shí)間,保持時(shí)間,和恢復(fù)時(shí)間

2017-04-08 16:52:35

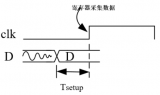

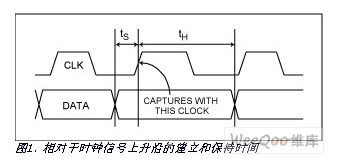

setip 建立時(shí)間 holdup 保持時(shí)間 建立時(shí)間是指, 時(shí)鐘邊緣前,數(shù)據(jù)信號保持不變的的時(shí)間,保持時(shí)間 是指時(shí)鐘跳變邊緣數(shù)據(jù)信號數(shù)據(jù)信號保持不變的時(shí)間。

2019-08-02 11:54:27

。這種方法把準(zhǔn)確性和精確度建立在波形生成器和采樣保持電路的相對速度上。 受測器件的步進(jìn)輸入 本文中,建立時(shí)間是指使用某個(gè)理想步進(jìn)輸入,到受測器件(DUT)進(jìn)入并維持在某個(gè)規(guī)定誤差范圍(終值對稱)內(nèi)

2012-07-30 17:36:20

關(guān)于數(shù)字IC的建立時(shí)間以及保持時(shí)間你想知道的都在這

2021-09-18 07:24:40

多路復(fù)用器輸入端的建立瞬變(由多路復(fù)用器輸出端的大尺度開關(guān)瞬變引起)導(dǎo)致需要較長采集時(shí)間,使得多通道數(shù)據(jù)采集系統(tǒng)的整體吞吐量顯著降低。然后,文中將著重闡述使輸入建立時(shí)間最小化以及提高數(shù)據(jù)吞吐量和系統(tǒng)

2018-10-29 17:06:48

密度。本文將說明多路復(fù)用器輸入端的建立瞬變(由多路復(fù)用器輸出端的大尺度開關(guān)瞬變引起)導(dǎo)致需要較長采集時(shí)間,使得多通道數(shù)據(jù)采集系統(tǒng)的整體吞吐量顯著降低。然后,本文將著重闡述使輸入建立時(shí)間最小化以及提高數(shù)據(jù)吞吐量和系統(tǒng)效率所需的設(shè)計(jì)權(quán)衡。

2020-12-28 07:30:52

建立時(shí)間測量的采樣保持方法測試裝置存在哪些局限性?

2021-04-09 06:08:05

建立時(shí)間(Setup Time)是指觸發(fā)器的時(shí)鐘信號上升沿到來之前,數(shù)據(jù)保持穩(wěn)定不變的時(shí)間。 輸入信號應(yīng)該提前時(shí)鐘上升沿(如上升沿有效)Tsu時(shí)間到達(dá)芯片,這個(gè) Tsu就是建立時(shí)間。如果不滿足建立時(shí)間

2021-07-26 07:36:01

請問,對于觸發(fā)器的時(shí)鐘信號,建立時(shí)間和保持時(shí)間有要求嗎?剛看到一個(gè)門控時(shí)鐘產(chǎn)生毛刺的反例,(如下圖)想到了這個(gè)問題。若此時(shí)鐘信號毛刺極小,有沒有可能被觸發(fā)器忽略呢?為什么呢?如果有可能小到什么程度會被忽略呢?

2012-01-27 18:44:58

作者:Kevin Duke德州儀器今天,我們將介紹兩種相關(guān)的動態(tài)參數(shù) — 壓擺率與建立時(shí)間。如欲了解更多有關(guān)靜態(tài)和動態(tài)參數(shù)的不同之處,敬請參閱本文。什么是壓擺率?TI退休員工模擬專家 Bruce

2018-09-13 09:56:17

示波器測量的是INA333的輸出波形

信號的輸入是應(yīng)變片全橋電路,應(yīng)變片和INA333采用PWM的波形間歇性上電。輸入信號建立時(shí)間ina333電源的波形建立時(shí)間是300us左右,但是輸出信號的建立時(shí)間在1ms的時(shí)候還沒有穩(wěn)定。規(guī)格書里的輸出信號建立時(shí)間小于400us。是電路哪里有問題嗎?

2024-08-13 07:45:40

建立時(shí)間是什么意思?精確測量ADC驅(qū)動電路建立時(shí)間

2021-04-14 06:29:09

AD8021的建立時(shí)間具體是多少,在Datasheet上The AD8021 is a well-behaved amplifier that settles to 0.01% in 23 ns

2018-07-30 06:55:57

您好:我在ADE7880的文檔中多處看到建立時(shí)間,那我在配置或者在編程中如何去考慮這個(gè)建立時(shí)間?

2018-11-05 09:00:08

一般運(yùn)算放大器的datasheet都會給出0.01%建立時(shí)間(有的給出0.1%建立時(shí)間),比如ADA4897,給出2V階躍測試時(shí)0.01%建立時(shí)間為90 ns。

因此對于單運(yùn)放電路來說,建立時(shí)間

2023-11-27 06:54:56

一般運(yùn)算放大器的datasheet都會給出0.01%建立時(shí)間(有的給出0.1%建立時(shí)間),比如ADA4897,給出2V階躍測試時(shí)0.01%建立時(shí)間為90 ns。因此對于單運(yùn)放電路來說,建立時(shí)間可以

2018-11-13 15:08:15

在為ad7610選擇一個(gè)單電源的驅(qū)動放大器,手冊中推薦的ad8021是雙電源,建立時(shí)間參數(shù)為:Settling Time to 0.01% VO = 1 V step, RL = 500 Ω 23

2018-08-01 09:25:24

16444_[。只有降低SPI頻率到20MHz才ok。(2)問題分析:通過示波器測量,發(fā)現(xiàn)DM9051的cs建立時(shí)間和保持時(shí)間很緊張,其它信號質(zhì)量和時(shí)序ok,需要增加cs的建立時(shí)間和保持時(shí)間來試試。(3

2023-02-15 06:55:16

)問題分析:

通過示波器測量,發(fā)現(xiàn)DM9051的cs建立時(shí)間和保持時(shí)間很緊張,其它信號質(zhì)量和時(shí)序ok,需要增加cs的建立時(shí)間和保持時(shí)間來試試。

(3)問題解決:

根據(jù)

2024-06-18 07:31:22

我們對dac7811進(jìn)行了仿真,目的想確認(rèn)dac7811的電壓建立時(shí)間是否滿足0.2us,仿真結(jié)果有些疑問。

(1)、下圖是仿真模型

(2)下圖是仿真結(jié)果,

序號1是輸入模擬電壓給的時(shí)間點(diǎn)

2024-11-14 06:22:34

T2max,最小為T2min。問,觸發(fā)器D2的建立時(shí)間T3和保持時(shí)間應(yīng)滿足什么條件

2019-09-09 17:19:55

計(jì)算開關(guān)電容ADC的建立時(shí)間:很多C8051F器件具有片內(nèi)模/數(shù)轉(zhuǎn)換器ADC這些ADC使用一個(gè)采樣電容該電容被充電到輸入信號電壓由SAR邏輯進(jìn)行數(shù)據(jù)轉(zhuǎn)換由于存在ADC采樣電容輸入阻抗和外部輸

2008-10-30 18:25:08 24

24 該文簡要討論了環(huán)路性能(建立時(shí)間,相位噪聲和雜散信號)和環(huán)路參數(shù)(帶寬,相位裕度等)的相互關(guān)系。提出并分析了一種自適應(yīng)的具有快速建立時(shí)間的鎖相環(huán)結(jié)構(gòu)及其關(guān)鍵模塊(鑒相

2010-04-23 08:33:53 20

20 常估算運(yùn)算放大器建立時(shí)間的方法受示波器分辨率或電路寄生的制約,而且這些方法都未考慮模數(shù)轉(zhuǎn)換器(ADC)的采樣電路、封裝寄生電容和電感等因素。對此給出了一個(gè)精

2010-12-20 17:51:37 39

39 基本概念:線與邏輯、鎖存器、緩沖器、建立時(shí)間、緩沖時(shí)間

基本概念:線與邏輯、鎖存器、緩沖器、建立時(shí)間、緩沖時(shí)間

標(biāo)簽/分類:

2007-08-21 15:17:27 1607

1607 時(shí)延和建立時(shí)間setup在ADC電路中的區(qū)別:對于大多數(shù) ADC 用戶來說,“時(shí)延”和“建立時(shí)間”這兩個(gè)術(shù)語有時(shí)可以互換。但對于 ADC 設(shè)計(jì)人員而言,他們非常清楚

2007-11-22 23:33:07 1940

1940 本文將介紹一種新方法,其經(jīng)過證明可以有效地完成這些測量工作。它是一種相對低成本、簡單的建立時(shí)間測量方法。這種方法把準(zhǔn)確性和精確度建立在波形生成器和采樣保持電路的相

2012-07-27 10:25:16 1810

1810

如何計(jì)算多路復(fù)用器的建立時(shí)間和采樣速率

2013-08-21 17:33:12 0

0 建立時(shí)間和保持時(shí)間貫穿了整個(gè)時(shí)序分析過程。只要涉及到同步時(shí)序電路,那么必然有上升沿、下降沿采樣,那么無法避免setup-time 和 hold-time這兩個(gè)概念。 1. 什么是setup-time

2017-02-08 14:48:11 7008

7008 今天,我們將介紹兩種相關(guān)的動態(tài)參數(shù) — 壓擺率與建立時(shí)間。如欲了解更多有關(guān)靜態(tài)和動態(tài)參數(shù)的不同之處,敬請參閱本文。

2018-07-10 16:14:00 6586

6586

建立時(shí)間;保持時(shí)間;建立時(shí)間裕量;保持時(shí)間裕量

2018-12-01 08:20:57 4312

4312

建立和保持時(shí)間的話,那么DFF將不能正確地采樣到數(shù)據(jù),將會出現(xiàn)metastability 的情況。如果數(shù)據(jù)信號在時(shí)鐘沿觸發(fā)前后持續(xù)的時(shí)間均超過建立和保持時(shí)間,那么超過量就分別被稱為建立時(shí)間裕量和保持時(shí)間裕量。

2020-10-27 16:26:00 11

11 本篇仿真介紹放大器的建立時(shí)間,也稱為上升時(shí)間。它是高速放大電路、或在SARADC驅(qū)動電路設(shè)計(jì)時(shí),需要謹(jǐn)慎評估的參數(shù)。

2021-02-15 16:37:00 7260

7260

AN-1024: 如何計(jì)算多路復(fù)用器的建立時(shí)間和采樣速率

2021-03-21 09:43:42 8

8 MT-046:運(yùn)算放大器建立時(shí)間

2021-03-21 11:48:10 11

11 AN-256:準(zhǔn)確測試運(yùn)算放大器建立時(shí)間

2021-04-17 19:28:04 1

1 AN74組件和測量改進(jìn)確保16位DAC建立時(shí)間

2021-04-20 08:04:18 8

8 AN10-運(yùn)算放大器建立時(shí)間的測量方法

2021-04-27 15:21:40 2

2 AN-359:運(yùn)算放大器的建立時(shí)間

2021-04-29 15:28:46 4

4 寬帶放大器的128-2納秒、1%分辨率的建立時(shí)間測量

2021-05-25 17:05:58 6

6 AN79-30納秒精密寬帶放大器建立時(shí)間測量

2021-05-27 09:22:10 7

7 時(shí)間裕量包括建立時(shí)間裕量和保持時(shí)間裕量(setup slack和hold slack)。從字面上理解,所謂“裕量”即富余的、多出的。什么意思呢?即保持最低要求的建立時(shí)間或保持時(shí)間所多出的時(shí)間,那么“裕量”越多,意味著時(shí)序約束越寬松。

2022-08-04 17:45:04 1079

1079 時(shí)間裕量包括建立時(shí)間裕量和保持時(shí)間裕量(setup slack和hold slack)。從字面上理解,所謂“裕量”即富余的、多出的。

2023-02-06 11:06:03 793

793 本篇通過仿真介紹放大器的建立時(shí)間,也稱為上升時(shí)間。它是高速放大電路、或在SAR ADC驅(qū)動電路設(shè)計(jì)時(shí),需要謹(jǐn)慎評估的參數(shù)。

2023-02-22 11:29:31 1919

1919

運(yùn)算放大器建立時(shí)間是保證數(shù)據(jù)采集系統(tǒng)性能的關(guān)鍵參數(shù)。為了實(shí)現(xiàn)精確的數(shù)據(jù)采集,運(yùn)算放大器輸出必須在A/D轉(zhuǎn)換器能夠準(zhǔn)確數(shù)字化數(shù)據(jù)之前建立。然而,建立時(shí)間通常不是一個(gè)容易測量的參數(shù)。

2023-06-17 10:37:54 1635

1635

??本文主要介紹了建立時(shí)間和保持時(shí)間。

2023-06-21 14:38:26 4826

4826

在時(shí)序電路設(shè)計(jì)中,建立時(shí)間/保持時(shí)間可以說是出現(xiàn)頻率最高的幾個(gè)詞之一了,人們對其定義已經(jīng)耳熟能詳,對涉及其的計(jì)算(比如檢查時(shí)序是否正確,計(jì)算最大頻率等)網(wǎng)上也有很多。

2023-06-27 15:43:55 18883

18883

建立時(shí)間和保持時(shí)間是SOC設(shè)計(jì)中的兩個(gè)重要概念。它們都與時(shí)序分析有關(guān),是確保芯片正常工作的關(guān)鍵因素。

2023-08-23 09:44:55 1828

1828 電子發(fā)燒友網(wǎng)站提供《多路復(fù)用器的建立時(shí)間和采樣速率的計(jì)算.pdf》資料免費(fèi)下載

2023-11-24 11:03:17 0

0 文件提到兩種setup/hold測量方式:10% push-up和pass/fail,按照TSMC說法,前者會更樂觀一些,因此如果是采用前者(10% push-up)的測量方式得到建立時(shí)間和保持時(shí)間,需要十份小心時(shí)序裕量是否足夠,最好人為添加margin。

2023-12-05 11:19:38 3630

3630

采用CMOS技術(shù)設(shè)計(jì)的數(shù)字電路通常將電源擺幅的中間值作為切換點(diǎn)。因此,時(shí)間參考點(diǎn)定在信號邊沿的中點(diǎn)。圖1波形標(biāo)明了器件在典型條件下的建立和保持時(shí)間。注意此時(shí)定義的這兩個(gè)參數(shù)均為正值,但在建立或保持時(shí)間出現(xiàn)負(fù)值時(shí)將會令人迷惑不解。

2024-02-15 16:57:00 2100

2100

電子發(fā)燒友App

電子發(fā)燒友App

評論