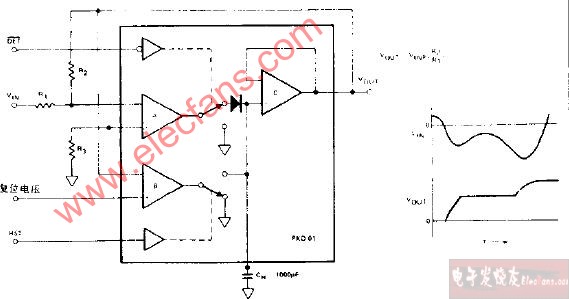

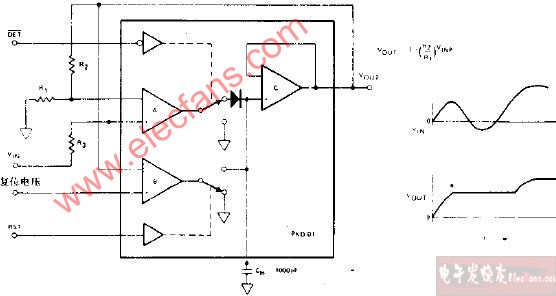

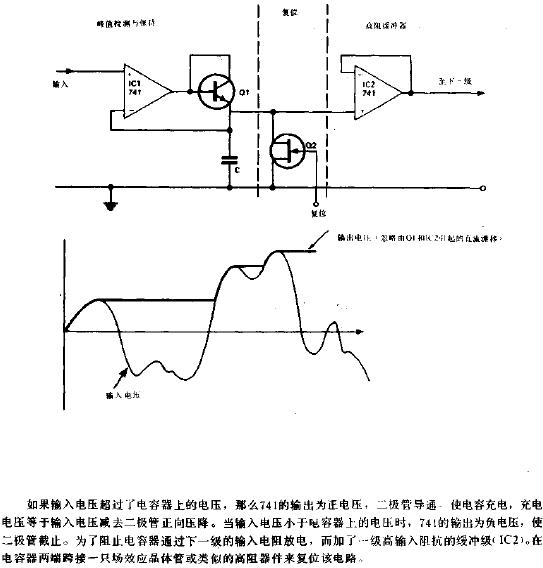

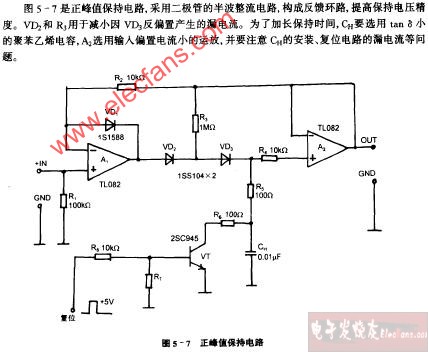

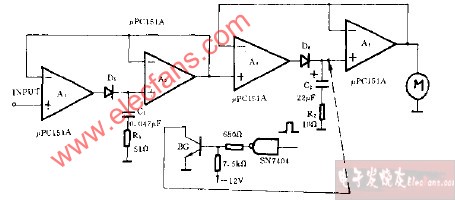

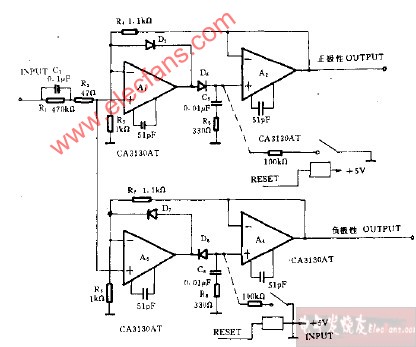

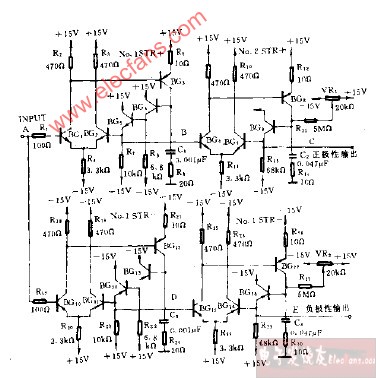

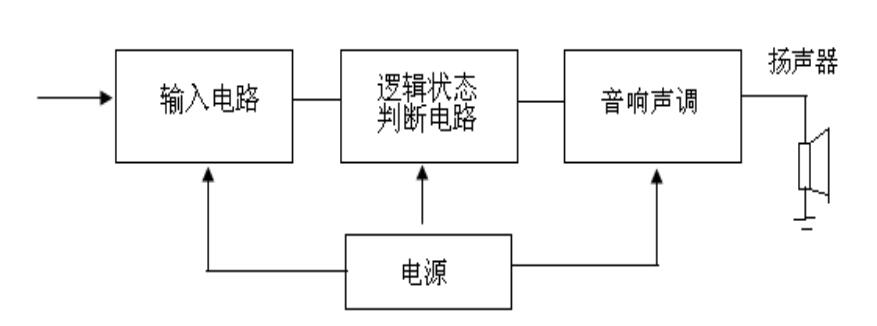

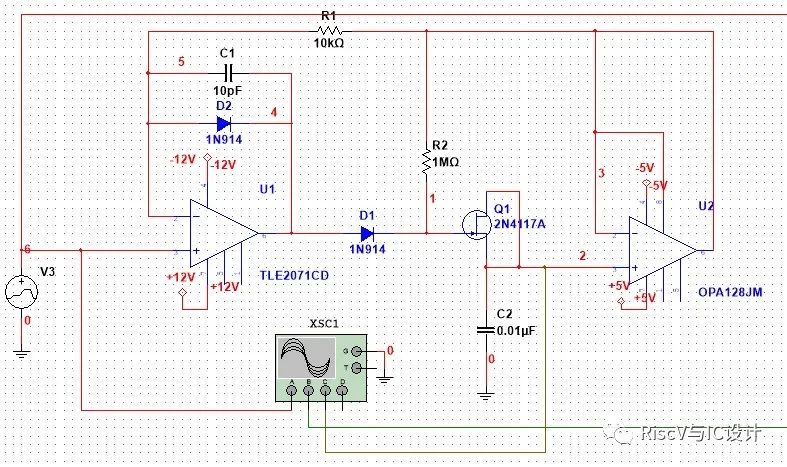

可用邏輯電平選擇極盡性的正、負峰值保持電路

- 保持電路(24254)

相關推薦

熱點推薦

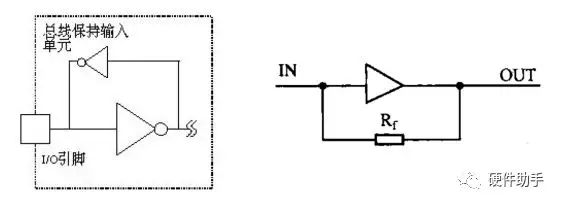

邏輯電平之特殊互連(總線保持、串聯阻尼電阻、熱插拔)

本篇主要介紹邏輯互連中的一些具有特殊功能的互連。這些特殊功能包括總線保持、串聯阻尼電阻、熱插拔等。 1、總線保持(Bus Hold) 假設初始狀態為輸入端和輸出端均為高電平,反饋電路沒有電流

2020-12-20 12:02:06 9615

9615

9615

9615

二進制與邏輯電平的變化范圍

二進制中的兩個數字0和1稱為位(bit, 是二進制數字binary digit的縮寫)。在數字電路中,使用兩個不同的電平表示這兩個位。一般情況下,1 用高電平表示,0用低電平表示,這種邏輯體制稱為正邏輯。

2024-02-04 16:54:09 3034

3034

3034

3034

100MHz峰值檢測保持電路

各位大俠,現在需要檢測保持一個幾十ns的脈沖峰值,峰值大概在10mV左右(如果太小可以增大到幾百mV),如下圖所示。目前看了使用比較器的高速峰值保持電路,請問使用該電路能達到10ns的峰值檢測保持嗎?器件該怎么選擇?或者有沒有使用峰值檢波IC或者其他的方案可以選擇?希望各位指教。

2016-11-01 19:47:06

峰值保持電路保持電壓不正確的問題

小弟最近正在搞一個高速窄脈沖峰值保持的電路,信號的上升沿>2ns,峰值在1V到2V之間,根據資料搭出了一個電路,但是峰值保持的電壓不對,不知道問題出在哪里。現在問題是上升沿為5ns時,峰值1V

2015-12-15 20:32:20

峰值保持電路設計

想要保持探測器輸入的窄脈沖信號的峰值,輸入脈沖寬度大概10ns,重頻幾十Hz,要實現峰值保持時間為幾毫秒,該使用哪種峰值保持電路設計,電壓型峰值保持電路能達到要求嗎?

2016-07-28 16:48:45

邏輯電平介紹

,下面以邏輯器件的功能、工藝特點和邏輯電平等方法來進行簡單描述。 :TTL和CMOS器件的功能分類按功能進行劃分,邏輯器件可以大概分為以下幾類: 門電路和反相器、選擇器、譯碼器、計數器、寄存器、觸發器、鎖

2009-04-12 12:03:33

邏輯電平設計規范(一)

必須要求輸入高電平> Vih,輸入低電平<Vil,而如果輸入電平在閾值上下,也就是Vil~Vih這個區域,電路的輸出會處于不穩定狀態。對于一般的邏輯電平,以上參數的關系如下

2008-06-24 09:38:52

OPA615做峰值保持,輸出一直有1v的門檻電壓,為什么?

OPA615

按手冊中圖48設計電路,hold control端一直接高電平,輸入1.5us正脈沖,電容上有600mv的門檻電壓,只有當脈沖峰值超過600mv時才能看到脈沖,電壓輸出端有1v的門檻

2024-08-16 12:17:47

OPA860做峰值保持電路,無法實現峰值保持的功能是為什么?

我用opa860芯片做峰值保持電路,輸入為10ns的脈沖信號,我在論壇里看到有類似的帖子,并且按照上面的電路原理圖用Tina仿真,仿真結果是能夠實現峰值保持電路功能的。并且設計了電路板,調試了很久

2024-08-01 07:46:08

PIN如果選擇正或負,IOC是否總是設置為兩者

PIN模塊:如果選擇正或負,IOC總是設置為兩者。注意:如果使用PLL,系統時鐘給出大于推薦值(20MHz)的警告。

2020-05-04 18:19:59

二極管換成肖特基二極管1n5817后,都不能保持峰值,只是跟隨的作用,為什么?

電路原理圖就是芯片手冊里的,仿真用orcad。有幾個問題,謝謝指導~

1.輸入負脈沖信號,放置二極管1N4148,control端一直接正電壓即一直處于跟隨狀態。保持峰值結果如下圖,紅色是脈沖

2024-09-10 06:41:11

做一個基于OPA615的峰值檢測模塊,在HOLD腳高電平時為采樣時保持的峰值不對,為什么?

最近在做一個基于OPA615的峰值檢測模塊,用的是數據手冊上的電路圖,但是調試過后,發現有問題:輸出的波形形式是正確的,就是在HOLD腳高電平時為采樣,低電平時為保持,頻率也是和七腳脈沖頻率相同

2024-09-12 07:36:02

關于震蕩電路中選擇電容問題

最近看了不少關了這種電路的圖,其中好幾個都選擇的是有極電解電容但我很奇怪的是,如果選擇有極電容時候,就比如右半邊來說,到底選擇左正右負?還是左負右正呢?因為剛開始時候電流走向是1的線路,也說是需要左

2020-01-23 18:50:38

如何從負脈沖獲得正脈沖

本帖最后由 gk320830 于 2015-3-9 15:55 編輯

本例中的電路可將負脈沖轉換為正脈沖。盡管這個任務看似簡單,但負脈沖的幅度為-5V~-2V。按照不同應用要求,正脈沖也需要

2011-10-14 17:19:21

如何將開關的開/斷狀態轉變成Arduino能夠讀取的高/低電平

如何將開關的開/斷狀態轉變成Arduino能夠讀取的高/低電平。解決的辦法是通過上 /下拉電阻,按照電路的不同通常又可以分為正邏輯(Positive Logic)和負邏輯(Inverted Logic)兩種...

2022-01-17 08:35:42

數字信號電平轉換

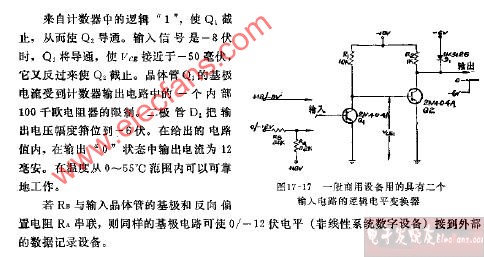

性,系統電源為負極性。兩個電路都利用NPN晶體管將比較器的輸出電平偏移VBE (R5 + R4)/R5 ≈ 4.5V (對于單相輸出,可以選擇單輸出比較器)。圖3. 該電路把負脈沖輸出轉換成正脈沖輸出

2020-11-23 09:36:51

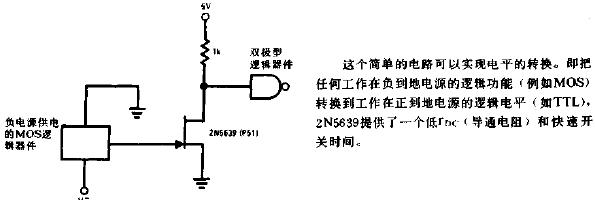

有負電勢的反相電平轉換電路

180°反相,但這個反相并不影響器件的功能。 這是一款簡單而快速的電平轉換電路,可以將輸入時鐘調節為適應正、負電壓電平。 電平轉換電路包括快速切換的晶體管Q1和Q2.用戶選擇電平轉換為高和轉換為低

2018-11-29 17:01:56

模擬峰值保持電路放電問題

如圖,在multsim上仿真峰值保持電路,用模擬開關控制放電。仿真出來在模擬開關放電結束的時刻,C4上出現負電平,不知道是什么引起的。由于C點出現負電平,反饋到運放1的反向端后會使得B點輸出高電平,繼而使二極管D1導通,C4又被充電了。搜了很多相關帖子都沒看到有人講過這里的問題。

2019-11-25 19:44:09

求助,對于有正有負的正弦脈沖信號應選擇怎樣的ADC進行采樣?

需要選擇一款帶寬在2MHz以上、采樣率在20MSPS、位數最好是16位的高速ADC,對于有正有負的正弦脈沖信號應選擇怎樣的ADC進行采樣?

2023-12-21 07:40:09

簡單而快速的電平轉換電路

這是一款簡單而快速的電平轉換電路,可以將輸入時鐘調節為適應正、負電壓電平。upg4hw電平轉換電路包括快速切換的晶體管Q1和Q2。用戶選擇電平轉換為高和轉換為低,這是直流偏置電壓,連接到晶體管的射極

2013-09-30 17:02:18

請問對于有正有負的正弦脈沖信號應選擇怎樣的ADC進行采樣?

需要選擇一款帶寬在2MHz以上、采樣率在20MSPS、位數最好是16位的高速ADC,對于有正有負的正弦脈沖信號應選擇怎樣的ADC進行采樣?附件print_26.bmp2.3 MB

2018-10-26 09:33:24

門電路課件(ppt電子教案)

1、門電路2、高低電平與正負邏輯高電平為1,低電平為0稱為正邏輯高電平為0,低電平為1稱為負邏輯3、分立元件門電路和集成門電路2. 2 二極管和三極管的開

2009-07-15 18:49:29 0

0

0

0幾種常用高速邏輯電平電路的特點及應用

幾種常用邏輯電平電路的特點及應用

幾種常用邏輯電平電路的特點及應用

標簽/分類:

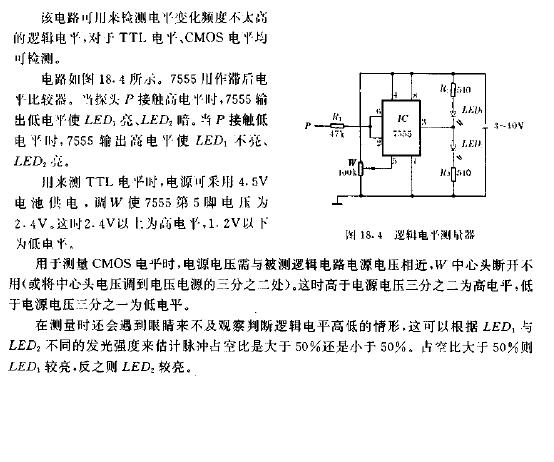

在通用的電子器件設備中,TTL和CMOS電路的應用非常廣泛。但

2007-08-21 15:34:59 1804

1804

1804

1804

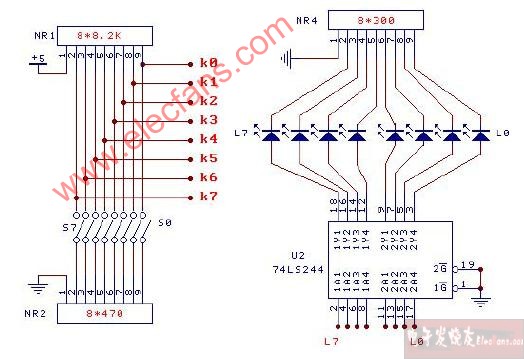

邏輯電平開關電路

邏輯電平開關電路如圖所示實驗臺右下方設有8個開關K7~K0,開關撥到“1”位置時開關斷開,輸出高電平。向下打到“0”位置時開關接通,輸出低電平。電路中

2009-03-25 09:29:17 6749

6749

6749

6749

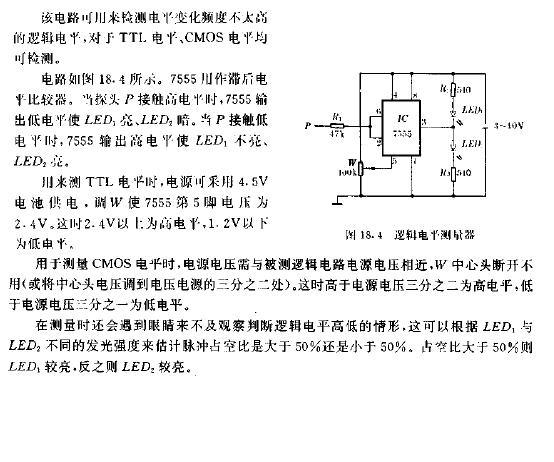

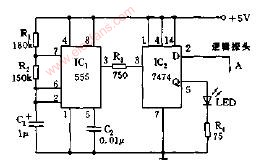

正的邏輯探針電路,Logic Probe Plus

正的邏輯探針電路,Logic Probe Plus

This project is based on a probe logic states, capable of measuring levels fr

2010-04-11 09:24:33 2355

2355

2355

2355

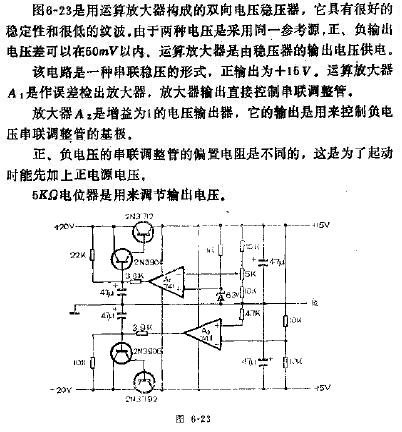

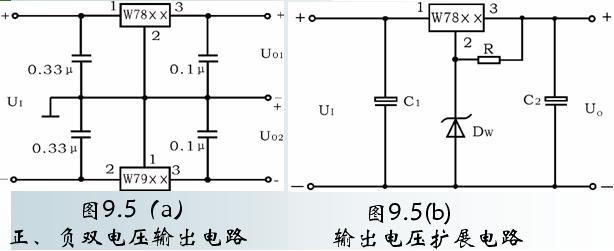

W611、w616組成正、負穩壓電路圖

圖中所示是用W611和W616正,負集成穩壓器組成的正,負穩壓電路的應用電路.當需要正,負兩組穩壓電源時,可以用W611

2010-10-17 12:49:31 1943

1943

1943

1943

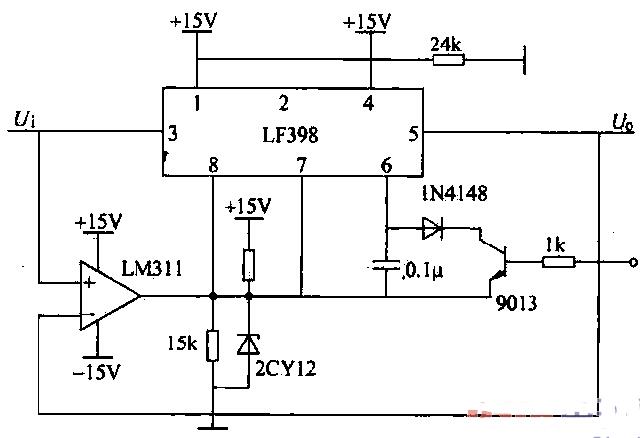

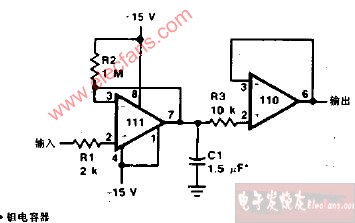

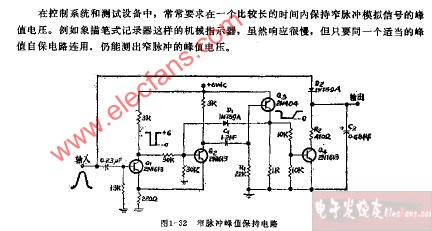

高速脈沖峰值保持電路的設計

為滿足能譜分析中多道脈沖幅度分析器A/D轉換的要求,設計了一種高速脈沖峰值保持電路。以高速電壓比較器LM311、采樣/保持芯片LF398作為主要器件,具有幅度判別、波形采樣、峰值保

2012-06-28 17:16:15 639

639

639

639一種實用的峰值保持電路

介紹了一種以采樣/ 保持器L F398 芯片為主要器件的峰值保持電路。該電路具有結構簡單、調試方便、性能優良等優點可廣泛應用于各種脈沖分析系統。

2016-03-16 14:48:35 140

140

140

140lf398峰值采樣保持電路

摘要 :本文介紹了一種以采樣/ 保持器 L F398 芯片為主要器件的峰值保持電路。該電路具有結構簡單、調試方便、性能優良等優點 ,可廣泛應用于各種脈沖分析系統。

2017-11-04 10:07:35 28647

28647

28647

28647

常用邏輯電平及光模塊接口耦合電路的全解析

介紹常用的幾種邏輯電平,然后給出其與光模塊的接口電路。 TTL 電路的電平就叫 TTL 電平,CMOS 電路的電平就叫 CMOS 電平。 TTL 集成電路的全名是晶體管-晶體管邏輯集成電路(Transistor-Transistor Logic),標準 TTL 輸入高電平最小 2V,輸出高電平

2017-11-06 16:50:08 100

100

100

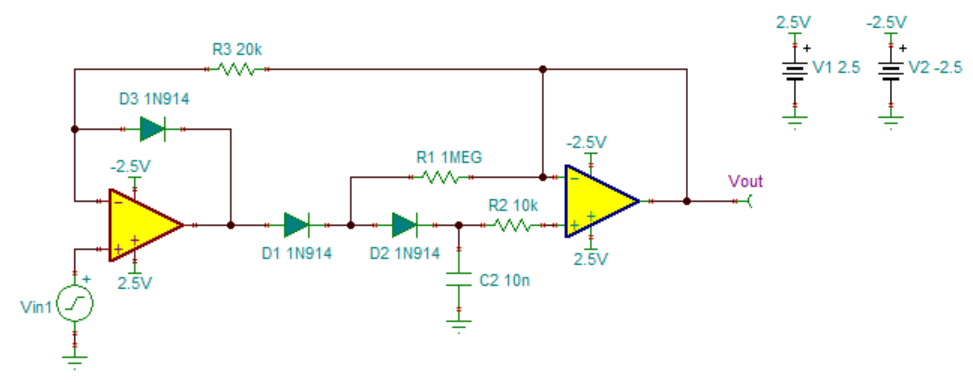

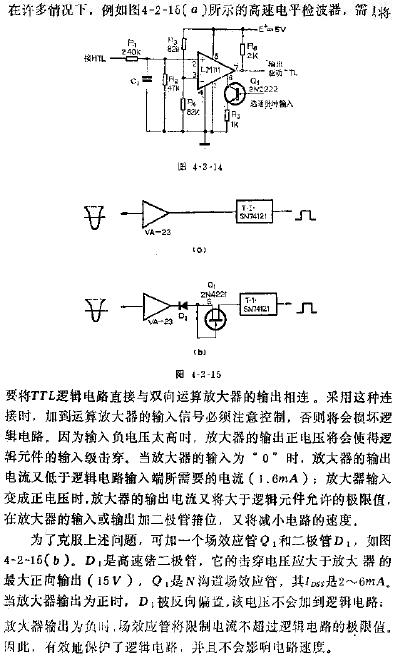

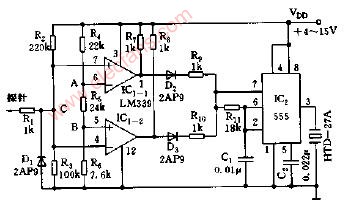

100由SMP04與運放構成的具有保持控制的正、負峰值檢波電路

關鍵詞:SMP04 , 檢波電路 如圖所示為由SMP04與運放構成的具有保持控制的正、負峰值檢波電路。放大器A用于正峰值檢波,放大器B用于負峰值檢波。假定SMP04內部采樣保持開關閉合,當正輸入電壓

2019-01-28 18:38:01 2061

2061

2061

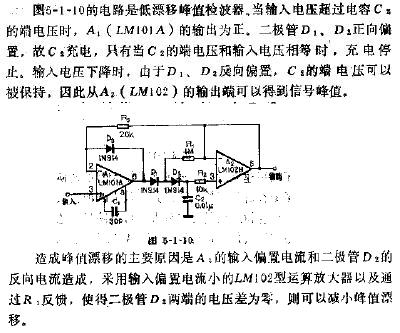

2061峰值電壓采樣保持電路

峰值電壓采樣保持電路:峰值電壓采樣保持電路如圖12-50所示。峰值電壓采樣保持電路南一片采樣保持器芯片LF398和一塊電壓比較器LM311構成。LF398的輸出電壓和輸入電壓通過LM3J1進行比較t當U.》Uo時.

2020-01-21 17:21:00 17745

17745

17745

17745

邏輯電平--差分信號(PECL、LVDS、CML)電平匹配

由于各種邏輯電平的輸入、輸出電平標準不一致,所需的輸入電流、輸出驅動電流也不同,為了使不同邏輯電平能夠安全、可靠地連接,邏輯電平匹配將是電路設計中必須考慮的問題。

2022-11-10 10:01:54 17496

17496

17496

17496【硬聲推薦】邏輯電平視頻合集

為了精簡電路 電器中會用到邏輯電平代替復雜的接線 他們都是如何設計的呢? CMOS器件與TTL器件? ? CMOS電平與TTL電平 ? 如何利用MOS管實現雙向電平轉換 ? 什么是LVDS電平

2022-12-14 11:36:07 1241

1241

1241

1241邏輯電平轉換

自TTL和5V CMOS成為邏輯電路的主要標準以來,電子設計發生了很大變化。現代電子系統的日益復雜導致邏輯電壓降低,這反過來又可能導致系統內邏輯系列的輸入和輸出電平不兼容。例如,工作在1.8V的數字

2023-03-02 13:55:39 2805

2805

2805

2805

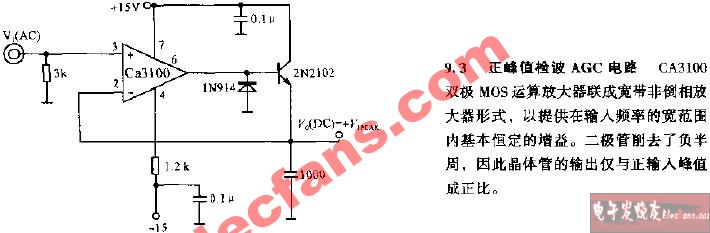

峰值檢測電路的使用場景

峰值檢測電路(Peak Detection Circuit)是一種用于測量信號中最大值(正峰值)或最小值(負峰值)的電子電路。這種電路在很多領域都有廣泛的應用,以下是峰值檢測電路的一些典型使用場景。

2023-06-06 17:22:32 5523

5523

5523

5523

基于二極管的鉗位電路

這是另一個使用二極管的電路,它工作在輸入波形上,但與限波電路不同。箝位電路用于為輸入交流信號添加直流電平,并將交流信號的峰值電壓(正峰值和負峰值)改變到任何所需的電平。這里的直流電平是指交流信號從正半周期移動到負半周期的0v 點,反之亦然。簡單地放置箝位電路可以將整個信號轉移到正側或負側。

2023-06-15 18:13:24 2638

2638

2638

2638

什么是邏輯電平?如何實現電平轉換?(原理講解+電路圖)

邏輯電平是數字電子系統中的關鍵概念之一。它決定了信號被認定為高電平還是低電平,并進一步影響著數字電路的正確操作。邏輯電平是用來表示數字信號狀態的電壓水平。在數字電子系統中,常用的邏輯電平有高電平

2023-11-24 08:20:20 13297

13297

13297

13297

什么是正尖脈沖?什么是負尖脈沖?

什么是正尖脈沖?什么是負尖脈沖? 正尖脈沖和負尖脈沖是時間信號中常見的兩種形式。它們是一種特殊的脈沖信號,具有較短的持續時間和較高的峰值幅度。 首先,正尖脈沖是一種單極性脈沖信號,其峰值幅度快速上升

2024-02-18 09:43:36 5271

5271

5271

5271邏輯電平輸出是什么意思

邏輯電平輸出是數字電路中的一個重要概念,它涉及到數字信號的表示和傳輸。在數字電路中,邏輯電平通常指的是電路中用于表示二進制數字(0和1)的電壓水平。邏輯電平輸出則是指電路輸出端能夠提供的邏輯電平

2024-09-20 17:32:57 2210

2210

2210

2210峰值檢測電路的基本組成

峰值檢測電路(Peak Detection Circuit),又稱為峰值檢測器(Peak Detector),是一種用于測量信號波形中最大值(正峰值)或最小值(負峰值)的電子電路。這種電路在信號處理

2024-10-10 16:10:13 5432

5432

5432

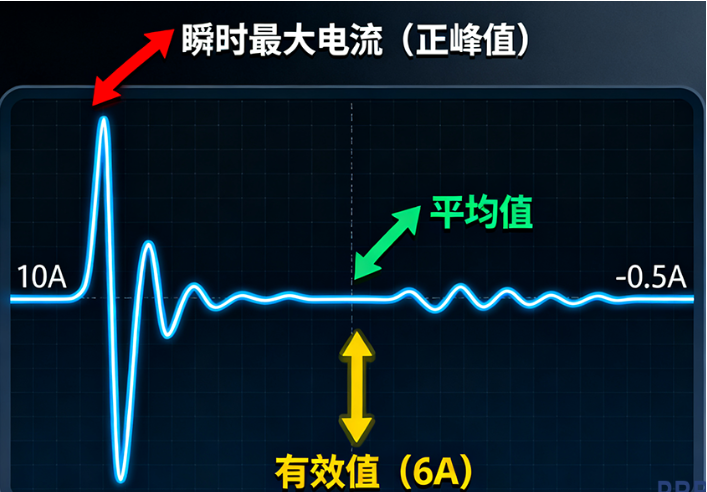

5432示波器測電流:正、負峰值之差≠電流大小

用示波器觀測電流時,一個極易踩陷的認知陷阱是:將"正、負峰值之差"直接當作電流的實際大小。 這種理解會徹底混淆"峰峰值"與"電流強度"的本質區別——前者只是描述信號擺幅的標尺,后者才是衡量電流強弱

2025-11-12 13:52:19 364

364

364

364

電子發燒友App

電子發燒友App

評論