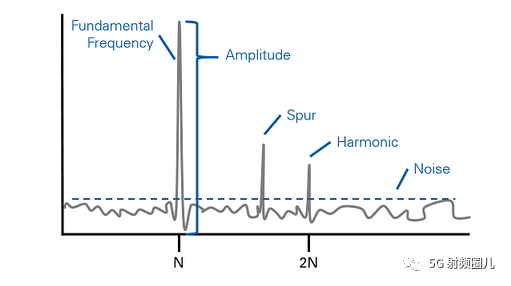

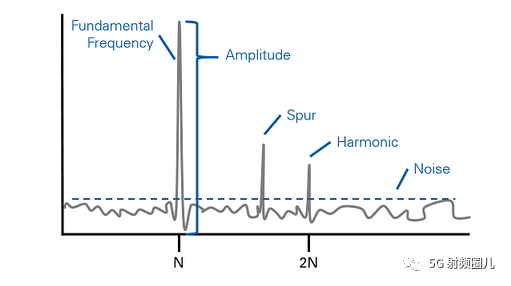

鎖相環(huán) (PLL) 和壓控振蕩器 (VCO) 輸出特定頻率的RF信號(hào),理想情況下此信號(hào)應(yīng)當(dāng)是輸出中的唯一信號(hào)。但事實(shí)上,輸出中存在干擾雜散信號(hào)和相位噪聲。本文討論最麻煩的雜散信號(hào)之一——整數(shù)邊界雜散,它如何仿真與消除,你真的搞清楚了?

2023-05-22 11:10:35 10630

10630

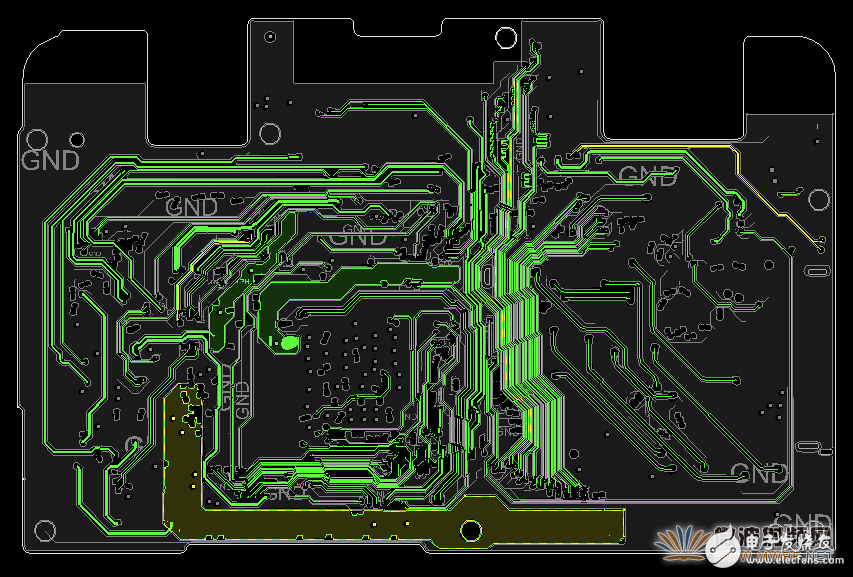

在整個(gè)PCBA生產(chǎn)制造過(guò)程中, PCB 設(shè)計(jì)是至關(guān)重要的一部分,今天主要是關(guān)于 PCB 雜散電容、影響PCB 雜散電容的因素,PCB 雜散電容計(jì)算,PCB雜散電容怎么消除。

2023-09-11 09:41:20 2916

2916

對(duì)于高速TIA的PCB來(lái)說(shuō),最大的挑戰(zhàn)就是如何減小雜散電容Cstray了** 。這是為什么呢?假如帶寬很高,增益很高,那么Cf可能需要設(shè)置在如0.5pF,而普通貼片電阻的雜散電容就有0.1pF。

2023-11-01 10:59:04 2532

2532

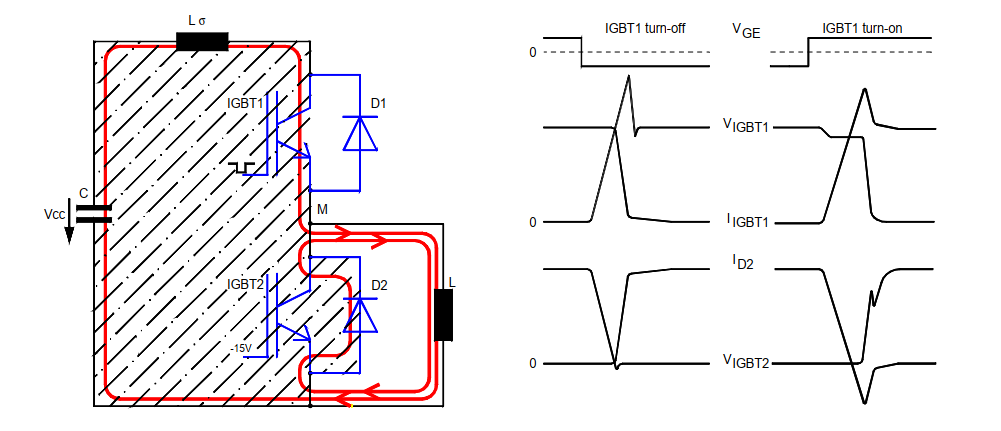

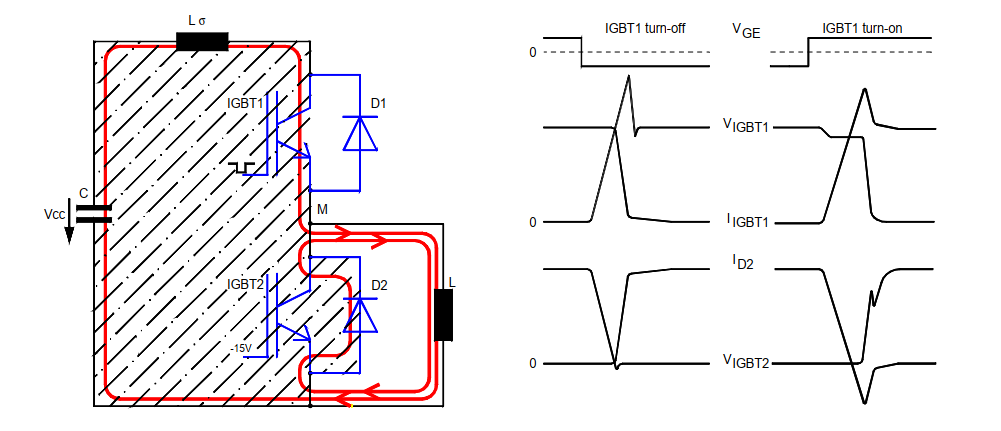

在IGBT功率模塊的動(dòng)態(tài)測(cè)試中,夾具的雜散電感(Stray Inductance,Lσ)是影響測(cè)試結(jié)果準(zhǔn)確性的核心因素。雜散電感由測(cè)試夾具的layout、材料及連接方式引入,會(huì)導(dǎo)致開(kāi)關(guān)波形畸變、電壓尖峰升高及損耗測(cè)量偏差。

2025-06-04 15:07:31 1752

1752

消除所有雜散。在系統(tǒng)機(jī)柜中,對(duì)傳感器至DAQ板之間的線(xiàn)路進(jìn)行布線(xiàn)時(shí)應(yīng)格外注意。將敏感的低電平模擬信號(hào)與大電流電力線(xiàn)隔離開(kāi)來(lái)是一個(gè)良好的操作習(xí)慣。 由燈具輻射導(dǎo)致的雜散問(wèn)題在測(cè)試

2019-02-14 14:18:45

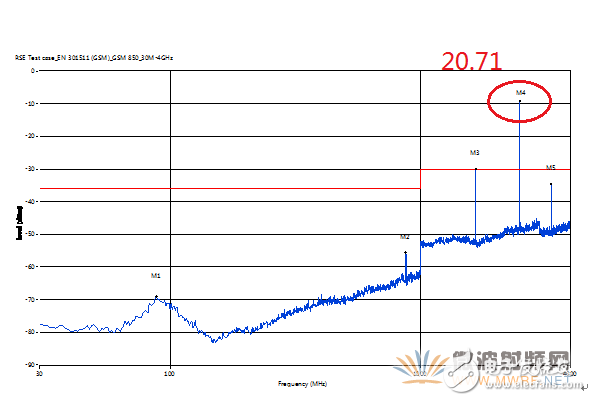

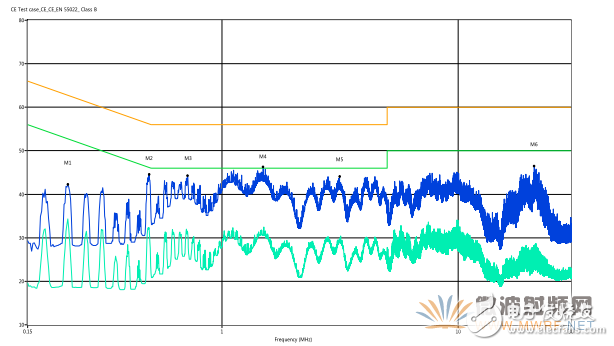

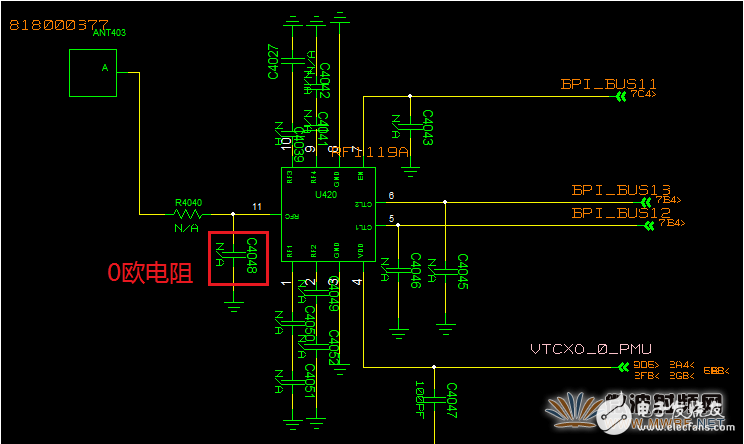

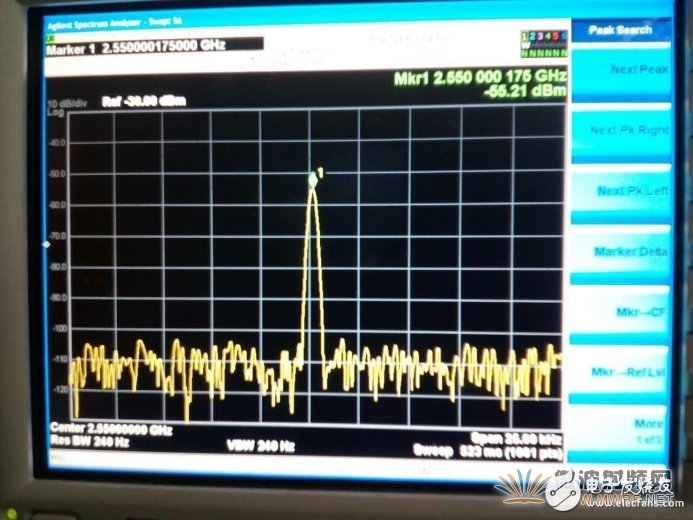

消費(fèi)市場(chǎng)認(rèn)可。是德科技在測(cè)試測(cè)量領(lǐng)域有著悠久的歷史,從1938年第一臺(tái)諧波分析儀面世(彼時(shí)還時(shí)HP公司)到如今110GHz毫米波測(cè)試測(cè)量方案的開(kāi)發(fā),一直為我們產(chǎn)品研發(fā)領(lǐng)域的驗(yàn)證帶來(lái)不同的驚喜。以下通過(guò)一個(gè)案例,使用是德科技測(cè)試測(cè)量解決方案,完成無(wú)線(xiàn)智能終端產(chǎn)品的輻射雜散的最終優(yōu)化。

2019-06-10 06:38:45

雜散測(cè)試線(xiàn)損問(wèn)題? 有的時(shí)候是一個(gè)范圍,怎么確定線(xiàn)損呢?

2020-05-08 05:55:31

雜散測(cè)試線(xiàn)損問(wèn)題? 有的時(shí)候測(cè)得是一個(gè)范圍,怎么確定線(xiàn)損呢?

2016-09-11 23:41:06

,環(huán)路濾波器可以進(jìn)行有效抑制。所以在實(shí)際使用中,這種參考雜散可以不予考慮。但是由于反饋中引入了小數(shù),特定的小數(shù)部分也會(huì)引起相應(yīng)的雜散。其分布規(guī)律如下。設(shè)小數(shù)部分的分母為DEN:(1)一階分?jǐn)?shù)雜散。最大

2019-01-16 12:27:07

分頻的鎖相環(huán)雜散的分布規(guī)律是什么?A:小數(shù)分頻的鎖相環(huán)由于應(yīng)用在工作的鑒相頻率較高,所以其參考雜散也會(huì)分布到偏離載波很遠(yuǎn)的位置上,環(huán)路濾波器可以進(jìn)行有效抑制。所以在實(shí)際使用中,這種參考雜散可以不予考慮

2017-04-27 15:58:16

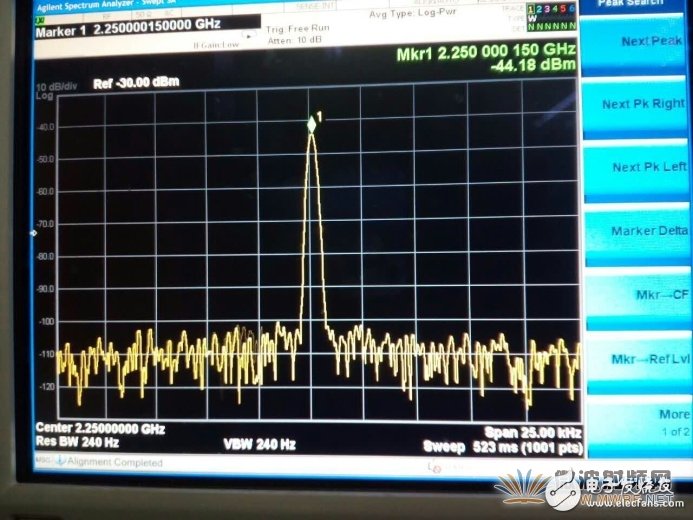

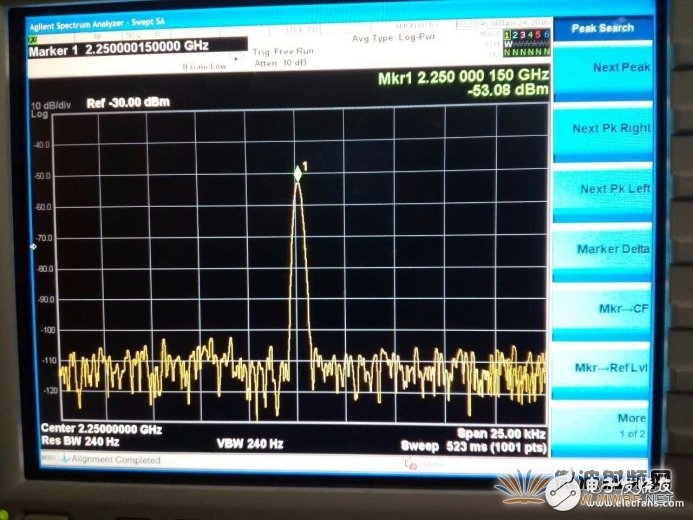

出現(xiàn)一個(gè)與基帶信號(hào)相關(guān)的雜散點(diǎn)幅度-50dBm左右,影響了射頻輸出的Sfdr。具體現(xiàn)象:

輸出2.2ghz點(diǎn)頻時(shí),雜散點(diǎn)在2.6GHz

輸出2.3ghz點(diǎn)頻時(shí),雜散在2.5ghz

輸出2.4ghz點(diǎn)頻

2023-12-04 07:39:16

我們準(zhǔn)備把AD9361用于TDD系統(tǒng),但由于時(shí)延等問(wèn)題,想把9361配置成FDD模式,通過(guò)外部的開(kāi)關(guān)實(shí)現(xiàn)TDD切換;需要了解一下FDD模式下TX通道的雜散/噪底等情況,以便設(shè)計(jì)開(kāi)關(guān)的收發(fā)隔離;1

2018-12-27 09:24:47

各位大牛,請(qǐng)教一下。我現(xiàn)在用AD9467-250,采樣時(shí)鐘用AD9517-3出的200MHz,采集70M、0dBm單音信號(hào)。頻譜上出現(xiàn)較多的雜散。ADC前端電路按照AD9467手冊(cè)推薦的設(shè)計(jì)。ADC

2019-01-25 08:21:14

各位大牛,請(qǐng)教一下。我現(xiàn)在用AD9467-250,采樣時(shí)鐘用AD9517-3出的200MHz,采集70M、0dBm單音信號(hào)。頻譜上出現(xiàn)較多的雜散。ADC前端電路按照AD9467手冊(cè)推薦的設(shè)計(jì)。ADC

2023-12-08 06:52:03

參考輸入為245.76MHz/0dBm,輸出61.44MHz附近給鎖相環(huán)做參考,可是輸出一直有雜散。我改用信號(hào)源直接給鎖相環(huán)提供參考就沒(méi)有雜散了,所以推斷出是AD9912引入的雜散。我同事他也用

2018-12-25 11:41:21

,85Hz和110Hz及其N(xiāo)次諧波的雜散。時(shí)鐘采用400MHz,對(duì)時(shí)鐘的實(shí)現(xiàn)是100MHz晶振通過(guò)放大器飽和區(qū)取出4次諧波,通過(guò)聲表濾波器和放大器,對(duì)400MHz進(jìn)行放大濾波處理。不知道這種時(shí)鐘的實(shí)現(xiàn)有沒(méi)有問(wèn)題?時(shí)鐘的功率肯定夠。求解?

2019-02-22 08:27:59

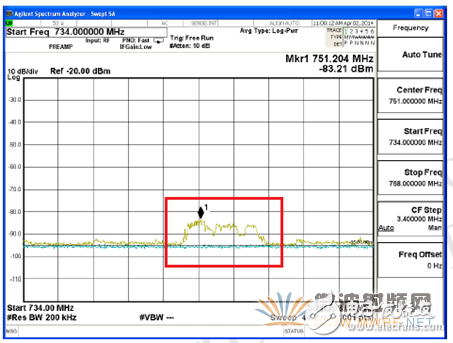

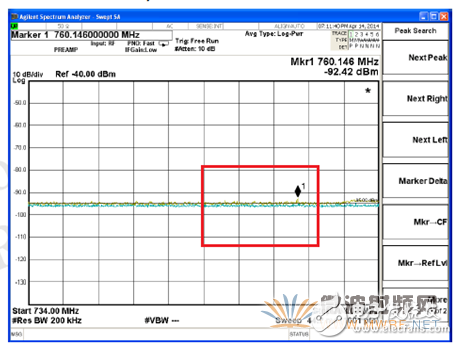

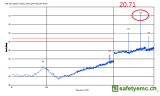

濾波按照仿真參數(shù)設(shè)計(jì)和調(diào)試,仿真結(jié)果沒(méi)有此雜散,而實(shí)際無(wú)論如何都存在 此雜散,我現(xiàn)在弄不清楚此雜散的來(lái)源,頻譜見(jiàn)下圖所示.

2018-10-12 09:24:23

ATK-HSWLDBG無(wú)線(xiàn)調(diào)試器-帶小接收端 BURNER 5V

2023-03-28 13:05:52

我用cc1120實(shí)現(xiàn)頻分復(fù)用,現(xiàn)在發(fā)現(xiàn)存在雜散現(xiàn)象,尤其是2個(gè)以上不同信道一起發(fā)射時(shí),他們的雜散疊加導(dǎo)致其他信道被污染,請(qǐng)問(wèn)這種情況有解決方法么

2018-06-24 03:14:54

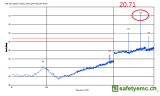

當(dāng)前DTRU產(chǎn)品中使用了DAC3482,故障率達(dá)到12%,從FPGA側(cè)IQ數(shù)據(jù)到達(dá)DAC3482,從3482出口處測(cè)量到的信號(hào),發(fā)現(xiàn)近端存在雜散。具體見(jiàn)下圖所示。

另外做了如下實(shí)驗(yàn):

1、將

2024-12-16 06:23:44

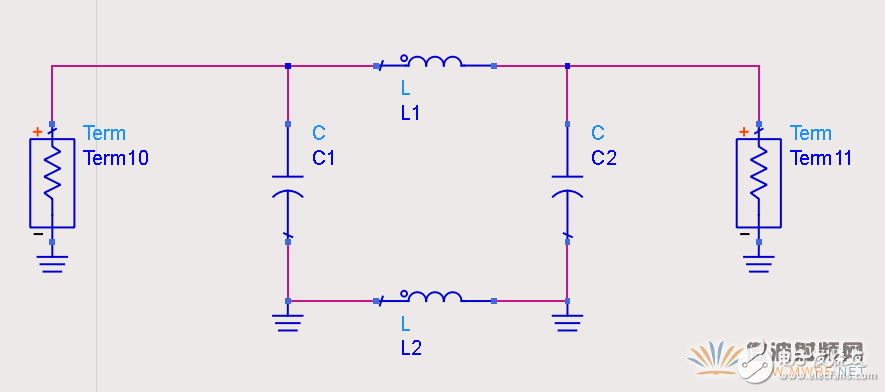

DC/DC開(kāi)關(guān)電源的開(kāi)關(guān)頻率雜散有什么有效的解決方法沒(méi)有?在其后加多級(jí)LDO都不能很好的解決。尋找一種能夠通過(guò)電感或電容的解決方案。開(kāi)關(guān)頻率在幾百KHz左右的。

2024-01-08 07:25:39

本帖最后由 EMChenry 于 2015-8-6 10:17 編輯

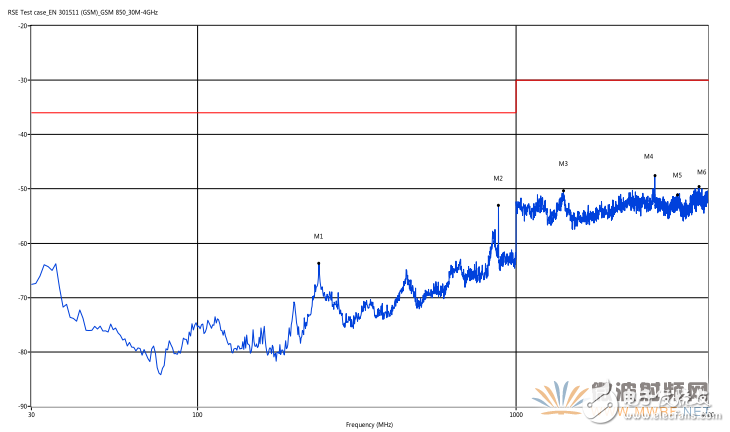

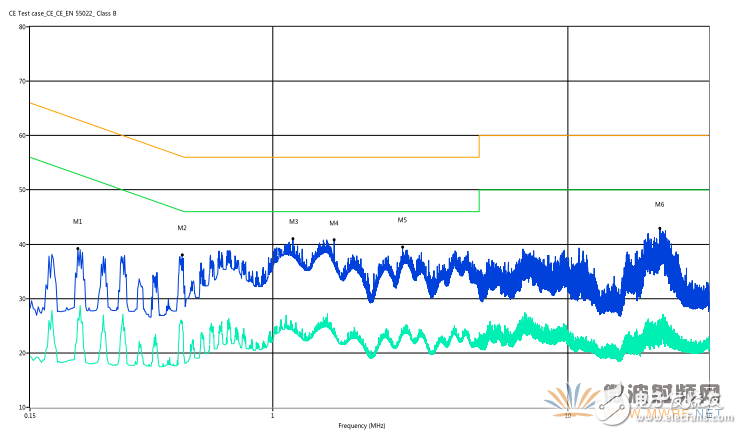

EMC案例之輻射雜散測(cè)試

2015-08-06 10:15:32

在使用HMC704中遇到非整數(shù)邊界雜散問(wèn)題,麻煩各位看看: REFin:100MHz, N=2, 鑒相頻率50MHz輸出分別為10025MHz,10050MHz和10075MHz環(huán)路濾波器帶寬:1

2019-02-21 14:05:56

我的參考頻率為80MHz,鑒相頻率為160MHz,現(xiàn)在雜散為80 的整數(shù)倍,是否為整數(shù)邊界雜散?如何降低整數(shù)邊界雜散?如何計(jì)算哪些點(diǎn)的整數(shù)邊界雜散高?哪些點(diǎn)的整數(shù)邊界雜散低?

2024-11-11 08:02:42

240KHz左右出現(xiàn)較大雜散信號(hào),抑制在50dB左右,嚴(yán)重影響到后面的信號(hào)處理。

問(wèn)題:該雜散可能是在哪個(gè)環(huán)節(jié)產(chǎn)生的,應(yīng)如何有效避免?

2025-02-14 06:49:19

每隔3KHz存在雜散,無(wú)法通過(guò)降低信號(hào)功率,改變時(shí)鐘數(shù)據(jù)相位來(lái)改善

更改參考時(shí)鐘為60MHz,雜散間隔變?yōu)?5K

更改參考時(shí)鐘為20MHz是,雜散消失

請(qǐng)問(wèn)各位大神這個(gè)問(wèn)題應(yīng)該怎么考慮,謝謝

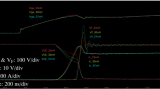

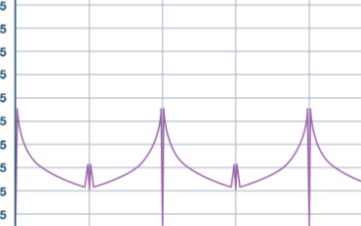

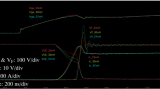

另外當(dāng)去掉DAC輸出輔助之后用示波器測(cè)試波形如下,這種現(xiàn)象是信號(hào)發(fā)生反射了嗎?

2023-12-07 07:09:55

、驗(yàn)證中尋找出合適的、較優(yōu)的、低成本的方案從而縮短開(kāi)發(fā)周期,進(jìn)而搶先獲得消費(fèi)市場(chǎng)認(rèn)可。本案例向我們揭示了一種通過(guò)使用頻譜儀和近場(chǎng)探頭測(cè)試解決方案來(lái)完成無(wú)線(xiàn)智能通訊設(shè)備的輻射雜散調(diào)試的方法。一個(gè)快速精準(zhǔn)

2018-03-27 14:30:31

測(cè)量發(fā)射機(jī)1(或2)的輸出載頻和雜散,從多工器泄漏過(guò)來(lái)的另一臺(tái)發(fā)射機(jī)的信號(hào)。以及發(fā)射機(jī)由此所產(chǎn)生的反向互調(diào)。而端口3對(duì)于系統(tǒng)來(lái)說(shuō)是最為重要的,因?yàn)樗械妮d頻和雜散都從這里開(kāi)始輻射到空中。也就是說(shuō),無(wú)論

2017-11-15 10:35:09

DDS的工作原理是什么?如何抑制DDS輸出信號(hào)中雜散問(wèn)題?

2021-05-26 07:15:37

進(jìn)行預(yù)測(cè)。以下內(nèi)容旨在幫助您確定DDS輸出信號(hào)頻譜中的雜散源。如果通過(guò)改變DDS頻率調(diào)諧字使雜散與DDS/DAC相關(guān),則并不難確定雜散源。這是因?yàn)楦淖冋{(diào)諧字時(shí),上述所有雜散噪聲的頻率偏移均隨基波變化

2023-12-15 07:38:37

雜散測(cè)試的一些資料,期刊論文,有需要的朋友自行下載吧

2018-09-26 10:15:21

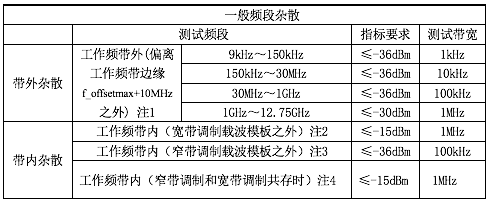

傳導(dǎo)和輻射雜散的FCC限值是什么情況,沒(méi)看懂,求指點(diǎn)。另外,2G和3G的雜散測(cè)試,除了測(cè)試頻率范圍不同外,還有哪些不同,提前謝謝大神!!!!!!!

2013-03-10 21:38:03

小弟正在調(diào)試一款X波段(9.6-10.8GHz)的鎖相環(huán),采用的是內(nèi)部集成VCO的HMC778LP6CE芯片。在調(diào)試中,我發(fā)現(xiàn)在距中心頻率50Hz整數(shù)倍的頻率處有很多雜散,請(qǐng)問(wèn)各位大神這些雜散

2014-07-21 15:47:54

(1)外觀判斷法對(duì)埋地管道來(lái)說(shuō),如果受到直流雜散電流的腐蝕,其外觀是:孔蝕傾向大,創(chuàng)面光滑、邊緣比較整齊,有時(shí)有金屬光澤,腐蝕產(chǎn)物似炭黑色粉末,無(wú)分層現(xiàn)象,有水存在且腐蝕激烈時(shí),可以明顯觀察到電解

2020-12-01 16:22:35

最近使用AD9910時(shí)發(fā)現(xiàn),在960MHz時(shí)鐘下。AD9910輸出300MHz、290MHz和302MHz(均為單音模式),3個(gè)點(diǎn)頻信號(hào)。其中300MHz信號(hào)在100MHz頻寬內(nèi)雜散較好,基本都在

2018-11-29 09:49:07

貴公司的專(zhuān)家們好,我最近在做的項(xiàng)目使用的AD9914芯片,芯片使用3.2GHz參考時(shí)鐘,DDS輸出950MHz信號(hào)時(shí)150MHz,200MHz,處有-65dBc左右的雜散,300MHz處有

2018-11-13 09:35:04

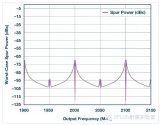

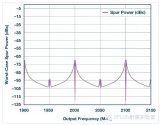

如圖,這是數(shù)據(jù)手冊(cè)上說(shuō)的HMC833參考為50MHz輸出為5900.8Mhz時(shí)的雜散情況。圖上頻偏頻偏為400KHz和800Khz的地方都有雜散。根據(jù)數(shù)據(jù)手冊(cè)上的理論,我能理解800Khz處的雜散是整數(shù)邊界雜散,但我沒(méi)弄懂400Khz處的雜散緣由?哪位明白的,可以解釋一下?謝謝

2018-10-09 17:57:58

HMC833低雜散(1)HMC833是否有低雜散模式。(2)改變seed in fraction是否有作用?

2019-01-15 08:42:05

各位好我在看模擬對(duì)話(huà)的時(shí)候,看到邊帶雜散和開(kāi)關(guān)雜散不太明白,請(qǐng)問(wèn)大家這其中的含義以及它將導(dǎo)致什么后果?謝謝大家了!!!

2019-01-09 09:29:01

我在看ADC供電部分的時(shí)候,看到邊帶雜散和開(kāi)關(guān)雜散這兩詞不知道它的含義。請(qǐng)問(wèn)下大家它們的含義以及它們將會(huì)對(duì)電路造成什么影響?

謝謝大家了!!!!!

2024-12-31 06:32:31

Hello! 請(qǐng)教個(gè)關(guān)于鑒相頻率雜散與環(huán)路濾波器布線(xiàn)的問(wèn)題。例如ADF4360,鑒相頻率的雜散抑制的典型值為-70dBc左右,而實(shí)測(cè)為-60~-65dBc,也能接受,只是感覺(jué)各次倍頻的鑒相頻率太多

2018-11-07 09:03:01

最近調(diào)試遇到個(gè)問(wèn)題,40W功放輸出功率時(shí)在225K左右會(huì)有雜散,抑制在-50dB左右,初步認(rèn)為是由于風(fēng)扇引起的,如過(guò)是風(fēng)扇引起的話(huà),該如何解決

2014-03-28 09:58:41

可能會(huì)出現(xiàn)雜散,這有可能會(huì)使信號(hào)鏈的動(dòng)態(tài)范圍降級(jí)。AD7616 是一款16位數(shù)據(jù)采集系統(tǒng)(DAS),支持在電力線(xiàn)監(jiān)控中對(duì)16個(gè)通道進(jìn)行雙路同步采樣。該器件具有很高的PSRR,將能有效地抑制/衰減開(kāi)關(guān)紋波

2018-10-19 10:38:17

高速無(wú)線(xiàn)調(diào)試器HSWLDBG BURNER 3.3,5

2023-03-28 13:06:20

電容器的寄生作用與雜散電容.pdf

2006-04-04 23:33:03 0

0 分析了地鐵雜散電流的形成及危害, 闡述了地鐵雜散電流監(jiān)測(cè)控制系統(tǒng)的功能,設(shè)計(jì)了基于CAN 總線(xiàn)的地鐵雜散電流的監(jiān)測(cè)系統(tǒng)。論文對(duì)該系統(tǒng)的下位機(jī)軟硬件結(jié)構(gòu),PC-CAN接口卡以及

2010-01-20 15:29:54 21

21 無(wú)線(xiàn)數(shù)據(jù)卡為筆記本用戶(hù)提供了方便快捷的互聯(lián)網(wǎng)服務(wù),但無(wú)線(xiàn)數(shù)據(jù)卡在工作時(shí)如果其輻射雜散指標(biāo)過(guò)高將會(huì)影響到網(wǎng)絡(luò)安全及其他用戶(hù)和設(shè)備。在分析屏蔽原理的基礎(chǔ)上,采用屏

2010-07-06 16:07:37 21

21 直接數(shù)字頻率合成(DDS)技術(shù)推動(dòng)了頻率合成領(lǐng)域的高速發(fā)展,但固有的雜散特性極大的限制了其應(yīng)用發(fā)展。在分析DDS工作原理及雜散噪聲來(lái)源的基礎(chǔ)上,介紹了幾種雜散抑制的方法,

2010-07-31 10:36:19 32

32 雜散特性是制約DDS(直接數(shù)字頻率合成)技術(shù)進(jìn)一步應(yīng)用和發(fā)展的重要因素,其相位舍位、幅度量化和DAC(數(shù)模轉(zhuǎn)換器)的非理想特性等是影響DDS輸出頻譜質(zhì)量的主要雜散源。文中對(duì)

2010-10-20 16:34:46 38

38 雜散特性限制著直接數(shù)字頻率合成(DDS)技術(shù)的應(yīng)用和發(fā)展,其中相位舍位、幅度量化和DAC的非理想特性等是影響DDS輸出頻譜質(zhì)量的主要雜散源。文中主要研究相位舍位對(duì)DDS輸出頻

2010-10-20 16:35:31 28

28 無(wú)雜散動(dòng)態(tài)范圍(SFDR)

SFDR(無(wú)雜散動(dòng)態(tài)范圍)衡量的只是相對(duì)于轉(zhuǎn)換器滿(mǎn)量程范圍(dBFS)或輸入信號(hào)電平(dBc)的最差頻譜偽像。比較ADC時(shí)

2011-01-01 12:14:56 14336

14336 對(duì)無(wú)線(xiàn)電管理工作來(lái)說(shuō),雜散發(fā)射是產(chǎn)生干擾的重要原因,在無(wú)線(xiàn)電發(fā)射設(shè)備檢測(cè)中,雜散發(fā)射是一個(gè)重要的必測(cè)項(xiàng)目。那么,怎樣正確測(cè)量雜散發(fā)射呢?本文參考國(guó)際電聯(lián)的ITU-R SM .3

2011-05-20 15:44:07 71

71 系統(tǒng)地研究了快速跳頻PLL 中雜散來(lái)源,給出了環(huán)路雜散模型,定義了雜散抑制比。定性分析了MF2SK2FH 通信系統(tǒng)檢測(cè)誤碼率Pe 與雜散抑制比之間的關(guān)系,并通過(guò)計(jì)算機(jī)輔助分析,定量計(jì)算出誤

2011-09-01 16:30:45 46

46 雜散抑制是PLL 頻率合成器的幾個(gè)關(guān)鍵指標(biāo)之一。在實(shí)際設(shè)計(jì)中,雜散的輸出種類(lèi)比較多,產(chǎn)生的原因也各不一樣,但是它們中的大多數(shù)并不常見(jiàn)。首先從雜散的基本概念出發(fā),詳細(xì)地介紹了

2011-09-01 16:34:56 69

69 直接數(shù)據(jù)頻率合成器(DDS)因能產(chǎn)生頻率捷變且殘留相位噪聲性能卓越而著稱(chēng)。另外,多數(shù)用戶(hù)都很清楚DDS輸出頻譜中存在的雜散噪聲,比如相位截?cái)?b class="flag-6" style="color: red">雜散以及與相位-幅度轉(zhuǎn)換過(guò)程相關(guān)的

2012-02-02 10:41:21 44

44 LMX2531 系列產(chǎn)品被廣泛應(yīng)用于無(wú)線(xiàn)通訊基站系統(tǒng),相比較整數(shù)分頻,采用小數(shù)分頻可以獲得更好的相位噪聲性能,但是小數(shù)分頻會(huì)導(dǎo)致雜散問(wèn)題,特別是整數(shù)邊界雜散尤為突出。本文介紹一種在盡可能保證相位噪聲性能的基礎(chǔ)上,改善整數(shù)邊界雜散達(dá)10dB。

2013-04-27 15:51:04 3492

3492 新大管道雜散電流干擾影響研究新大管道雜散電流干擾影響研究

2015-11-16 14:43:22 0

0 電容器的寄生作用與雜散電容,還不錯(cuò)哦

2016-06-15 15:53:57 6

6 電容器的寄生作用與雜散電容

2017-01-28 21:32:49 5

5 針對(duì)大功率變流器功率開(kāi)關(guān)關(guān)斷時(shí),由疊層母排雜散電感引起的瞬時(shí)高壓?jiǎn)栴},對(duì)疊層母排的雜散電感與其結(jié)構(gòu)之間的關(guān)系進(jìn)行了研究。利用Q3D軟件對(duì)不同尺寸、開(kāi)孔、開(kāi)槽等母排常見(jiàn)的結(jié)構(gòu)進(jìn)行了建模與雜散電感提取

2018-03-07 16:25:15 4

4 通過(guò)一個(gè)案例,使用是德科技測(cè)試測(cè)量解決方案,完成無(wú)線(xiàn)智能終端產(chǎn)品的輻射雜散的最終優(yōu)化。

2018-07-13 16:37:20 8878

8878

5G基站雜散OTA測(cè)試要掃幾萬(wàn)個(gè)TRP?

2020-07-23 10:26:00 4

4 隨著5G時(shí)代的推進(jìn),智能終端產(chǎn)品作為寬帶射頻應(yīng)用最大的消費(fèi)市場(chǎng)面臨著一系列開(kāi)發(fā)與驗(yàn)證的問(wèn)題。其中,越來(lái)越小的設(shè)計(jì)空間與電磁輻射雜散性能之間的矛盾,將是商業(yè)研究人員開(kāi)發(fā)和驗(yàn)證中面臨的巨大挑戰(zhàn)。若要

2020-07-09 18:56:00 2

2 鎖相環(huán) (PLL) 和壓控振蕩器 (VCO) 輸出特定頻率的RF信號(hào),理想情況下此信號(hào)應(yīng)當(dāng)是輸出中的唯一信號(hào)。但事實(shí)上,輸出中存在干擾雜散信號(hào)和相位噪聲。本文討論最麻煩的雜散信號(hào)之一——整數(shù)邊界雜散——的仿真與消除。

2020-09-09 10:09:56 5000

5000

雜散發(fā)射包括諧波發(fā)射、寄生發(fā)射、互調(diào)發(fā)射及變頻產(chǎn)物,但帶外發(fā)射除外。輻射雜散主要是由于機(jī)箱(或機(jī)柜)以及設(shè)備的結(jié)構(gòu)而引起的任何雜散發(fā)射 通信產(chǎn)品的發(fā)射機(jī)輸出信號(hào)通常為大功率信號(hào),在產(chǎn)生大功率信號(hào)的過(guò)程中可能會(huì)在發(fā)射信號(hào)的頻帶之外產(chǎn)生較高的雜散。

2021-03-21 11:53:46 3709

3709

換流回路中的雜散電感會(huì)引起波形震蕩,EMI或者電壓過(guò)沖等問(wèn)題。因此在電路設(shè)計(jì)的時(shí)候需要特別留意。本文給出了電路雜散電感的測(cè)量方法以及模塊數(shù)據(jù)手冊(cè)中雜散電感的定義方法。 圖1為半橋電路的原理電路以及

2021-10-13 15:36:13 5840

5840

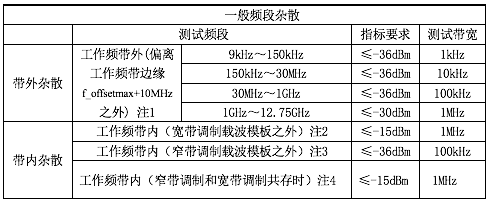

對(duì)無(wú)線(xiàn)電管理工作來(lái)說(shuō),雜散發(fā)射是產(chǎn)生干擾的重要原因 . 在無(wú)線(xiàn)電發(fā)射設(shè)備檢測(cè)過(guò)程中,雜散測(cè)試是一個(gè)重要的必測(cè)項(xiàng)目。雜散是指在工作帶寬外某個(gè)頻點(diǎn)或某些頻率上的發(fā)射,其發(fā)射電平可降低但不影響相應(yīng)的信息傳遞。包括:諧波發(fā)射、寄生發(fā)射、互調(diào)產(chǎn)物、以及變頻產(chǎn)物,但帶外發(fā)射除外。

2022-09-16 15:49:55 5437

5437 換流回路中的雜散電感會(huì)引起波形震蕩,EMI或者電壓過(guò)沖等問(wèn)題。

2023-02-07 16:43:47 5657

5657

某藍(lán)牙無(wú)線(xiàn)耳機(jī)與藍(lán)牙適配器做FCC ID認(rèn)證,輻射雜散不合格,其2次諧波,3次諧波,4次諧波都不合格。不滿(mǎn)足FCC Part 15.247的輻射雜散限值要求,F(xiàn)CC限值詳細(xì)如下:

2023-04-18 10:43:55 2106

2106

雜散干擾主要是由于接收機(jī)的靈敏度不高造成的。 發(fā)射機(jī)輸出信號(hào)通常為大功率信號(hào),在產(chǎn)生大功率信號(hào)的過(guò)程中會(huì)在發(fā)射信號(hào)的頻帶之外產(chǎn)生較高的雜散。 如果雜散落入某個(gè)系統(tǒng)接收頻段內(nèi)的幅度較高,則會(huì)導(dǎo)致接收

2023-05-08 16:18:38 3279

3279

-本文要點(diǎn)理解電路中的雜散電容。了解雜散電容如何影響電子電路。探索減少電路中雜散電容的策略。雜散電容就像被遺棄的寵物流浪在街道和巷子里一樣,它們潛伏在電路中。本文將了解電子電路中的雜散電容是如何產(chǎn)生

2023-01-05 15:45:29 4612

4612

一站式PCBA智造廠家今天為大家講講如何減少PCB雜散電容的影響?減少PCB雜散電容的PCB設(shè)計(jì)方法。當(dāng)提到PCBA上的電子電路時(shí),經(jīng)常使用的術(shù)語(yǔ)是雜散電容。PCB上的導(dǎo)體、無(wú)源器件的預(yù)制電路板

2023-08-24 08:56:32 1437

1437 雜散就是在頻譜上產(chǎn)生一些我們不想要的信號(hào)。

2023-10-10 14:13:31 2351

2351

什么是無(wú)雜散動(dòng)態(tài)范圍 (SFDR)?為什么SFDR很重要? 無(wú)雜散動(dòng)態(tài)范圍(SFDR)是指模擬信號(hào)中最大的無(wú)雜散動(dòng)態(tài)范圍。它是在硬件設(shè)備中測(cè)量的。它是指能夠測(cè)量的模擬信號(hào)的最大幅度范圍,其中沒(méi)有雜散

2023-10-31 09:34:29 10717

10717 電容器的寄生作用與雜散電容

2022-12-30 09:21:51 4

4 電容器的寄生作用與雜散電容

2023-03-01 15:37:55 1

1 變頻器控制引起的電機(jī)軸電壓雜散? 變頻器(簡(jiǎn)稱(chēng)VFD)是通過(guò)調(diào)整輸入電源頻率和電壓來(lái)控制電機(jī)轉(zhuǎn)速的裝置。它在工業(yè)控制應(yīng)用中得到廣泛應(yīng)用,可以提高能效和精度,并減少能源消耗。然而,變頻器控制引起的電機(jī)

2024-02-01 14:08:21 1619

1619 電子發(fā)燒友網(wǎng)站提供《時(shí)鐘雜散對(duì)高速DAC性能的影響.pdf》資料免費(fèi)下載

2024-10-17 11:10:28 0

0 說(shuō)到射頻的難點(diǎn)不得不提雜散,雜散也是射頻被稱(chēng)為“玄學(xué)”的來(lái)源。雜散也是學(xué)習(xí)射頻必經(jīng)的一個(gè)難點(diǎn)。本篇文章就來(lái)講一下雜散。

2024-11-05 09:59:34 6935

6935

什么是晶振的雜散電容?晶振的雜散電容,也叫做寄生電容,是指電路中非人為設(shè)計(jì)、由物理結(jié)構(gòu)自然產(chǎn)生的、有害的隱藏電容。它為什么重要?(影響)雜散電容之所以關(guān)鍵,是因?yàn)樗鼤?huì)直接影響晶振的振蕩頻率精度。核心

2025-11-13 18:13:41 225

225

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論