完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > pll

文章:581個(gè) 瀏覽:138182次 帖子:522個(gè)

分析和管理電源噪聲和時(shí)鐘抖動(dòng)對(duì)高速DAC相位噪聲的影響

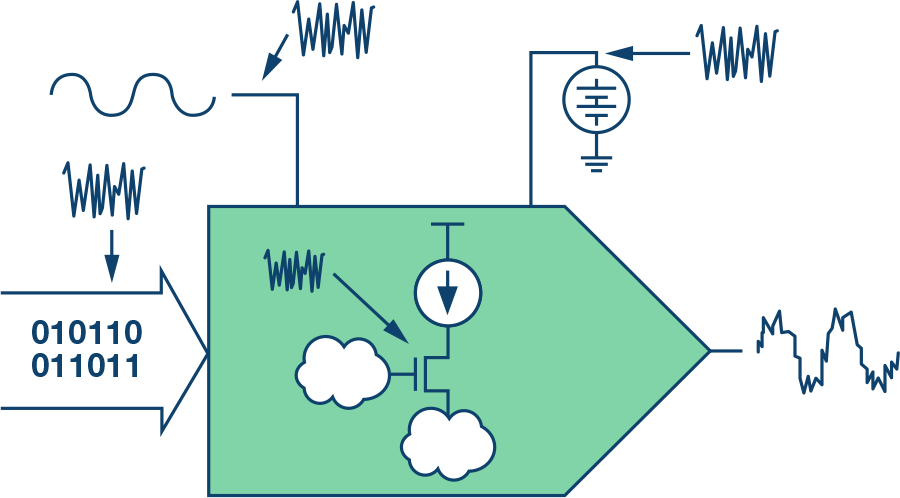

從一張白紙開(kāi)始,DAC首先被視為一個(gè)塊盒。噪聲可以在內(nèi)部產(chǎn)生,因?yàn)槿魏螌?shí)際組件都會(huì)產(chǎn)生一些噪聲,或者噪聲可能來(lái)自外部來(lái)源。外部電源的入口可以通過(guò)任何DA...

ADF4356/ADF5356器件上的相位對(duì)齊和控制

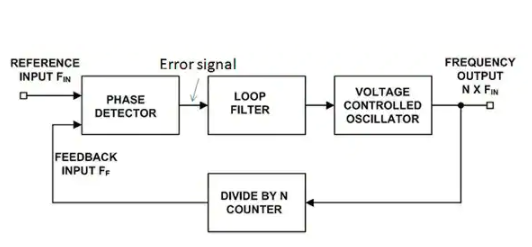

顧名思義,鎖相環(huán)(PLL)使用鑒相器將反饋信號(hào)與參考信號(hào)進(jìn)行比較,將兩個(gè)信號(hào)的相位鎖定在一起。雖然該特性仍有許多應(yīng)用,但目前PLL最常用于頻率合成,通常...

2023-01-04 標(biāo)簽:放大器轉(zhuǎn)換器變頻器 3.2k 0

該問(wèn)題由某客戶(hù)提出,發(fā)生在 STM32F103VDT6 器件上。據(jù)其工程師講述:在其產(chǎn)品的設(shè)計(jì)中,STM32 的 HSE 外接 8MHz 的晶體產(chǎn)生振蕩...

FPGA知識(shí)匯集-FPGA系統(tǒng)時(shí)序理論

上式中:Tco_clkb是系統(tǒng)時(shí)鐘信號(hào)CLKB在時(shí)鐘驅(qū)動(dòng)器的內(nèi)部延遲;Tflt_ clkb 是CLKB從時(shí)鐘驅(qū)動(dòng)器輸出后到達(dá)發(fā)送端(CPU)觸發(fā)器的飛行...

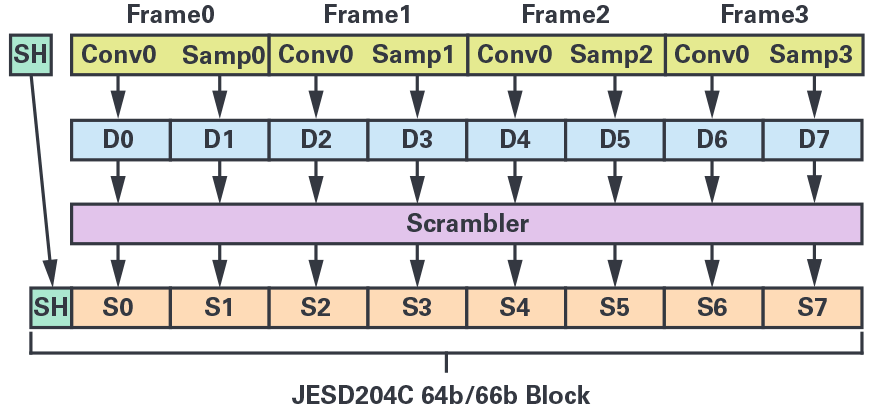

對(duì)于 64b/66b 鏈路層,66 位數(shù)據(jù)塊是兩個(gè)同步標(biāo)頭位,后跟八個(gè)八位字節(jié)的示例數(shù)據(jù),部分基于 IEEE 802.3 條款 49 中定義的塊格式。與...

2022-12-21 標(biāo)簽:轉(zhuǎn)換器pll 2.2k 0

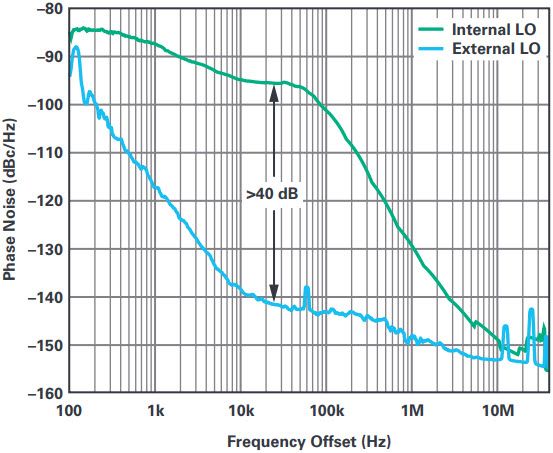

ADI公司ADRV9009收發(fā)器使用外部本振(LO)時(shí)的測(cè)量表明,使用低噪聲LO時(shí),相位噪聲可以顯著改善。收發(fā)器架構(gòu)是從相位噪聲貢獻(xiàn)的角度提出的。通過(guò)一...

PLL/VCO技術(shù)如何提高性能、減小尺寸并簡(jiǎn)化設(shè)計(jì)周期

多年來(lái),微波頻率生成給工程師帶來(lái)了重大挑戰(zhàn),需要深入了解模擬、數(shù)字和射頻 (RF) 以及微波電子學(xué),特別是鎖相環(huán) (PLL) 和壓控振蕩器 (VCO) ...

驅(qū)動(dòng)高壓鎖相環(huán)頻率合成器電路的VCO

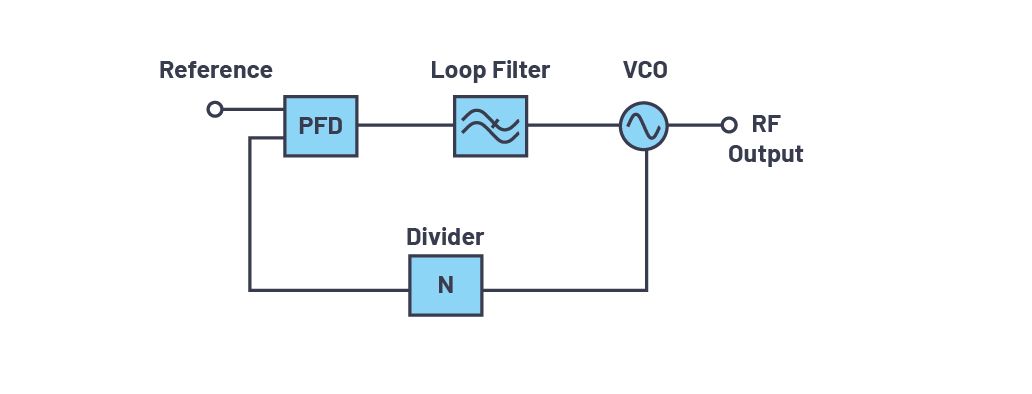

鎖相環(huán)(PLL)電路是一種反饋系統(tǒng),它結(jié)合了壓控振蕩器(VCO)和鑒相器,使振蕩器信號(hào)以正確的頻率和相位跟蹤施加的頻率或相位調(diào)制信號(hào)。當(dāng)需要從固定的低頻...

為什么完全集成的轉(zhuǎn)換環(huán)路器件可實(shí)現(xiàn)最佳的相位噪聲性能

該設(shè)備配備了自動(dòng)校準(zhǔn)引擎,可以識(shí)別 給定目標(biāo)頻率的最佳VCO頻段。在校準(zhǔn)模式下, 設(shè)備可以在實(shí)際溫度下搜索正確的頻段,并且 工藝條件,使調(diào)頻過(guò)程無(wú)縫銜接。

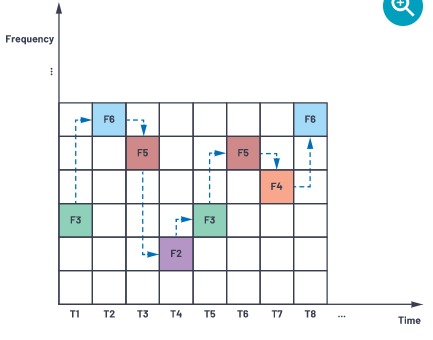

下一代軟件定義無(wú)線電收發(fā)器在跳頻方面取得巨大進(jìn)步

本文深入討論了跳頻(FH)的高級(jí)概念、通過(guò)ADRV9002 SDR收發(fā)器的靈活鎖相環(huán)(PLL)架構(gòu)實(shí)現(xiàn)的跳頻設(shè)計(jì)原理及其四個(gè)主要跳頻特性。這些功能使用戶(hù)...

集成式相位檢波器(PD)和Σ-Δ型調(diào)制器能以高達(dá)100 MHz的頻率工作,實(shí)現(xiàn)更寬的環(huán)路帶寬和出色的頻譜性能。

鎖相環(huán)(PLL)電路存在于各種高頻應(yīng)用中,從簡(jiǎn)單的時(shí)鐘凈化電路到用于高性能無(wú)線電通信鏈路的本振(LO),以及矢量網(wǎng)絡(luò)分析儀(VNA)中的超快開(kāi)關(guān)頻率合成器。

一種FLL輔助PLL的GNSS接收機(jī)矢量跟蹤環(huán)路

摘 要:全球?qū)Ш叫l(wèi)星系統(tǒng)(GNSS)接收機(jī)的設(shè)計(jì)主要包括捕獲、跟蹤、解算三個(gè)環(huán)節(jié),其中,跟蹤環(huán)節(jié)中載波頻率和碼頻率的穩(wěn)定性直接影響著導(dǎo)航定位性能。為改...

時(shí)鐘信號(hào)在很大程度上決定了整個(gè)設(shè)計(jì)的性能和可靠性,盡量避免使用FPGA內(nèi)部邏輯產(chǎn)生的時(shí)鐘,因?yàn)樗苋菀讓?dǎo)致功能或時(shí)序出現(xiàn)問(wèn)題。內(nèi)部邏輯(組合邏輯)產(chǎn)生的...

2022-10-26 標(biāo)簽:fpgapll時(shí)鐘信號(hào) 2k 0

如果用一個(gè)自由振蕩的振蕩器,給MCU提供時(shí)鐘。會(huì)咋樣呢?

時(shí)鐘是芯片正確高效運(yùn)行的基礎(chǔ),正確的時(shí)鐘配置是芯片能正確運(yùn)行的必要條件,其重要性不言而喻。AT32各系列產(chǎn)品的時(shí)鐘配置部分可能存在細(xì)微的差異和需要注意的...

什么是時(shí)鐘緩沖器(Buffer)?時(shí)鐘緩沖器(Buffer)參數(shù)解析

什么是時(shí)鐘緩沖器(Buffer)?時(shí)鐘緩沖器(Buffer)參數(shù)解析 什么是時(shí)鐘緩沖器(Buffer)?我們先把這個(gè)概念搞清楚。 時(shí)鐘緩沖器就是常說(shuō)的C...

2022-10-18 標(biāo)簽:時(shí)鐘緩沖器pll時(shí)鐘 3.1萬(wàn) 0

要滿(mǎn)足苛刻的頻率合成器要求,通常需要做到一定程度的設(shè)計(jì)靈活性。基本的鎖相環(huán)(PLL)頻率合成器能以低成本、高空間效率、低功耗封裝提供合理的頻譜純度和頻率...

jitter的關(guān)鍵術(shù)語(yǔ)和參數(shù)

時(shí)鐘電路是芯片中最基礎(chǔ)的電路,時(shí)鐘電路性能的好壞關(guān)乎SoC中所有電路能否達(dá)到預(yù)期目標(biāo),例如:計(jì)算核(CPU/GPU/NPU)的主頻,DDR的帶寬,高速接...

詳解鎖相環(huán) (PLL)電路、信號(hào)、模塊組成

鎖相環(huán) (PLL) 是電子系統(tǒng)中最通用、最靈活和最有價(jià)值的電路配置之一,因此在許多應(yīng)用中都有使用。它用于時(shí)鐘重定時(shí)和恢復(fù),作為頻率合成器和可調(diào)諧振蕩器,...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語(yǔ)言教程專(zhuān)題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無(wú)刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺(jué) | 無(wú)人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹(shù)莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |