完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > orcad

OrCAD 是一套在個(gè)人電腦的電子設(shè)計(jì)自動(dòng)化套裝軟件,專門用來讓電子工程師設(shè)計(jì)電路圖及相關(guān)圖表,設(shè)計(jì)印刷電路板所用的印刷圖,及電路的模擬之用。

文章:149個(gè) 瀏覽:120380次 帖子:337個(gè)

【工具升級(jí)】 I OrCAD X 全版本新功能匯總,高效搞定電路協(xié)同設(shè)計(jì)

在電子電路設(shè)計(jì)領(lǐng)域,一款功能強(qiáng)大、適配協(xié)同工作的工具,能大幅提升設(shè)計(jì)效率與精準(zhǔn)度。OrCADX系列版本更新,圍繞協(xié)作、易用性、仿真分析三大核心,為個(gè)人及...

2026-01-16 標(biāo)簽:orcad協(xié)同設(shè)計(jì) 1.2k 0

網(wǎng)絡(luò)研討會(huì) I OrCAD X 24.1中的新功能

時(shí)間日期:2024年10月16日,星期三時(shí)間:北京時(shí)間-下午15:00課程概述無論您是經(jīng)驗(yàn)豐富的用戶還是新手,都可以加入這次由Cadence主辦的網(wǎng)絡(luò)研...

2024-10-12 標(biāo)簽:數(shù)據(jù)管理CADorcad 2.2k 0

ORCAD-Capture CIS: 如何調(diào)整原理圖頁面打印順序

ORCAD Capture原理圖頁面打印順序調(diào)整

2024-09-23 標(biāo)簽:orcad 3.7k 0

核心優(yōu)勢?緊密集成的易用平臺(tái)交互式布線:精簡的PCB編輯器,提供直觀的菜單和基于規(guī)則的布線操作,可在設(shè)計(jì)過程中使用hug、shove等布線方法,輕松調(diào)整...

2024-08-30 標(biāo)簽:pcb信號(hào)完整性orcad 949 0

1關(guān)鍵要點(diǎn)OrCADX是OrCAD平臺(tái)的下一代,為具有OrCAD經(jīng)驗(yàn)的設(shè)計(jì)師和新設(shè)計(jì)師提供了許多功能,以改善布局工作流程和可制造性。OrCADX具有更直...

2024-06-08 標(biāo)簽:PCB設(shè)計(jì)orcad信號(hào)仿真 4.4k 0

orcad在移動(dòng)器件的時(shí)候怎么讓連線不跟著一起動(dòng)呢?

鼠標(biāo)左鍵選中元器件,按住鼠標(biāo)左鍵不松,就可以對元器件進(jìn)行任意位置的拖動(dòng),若此元器件已經(jīng)與其它電路相連,這些連線會(huì)跟著一起移動(dòng);

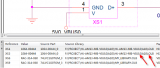

怎么在orcad中點(diǎn)亮整個(gè)網(wǎng)絡(luò)

答:在原理圖進(jìn)行檢查的時(shí)候,為了核查網(wǎng)絡(luò),有時(shí)候需要將一個(gè)網(wǎng)絡(luò)在整個(gè)原理圖中點(diǎn)亮,如圖Allegro軟件設(shè)計(jì)中的高亮命令一樣,操作方式如下示:

2022-08-26 標(biāo)簽:鼠標(biāo)網(wǎng)絡(luò)orcad 3.1k 0

頁面刪除:選中要?jiǎng)h除的原理圖,點(diǎn)擊右鍵選擇Delete或者是Cut即可對選中的原理圖進(jìn)行刪除,彈出的窗口是提示此操作是不可逆的,選擇確定按鈕,完成對原理...

答:我們在進(jìn)行原理圖設(shè)計(jì)或者是進(jìn)行PCB設(shè)計(jì),都會(huì)遇到這樣的問題,需要降低設(shè)計(jì)文件的版本,我們這里講解下,Orcad軟件設(shè)計(jì)的原理圖如何去降低原理圖的版...

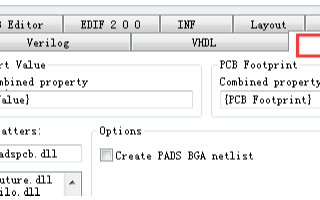

OrCAD與PADS聯(lián)合設(shè)計(jì)電路及PCB的方法

我們在進(jìn)行復(fù)雜的電路設(shè)計(jì)的時(shí)候,一般都是分工合作進(jìn)行,比如有人設(shè)計(jì)原理圖,有人負(fù)責(zé)PCB layout。OrCAD因?yàn)樗妮敵鼍W(wǎng)表種類相當(dāng)豐富,操作方便...

忽略原理圖規(guī)則設(shè)置PCB網(wǎng)表的操作步驟

Orcad如何輸出不含有原理圖規(guī)則的PCB網(wǎng)表呢?

如何對Orcad輸出或者打印PDF的參數(shù)進(jìn)行篩選?

如何對Orcad輸出或者打印PDF的參數(shù)進(jìn)行篩選?

使用Orcad軟件輸出Allegro第一方網(wǎng)表出現(xiàn)錯(cuò)誤怎么處理

Orcad輸出網(wǎng)表出現(xiàn)“Illegal-- character”的錯(cuò)誤,怎么處理?

Orcad怎么產(chǎn)生Cadence Allegro的第三方網(wǎng)表

Orcad怎么產(chǎn)生Cadence Allegro的第三方網(wǎng)表? 答:orcad產(chǎn)生Cadence Allegro的網(wǎng)表的操作步驟如下; 第一步,選擇原理...

如何處理orcad與Cadence Allegro的交互式操作

orcad與Cadence Allegro的交互式操作應(yīng)該怎么處理? 答:orcad與Cadence Allegro的交互式操作需要滿足以下兩個(gè)要求才可...

orcad產(chǎn)生Cadence Allegro的網(wǎng)表操作步驟

orcad怎么產(chǎn)生Cadence Allegro的第一方網(wǎng)表? 答:orcad產(chǎn)生Cadence Allegro的網(wǎng)表的操作步驟如下; 第一步,選擇原理...

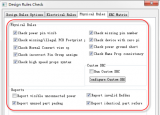

orcad的物理規(guī)則檢查的每一個(gè)的含義是什么? 答:orcad進(jìn)行物理DRC檢測時(shí),如圖3-65所示,需要對檢查的每一項(xiàng)參數(shù)進(jìn)行設(shè)置,每個(gè)參數(shù)的含義如下...

orcad原理圖文件怎么進(jìn)行DRC的檢測? 答:第一步,選擇原理圖的根目錄,然后執(zhí)行菜單Tools-Design Rules Check,進(jìn)行設(shè)計(jì)規(guī)則的...

orcad的電氣規(guī)則檢查的每一個(gè)的含義是什么

orcad的電氣規(guī)則檢查的每一個(gè)的含義是什么? 答:orcad進(jìn)行電氣DRC檢測時(shí),如圖3-64所示,需要對檢查的每一項(xiàng)參數(shù)進(jìn)行設(shè)置,每個(gè)參數(shù)的含義如下...

orcad的DRC檢測參數(shù)設(shè)置的含義是什么

orcad的DRC檢測參數(shù)設(shè)置的含義是什么? 答:orcad進(jìn)行DRC檢測時(shí),如圖3-63所示,需要對參數(shù)進(jìn)行設(shè)置,每個(gè)參數(shù)的含義如下所示: 圖3-63...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |