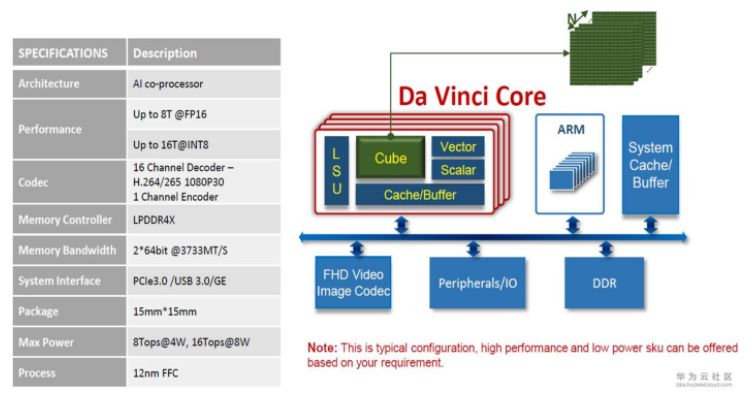

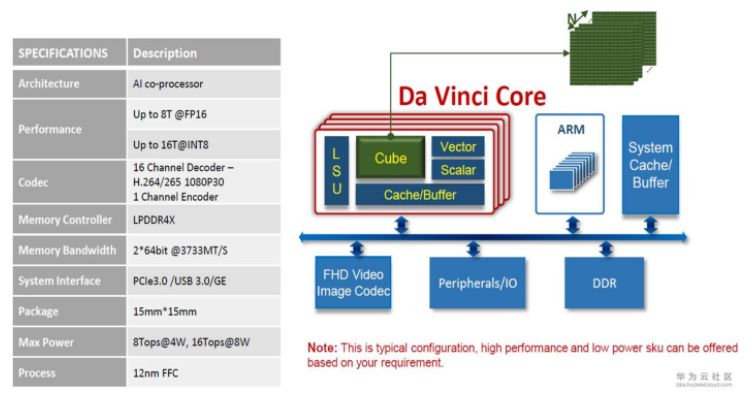

Ascend310 AI處理器邏輯架構昇騰AI處理器的主要架構組成:芯片系統控制CPU(Control CPU)AI計算引擎(包括AI Core和AI CPU)多層級的片上系統緩存(Cache)或

2023-06-05 14:09:27 17739

17739

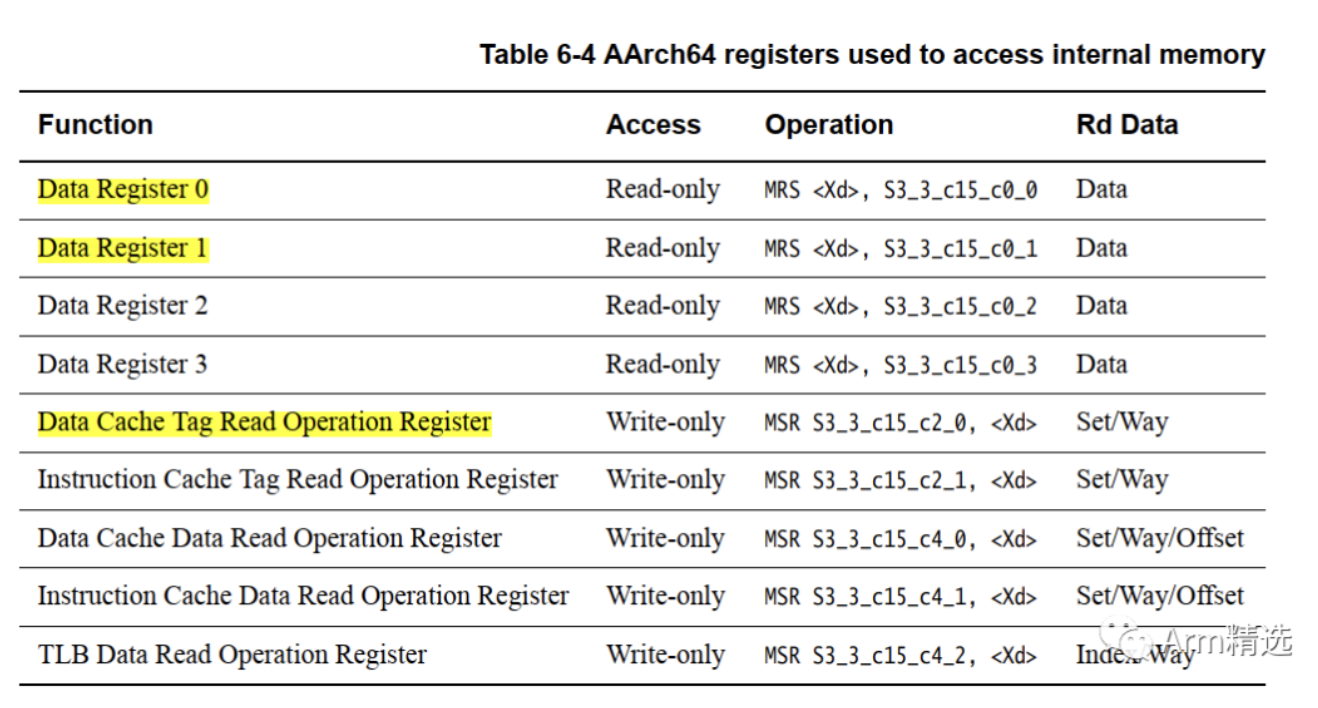

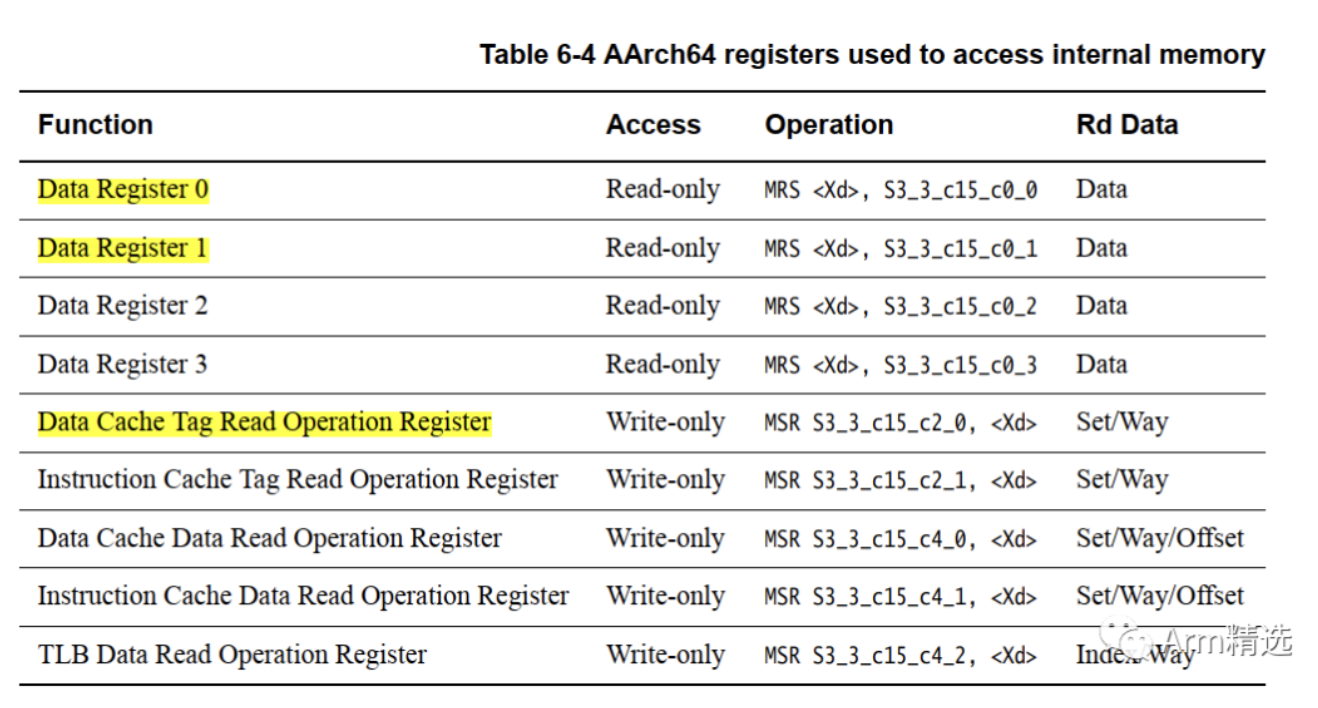

本文以Cortex-A53處理器為例,通過訪問 處理器中的 **內部存儲單元** (tag RAM和dirty RAM),來讀取cache line 中的MOESI信息。

2023-09-08 14:35:44 1679

1679

隨著 RISC -V處理器在 FPGA 領域的廣泛應用,易靈思 FPGA 的 Sapphire RISC-V 內核憑借軟硬核的靈活支持,為開發者提供多樣選擇。本文深入探討 Sapphire SoC 中 RISC - V 平臺級中斷控制器(PLIC),解析其架構與操作機制,助力你深入了解與應用。

2025-11-08 09:35:48 7528

7528

人工智能大熱,國內外芯片開發商競相發布自己的AI處理器智能芯片。小編比較了目前主流“AI處理器”的技術和市場

2018-01-19 08:59:22 19357

19357 電子發燒友網綜合報道:端側 AI 音頻處理器是專為智能物聯網(AIoT)端側設備設計,集成了人工智能(AI)加速器的系統級音頻處理器。這類處理器旨在打造低功耗、高算力的芯片平臺,以滿足智能物聯網設備

2025-02-16 00:13:00 3289

3289 電子發燒友網(文 / 李彎彎)光子 AI 處理器,作為一種借助光子執行信息處理與人工智能(AI)計算的新型硬件設備,正逐漸嶄露頭角。與傳統基于晶體管的電子 AI 處理器(如 GPU、TPU)截然不同

2025-04-19 00:40:00 3876

3876 作為通用處理器,CPU (Central Processing Unit) 是計算機中不可或缺的計算核心,結合指令集,完成日常工作中多種多樣的計算和處理任務。然而近年來,CPU在計算平臺領域一統天下的步伐走的并不順利,可歸因于兩個方面,即自身約束和需求轉移。

2019-08-09 07:42:46

Cache為什么還要分I-Cache,D-Cache,L2 Cache,作用是什么?

2023-10-25 06:38:45

在Multisim的仿真分析中后處理器(postprocesser)應該如何使用?如何在以一個α量為參數運行參數掃描獲得兩個相關量(設為a,b)的圖線后,獲得a,b之間的圖線?要獲得上面的結果是否要使用后處理器?

2013-06-22 16:43:41

處理器中斷處理的過程是怎樣的?處理器在讀內存的過程中,CPU核、cache、MMU如何協同工作?

2021-10-18 08:57:48

深入解析傳感器網絡中實時通信的研究

2021-05-26 06:00:09

ARM Cortex-M4處理器在C源文件里面調用匯編函數,參數傳遞機制是怎樣的?比如C源文件里面調用匯編語言實現的函數uint8_t Code(uint8_t a,uint32_t b

2022-08-22 15:23:43

。build_mem_type_table()屬于early_mm_init()自己的一部分,因此,從early_mm_init()入手,逐步解析CACHE的寫機制。early_mm_init(mdesc)early_mm_init() 可以執行了當前Mkernel是否能夠執行。原作者:linux-soc

2022-06-30 16:05:05

ARM處理器中的邏輯cache和物理cache是什么?有沒有哪位大神可以幫忙解決一下這個問題

2022-11-03 15:25:40

早期的ARM處理器使用虛擬地址(virtual addresses)來提供cache index和cache tag。VIVT優點這樣做的好處是處理器內核可以使用虛擬地址進行cache look

2022-06-20 15:22:23

ARM處理器設計的機制是如何使得它的運行速度遠快于51單片機的運行速度的?求解答

2022-08-04 14:22:11

的cache line為32 bytes。在cache方面,在一個cluster里面的至多4個A9處理器的L1 data cache可以通過SCU的MESI協議做一致性維護。大多數的A9多核系統會外接一

2022-12-14 16:17:15

本帖最后由 eehome 于 2013-1-5 10:03 編輯

NAND閃存深入解析

2012-08-09 14:20:47

RK3188處理器有哪些特性呢?RK3168處理器具備哪幾大特點呢?RK3126處理器是什么?有何作用?

2022-02-18 07:21:37

微處理器ELANSC520-100AI是如何工作的?這個處理器通電后是怎么工作的,外部給他提供一個FLASH里面是BOOT程序。起上電復位和開機自檢作用。

2010-08-28 17:02:50

處理器涉及到的主存塊內容。在需要讀取數據是,處理器可能就會從Cache中讀取需要的數據,而不是從主存中獲取數據,這樣就提高了系統的運行效率。二、ARM處理器的CacheARM處理器支持Cache機制,并將

2016-10-13 18:02:50

的效果。

7.總結

本文詳細介紹了中斷機制在計算機系統中的作用,以及如何在e203處理器中利用外部中斷來處理用戶輸入輸出。除此之外,中斷也能對設備響應和其他緊急任務進行處理。

2025-10-21 12:47:00

主流四核移動處理器解析

2012-08-20 13:01:36

:1、如果cacheline 在 L1 cache中找到,則從 L1 cache中讀取數據并返回給處理器。2、如果該cacheline 未在 L1 cache中找到,但存在于 L2 cache中,則從

2022-07-20 14:46:15

低功耗DRP-AI動態可配置處理器有哪些關鍵特性呢?

2021-11-08 09:16:49

多任務在多核上運行。這樣的機制使一份RTOS在系統存儲器中拷貝了多份,浪費了一定的存儲空間;同時由于對應用程序不透明,需要設計多任務在多核處理器上的調度和運行,增加了應用程序的復雜度,同時需要更多

2019-06-29 08:30:00

你好我想提出我的兩個問題希望我們可以討論它嗎?1.雙處理器設計與雙核設計之間的差異是什么?2. Xilinx雙微填充設計中如何緩存高速緩存一致性。在xilinx WP 262中,聲明

2019-03-04 13:41:13

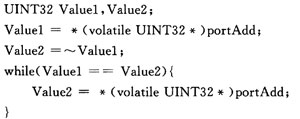

看出,信箱寄存器機制需要處理器輪詢,所以通信效率不高,在休眠/喚醒這類不頻繁的操作中還可以,如果是比較頻繁的核間通信就不適用了,要采取中斷機制。以上是多核處理器啟動的基本原理,至于具體實現,不同的廠商有

2022-06-07 16:41:29

機)節點集成到同一芯片內,各個處理器并行執行不同的線程或進程。在基于SMP結構的單芯片多處理機中,處理器之間通過片外Cache或者是片外的共享存儲器來進行通信。而基于DSM結構的單芯片多處理器中,處理器間

2011-04-13 09:48:17

處理器涉及到的主存塊內容。在需要讀取數據是,處理器可能就會從Cache中讀取需要的數據,而不是從主存中獲取數據,這樣就提高了系統的運行效率。更多嵌入式學習 2848988085二、ARM處理器

2016-08-31 16:30:26

。5.協處理器寄存器傳送除了以上情況,在ARM和協處理器寄存器之間傳送數據有時是有用的。再以使用浮點協處理器為例,FIX指令從協處理器寄存器取得浮點數據,將它轉換為整數,并將整數傳送到ARM寄存器中

2022-04-24 09:36:47

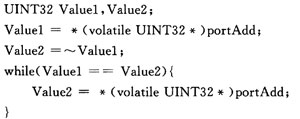

直接運行ELF文件,情況也是一樣,拷貝完代碼后一定要刷新Cache,以免不測。 還有,對硬件的操作要小心。很多寄存器值都是被硬件改變的,讀寫時,要保證確實訪問到它的地址。首先,在C語言代碼中聲明

2017-08-19 22:42:08

隨著嵌入式計算機應用的發展,嵌入式CPU的主頻不斷提高,這就造成了慢速系統存儲器不能匹配高速CPU處理能力的情況。為了解決這個問題,許多高性能的嵌入式處理器內部集成了高速緩存Cache。其中,三星公司的S3C44B0X內部就集成了8KB空間統一的指令和數據Cache。

2019-09-05 07:00:20

本文設計了一種在多處理器系統中的Nios II軟核處理器的啟動方案,這個方案在外部處理器向Nios II的程序存儲器和數據存儲器加載數據時,可以控制Nios II處理器的啟動。

2021-04-27 06:52:42

時決定替換掉哪一個way的cacheline;寫策略cache收到處理器內核的寫請求時,相應的cache行為,例如是否先寫到cache中,等到實在有必要時再寫入到主存中。分配策略當處理器內核

2022-06-15 16:24:48

需要連接多種外設的產品。顯示: 支持雙屏異顯,最高4K@60fps輸出。

RK1126B: 一款集成自研NPU的智能視覺AI處理器,專注于視頻輸入端的AI分析與處理。CPU: 雙核A53,主要負責

2025-12-19 13:44:47

看出,信箱寄存器機制需要處理器輪詢,所以通信效率不高,在休眠/喚醒這類不頻繁的操作中還可以,如果是比較頻繁的核間通信就不適用了,要采取中斷機制。以上是多核處理器啟動的基本原理,至于具體實現,不同的廠商有

2022-07-19 15:00:47

視頻后處理器PNX5100有什么作用?

2021-06-02 06:32:46

的系統控制和配置”、“MMC 控制和管理”、“cache 控制和管理”和“系統性能監控”功能。 在 ARM 的匯編代碼中,凡是看到“mrc”和“mcr”指令,就表明接下來有一小段代碼用來控制協處理器

2019-07-29 15:36:26

,指令cache和數據cache是同一個,在優化后的哈弗架構中使用獨立的指令cache(I-cache)和數據cache(D-cache),即可以同時訪問指令和數據。在ARMv8處理器中,L1

2022-06-15 16:30:39

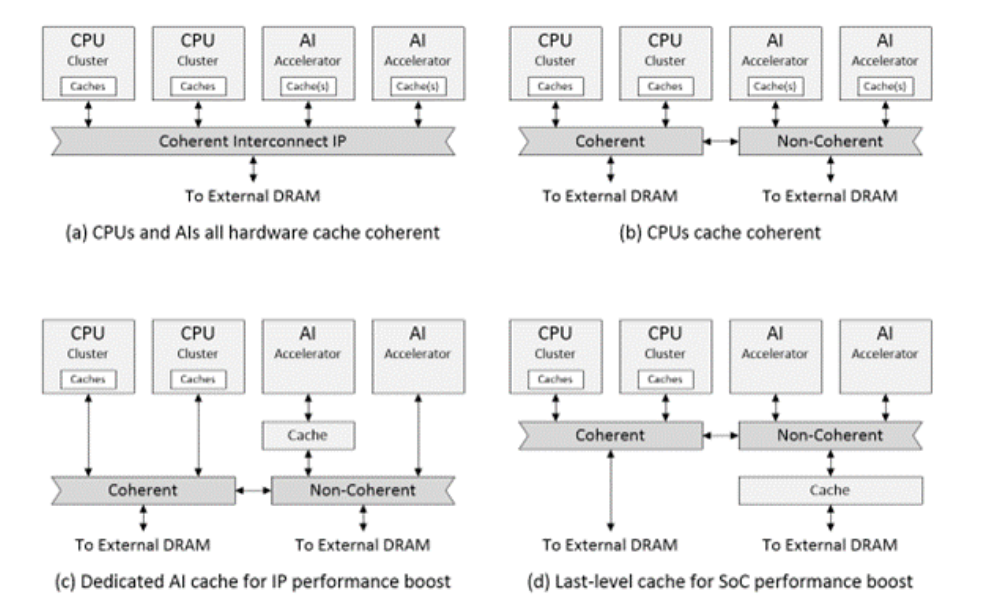

SoC技術的發展使多個異構的處理器集成到一個芯片成為可能,這種結構已成為提高微處理器性能的重要途徑。與傳統的多處理器系統一樣,Cache一致性問題也是片內異構多處理器系統

2009-09-26 15:02:01 11

11 摘要:在SoC系統中,片上緩存(Cache)的采用是解決片上處理器和片外存儲器之間速度差異的重要方法,Cache中用來存儲標記位并判斷Cache是否命中的Tag電路的設計將會影響到整個Cache的

2010-05-08 09:26:24 11

11 CMP是處理器體系結構發展的一個重要方向,其中Cache一致性問題的驗證是CMP設計中的一項重要課題。基于MESI一致性協議,本文建立了CMP的Cache一致性協議的驗證模型,總結了三種驗證

2010-07-20 14:18:27 38

38 高速緩沖存儲器Cache在微處理器中已經成為至關重要的一部分,它的使用能有效地緩和CPU和主存之間速度匹配的問題。本文以32位S698M微處理器的高速緩沖存儲器Cache為例,分析了Cac

2010-09-13 08:19:14 9

9 處理器緩存 緩存(Cache)大小是CPU的重要指標之一,其結構與大小對CPU速度的影響非常大。簡單地講,緩

2009-12-17 11:06:25 503

503 什么是處理器緩存處理器緩存:

Cache(高速緩沖存儲器)是位于CPU與主內存間的一種容量較小但速度很高的存儲器。由于CPU的速度遠

2010-02-04 12:02:26 1093

1093 Blackfin處理器在工業圖像處理中的設計應用

由于處理器(PC))能提供低成本、小尺寸、可擴展的圖像處理系統,所以它們比功耗和價格較高的其它同

2010-03-11 15:58:42 884

884 嵌入式編程需注意的Cache機制及其原理

1 Cache的原理 Cache即高速緩存,它的出現基于兩種因素:一、CPU的速度和性能提高很快,而主

2010-05-26 16:40:03 1653

1653

:本文給出了一種 處理器 系統接口部件的具體設計方案。該接口部件通過使用Split讀和片外Cache來提高處理器的性能。測試結果表明,Split讀和片外Cache能夠以比較低的代價使處理器性能得

2011-06-29 15:59:52 10

10 預處理器的工作原理作用,希望對學者們有幫助。

2015-10-29 11:40:46 0

0 現代高速處理器的設計中對于cache技術的研究已經成為了提高處理器性能的關鍵技術,本文針對在流水線結構中采用非阻塞cache技術進行分析研究,提高cache的命中率,降低缺少代價,提高處理器的性能,并介紹了“龍騰”R2處理器的流水線結構的非阻塞cache 的設計。

2015-12-28 09:54:57 8

8 多核密碼處理器數據緩存機制研究_陳曉鋼

2017-01-07 18:39:17 0

0 機)節點集成到同一芯片內,各個處理器并行執行不同的線程或進程。在基于SMP結構的單芯片多處理機中,處理器之間通過片外Cache或者是片外的共享存儲器來進行通信。而基于DSM結構的單芯片多處理器中,處理器間通過連接分布式存儲器的片內高速交叉開關網絡

2017-10-26 16:24:14 0

0 基于高通Adreno圖形處理器全解析

2017-10-30 16:15:18 11

11 讀了候老師的《深入淺出MFC》后,感覺到Visual C++的Application FrameWork十分精制。在以前,我對SDI結構處理消息有一定的認識,但對于模式對話框的消息機制不了解,讀了

2017-11-07 10:36:12 1

1 隨著集成電路設計復雜度指數級增長,功能驗證已經越來越成為大規模芯片設計的瓶頸,而在多核處理器中,Cache -致性協議十分復雜,驗證難度大。針對Cache -致性協議驗證提出基于模擬驗證的一種基于貝

2017-11-17 17:24:07 2

2 Vviado-HLS基于Xilinx FPGA對C的解析,綜合原理。Vivado-HLS FPGA并行與處理器架構 與處理器架構相比,FPGA結構具有更高的并行。Vivado-HLS對軟件C程序編譯時與處理器編譯是不一樣的執行機制。

2017-11-18 12:23:09 3066

3066

全彩LED顯示屏為何非得要用視頻處理器這個問題,一點不夸張的說視頻處理器的優劣直接決定了全彩LED顯示屏的一個顯示效果。下面就來介紹下LED視頻處理器的主要作用。

2018-01-18 13:53:08 11276

11276 Cache存儲系統知多少?

2018-04-09 16:22:46 1

1 本文首先介紹了協處理器概念,其次介紹了協處理器內部結構與手機協處理器的作用,最后介紹了蘋果的M8協處理器的作用。

2018-04-24 09:27:14 23028

23028 AI已經深入到社會經濟的很多領域,尤其進來在手機行業掀起了一股AI的狂潮。很多智能手機搭載了AI處理器,經具備了AI的功能和應用。當前小米、vivo、OPPO等眾多OEM廠商的旗下智能手機諸多新品均

2018-06-28 06:32:00 1269

1269 日前,高通宣布推出驍龍632處理器、439處理器和429處理器。這三款處理器可以支持廣泛的終端側AI用例,在AI能力、性能、圖形處理等方面都有所增強。可以進一步提升中端和入門級智能手機市場性能與能效

2018-07-10 11:20:00 1339

1339 電感器在電路中的五種作用解析,具體的跟隨小編來了解一下。

2018-07-28 11:05:07 55642

55642

隨著嵌入式計算機應用的發展,嵌入式CPU的主頻不斷提高,這就造成了慢速系統存儲器不能匹配高速CPU處理能力的情況。為了解決這個問題,許多高性能的嵌入式處理器內部集成了高速緩存cache。其中,三星公司的S3C44B0X內部就集成了8 KB空間統一的指令和數據Cache。

2019-03-24 09:07:35 3926

3926

操作系統中的地位和作用、Linux 中文件 Cache相關的數據結構、Linux 中文件 Cache 的預讀和替換、Linux 中文件 Cache 相關 API 及其實現。2 文件 Cache 的地位

2019-04-02 14:38:49 714

714 三年前,AI成為了智能手機的新賣點。一時間,支持AI特性的智能手機快速普及,AI性能表現成為了繼CPU、GPU之后,消費者最為關注的手機處理器參數。如今,展示AI性能已經成為了手機和手機處理器發布會上必不可少的環節。

2020-01-17 15:07:00 7829

7829 本文主要闡述了音頻處理器的作用及音頻處理器和效果器的區別。

2020-04-09 10:41:49 32252

32252 由于處理器是核心硬件,相信我們在選擇處理器的時候都會去關心處理器參數方面,而在處理器核心參數中,我們經常會看到緩存(Cache)這個參數,那么CPU的緩存有什么作用呢?下面小編科普一下關于CPU緩存的作用。

2020-05-19 09:24:56 8547

8547 流處理器這個名詞第一次出現在人們的視線中還要上溯到2006年12月4日, NVIDIA在當天正式對外發布新一代DX10顯卡8800GTX,在技術參數表里面,看不到慣常使用的兩個參數:Pixel

2020-05-29 09:39:01 3656

3656 流處理器這個名詞第一次出現在人們的視線中還要上溯到2006年12月4日, NVIDIA在當天正式對外發布新一代DX10顯卡8800GTX,在技術參數表里面,看不到慣常使用的兩個參數:Pixel

2020-05-31 09:35:23 2661

2661 能夠存留下來讓我們慢慢的回頭看,視頻處理器的出現就是讓我們的視頻能夠在質量上有提升,讓畫面看起來更讓人舒服。下面介紹一下視頻處理器的作用。

2020-06-01 09:29:43 5741

5741 處理器的作用是什么?跟著我一起了解下。

2020-06-10 09:40:11 20333

20333 今天就來說說關于它的那些事兒吧。 只要親手摸一摸處理器頂蓋,就一定會對它的厚實留下深刻印象,很明顯,它的首要作用就是保護脆弱的處理器芯片,可以安裝更緊密更重的散熱器。第二則是借助金屬銅的高導熱能力,快速導出熱

2020-09-09 09:34:14 6104

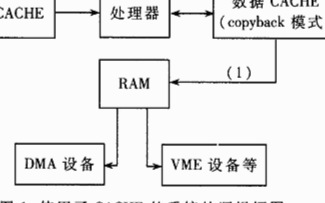

6104 (2)在有DMA控制器的系統和多處理器系統中,有多個部件可以訪問主存?這時,可能其中有些部件是直接訪問主存,也可能每個DMA部件和處理器配置一個CACHE?這樣,主存的一個區塊可能對應于多個

2020-10-04 16:55:00 2509

2509

數據 Cache的實時動態遷移機制,采用四級全互連和遷移互連,以數據訪問頻率為依據對遠程數據進行動態調度,有效降低了遠程訪存的延遲。并基于陣列處理器分布式¢ache結構,通過運動補償等典型算法的并行實現,對所提出的實時

2021-04-07 15:09:11 20

20 Cache的chiplet以3D堆疊的形式與處理器封裝在了一起。 在AMD展示的概念芯片中,處理器芯片是Ryzen 5000,其原本的處理器Chiplet中就帶有32 MB L3 Cache,而在和64

2021-06-21 17:56:57 3955

3955 Linux內核文件Cache機制(開關電源技術與設計 第二版)-Linux內核文件Cache機制? ? ? ? ? ? ? ??

2021-08-31 16:34:54 4

4 深度解析Asp.Net2.0中的Callback機制(ups電源技術維修)-該文檔為深度解析Asp.Net2.0中的Callback機制講解文檔,是一份還算不錯的參考文檔,感興趣的可以下載看看,,,,,,,,,,,,,,,,,

2021-09-27 16:28:20 1

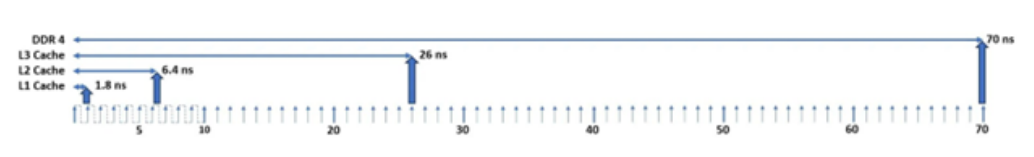

1 L1 Cache和L2 Cache通常和處理器是在一塊實現的。在SoC中,主存和處理器之間通過總線SYSBUS連接起來。

2023-01-08 10:56:03 1725

1725 年間,處理器時鐘頻率以每年55%的速度增長,而主存的增長速度只是7%。在現在的系統中,處理器需要上百個時鐘周期才能從主存中取到數據。如果沒有cache,處理器在等待數據的大部分時間內將會停滯不動。

2023-03-21 14:34:53 2176

2176

按照數據關系劃分:Inclusive/exclusive Cache: 下級Cache包含上級的數據叫inclusive Cache。不包含叫exclusive Cache。舉個例子,L3 Cache里有L2 Cache的數據,則L2 Cache叫exclusive Cache。

2023-05-30 16:02:34 1390

1390

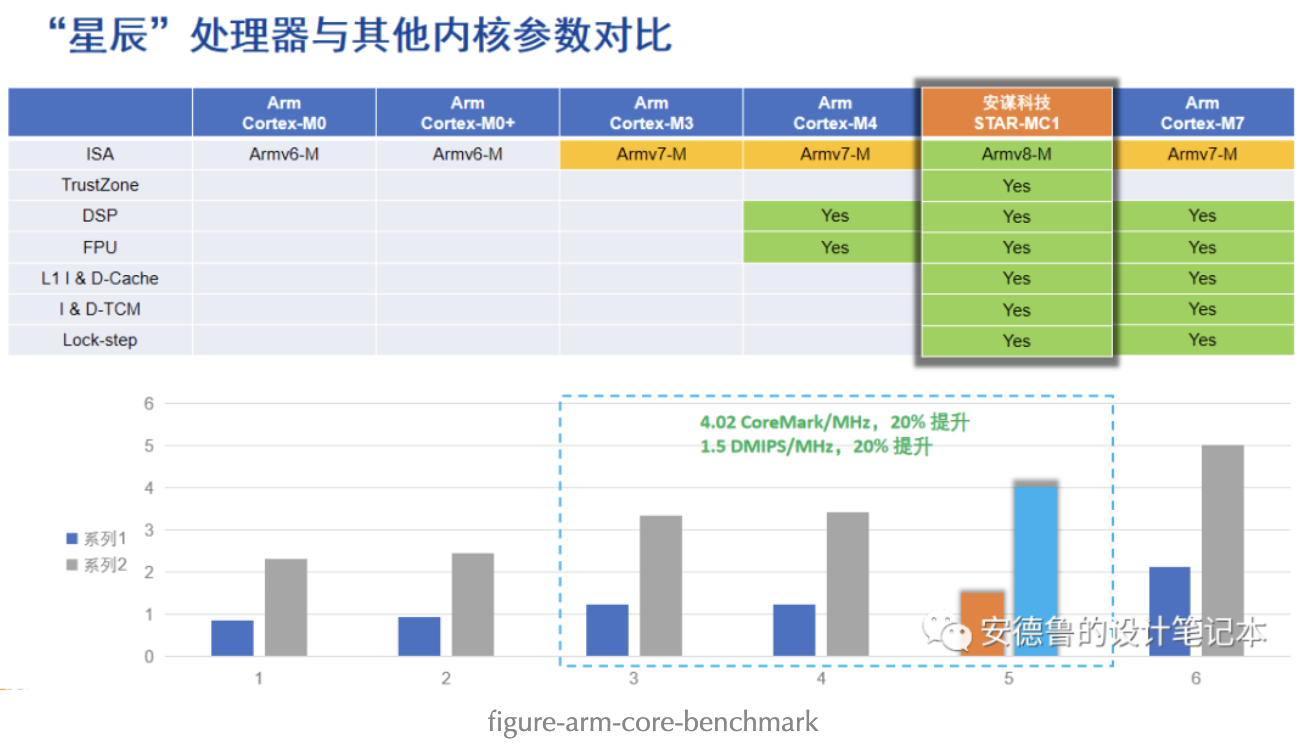

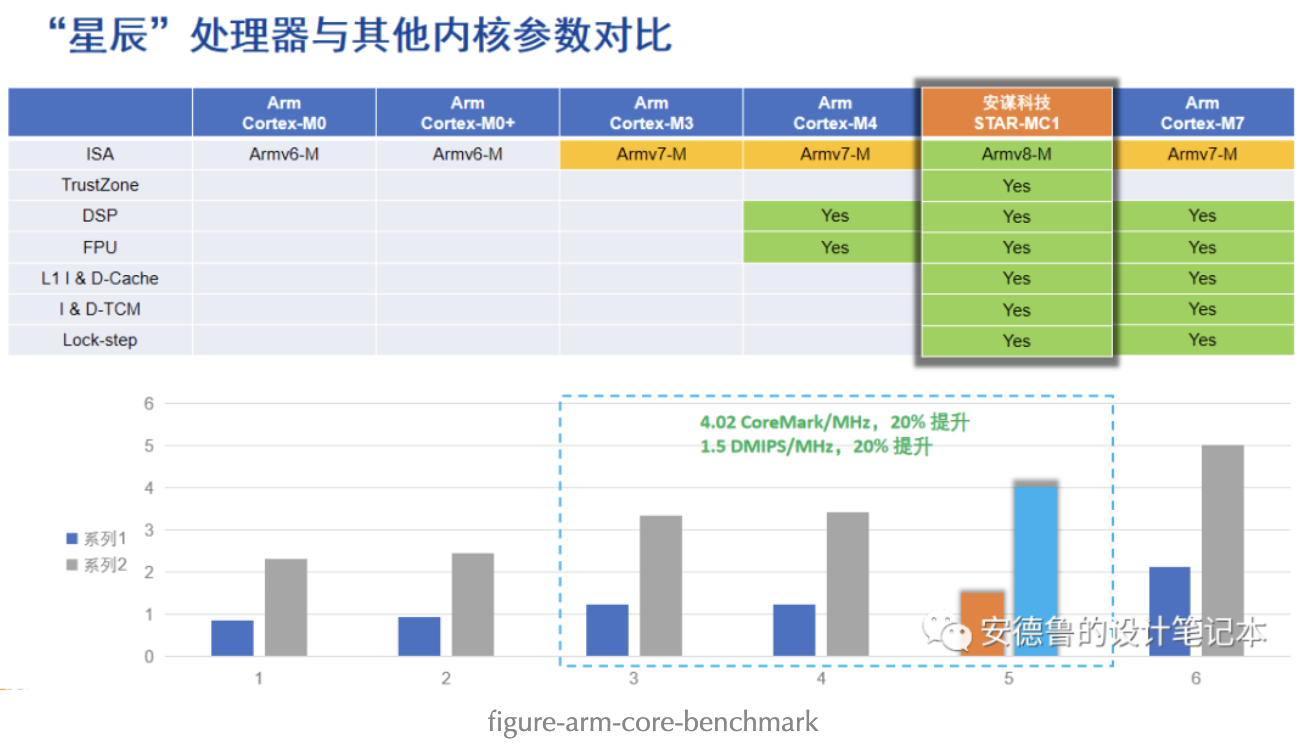

STAR-MC1),從官方數據來看,使用星辰處理器(STAR-MC1)的MM32F5對指令的處理效率要高于使用Cortex-M3處理器的MM32F3。如圖x所示。

2023-07-21 15:08:19 795

795

ARP學習和老化機制在Linux網絡通信中起著至關重要的作用。ARP(Address Resolution Protocol)地址解析協議是將IP地址解析為MAC地址的一種機制。

2023-08-04 16:55:27 2147

2147 STAR-MC1),從官方數據來看,使用星辰處理器(STAR-MC1)的MM32F5對指令的處理效率要高于使用Cortex-M3處理器的MM32F3。如圖x所示。

2023-08-29 17:28:01 1501

1501

視頻處理器是一種專門用來處理視頻信號的器件或組件。它的主要作用是對輸入的視頻信號進行處理和優化,從而提高畫質、增強效果、提供更好的音視頻體驗。視頻處理器通常由多個功能模塊組成,每個模塊負責不同的處理

2024-02-01 17:23:33 5794

5794 處理器,作為計算機系統的核心部件,承載著執行指令、處理數據的重要任務。隨著信息技術的飛速發展,處理器的種類和性能也在不斷提升。本文將對處理器的定義進行闡述,并詳細介紹處理器的種類及其特點,以便讀者對處理器有更深入的了解。

2024-05-12 18:12:00 7659

7659 微處理器在人工智能(AI)方面的應用日益廣泛且深入,成為了推動AI技術發展的重要力量。本文將從微處理器在AI中的核心作用、具體應用案例、技術挑戰與解決方案、以及未來發展趨勢等多個方面進行探討,旨在全面展現微處理器在AI領域的廣泛應用與重要價值。

2024-08-22 14:21:58 2059

2059 微處理器的指令集和指令系統是兩個緊密相關但又有所區別的概念,它們在微處理器的設計和運行中扮演著不同的角色。以下是對這兩個概念的詳細解析,旨在深入探討它們之間的不同點。

2024-10-05 14:57:00 1604

1604 微處理器中的寄存器是計算機體系結構中的核心組成部分,它們扮演著至關重要的角色。寄存器是一種高速的存儲單元,用于暫時存儲數據、指令和地址等信息,以便微處理器能夠快速地訪問和處理這些數據。以下將詳細解釋微處理器中寄存器的作用,從多個方面進行深入剖析。

2024-10-05 15:07:00 2068

2068 Cache(高速緩存)和內存(Memory,通常指主存儲器或RAM)是計算機存儲系統中兩個重要的組成部分,它們在計算機的性能和數據處理中扮演著不同的角色。以下是對Cache和內存之間區別的詳細解析。

2024-09-26 15:28:27 6087

6087 緩存(Cache)是一種高速存儲器,用于臨時存儲數據,以便快速訪問。在計算機系統中,緩存的作用是減少處理器訪問主存儲器(如隨機存取存儲器RAM)所需的時間。 緩存(Cache)概述 緩存是一種位于

2024-12-18 09:28:31 16006

16006 量子處理器(QPU),又稱量子級計算機處理器,是量子計算機中的核心部件,其作用主要體現在以下幾個方面:

一、高速計算與處理能力

量子處理器利用量子比特的疊加和糾纏特性來執行計算

2025-01-27 13:44:00 1663

1663 云拼接處理器作為大屏拼接及音視頻解決方案中的關鍵設備,其性能直接影響著展覽展示、可視化展廳、中小控制室和園區監控等行業的視覺呈現效果與系統運行穩定性。深圳融大視覺科技有限公司推出的云拼接處理器,在

2025-09-05 00:11:45 594

594 深入解析NXP S32G3:高性能汽車網絡處理器的技術洞察 在汽車電子領域,高性能、高安全性的處理器需求日益增長。NXP的S32G3系列處理器憑借其卓越的性能和豐富的功能,成為了眾多汽車應用的理想

2025-12-24 16:45:13 158

158 TDA7418:高性能3頻段汽車音頻處理器的深度解析 在汽車音頻系統的設計中,一款優秀的音頻處理器至關重要。TDA7418作為一款高性能的3頻段汽車音頻處理器,具備豐富的功能和出色的性能,能夠滿足

2026-01-05 18:15:06 923

923

電子發燒友App

電子發燒友App

評論