隨著 RISC -V處理器在 FPGA 領域的廣泛應用,易靈思 FPGA 的 Sapphire RISC-V 內核憑借軟硬核的靈活支持,為開發者提供多樣選擇。本文深入探討 Sapphire SoC 中 RISC - V 平臺級中斷控制器(PLIC),解析其架構與操作機制,助力你深入了解與應用。

Part 01 RISC-V中斷生態系統導論

1.1 中斷在現代計算系統中的角色

在現代計算系統中,中斷是實現異步事件處理的核心機制。它允許外部設備(如網絡控制器、磁盤驅動器或用戶輸入設備)在需要處理器關注時主動發送信號,從而將處理器從低效的、持續性的輪詢(polling)模式中解放出來。通過中斷機制,系統能夠高效地管理多任務并行、處理I/O操作,并對外部事件做出快速響應,這對于構建高性能、高能效的計算平臺至關重要。

1.2 中斷架構的劃分:本地中斷與全局中斷

RISC-V的特權架構對中斷進行了明確的分類,這種設計策略性地分離了不同層級的關注點,以同時優化延遲和可擴展性。中斷源被劃分為兩大類:本地中斷(Local Interrupts)和全局中斷(Global or External Interrupts)。

本地中斷

本地中斷源直接連接到特定的處理器核心(在RISC-V中稱為“Hart”),其處理不經過平臺級中斷控制器(PLIC)。RISC-V標準定義了兩種核心的本地中斷:軟件中斷(Software Interrupts)和計時器中斷(Timer Interrupts)。這些中斷通常由一個名為核心本地中斷器(Core Local Interrupter, CLINT)或更高級的核心本地中斷控制器(Core Local Interrupt Controller, CLIC)的模塊管理 。本地中斷的關鍵特性是延遲極低,因為它不需要在多個Hart之間進行仲裁,并且服務Hart可以通過直接讀取mcause等控制與狀態寄存器(CSR)來快速確定中斷源 。這種設計確保了對時間敏感的核心級功能(如上下文切換調度、核間通信)的最高效處理。

全局(外部)中斷

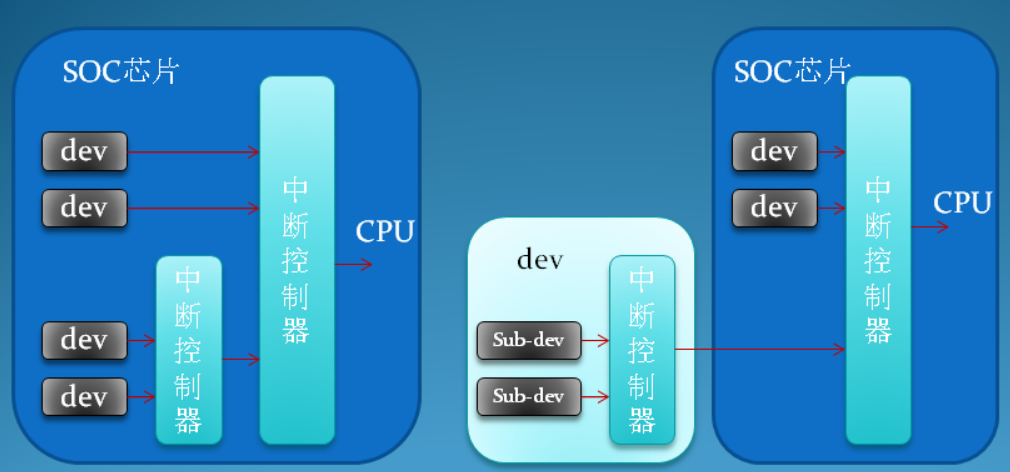

全局中斷,也常被稱為外部中斷,源自處理器核心外部的平臺級設備,例如UART、GPIO、以太網控制器或DMA引擎 。在一個復雜的片上系統(SoC)中,這類中斷源的數量可能非常龐大。為了有效管理這些中斷,RISC-V架構引入了一個專用的、可擴展的控制器,即平臺級中斷控制器(PLIC)。全局中斷需要一個集中的仲裁單元來處理來自眾多外設的請求,根據預設的優先級進行裁決,并將中斷信號路由到一個或多個目標Hart 。

1.3 平臺級中斷控制器(PLIC)的目標與重要性

PLIC是RISC-V針對全局中斷管理所提出的標準解決方案,其在SoC設計中扮演著基石的角色。它的核心目標是解決在擁有豐富外設集的復雜系統中管理大量中斷源的挑戰。PLIC的主要功能可以概括為以下三點:

多路復用(Multiplexing):將來自多達1023個不同外部設備的中斷信號匯集起來進行統一管理。

優先級仲裁(Prioritization):提供硬件支持的中斷優先級機制,確保高優先級的緊急事件能夠優先得到處理。

路由(Routing):根據軟件的配置,將裁決后的中斷通知精確地分發到指定的一個或多個Hart上下文(Hart Context)。

通過將全局中斷的管理從核心中分離出來,PLIC的設計體現了RISC-V架構的模塊化和可擴展性理念。它使得SoC設計者能夠根據平臺外設的復雜程度來調整PLIC的實現規模,而不會影響核心內部計時器等基礎中斷機制的性能。對于旨在運行如Linux等功能完備的操作系統的平臺而言,一個高效的PLIC是不可或缺的組成部分。

Part 02 PLIC架構深度解析

PLIC的硬件架構是一個精心設計的、可配置的硬件排序與過濾引擎。它將識別最高優先級中斷的復雜任務從軟件層面轉移到硬件層面,從而顯著降低了中斷處理的延遲。若沒有PLIC,軟件在收到一個通用的“外部中斷”信號后,必須通過輪詢大量外設的狀態寄存器來確定中斷源,并依據軟件邏輯判斷其優先級,這一過程緩慢且效率低下。PLIC通過其硬件仲裁機制,將這一串行、低效的軟件輪詢循環轉變為并行、高速的硬件決策過程。

2.1 概念框圖與組件交互

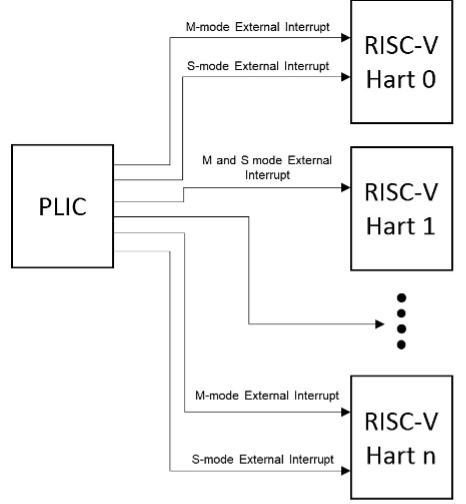

下圖(圖1)展示了PLIC的架構,描繪了從中斷源到中斷目標(Hart)的完整信號流。

圖 1: RISC-V PLIC 概念架構框圖

該架構主要由四個核心組件構成:中斷源、中斷網關、PLIC核心以及中斷目標。

2.2 中斷源與中斷網關:信號接收的前線

中斷源(Interrupt Sources):指產生中斷信號的外部物理設備,如UART、I2C控制器等。PLIC規范支持多達1023個中斷源,其ID范圍為1至10。中斷ID 0被特殊保留,表示“無中斷”。

中斷網關(Interrupt Gateways):每個中斷源都連接到一個專用的中斷網關。網關的職責是處理來自設備的原始中斷信號(可以是電平觸發、邊沿觸發等),并將其轉換為標準化的中斷請求格式,然后轉發給PLIC核心。網關確保在任何時刻,每個中斷源在PLIC核心中最多只能有一個掛起的請求。只有在收到前一個中斷的完成消息后,網關才會轉發來自同一源的下一個新請求。

2.3 PLIC核心:仲裁與路由邏輯

PLIC核心是整個控制器的中樞,它接收來自所有網關的請求,并執行關鍵的仲裁與路由邏輯。其內部主要包含以下幾個關鍵部分:

中斷掛起(Interrupt Pending, IP)位:一個位數組,用于鎖存(latch)從網關傳入的中斷請求。當某個中斷源的IP位被置位時,表示該源有一個活躍的請求正在等待服務。

中斷優先級(Interrupt Priority)寄存器:一個寄存器數組,每個中斷源對應一個。軟件可以通過寫這些寄存器來為每個中斷源分配一個數值化的優先級。

中斷使能(Interrupt Enable, IE)矩陣:一個龐大的位矩陣,允許軟件為每一個中斷目標獨立地使能或禁用每一個中斷源。

優先級閾值(Priority Threshold)寄存器:每個中斷目標都擁有一個獨立的閾值寄存器。PLIC只有在檢測到一個掛起且已使能的中斷,并且其優先級嚴格大于目標當前的閾值時,才會向該目標發送中斷通知。

2.4 中斷目標:定義中斷傳遞的Hart上下文

中斷目標是中斷通知的最終接收者。在RISC-V中,一個中斷目標通常被定義為一個“Hart上下文”,即某個特定Hart上的特定特權模式(例如,Hart 0的機器模式,或Hart 1的監管者模式)。PLIC規范理論上最多可支持15872個獨立的Hart上下文。

當PLIC決定向一個Hart上下文發送中斷通知時,它會通過置位該Hart的mip(機器中斷掛起)或sip(監管者中斷掛起)CSR中的相應位來實現,具體來說是MEIP(機器外部中斷掛起)或SEIP(監管者外部中斷掛起)位。

一個至關重要的架構特性是,PLIC獨立地對待每一個中斷目標,其本身不提供中斷搶占(preemption)或嵌套(nesting)的概念。這些復雜的行為必須由接收中斷的處理器核心自身通過軟件或硬件邏輯來處理。

Part 03 PLIC的核心運行機制

PLIC的強大功能源于其優先級、閾值和使能機制的協同工作。這套機制構成了一個靈活的兩級過濾系統,為操作系統設計者提供了巨大的便利。它成功地將設備的靜態重要性(通過優先級設定)與運行核心的動態上下文(通過閾值調節)分離開來。

3.1 優先級系統:為中斷源賦予重要性

每個中斷源(ID 1-1023)都可以通過寫入其專用的32位內存映射優先級寄存器來分配一個優先級。

優先級值為0是一個特殊值,表示“從不中斷”,這等同于在源頭禁用了該中斷。

優先級1是最低的有效優先級。最高優先級級別由具體的PLIC實現來定義。

為了保證處理的確定性,當多個中斷具有相同的優先級時,PLIC會采用中斷ID作為決勝規則:ID號較小的中斷擁有更高的有效優先級。

3.2 基于閾值的過濾:每個目標的動態中斷屏蔽

每個中斷目標(Hart上下文)都擁有自己的優先級閾值寄存器。PLIC在向目標發送中斷通知前,會進行一次關鍵的比較:只有當一個掛起中斷的優先級嚴格大于該目標閾值寄存器中的值時,通知才會被發出。

將閾值設置為0,意味著允許所有優先級大于0的中斷通過。

將閾值設置為實現所支持的最高優先級,則可以有效地屏蔽該目標的所有全局中斷。

這種機制賦予了軟件(如操作系統內核)強大的動態控制能力。例如,當一個核心進入一個不希望被中等優先級的網絡中斷打擾的臨界區時,內核可以臨時將其閾值提升到網絡中斷的優先級之上。這僅僅屏蔽了該核心的中斷,而不會影響其他核心,也無需全局禁用中斷。

3.3 中斷使能矩陣:對每個目標的精細化控制

PLIC內部維護著一個龐大的中斷使能(IE)位數組,該數組按目標進行組織。對于每一個目標,都有一組與之對應的使能位,每個中斷源占用其中一位。只有當中斷源針對某個目標的IE位被置位時,該中斷才會被該目標所考慮。

這種矩陣式的控制結構支持非常靈活的路由策略。例如,一個調試用的UART中斷可以只為Hart 0使能(用于控制臺I/O),而對正在執行實時控制任務的Hart 1禁用。

3.4 交互與優先級:兩階段過濾流程

綜合來看,PLIC決定是否向一個Hart發出中斷信號是一個嚴謹的多階段過濾過程。對于一個中斷源N和一個中斷目標T,必須同時滿足以下所有條件,中斷通知才會被發出:

中斷N必須處于掛起狀態(其IP位為1)。

中斷N必須為目標T使能(其在IE矩陣中對應T的位為1)。

中斷N的優先級必須大于0。

中斷N的優先級必須嚴格大于目標T的當前閾值。

在所有同樣滿足以上四個條件的中斷中,不存在任何其他中斷M的優先級高于N。

Part 04 完整的中斷生命周期:從設備信號到軟件完成

理解PLIC的完整工作流程需要貫穿硬件和軟件兩個領域。整個過程可以劃分為四個主要階段,每個階段都有明確的責任實體。

4.1 階段一:中斷生成與PLIC裁決(硬件域)

信號生成:一個外部設備(如GPIO)因某個事件(如電平變化)而觸發并拉高其中斷線。

網關請求:與該設備連接的PLIC中斷網關接收到信號,并向PLIC核心發送一個標準化的中斷請求。

請求鎖存:PLIC核心收到請求后,在其中斷掛起(IP)位數組中將對應中斷ID的位設置為1。

持續評估:PLIC的硬件邏輯持續地、并行地評估所有掛起的IP位。對于每一個中斷目標,它都會檢查該中斷是否被使能,以及其優先級是否高于該目標的閾值。

發送通知:一旦某個掛起的中斷通過了針對某個目標的所有檢查,PLIC就會向該目標Hart發出外部中斷通知,通常是置位Hart的mip.MEIP或sip.SEIP位。

4.2 階段二:Hart通知與陷入機制(軟硬件接口)

信號檢測:目標Hart檢測到其外部中斷掛起位(如mip.MEIP)被置位,并且對應的中斷使能位(mie.MEIE)也已置位。

陷入觸發:在mstatus寄存器中的全局中斷使能位(MIE)為1的前提下,Hart會停止當前指令的執行,進入一個“陷入”(trap)狀態。

硬件自動操作:Hart的硬件會自動執行一系列上下文保存操作:將當前的程序計數器(PC)值保存到mepc寄存器;在mcause寄存器中設置一個值以表明陷入原因是外部中斷(例如,機器模式外部中斷的原因為11);保存當前的全局中斷使能狀態,然后禁用全局中斷以防嵌套;最后,跳轉到mtvec寄存器所指向的地址開始執行異常處理代碼。

4.3 階段三:關鍵的聲明/完成協議(軟件域)

聲明(Claim):此時,軟件中斷處理程序開始執行。它的首要任務是向PLIC聲明中斷。這通過讀取其Hart上下文專用的claim/complete寄存器來完成。PLIC硬件在響應這次讀操作時,會返回當前待處理的、優先級最高的中斷ID。這次讀取操作是原子的,并且帶有一個至關重要的副作用:PLIC會自動清除該中斷ID對應的IP位。

服務(Service):軟件通過上一步獲得的ID,知道了中斷源。它利用這個ID來調用相應的設備驅動程序中的中斷服務例程(Interrupt Service Routine, ISR)。ISR執行具體的工作,例如從UART的FIFO中讀取數據。一個常被忽略但至關重要的步驟是:ISR必須清除設備本身的中斷狀態。

完成(Complete):ISR執行完畢后,軟件必須向PLIC發送完成信號。這通過將之前聲明時獲得的同一個中斷ID寫回到同一個claim/complete寄存器來完成。這個寫操作通知了中斷網關,該中斷已被完全處理,允許網關在需要時轉發來自同一源的新中斷。

4.4 階段四:上下文恢復與中斷重使能(軟硬件接口)

返回:主陷入處理程序執行一條特權返回指令(如mret)。

硬件自動恢復:Hart硬件自動將mepc中保存的地址恢復到PC,并恢復陷入前的全局中斷使能狀態,從而重新允許中斷的發生,程序從被中斷處繼續執行。

下表清晰地總結了在中斷生命周期的每個環節中,各個實體的責任。

表1:中斷生命周期責任矩陣

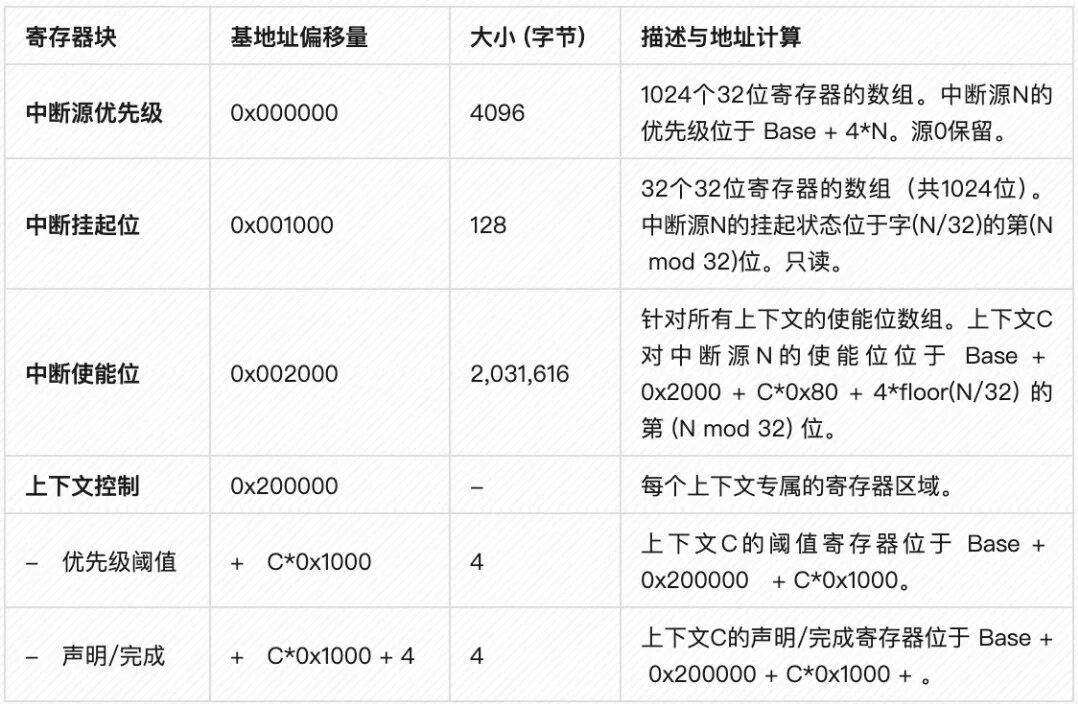

Part 05 PLIC寄存器接口與內存映射

PLIC是一個內存映射設備,這意味著CPU通過標準的加載(load)和存儲(store)指令來訪問其內部寄存器。RISC-V規范定義了PLIC各個寄存器塊的相對偏移量,但并未強制規定其基地址。基地址由具體的SoC平臺定義,軟件需要從設備樹(Device Tree)等平臺信息中獲取。

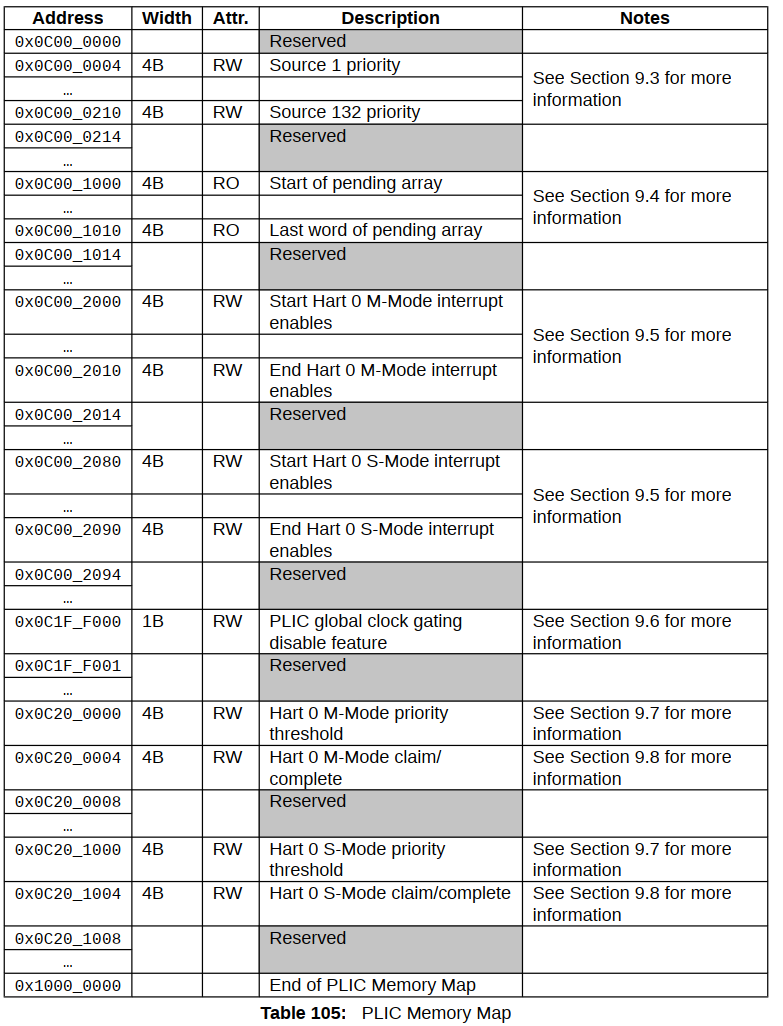

下表整合了來自多個規范文檔的信息,提供了一個全面的PLIC寄存器內存映射參考。

表2:PLIC綜合寄存器內存映射表

注:Base指PLIC模塊的內存映射基地址,C指上下文ID,N指中斷源ID。

Part 06 PLIC軟件編程實踐指南

PLIC的聲明/完成協議為軟件和硬件之間建立了一份嚴格且不可協商的契約。對同一個寄存器地址的讀(聲明)和寫(完成)所附帶的副作用是這份契約的核心,是整個外部中斷系統正確運行的基礎。任何對該協議的違反,例如聲明后忘記完成,或是不聲明而直接輪詢設備,都會導致系統中斷功能失常甚至崩潰。

6.1 系統初始化與PLIC配置序列

在系統啟動階段,通常由引導加載程序(bootloader)或操作系統內核對PLIC進行初始化。一個標準的配置序列如下:

全局禁用中斷:通過清除mstatus.MIE位,確保在配置過程中不會有中斷發生。

禁用所有源:遍歷所有PLIC中斷源的優先級寄存器,將其值全部設為0,以禁用所有中斷源。

清除所有使能:清除所有上下文的所有中斷使能位。

設置默認閾值:為所有目標的優先級閾值寄存器設置一個安全的默認值。通常設為0,表示允許所有已使能的中斷;或設為最大值,表示暫時屏蔽所有中斷。

配置特定中斷:對于需要使用的每個設備中斷:

在其中斷源優先級寄存器中設置一個非零的優先級值(例如1到7)。

在中斷使能矩陣中,為需要接收該中斷的目標上下文設置相應的使能位。

設置陷入向量:配置mtvec寄存器,使其指向主陷入處理程序的入口地址。

全局使能中斷:設置mstatus.MIE位,重新允許中斷。

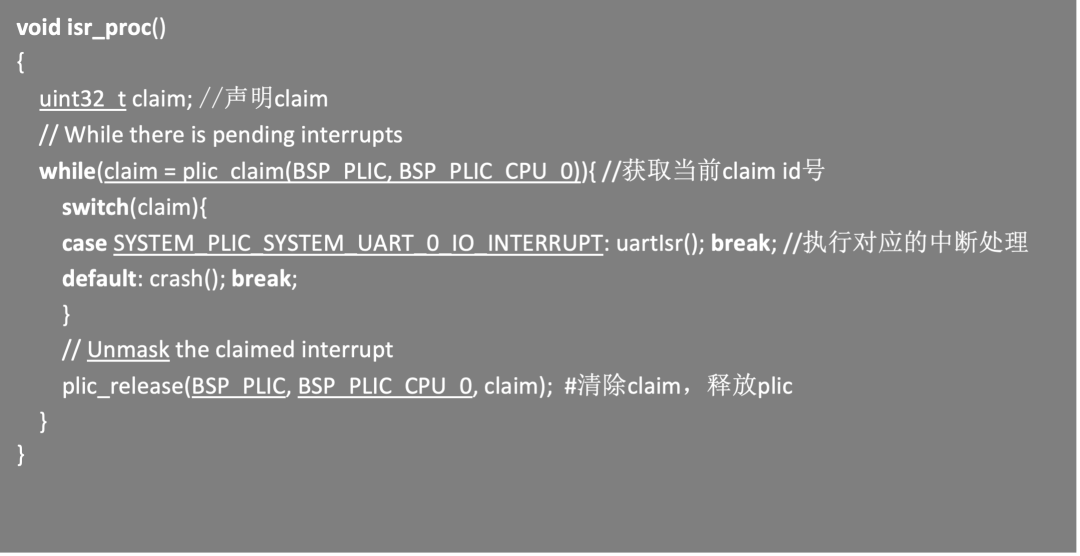

6.2 實現健壯的中斷服務例程(ISR)

一個健壯的PLIC中斷處理程序必須嚴格遵循“聲明 -> 服務 -> 完成”的序列。以下是偽代碼示例和關鍵點說明:

關鍵點:在設備ISR(如uart0_isr())內部,必須通過訪問設備自身的寄存器來清除引起中斷的條件。對于電平觸發的中斷,如果不這樣做,設備會持續斷言中斷信號,導致PLIC在完成當前中斷后立即再次觸發同一個中斷,形成“中斷風暴” 。

6.3 高級考量:多核與中斷處理循環

多核仲裁:PLIC的claim操作是原子的,這為多核環境提供了天然的硬件鎖。即使一個中斷被同時路由到多個Hart,PLIC也確保只有一個Hart能夠成功聲明它。當一個Hart讀取claim寄存器并獲得中斷ID時,其他Hart在同一時刻讀取只會得到0(表示無中斷)。

處理多個掛起中斷:為了提高效率,一個設計良好的中斷處理程序應該在一個循環中處理中斷。在完成一個中斷后,應立即嘗試再次聲明。如果返回非零ID,則表示有另一個中斷正在等待處理,應繼續服務。此循環應持續進行,直到claim操作返回0為止。這避免了為處理背靠背發生的多個中斷而反復進入和退出陷入處理程序的巨大開銷。

Part 07 結論:PLIC作為RISC-V可擴展性的基石

7.1 關鍵架構特性總結

PLIC的設計體現了RISC-V架構的核心理念。其關鍵特性包括:集中的硬件仲裁機制、基于優先級的硬件排序、通過使能矩陣實現的靈活路由,以及通過每個目標的獨立閾值實現的動態屏蔽。這些特性共同構成了一個強大而高效的全局中斷管理框架。

7.2 PLIC在使能復雜多外設系統中的作用

PLIC的架構使其能夠從容應對從僅有少量外設的簡單微控制器到擁有數十個中斷源和多個核心、能夠運行Linux等復雜操作系統的應用處理器的擴展需求。它通過硬件加速中斷仲裁,為構建高性能、高響應性的RISC-V系統提供了堅實的基礎。

7.3 未來方向與演進中的RISC-V中斷格局

PLIC規范體現了RISC-V的一個核心哲學:定義一個最小化的、功能性的基線以確保互操作性,同時為實現者保留優化和差異化的空間。這是一個雙刃劍。規范定義了寄存器的偏移量和行為,為通用軟件驅動程序提供了基礎。然而,它將基地址、源和目標的最大數量、優先級級別數以及中斷觸發類型(電平/邊沿)的配置等細節留給了實現者。

這種靈活性允許SoC設計者根據成本和需求量體裁衣,但同時也給軟件帶來了挑戰。操作系統需要一種機制來發現其所運行硬件的具體參數。因此,設備樹(DeviceTree)等平臺描述機制在RISC-V生態中至關重要,它為軟件提供了一種標準化的方式來了解硬件的具體實現。

同時,RISC-V中斷生態系統也在不斷演進。雖然PLIC是當前管理全局中斷的標準,但新的架構如核心本地中斷控制器(CLIC)正在為需要更低延遲和向量化中斷支持的場景提供替代方案。這表明RISC-V社區在中斷處理領域持續創新,以滿足更多樣化的應用需求。總而言之,PLIC的設計完美地展示了規范的簡潔性/靈活性與軟件的復雜性/可移植性之間的權衡,這也是整個RISC-V生態系統的一個顯著特征。

易靈思公司介紹

易靈思是一家國產FPGA公司,總部位于深圳前海。公司憑借自主可控的Quantum硬件架構,采用邏輯和路由可以互換的XLR結構,實現了創新的產品設計與軟件算法,使得FPGA產品具備低功耗、小體積、高密度、高性能等優勢。已量產的40nm Trion系列及16nm鈦金系列 FPGA產品,廣泛應用于機器視覺、顯示、工業控制、醫療、汽車、AI和通信等終端領域。

重要產品

鈦金系列FPGA具有增強的Quantum架構,16nm工藝,35K 至 1,000K 邏輯單元,超高性能 300-500MHz,封裝最小可至3.5mm*3.4mm@60K LE,功耗低至競爭對手的1/4,硬核資源豐富,最新產品TJ375現已量產。

-

處理器

+關注

關注

68文章

20267瀏覽量

252844 -

中斷控制器

+關注

關注

0文章

64瀏覽量

9830 -

RISC-V

+關注

關注

48文章

2897瀏覽量

53125

原文標題:RISC-V平臺級中斷控制器(PLIC):架構與操作機制綜合分析

文章出處:【微信號:易靈思官微,微信公眾號:易靈思官微】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

RISC-V內核的32位通用微控制器 GD32VF103芯片簡介

學習RISC-V入門 基于RISC-V架構的開源處理器及SoC研究

RISC-V應用領域的拓展

RISC-V SoC 新開源平臺發布 zqh_riscv

RISC-V核、平臺和芯片該如何選擇?

256核!賽昉發布全新RISC-V眾核子系統IP平臺

三種RISC-V SoC系統芯片將提供各種計算和 I/O 功能

中斷控制器的驅動解析(上)

中斷控制器級聯的類型有哪幾種

RISC-V怎么實現核間中斷?核心本地中斷控制器(CLINT)深度解析

易靈思Sapphire SoC中RISC-V平臺級中斷控制器深度解析

易靈思Sapphire SoC中RISC-V平臺級中斷控制器深度解析

評論