Kintex-7 FPGA的內部結構相比傳統FPGA的內部結構嵌入了DSP48E1,PCIE,GTX,XADC,高速IO口等單元,大大提升了FPGA的性能。

2023-08-24 09:26:56 3325

3325

本文章以8086微機系統為例,簡要介紹微機系統的物理構成。一、結構概述8086微機系統內部分為執行單元(EU)與總線接口單元(BIU)兩部分。其中執行單元由運算器、通用寄存器、標志寄存器、控制電路幾部分組成。具體器件構成見下圖:二、具體講解1.執行單元數據寄存器AX:累加器I/O接口與單片機

2022-01-25 07:50:31

Verilog HDL優點:類似C語言,上手容易,靈活。大小寫敏感。在寫激勵和建模方面有優勢。缺點:很多錯誤在編譯的時候不能被發現。VHDL優點:語法嚴謹,層次結構清晰。缺點:熟悉時間長,不夠靈活

2021-08-19 16:07:45

希望在今后的學習中大家多多幫助,先來幾個基礎的verilog 教材吧 現在我用到了FPGA關鍵分配的知識。 不過還是想系統的學習一下。那就先從軟件的使用和語法開始學習吧。 完整的pdf格式文檔電子發燒友下載地址(共31頁): FPGA中文VHDL語言教程.pdf

2018-07-04 01:11:32

FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法介紹了利用現場可編程邏輯門陣列FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法。重點介紹了DDS技術在FPGA中的實現

2012-08-11 18:10:11

的設計早期就能查驗設計系統的功能可行性,隨時可對設計進行仿真模擬。3.大規模設計一些大型的 FPGA 設計項目必須有多人甚至多個開發組共同并行工作才能實現。VHDL 語句的行為描述能力和程序結構決定了它具有

2018-09-07 09:04:45

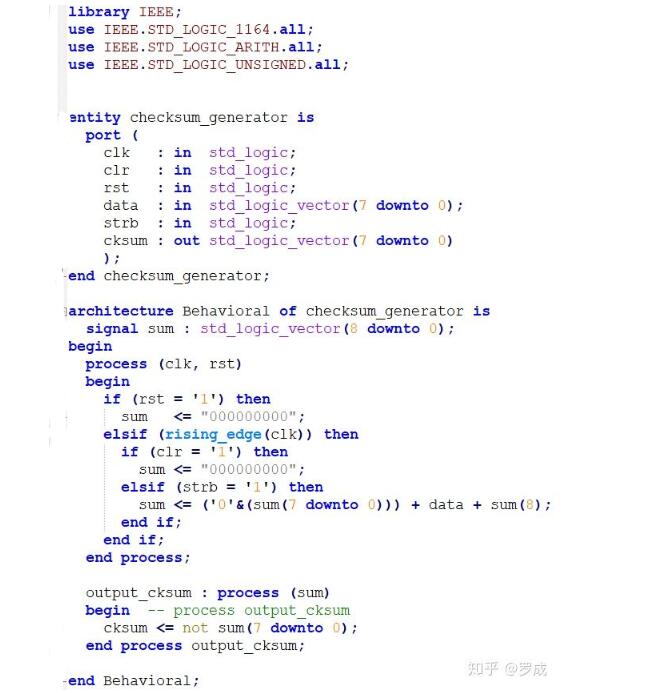

一般的 VHDL 程序可以由實體(Entity)、結構體(Architecture)、配置(Configuration)、程序包和程序包體(Package)以及庫(Library)5 個部分

2018-09-07 09:11:08

VHDL與FPGA設計

2012-08-17 09:44:37

程序的基本結構由于VHDL已是IEEE規定的標準,所以只是CPLD、FPGA等芯片公司,它們都會提供這個標準的定義庫(Library IEEE),而且由于這里面寫了許多的定義和參數,初學者一時之間也

2009-03-19 14:52:00

超高速集成電路硬件描述語言,主要是應用在數字電路的設計中。它在中國的應用多數是用在FPGA/CPLD/EPLD的設計中。當然在一些實力較為雄厚的單位,它也被用來設計ASIC。VHDL主要用于描述數字系統的結構

2015-09-30 13:48:29

電流保護、正序電流保護、過載保護、堵轉保護、過熱保護、失壓保護等功能。最后對電動機微機保護裝置提出了一些改進看法,并預測了微機電動機保護裝置的發展趨勢。闡述了微機保護的硬件結構原理和微機型電動機保護裝置的

2021-09-02 07:40:53

早上剛考完微機原理, 唉, 沒心復習, 發現好多不會填不管了, 對不掛科我還是比較有信心滴~發個之前微機原理實驗課寫的小程序, 實現一個簡易的計算器, 不支持除法和()這類的表達式, 本來想寫

2019-03-22 06:10:16

保護裝置的故障和誤差概率,從而提高裝置的可靠性。微機保護裝置可靠性高,可以更好地滿足現代電力系統的運行要求。通過分析影響線路保護的因素,提出了一些改善繼電保護的措施,以供參考。一、影響方面1.在強電磁干擾信號

2018-09-27 09:27:29

ModelSim IntelFPGA中是否提供VHDL源代碼模板?我注意到該選項存在于標準ModelSim版本中,但我還沒有在IntelFPGA版本中找到它。以上來自于谷歌翻譯以下為原文

2018-11-14 11:42:38

相關專業,具有良好的專業基礎知識。 感興趣可滴滴 JYHXDX534

2.工作年限不限,有工作經驗或優秀應屆畢業生亦可。

3.對FPGA芯片架構和資源有深入的理解,精通Verilog HDL、VHDL

2024-11-12 16:40:14

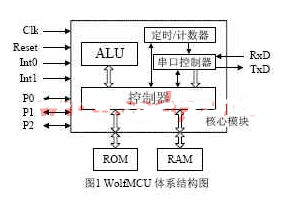

微型計算機的原理及結構一般不易理解掌握,利用FPGA來學習并構建一個簡易微型計算機無疑是一個好方法,對EDA的軟硬件學習也是一個不錯的選擇,可為將來進行相關ASIC沒計打下良好的基礎。

2014-12-04 14:35:41

微型計算機的原理及結構一般不易理解掌握,利用FPGA來學習并構建一個簡易微型計算機無疑是一個好方法,對EDA的軟硬件學習也是一個不錯的選擇,可為將來進行相關ASIC沒計打下良好的基礎。

2014-12-04 14:36:22

1.熟悉FPGA架構及應用,熟悉圖像算法的FPGA實現。

2.熟悉verilog vhdl,熟悉Xilinx或Intel等開發工具。

3.有AI算法 fpga實現經驗優先。

4.本科及以上學歷,碩士優先。具有強烈的責任心,執行力,良好的溝通能力和團隊合作能力。

2024-09-02 15:50:50

請問使用VHDL語言設計FPGA有哪些常見問題?

2021-05-06 09:05:31

一種基于FPGA的簡易頻譜分析儀設計方案,其優點是成本低,性能指標滿足教學實驗所要求的檢測信號范圍。

2021-04-30 06:43:21

`勇敢的芯伴你玩轉Altera FPGA連載4:Verilog與VHDL特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD Verilog

2017-09-26 21:07:34

的設計帶來了極大的靈活性,用戶可以利用FPGA(現場可編程門陣列)來開發出一個精簡指令的CPU,同時對微型計算機的原理及結構進行充分研究,便于將來進行相關ASIC(專用集成電路)設計,也可用于計算機原理教學之中。

2019-06-27 07:40:42

基于FPGA的簡易數字信號傳輸性能分析儀

2015-12-21 09:40:36

基于FPGA的簡易數字信號傳輸性能分析儀_張驍

2015-12-21 12:03:56

本帖最后由 eehome 于 2013-1-5 09:50 編輯

基于FPGA的簡易邏輯分析儀

2012-07-19 19:01:30

目前,由于頻譜分析儀價格昂貴,高等院校只是少數實驗室配有頻譜儀。但電子信息類教學,如果沒有頻譜儀輔助觀察,學生只能從書本中抽象理解信號特征,嚴重影響教學實驗效果。 針對這種現狀提出一種基于FPGA的簡易頻譜分析儀設計方案,其優點是成本低,性能指標滿足教學實驗所要求的檢測信號范圍。

2019-08-23 07:07:07

http://115.com/file/ant54869#《基于VHDL的FPGA與NIOS_II實例精煉》第七章代碼.rarhttp://115.com/file/e7wphx31#《基于VHDL

2012-02-06 11:27:54

精煉》第十五章_SDRAM讀寫操作的實現.avihttp://115.com/file/c2m0dlb3#《基于VHDL的FPGA與NIOS_II實例精煉》第二章_VHDL的基本結構.avihttp

2012-02-06 11:22:55

信息。 多CPU結構設計是防止保護誤動,提高微機保護系統可靠性的一種有效措施,但采用多CPU結構使硬件結構復雜,調試繁瑣,成本高,而且當多CPU同時程序跑飛時,同樣造成控制出口失控,有可能引起誤動

2019-04-25 07:00:04

語言進行CPLD/FPGA設計開發,Altera和Lattice已經在開發軟件方面提供了基于本公司芯片的強大開發工具。但由于VHDL設計是行為級設計,所帶來的問題是設計者的設計思想與電路結構相脫節,而且

2019-06-18 07:45:03

利用現場可編程門陣列(FPGA)和VHDL 語言實現了PCM碼的解調,這樣在不改變硬件電路的情況下,能夠適應PCM碼傳輸速率和幀結構變化,從而正確解調數據。

2021-05-07 06:58:37

本人小菜鳥,開始學FPGA的時候學的Verilog語言,后來因為課題組前期的工作都是VHDL就該學VHDL了。最近聽了幾個師兄的看法,說國內用VHDL的已經很少了,建議我還是堅持用Verilog,小菜現在好糾結,請問到底應該用哪種語言呢?望各位大神指點!

2015-07-08 10:07:56

VHDL硬件描述語言教學:包括fpga講義,VHDL硬件描述語言基礎,VHDL語言的層次化設計的教學幻燈片

2006-03-27 23:46:49 93

93 第1章 緒論 1.1 關于EDA 1.2 關于VHDL 1.3 關于自頂向下的系統設計方法 1.4 關于應用 VHDL的 EDA過程 1.5 關于在系統編程技術 1.6 關于FPGA/CPLD的優勢 1.7

2008-06-04 10:24:06 1682

1682 [學習要求] 掌握VHDL硬件描述語言的基本語法和源文件的結構,學會用VHDL硬件描述語言設計典型數字邏輯電路。[重點與難點]重點:VHDL語言的程序結構;VHDL語言的數據類型及數

2009-03-18 20:02:35 47

47 首先介紹異步FIFO 的概念、應用及其結構,然后分析實現異步FIFO的難點問題及其解決辦法; 在傳統設計的基礎上提出一種新穎的電路結構并對其進行綜合仿真和FPGA 實現。

2009-04-16 09:25:29 46

46 介紹高速圖像采集系統的硬件結構及工作原理, 講述FPGA 在圖像采集與數據存儲部分的VHDL 模塊設計, 給出采集同步模塊的VHDL 源程序。

2009-04-16 10:45:55 15

15 的一種新型小型化微機繼電保護測試儀。本微機繼電保護測試儀采用單機獨立運行,亦可聯接筆記本電腦運行的先進結構。儀器主機采用DSP+FPGA結構,真16位DAC輸出、

2022-11-10 20:31:27

剖析硬件描述語言VHDL-AMS 的新特性。通過對A/D 轉換器和D/A 轉換器進行建模和仿真分析可以看出,VHDL-AMS 突破了VHDL 只能設計數字電路的限制,使得VHDL 可以應用于模擬以及混合信

2009-07-08 09:49:23 22

22 FPGA/VHDL技術是近年來計算機與電子技術領域的又一場革命。本書以AAltera公司的FPGA/CPLD為主詳細介紹了FPGA、CPLD為主詳細介紹了FPGA的相關知識,MAX+PLUSⅡ開發環境和VHDL語言基礎,并

2009-07-11 15:06:42 58

58 基于FPGA的雙通道簡易可存儲示波器設計:本文介紹了一種基于FPGA的采樣速度60Mbit/s的雙通道簡易數字示波器設計,能夠實現量程和采樣頻率的自動調整、數據緩存、顯示以及與計算機

2009-09-29 10:45:23 110

110 觀測信號頻譜在科研中具有重大意義,在教學實驗中也有利于學生更直觀深入地了解信號特征。采用單片機C8051和FPGA,外加高速A/D轉換器設計一種簡易的頻譜分析儀。該系統主要包

2010-12-28 10:43:45 101

101 實驗六、VHDL的基本描述語句設計一? 實驗目的1掌握VHDL語言的基本結構及設計的輸入方法。2掌握VHDL語言的基本描述語句的使用方法。二? 實驗設備

2009-03-13 19:23:57 2351

2351 【摘 要】 通過設計實例詳細介紹了用VHDL(VHSIC Hardware DescriptionLanguage)語言開發FPGA/CPLD的方法,以及與電路圖輸入和其它HDL語言相比,使用VHDL語言的優越性。

2009-05-10 19:47:30 1437

1437

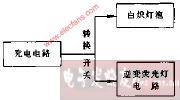

簡易應急燈電路結構電路圖

2009-06-11 11:25:27 7505

7505

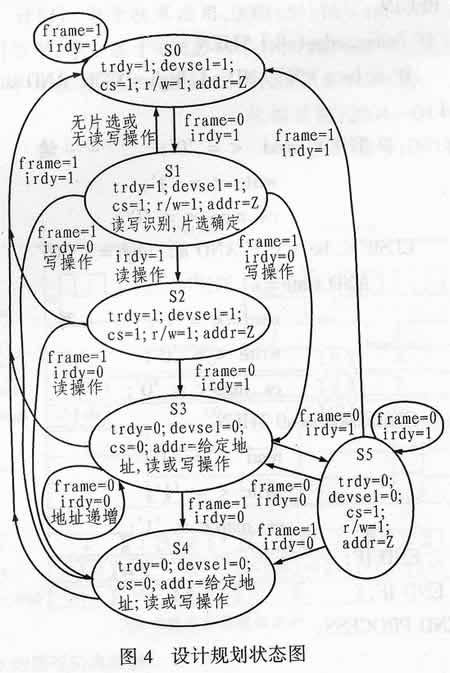

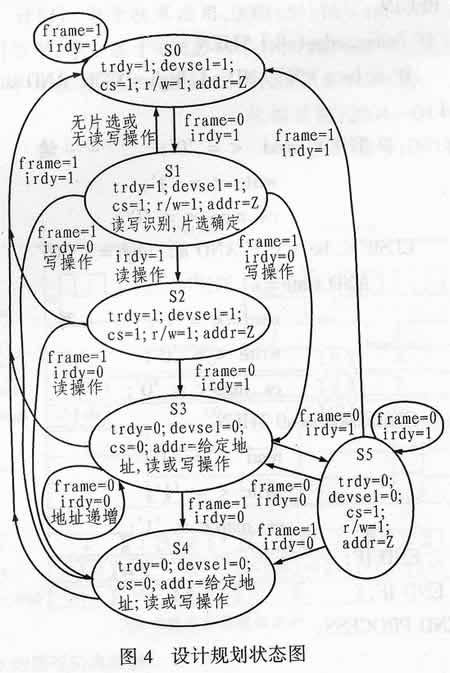

摘要: 從PCI時序分析入手,重點闡述了PCI通用的狀態機設計,說明了用VHDL語言來實現本PIC通信狀態機的軟件設計以及進行MaxPlusII驗證的程序和方法。用該方法所設

2009-06-20 13:10:10 1076

1076

摘要:介紹高速圖像采集系統的硬件結構及工作原理,講述FPGA在圖像采集與數據存儲部分的VHDL模塊設計,給出采集同步模塊的VHDL源程序。

關鍵

2009-06-20 14:35:02 919

919

數字電壓表的VHDL設計與實現

介紹數字電壓表的組成及工作原理,論述了基于VHDL語言和FPGA芯片的數字系統的設計思想和實現過程。 關鍵詞:數字電壓表;VHDL語

2009-10-12 19:14:32 2145

2145

采用CPLD/FPGA的VHDL語言電路優化原理設計

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工業標準硬件描述語言,是隨著可編程邏輯器件(PLD)的發展而發展起

2010-03-19 11:38:02 2834

2834

Verilog HDL與VHDL及FPGA的比較分析. Verilog HDL優點:類似C語言,上手容易,靈活。大小寫敏感。在寫激勵和建模方面有優勢。

2011-01-11 10:45:29 1580

1580 本文采用VHDL描述語言,充分利用Xilinx公司Spartan II FPGA的系統資源,設計實現了一種非對稱同步FIFO,它不僅提供數據緩沖,而且能進行數據總線寬度的轉換。

2011-01-13 11:33:43 2240

2240 針對傳統的實現FPGA局部動態可重構中總線宏的設計方法比較復雜的問題,提出了一種Virtex-5 FPGA局部動態重構中基于Slice的總線宏的簡易設計方法。在介紹總線宏基本原理的基礎上,分析傳統設計方法的復雜性,結合Virtex-5芯片的結構特點,以Xilinx的ISE9.1i和

2011-01-15 15:37:53 0

0 EDA與VHDL的實用電路模塊設計分析

2011-03-02 16:57:46 0

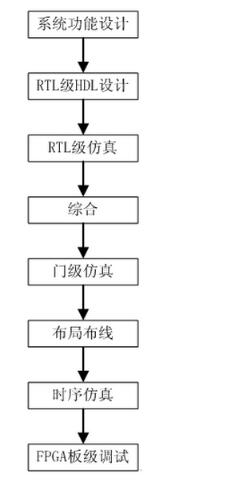

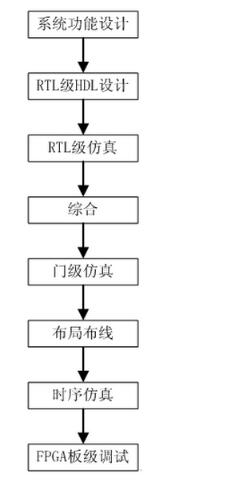

0 用 VHDL /VerilogHD語言開發PLD/ FPGA 的完整流程為: 1.文本編輯:用任何文本編輯器都可以進行,也可以用專用的HDL編輯環境。通常VHDL文件保存為.vhd文件,Verilog文件保存為.v文件 2.功能仿真

2012-05-21 12:58:06 1687

1687 為了能夠更簡潔嚴謹地描述MTM總線的主模塊有限狀態機的狀態轉換,同時減少FPGA芯片功耗,提高系統穩定性,文中在分析MTM總線結構和主模塊有限狀態機模型的基礎上,基于VHDL語言采

2012-05-29 15:39:09 20

20 本資料是關于基于Quartus II FPGA/CPLD數字系統設計實例(VHDL源代碼文件),需要的可以自己下載。

2012-11-13 14:03:36 907

907 altera FPGA/CPLD高級篇(VHDL源代碼)

2012-11-13 14:40:38 135

135 本書分為4個部分:Quartus Ⅱ軟件的基本操作、VHDL語法介紹、FPGA設計實例和Nios Ⅱ設計實例;總結了編者幾年來的FPGA設計經驗,力求給初學者或是想接觸這方面知識的讀者提供一種快速入

2012-11-28 11:48:12 635

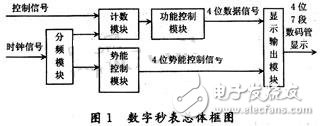

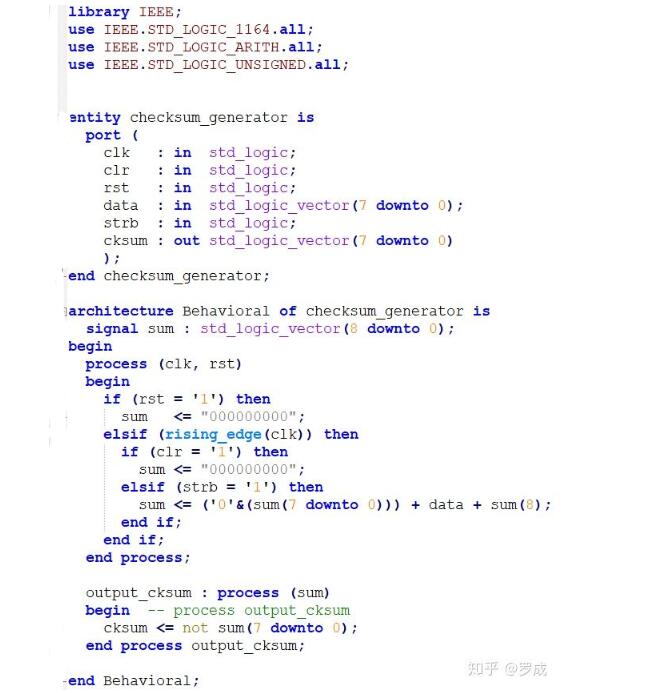

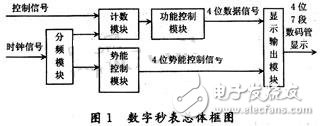

635 文中著重介紹了一種基于FPGA利用VHDL硬件描述語言的數字秒表設計方法,在設計過程中使用基于VHDL的EDA工具ModelSim對各個模塊仿真驗證,并給出了完整的源程序和仿真結果。

2012-12-25 11:19:24 7092

7092 FPGA簡易電子琴設計具體的模塊分析和源程序,

2016-02-16 16:32:57 31

31 本書共分為三個基本組成部分,首先詳細介紹VHDL語言的背景知識、基本語法結構和VHDL代碼的編寫方法;然后介紹VHDL電路單元庫的結構和使用方法,以及如何將新的設計加入到現有的或自己新建立的單元庫中

2016-04-25 17:07:53 0

0 本書共分為三個基本組成部分,首先詳細介紹VHDL語言的背景知識、基本語法結構和VHDL代碼的編寫方法;然后介紹VHDL電路單元庫的結構和使用方法,以及如何將新的設計加入到現有的或自己新建立的單元庫中

2016-04-25 17:07:53 0

0 Xilinx FPGA工程例子源碼:VHDL實現對圖像的采集和壓縮

2016-06-07 14:54:57 6

6 Xilinx FPGA工程例子源碼:含Verilog和VHDL版本級詳細說明文檔

2016-06-07 14:54:57 0

0 Xilinx FPGA工程例子源碼:簡易邏輯分析儀的設計用源代碼

2016-06-07 15:07:45 19

19 Xilinx FPGA工程例子源碼:基于XILINX的XC3系列FPGA的VGA控制器的VHDL源程序

2016-06-07 15:07:45 12

12 Xilinx FPGA工程例子源碼:用FPGA模擬VGA時序PS_2總線的鍵盤接口VHDL源代碼

2016-06-07 15:11:20 33

33 vhdl語法介紹FPGA設計實例nios ii設計實例北航版本

2016-07-14 17:34:13 74

74 VHDL程序實體--EDA資料,設計實體是VHDL語言設計的基本單元,簡單的可以是一個與門,復雜的可以是一個微處理器或一個數字系統,其結構基本是一致的,都是由實體說明和結構體兩部分組成。實體說明

2016-11-21 15:40:34 0

0 目前許多FPGA的邏輯資源(LE)都已超過1萬門,使得片上可編程系統SOPC已經成為可能。算術邏輯單元ALU應用廣泛,是片上可編程系統不可或缺的一部分。利用VHDL語言在FPGA芯片上設計ALU的研究較少,文中選用FPGA來設計32位算術邏輯單元ALU,通過VHDL語言實現ALU的功能。

2018-07-22 11:22:00 7904

7904

VHDL語言是一種在EDA設計中廣泛流行的硬件描述語言,主要用于描述數字系統的結構、行為、功能和接口。除了含有許多具有硬件特征的語句外,VHDL語言的句法、語言形式和描述風格十分類似于一般的計算機高級語言,是目前硬件描述語言中應用最為廣泛的一種。

2018-03-30 16:04:27 21

21 可編程器件門電路數有限的缺點。本文主要介紹的是FPGA開發流程及VHDL基本語法,具體的跟隨小編來了解一下。

2018-05-17 10:44:04 10903

10903

應用VHDL語言設計數字系統,很多設計工作可以在計算機上完成,從而縮短了系統的開發時間,提高了工作效率。本文介紹一種以FPGA為核心,以VHDL為開發工具的數字秒表,并給出源程序和仿真結果。

2019-07-24 08:05:00 4908

4908

本文檔的主要內容詳細介紹的是FPGA視頻教程之FPGA和CPLD與VHDL基礎知識的詳細資料說明。主要的目的是:1.VHDL入門,2.設計單元,3.體系結構建模基礎,4.VHDL邏輯綜合,5.層次化

2019-03-20 14:35:19 9

9 本文檔的主要內容詳細介紹的是FPGA視頻教程之學習FPGA選擇verilog還是vhdl詳細資料說明。

2019-03-22 14:00:07 24

24 本文檔的主要內容詳細介紹的是使用FPGA和VHDL語言進行的搶答器設計資料合集免費下載。

2019-06-03 08:00:00 19

19 在VHDL程序中,實體(ENTITY)和結構體(ARCHITECTURE)這兩個基本結構是必須的,他們可以構成最簡單的VHDL程序。通常,最簡單的VHDL程序結構中還包含另一個最重要的部分,即庫(LIBRARY)和程序包(PACKAGE)。

2020-04-23 15:43:38 5841

5841 用于描述數字系統的結構,行為,功能和接口。除了含有許多具有硬件特征的語句外,VHDL的語言形式和描述風格與句法是十分類似于一般的計算機高級語言。VHDL的程序結構特點是將一項工

2020-04-23 15:58:49 13149

13149 一個VHDL程序代碼包含實體(entity)、結構體(architecture)、配置(configuration)、程序包(package)、庫(library)等。

2020-07-16 08:42:04 3603

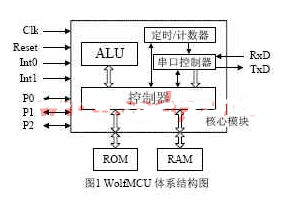

3603 基于以上討論,可以看出ASIP+FPGA設計模式可以從很大程度上解決引言中提到的兩個難題。為了進行更深入的研究,我們對該設計模式進行了嘗試,用VHDL硬件描述語言在FPGA上實現了一個8位微處理器軟

2020-07-28 17:44:49 1009

1009

今天給大家分享一個VHDL和Verilog的工具。很多新手初次學習FPGA都曾遇到過一個問題:是學Verilog OR VHDL?

2020-08-25 09:22:05 7558

7558

本文檔的主要內容詳細介紹的是使用VHDL實現簡易電子琴演奏器設計的工程文件免費下載。

2020-11-02 17:53:48 29

29 本文檔的主要內容詳細介紹的是使用FPGA驅動LCD顯示中文字符年的VHDL程序。

2020-12-18 16:44:14 10

10 本文檔的主要內容詳細介紹的是使用FPGA實現自動售貨機的VHDL程序與仿真資料。

2020-12-21 17:10:00 24

24 本文檔的主要內容詳細介紹的是使用FPGA實現自動售貨機的VHDL程序與仿真資料免費下載。

2020-12-22 17:07:00 15

15 本文檔的主要內容詳細介紹的是使用FPGA實現ADC0809的VHDL控制程序免費下載。

2021-01-18 17:17:00 21

21 本文檔的主要內容詳細介紹的是使用FPGA實現LCD控制的VHDL程序與仿真資料免費下載。

2021-01-18 17:19:08 10

10 本文檔的主要內容詳細介紹的是使用FPGA實現LED控制的VHDL程序與仿真資料免費下載。

2021-01-18 17:32:46 12

12 FPGA Express將VHDL描述轉換并優化為內部門級等效格式。然后針對給定的FPGA技術編譯此格式。

2021-01-21 16:02:09 7

7 基于FPGA的簡易頻譜儀設計與實現

2021-06-16 10:01:36 67

67 Verilog HDL 優點:類似C語言,上手容易,靈活。大小寫敏感。在寫激勵和建模方面有優勢。 缺點:很多錯誤在編譯的時候不能被發現。 VHDL 優點:語法嚴謹,層次結構清晰。 缺點:熟悉時間長

2021-08-20 10:03:43 5391

5391 關于Actel 的FPGA的譯碼器的VHDL源代碼(通信電源技術期刊2020年第14期)-關于Actel 的FPGA的譯碼器的VHDL源代碼。適合感興趣的學習者學習,可以提高自己的能力,大家可以多交流哈

2021-09-16 15:18:01 11

11 一個完整的VHDL程序包括實體(Entity),結構體(Architecture),配置(Configuration),包集合(Package),庫(Library)5個部分。在VHDL程序中,實體

2022-11-09 13:32:25 5989

5989 工作方式; IO串并轉換資源:分析IO資源如何實現串并轉換。 其中第二、三系列是對第一系列中的部分內容進行更進一步的詳細描述。本篇是對于第一個系列——IO資源進行部分描述,共分為幾個章節進行具體闡述。 FPGA IO資源的基本單元架構為一個個 IO tile ,下圖為 IO tile 的結構

2022-12-13 13:20:06 3155

3155 FPGA(現場可編程門陣列)的通用語言主要是指用于描述FPGA內部邏輯結構和行為的硬件描述語言。目前,Verilog HDL和VHDL是兩種最為廣泛使用的FPGA編程語言。

2024-03-15 14:36:34 1313

1313

電子發燒友App

電子發燒友App

評論