基于FPGA的數(shù)據(jù)采集控制模塊設(shè)計

0 引 言

數(shù)據(jù)采集和控制系統(tǒng)是對生產(chǎn)過程或科學(xué)實(shí)驗中各種物理量進(jìn)行實(shí)時采集、測試和反饋控制的

2010-02-08 10:00:28 1809

1809

各位大神,求指導(dǎo)!小弟的項目是這樣的,FPGA開發(fā)板對采集到的視頻數(shù)據(jù)做圖像處理,需要將處理后的視頻數(shù)據(jù),傳輸給ARM,然后讓ARM通過以太網(wǎng)傳輸視頻數(shù)據(jù)。小弟想知道,如何實(shí)現(xiàn)讓FPGA開發(fā)板傳輸視頻數(shù)據(jù)給ARM開發(fā)板???求指導(dǎo)!謝謝

2014-02-26 10:04:25

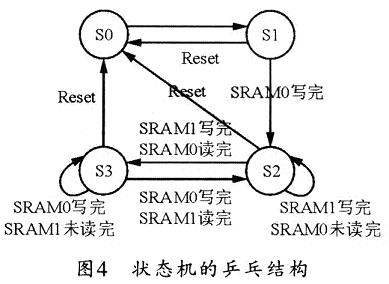

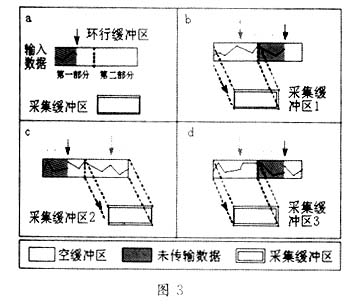

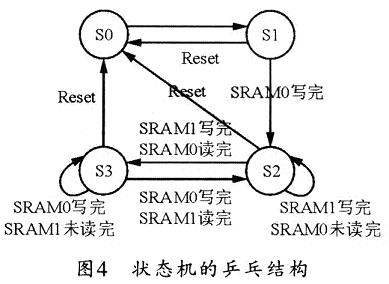

SAA7113 輸出的視頻圖像數(shù)據(jù)通過 8 位總線 VPO 傳輸給 FPGA,FPGA 需要將數(shù)據(jù)保存到 SRAM中。由于 PAL 制電視信號是隔行掃描,分為奇數(shù)場和偶數(shù)場分別傳輸,數(shù)字化以后仍然

2018-12-11 09:47:09

測量目標(biāo)的速度,以及從目標(biāo)回波中獲取的更多有關(guān)目標(biāo)的信息。所謂的雷達(dá)回波系統(tǒng)需要從接收到回波信號中提取、分析測量目標(biāo)的相關(guān)信息。隨著數(shù)據(jù)采集、處理技術(shù)的迅猛發(fā)展,在現(xiàn)代雷達(dá)回波系統(tǒng)的應(yīng)用過程中,高速

2016-07-01 11:47:58

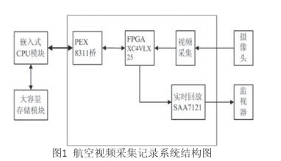

核心,以WinCE為軟件平臺,能實(shí)時、連續(xù)地采集清晰的視頻數(shù)據(jù)。1 系統(tǒng)結(jié)構(gòu)框圖及視頻數(shù)據(jù)采集原理視頻數(shù)據(jù)采集系統(tǒng)結(jié)構(gòu)如圖1所示。從圖1中可以看出。系統(tǒng)由嵌入式微處理器S3C2440、存儲器(包括

2019-08-06 08:30:15

DSP28335+FPGA+AD7606的數(shù)據(jù)采集系統(tǒng),DSP采用TI公司的TMS320F28335,FPGA使用 ALTERA的Cyclone3 的 EP3C5E144C8N在設(shè)計的過程中遇到

2016-07-18 16:53:28

DSP28335+FPGA+AD7606的數(shù)據(jù)采集系統(tǒng),DSP采用TI公司的TMS320F28335,FPGA使用 ALTERA的Cyclone3 的 EP3C5E144C8N在設(shè)計的過程中遇到

2016-07-18 17:13:01

數(shù)字化是很重要的一個環(huán)節(jié)。圖1是差分激光雷達(dá)接收系統(tǒng)的原理圖,圖上只列出了主要部件。下面我們重點(diǎn)介紹一下對數(shù)據(jù)采集卡的要求。激光雷達(dá)通常以20HZ的頻率發(fā)射激光脈沖,要求AD采集卡以10MHZ的速度與發(fā)射

2016-05-23 14:44:42

L138用BT656方式采集TW9910的視頻數(shù)據(jù)(9910只能輸出UYVY格式視頻數(shù)據(jù)),攝像頭視頻制式為PAL制式,BUFFER已獲取到視頻數(shù)據(jù),使用PYUV播放采集數(shù)據(jù)時圖像顯示不正常,不使

2018-06-21 10:28:07

。TMS320C6748為表準(zhǔn)工業(yè)極DSP處理器,主頻高達(dá)456MHZ,具有非常豐富的外設(shè)接口,非常適合智能家居音視頻數(shù)據(jù)采集與處理系統(tǒng)。板子的例程和相關(guān)資源非常豐富,非常適合研究、學(xué)習(xí)。計劃收到板子先

2015-09-10 11:17:52

數(shù)據(jù)獲取系統(tǒng)介紹★ 為何要進(jìn)行遠(yuǎn)程數(shù)據(jù)獲取隨著4G和無線網(wǎng)絡(luò)傳輸技術(shù)的發(fā)展,遠(yuǎn)程數(shù)據(jù)獲取成為可能? 數(shù)據(jù)采集記錄設(shè)備已可以實(shí)現(xiàn)遠(yuǎn)程數(shù)據(jù)傳輸,即將采集、記錄到的車輛數(shù)據(jù)通過互聯(lián)網(wǎng)實(shí)時傳輸?shù)街醒敕?wù)器上

2022-09-26 16:25:26

在使用PCM4204進(jìn)行音頻數(shù)據(jù)采集的過程中,如何把采集到的音頻數(shù)據(jù)通過USB傳輸?shù)絇C上呢?USB控制命令和音頻數(shù)據(jù)如何做,麻煩大佬指點(diǎn)一下,謝謝!

2024-10-15 06:44:49

基于FPGA 的DSP 數(shù)據(jù)采集分析系統(tǒng)設(shè)計

2012-08-20 15:35:41

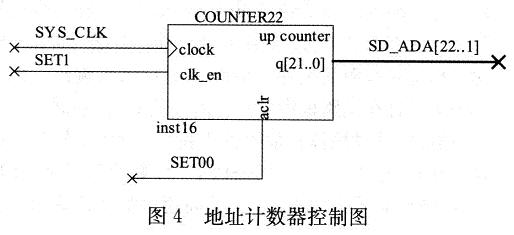

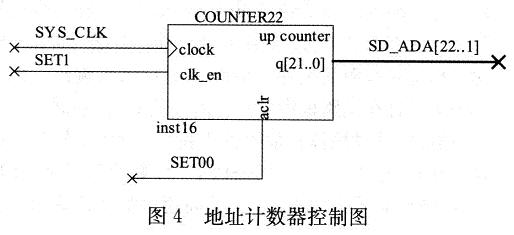

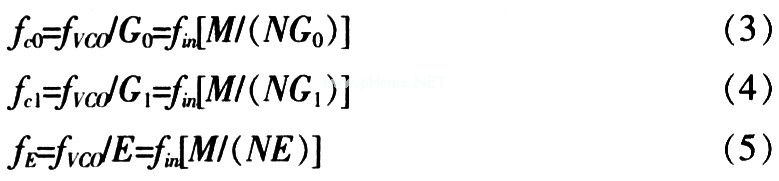

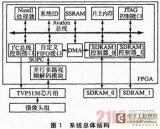

結(jié)果表明,系統(tǒng)結(jié)構(gòu)靈活,性價比高,數(shù)據(jù)采集能力強(qiáng),各項指標(biāo)均達(dá)到了設(shè)計要求,具有廣泛的實(shí)用性。2 數(shù)據(jù)采集系統(tǒng)的實(shí)現(xiàn)2.1 系統(tǒng)硬件設(shè)計2.1.1 主控模塊FPGA在本設(shè)計中,FPGA主控模塊

2018-08-09 14:28:00

基于FPGA+DSP的高速數(shù)據(jù)采集系統(tǒng)設(shè)計

2012-06-27 17:23:53

基于FPGA與SRAM數(shù)據(jù)采集系統(tǒng)設(shè)計中文期刊文章作 者:江麗 肖思其作者機(jī)構(gòu):[1]湖南高速鐵路職業(yè)技術(shù)學(xué)院,湖南衡陽421002出 版 物:《科技資訊》 (科技資訊)年 卷 期:2017年 第

2018-05-09 12:09:43

基于FPGA的數(shù)據(jù)采集系統(tǒng)IEE ... 介紹了數(shù)據(jù)采集系統(tǒng)中以FPGA為處理核心、采用TI公司接口芯片的IEEE1394接口設(shè)計,給出了系統(tǒng)硬件設(shè)計和FPGA邏輯設(shè)計,討論了IEEE1394總線

2012-08-11 15:43:47

設(shè)計高溫環(huán)境下(最高120°)基于FPGA的數(shù)據(jù)采集存儲系統(tǒng),就是通過傳感器采集數(shù)據(jù),通過FPGA來控制,把數(shù)據(jù)存儲到存儲芯片上,回頭可以通過接口讀取數(shù)據(jù)顯示在計算機(jī)上,求大師給我指導(dǎo),我急需整個系統(tǒng)的protel原理圖,請各位幫忙,我將感激不盡。最好有附件畫出整個原理圖,謝謝!

2012-10-29 21:37:12

目前,在數(shù)據(jù)采集系統(tǒng)的硬件設(shè)計方案中,有采用通用單片機(jī)和USB相結(jié)合的方案,也有采用DSP和USB相結(jié)合的方案,前者雖然硬件成本低,但是時鐘頻率較低,難以滿足數(shù)據(jù)采集系統(tǒng)對速度要求;后者雖然可以實(shí)現(xiàn)

2019-09-05 07:22:57

基于FPGA的高速實(shí)時數(shù)據(jù)采集系統(tǒng)設(shè)計

2012-08-20 20:00:14

平臺進(jìn)行開發(fā)實(shí)現(xiàn),實(shí)現(xiàn)由Windows平臺向Linux平臺的轉(zhuǎn)換,對于發(fā)展中國自主知識產(chǎn)權(quán)氣象軟件核心技術(shù), 提高信息安全有著極其重要的意義。本文基于Linux 操作系統(tǒng)(2.6.23內(nèi)核),實(shí)現(xiàn)了天氣雷達(dá)高速數(shù)據(jù)采集及處理,對天氣雷達(dá)系統(tǒng)由Windows平臺向Linux平臺移植具有參考價值。

2020-03-09 08:31:55

你好,我的FPGA接收視頻,視頻格式是1080p@ 60fps,YYY2。這是使用“32位從FIFO同步”傳輸視頻數(shù)據(jù)的唯一方法嗎?32位數(shù)據(jù)格式是什么?(D:7:0]?D [15:8]?D [23∶16]?,D [31:24]?我不知道如何分配我的視頻數(shù)據(jù)謝謝

2019-09-26 13:26:58

高速連續(xù)數(shù)據(jù)采集系統(tǒng)的背景及功能是什么?如何利用FPGA實(shí)現(xiàn)高速連續(xù)數(shù)據(jù)采集系統(tǒng)設(shè)計?FPGA在高速連續(xù)數(shù)據(jù)采集系統(tǒng)中的應(yīng)用有哪些?

2021-04-08 06:19:37

本文給出了基于FPGA高速數(shù)據(jù)采集系統(tǒng)中的輸入輸出接口的實(shí)現(xiàn),介紹了高速傳輸系統(tǒng)中RocketIO設(shè)計以及LVDS接口、LVPECL接口電路結(jié)構(gòu)及連接方式,并在我們設(shè)計的高速數(shù)傳系統(tǒng)中得到應(yīng)用。

2021-04-29 06:04:42

怎么實(shí)現(xiàn)基于WinCE的嵌入式視頻數(shù)據(jù)采集系統(tǒng)設(shè)計?

2021-06-03 06:39:40

我正在學(xué)習(xí)基于FPGA的數(shù)據(jù)采集系統(tǒng)的設(shè)計,請各位大神提供些有關(guān)這方面的資料,最好是Verilog HDL代碼!謝謝!

2015-07-16 09:23:32

`求基于XILINX的FPGA數(shù)據(jù)采集系統(tǒng),感激不盡!`

2015-06-29 22:13:07

綜合考慮到圖像采集系統(tǒng)所要求的實(shí)時性,可靠性,以及FPGA在數(shù)字電路的設(shè)計中的優(yōu)勢,為此本文討論如何利用FPGA設(shè)計基于LVDS的圖像數(shù)據(jù)采集傳輸系統(tǒng)?

2021-04-08 06:48:28

本帖最后由 一只耳朵怪 于 2018-6-21 11:29 編輯

大家好!請教一個問題, AM5728系統(tǒng)是如何通過OpenCL調(diào)用Cortex-M4采集視頻數(shù)據(jù)呢? 視頻數(shù)據(jù)從HDMI Camera輸入進(jìn)來,視頻數(shù)據(jù)為1080p。還請不吝告知! 謝謝大家!

2018-06-21 04:52:31

包括傳感器、信號調(diào)理儀器、信號記錄儀器。前兩者已有專門的廠商研發(fā)。計算機(jī)采集卡是信號記錄儀器中的重要組成部分,主要起AD轉(zhuǎn)換功能。目前主流數(shù)據(jù)采集卡都包含了完整的數(shù)據(jù)采集功能,如NI公司的E系列

2019-05-13 09:40:03

我想利用筆記本同步采集音頻和視頻數(shù)據(jù) 可是不知道為什么音頻數(shù)據(jù)才一次就出錯 視頻沒事 請高手指點(diǎn) 萬分感謝

2012-05-29 20:50:25

高速數(shù)據(jù)采集系統(tǒng)的硬件結(jié)構(gòu)MAX7000系列CPLD及其開發(fā)平臺介紹CPLD在高速數(shù)據(jù)采集系統(tǒng)中的應(yīng)用

2021-04-08 06:11:56

科技有限公司的ADQ14系列高速數(shù)據(jù)采集卡,因其自身采集速度快、數(shù)據(jù)處理能力強(qiáng)、可用戶定制算法開發(fā)等特點(diǎn)贏得了一系列軍工用戶,近期,其在某船舶研究機(jī)構(gòu)研制的船用雷達(dá)系統(tǒng)中,成功擔(dān)任了的雷達(dá)數(shù)據(jù)采集

2016-05-20 11:51:39

不必使用復(fù)雜的信號調(diào)理附件。您可用 8 種可選插入模塊建造緊湊的數(shù)據(jù)記錄儀,全功能數(shù)據(jù)采集系統(tǒng)或低成本的開關(guān)單元。模塊上的螺釘連接可不需要終端接線盒,獨(dú)特的繼電器

2022-07-13 16:02:48

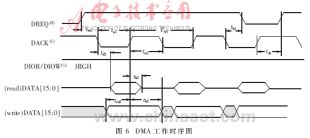

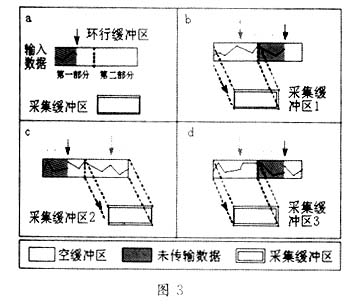

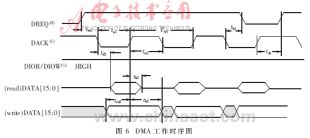

本文提出了一種用于雷達(dá)回波信號采集的高速數(shù)據(jù)采集系統(tǒng)。該系統(tǒng)實(shí)現(xiàn)了對數(shù)十兆赫的回波信號進(jìn)行連續(xù)的采樣和存儲。系統(tǒng)通過FPGA控制數(shù)據(jù)連續(xù)采集、緩沖,通過PCI9056將緩沖區(qū)

2009-08-15 11:45:53 23

23 介紹了一種基于DSP 的MPEG-4 視頻壓縮系統(tǒng)中,利用FPGA 控制視頻數(shù)據(jù)實(shí)時采集并對原始視頻數(shù)據(jù)進(jìn)行預(yù)處理的設(shè)計方案及實(shí)現(xiàn),解決了原始視頻數(shù)據(jù)格式與MPEG-4 壓縮算法不兼容的

2009-08-26 08:57:59 14

14 本文對在FPGA中嵌入Powerpc(hard IP Core),引入linux嵌入式操作系統(tǒng)用來開發(fā)嵌入式系統(tǒng)進(jìn)行了研究,系統(tǒng)實(shí)現(xiàn)了高速數(shù)據(jù)采集、高速視頻數(shù)據(jù)壓縮、實(shí)時視頻數(shù)據(jù)的網(wǎng)絡(luò)傳輸和實(shí)時壓縮圖像

2010-02-24 14:55:25 33

33 不必使用復(fù)雜的信號調(diào)理附件。您可用 8 種可選插入模塊建造緊湊的數(shù)據(jù)記錄儀,全功能數(shù)據(jù)采集系統(tǒng)或低成本的開關(guān)單元。模塊上的螺釘連接可不需要終端接線盒,獨(dú)特的繼電器

2023-12-05 18:02:56

設(shè)計一種基于FPGA的多通道同步數(shù)據(jù)采集存儲系統(tǒng),分為多通道同步數(shù)據(jù)采集模塊和數(shù)據(jù)存儲模塊。系統(tǒng)設(shè)計采用多通道數(shù)據(jù)的同步實(shí)時采集以及壞塊檢測技術(shù)。多通道同步數(shù)據(jù)采集

2010-12-27 15:31:33 70

70 AFE7769EVM:德州儀器數(shù)據(jù)采集開發(fā)模塊詳解在現(xiàn)代數(shù)據(jù)采集和信號處理應(yīng)用中,選擇合適的開發(fā)工具至關(guān)重要。AFE7769EVM 是由 德州儀器(Texas Instruments) 提供的一款數(shù)據(jù)采集

2024-10-06 12:58:48

銀河數(shù)據(jù)采集分析系統(tǒng)——軟件介紹 數(shù)據(jù)采集系統(tǒng)主要是通過以太網(wǎng)對WP4000變頻功率分析儀、DP1000直流功率表、VFE2000數(shù)據(jù)采集儀、EV

2024-10-08 13:33:21

采用FPGA的高速數(shù)據(jù)采集系統(tǒng)

隨著科學(xué)技術(shù)的發(fā)展,數(shù)據(jù)采集技術(shù)進(jìn)入到越來越多的領(lǐng)域。目前,已廣泛應(yīng)用于通信,圖像處理,軍事應(yīng)用,消費(fèi)電子,智能控制等方面

2009-04-20 11:03:13 2320

2320

基于USB2.0與FPGA技術(shù)的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計

基于USB2.0與FPGA技術(shù)的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計

近年來筆記本電腦迅速普及和更新,其中大部分已經(jīng)

2009-04-22 19:56:15 1960

1960

【摘 要】 詳細(xì)介紹了基于計算機(jī)PCI總線大容量雷達(dá)數(shù)據(jù)采集系統(tǒng)的研制和實(shí)現(xiàn)方法。該系統(tǒng)提供了兩路20MHz最高采樣頻率、12位采樣精度的數(shù)據(jù)采集通道。

2009-05-16 19:23:31 1362

1362

基于DSP+FPGA的實(shí)時視頻采集系統(tǒng)設(shè)計

0 引言

圖像是自然生物或人造物理的觀測系統(tǒng)對世界的記錄,是以物理為載體,以介質(zhì)來記錄信息的

2009-12-16 10:20:55 767

767

異步FIFO和PLL在高速雷達(dá)數(shù)據(jù)采集系統(tǒng)中的應(yīng)用

1 引言 隨著雷達(dá)系統(tǒng)中數(shù)字處理技術(shù)的飛速發(fā)展,需要對雷達(dá)回波信號進(jìn)行高速數(shù)據(jù)采集。在嵌入式條

2009-12-22 17:41:08 2646

2646

基于CPLD/FPGA高速數(shù)據(jù)采集系統(tǒng)的設(shè)計

0 引 言 傳統(tǒng)的數(shù)據(jù)采集系統(tǒng)一般采用單片機(jī),系統(tǒng)大多通過PCI總線完成數(shù)據(jù)的傳輸。其缺點(diǎn)是數(shù)學(xué)運(yùn)算能力差;

2010-01-27 09:35:01 791

791

FPGA芯片在高速數(shù)據(jù)采集緩存系統(tǒng)中的應(yīng)用

概 述在高速數(shù)據(jù)采集方面,FPGA有單片機(jī)和DSP無法比擬的優(yōu)勢。FPGA的時鐘頻率高,內(nèi)部時延小,全部控制邏輯都可由硬

2010-03-30 10:51:15 1179

1179

數(shù)據(jù)采集板作為雷達(dá)信號處理系統(tǒng)中的接收前端,必須面對越來越高的要求,為后續(xù)信號處理提供可靠的保證。將數(shù)據(jù)采集板獨(dú)立設(shè)計提高了通用性,降低了系統(tǒng)的研制

2010-07-19 18:52:41 2762

2762 摘要:介紹了視頻采集存儲系統(tǒng)的硬件設(shè)計及主要模塊的數(shù)據(jù)處理流程、系統(tǒng)測試結(jié)果。采集制式為PAL的視頻信。號,經(jīng)過視頻解碼器TVP5150轉(zhuǎn)換為數(shù)字視頻數(shù)據(jù),利用TMS320DM642和CPLD器件及與非門Flash等主要器件實(shí)現(xiàn)了集視頻數(shù)據(jù)采集、以太網(wǎng)傳輸、存儲、壓縮于

2011-02-28 00:59:31 93

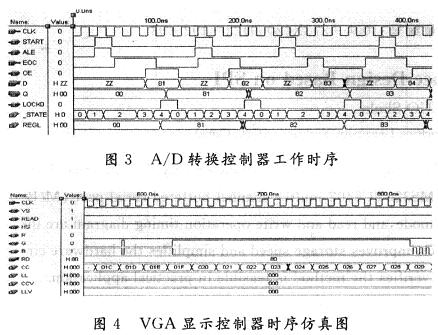

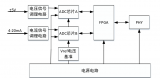

93 針對膜式氧合器測試中多傳感器數(shù)據(jù)采集的特性,設(shè)計了一種醫(yī)用膜式氧合器氧擴(kuò)散滲透率檢測的多路數(shù)據(jù)采集系統(tǒng);系統(tǒng)以FPGA為主控制模塊,對FPGA硬件資源進(jìn)行功能劃分,分別實(shí)現(xiàn)A/D轉(zhuǎn)換控制、FIFO數(shù)據(jù)緩存、時鐘分頻等功能,最后通過USB接口實(shí)現(xiàn)了數(shù)據(jù)傳輸;

2011-03-15 15:16:08 21

21 針對數(shù)據(jù)采集系統(tǒng)有信號形式多樣、實(shí)時傳輸和靈活配置的要求,介紹了一種基于FPGA的數(shù)據(jù)采集和傳輸系統(tǒng),以及系統(tǒng)數(shù)字電路的程序設(shè)計。該系統(tǒng)以現(xiàn)場可編程邏輯陣列(FPGA)作為

2011-09-29 17:31:04 54

54 設(shè)計了一個基于FPGA的數(shù)據(jù)采集系統(tǒng),并用Verilog HDL語言作為描述語言實(shí)現(xiàn)了對TLC0820的采樣控制和FPGA的數(shù)據(jù)處理等過程的控制,以Xilinx ISE 9.1i軟件為平臺,進(jìn)行了設(shè)計輸入、分析與綜合、

2012-05-08 15:17:06 80

80 為了提高大型實(shí)驗設(shè)備的利用率,在此提出利用Matlab、數(shù)據(jù)庫、FPGA和服務(wù)器等軟硬件設(shè)施,實(shí)現(xiàn)遠(yuǎn)程實(shí)驗系統(tǒng)數(shù)據(jù)采集的方案。該方案中設(shè)計了基于FPGA的數(shù)據(jù)采集箱,利用數(shù)據(jù)采集箱將

2012-05-17 09:41:19 2655

2655

FPGA由于集成了超大規(guī)模集成電路和可編程器件的諸多優(yōu)點(diǎn),其在現(xiàn)代工業(yè)生產(chǎn)和科學(xué)研究中的數(shù)據(jù)采集和處理的應(yīng)用越來越廣泛。本文針對SSI接口類傳感器數(shù)據(jù)采集與數(shù)理需求,設(shè)計了以FPGA為核心處理器的多

2015-12-18 15:48:43 138

138 隨著cPCI總線技術(shù)的發(fā)展,cPCI總線逐漸代替了PCI總線、VME總線,成為測控領(lǐng)域中最受人們青睞的總線形式。通過分析PCI總線協(xié)議,理解高頻數(shù)字電路設(shè)計方法和高速數(shù)據(jù)采集原理,本文開發(fā)了基于cPCI接口的高速數(shù)據(jù)采集系統(tǒng)。經(jīng)過綜合測試和現(xiàn)場應(yīng)用驗證表明,采集系統(tǒng)己達(dá)到了要求的性能指標(biāo)。

2016-01-06 11:33:27 21

21 高速數(shù)據(jù)采集系統(tǒng)中的FPGA的設(shè)計,下來看看

2016-05-10 11:24:33 15

15 基于FPGA的AD73360數(shù)據(jù)采集方法

2016-05-10 11:24:33 30

30 基于FPGA的PXI數(shù)據(jù)采集系統(tǒng)設(shè)計,下來看看

2016-05-10 13:45:28 36

36 于FPGA的高速多路數(shù)據(jù)采集系統(tǒng)的設(shè)計。

2016-05-10 13:45:28 41

41 基于FPGA的多通道數(shù)據(jù)采集系統(tǒng)設(shè)計,下來看看。

2016-05-10 13:45:28 64

64 基于FPGA的高速數(shù)據(jù)采集硬件系統(tǒng)設(shè)計.

2016-05-10 17:06:40 48

48 基于FPGA的高速數(shù)據(jù)采集系統(tǒng)接口設(shè)計.

2016-05-10 17:06:40 27

27 基于FPGA的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計,下來看看

2016-05-10 17:06:40 21

21 基于FPGA的數(shù)據(jù)采集及顯示,下來看看。

2016-05-10 17:46:07 30

30 基于FPGA的數(shù)據(jù)采集系統(tǒng)IEEE1394接口設(shè)計

2016-05-10 17:46:07 12

12 基于FPGA的高速數(shù)據(jù)采集系統(tǒng)設(shè)計,用ad芯片和sdram構(gòu)成高速數(shù)據(jù)采集系統(tǒng)。

2016-05-17 09:49:51 35

35 基于FPGA的某型雷達(dá)視頻采集預(yù)處理模塊設(shè)計

2016-08-30 15:10:14 34

34 基于FPGA的新型高速CCD圖像數(shù)據(jù)采集系統(tǒng)

2016-09-22 13:05:38 22

22 SoCFPGA在聲波測井數(shù)據(jù)采集系統(tǒng)中的應(yīng)用_張成暉

2017-03-19 11:41:51 0

0 基于ARM與DSP的聲頻數(shù)據(jù)采集系統(tǒng)設(shè)計

2017-10-20 08:34:12 6

6 隨著雷達(dá)數(shù)據(jù)處理技術(shù)的快速發(fā)展,需要高速采集雷達(dá)回波信號。然而激光雷達(dá)的發(fā)射波及回波信號經(jīng)光電器件轉(zhuǎn)換后,形成的電信號脈寬窄,幅度低,而且背景噪聲大,如采用低速的數(shù)據(jù)采集系統(tǒng)進(jìn)行采集,存在數(shù)據(jù)精度

2017-10-30 16:34:44 11

11 FPGA和UART的MCU總線數(shù)據(jù)采集系統(tǒng)設(shè)計

2017-10-31 15:20:51 8

8 首先介紹了基于FPGA視頻采集系統(tǒng)的整體設(shè)計,對于采集和存儲過程中實(shí)時性和高效性的要求,分別討論了ITU656視頻解碼中需要從采集到的視頻數(shù)據(jù)中提取出有效視頻數(shù)據(jù)流,以及將其調(diào)整為符合VGA顯示

2017-11-17 01:28:55 4742

4742

和處理單元的數(shù)據(jù)吞吐量要求在Gbits/s以上。因此,要實(shí)現(xiàn)一個雷達(dá)數(shù)據(jù)采集和圖像顯示系統(tǒng),對處理器的處理速度要求很高。傳統(tǒng)的雷達(dá)數(shù)據(jù)采集和圖像顯示系統(tǒng)采用的是微處理器+FPGA(或DSP)方案,利用微處理器實(shí)現(xiàn)操作系統(tǒng)、雷達(dá)

2018-02-21 07:45:00 5927

5927 設(shè)計了一種基于FPGA的視頻實(shí)時采集系統(tǒng), 視頻數(shù)據(jù)通過視頻解碼器、雙口RAM、內(nèi)存控制器, 然后存入片外SDRAM中。根據(jù)視頻處理算法的要求和SDRAM的特點(diǎn), 對視頻數(shù)據(jù)的存儲格式及讀寫時序進(jìn)行了優(yōu)化, 提高了系統(tǒng)的數(shù)據(jù)傳輸速率, 能夠滿足后續(xù)視頻處理系統(tǒng)的需要。

2018-10-18 17:25:35 7

7 介紹了1種基于FPGA和DSP的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計和實(shí)現(xiàn),其FPGA采用Altera公司ACEX 1K系列的EPIK50Tcl443器件,DSP芯片采用TI公司TMs320系列

2018-11-07 17:18:24 20

20 存儲系統(tǒng)。產(chǎn)品主要應(yīng)用于雷達(dá),通信,生物醫(yī)學(xué),超聲無損檢測,分布式光纖測試,質(zhì)譜,高能物理,高壓局放監(jiān)控等領(lǐng)域。?????12bit ? 4GSPS ?單通道??? 高速數(shù)據(jù)采集記錄存儲系統(tǒng)10bit

2018-11-13 21:21:34 968

968 持續(xù)不間斷采集記錄數(shù)據(jù)。高速數(shù)據(jù)采集記錄存儲系統(tǒng)已廣泛應(yīng)用于復(fù)雜環(huán)境電磁信號數(shù)據(jù)采集記錄存儲、電子偵察、衛(wèi)星導(dǎo)航、雷達(dá)信號高速數(shù)據(jù)記錄存儲等國防科研領(lǐng)域。?圖三 高速數(shù)據(jù)采集記錄存儲系統(tǒng)MR-HA-4G

2018-11-13 21:27:18 937

937 結(jié)合數(shù)據(jù)采集在往復(fù)式壓縮機(jī)在線監(jiān)測系統(tǒng)中的應(yīng)用, 設(shè)計了以FPGA(現(xiàn)場可編程門陣列)為核心的邏輯控制模塊的多通道數(shù)據(jù)采集系統(tǒng)。整個采集系統(tǒng)可實(shí)現(xiàn)16 路最大工作頻率為100kHz 的模擬信號的采集

2018-12-18 19:09:43 22

22 高速雷達(dá)數(shù)據(jù)采集系統(tǒng)的設(shè)計方法。該系統(tǒng)由FPGA芯片完成各芯片之間的邏輯控制,具有設(shè)計靈活、結(jié)構(gòu)簡單、實(shí)時性高、可靠性高等優(yōu)點(diǎn)。

2018-12-24 15:20:00 21

21 關(guān)鍵詞:PCI , 雷達(dá) , 視頻 , 數(shù)據(jù)采集 PCI總線(Peripheral Component Interconnect)是Intel公司推出的一種高性能32/64位局部總線,最大數(shù)據(jù)

2019-01-28 18:06:01 886

886 數(shù)字圖像處理技術(shù)廣泛地應(yīng)用在信息處理領(lǐng)域,如何高效、靈活地將現(xiàn)實(shí)世界圖像數(shù)字化是信息處理的關(guān)鍵技術(shù)之一。本文基于FPGA技術(shù)設(shè)計了一個高速多路視頻數(shù)據(jù)采集系統(tǒng)。基于Altera Cyclone II

2019-02-11 09:39:26 2549

2549

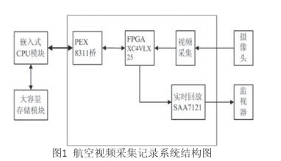

在航空視頻采集記錄系統(tǒng)中,攝像頭把載機(jī)任務(wù)系統(tǒng)的實(shí)時畫面視頻數(shù)據(jù)按預(yù)定格式組幀,通過LVDS信號總線傳輸給視頻采集模塊;經(jīng)過視頻采集模塊對LVDS信號電平進(jìn)行變換處理后,將單端視頻數(shù)字信號送給

2020-04-04 11:07:00 1423

1423

介紹了一種以DSP為核心的圖像系統(tǒng)中,以FPGA為數(shù)據(jù)采集邏輯控制單元,用DSP控制實(shí)現(xiàn)了黑白全電視信號圖象數(shù)據(jù)采集。在介紹了系統(tǒng)組成原理的基礎(chǔ)上,詳細(xì)討論了采集部分的結(jié)構(gòu)和FPGA的控制邏輯

2021-01-26 15:02:00 2

2 為研究脈沖星X射線輻射脈沖信號的特點(diǎn)需要記錄X射線脈沖信號的上升沿時刻與脈沖信號峰值。設(shè)計了基于FPGA的X射線脈沖信號數(shù)據(jù)采集系統(tǒng)。重點(diǎn)介紹了數(shù)據(jù)采集系統(tǒng)的組成、功能及硬件設(shè)計。其中,系統(tǒng)采用11

2021-06-01 09:37:44 17

17 基于LabVIEW的音頻數(shù)據(jù)采集系統(tǒng)設(shè)計.pdf

2021-12-13 09:12:58 65

65 實(shí)驗室數(shù)據(jù)采集 , 視頻數(shù)據(jù)收發(fā)卡 , 信號采集、分析 , PCIe的視頻數(shù)據(jù)卡 , 模擬輸出,存儲

2023-12-22 09:40:16 1011

1011

一、系統(tǒng)總體方案設(shè)計 為了滿足油田增壓站對數(shù)據(jù)采集的需求,我們設(shè)計了一套基于FPGA的多通道數(shù)據(jù)采集與傳輸系統(tǒng)。系統(tǒng)以FPGA作為主控制器,利用外部ADC芯片完成模擬信號的采集,通過以太網(wǎng)實(shí)現(xiàn)與上位

2024-12-09 10:45:02 1306

1306

電子發(fā)燒友App

電子發(fā)燒友App

評論