基于FPGA和DDS的信號源設計

1 引言

直接數字頻率合成DDS(Direct Digital Synthesizer)是基于奈奎斯特抽樣定理理論和現代器件生產技術發展的一種新的頻率合成技

2010-02-21 09:15:21 2106

2106

,這是為了支持掃頻而引入的。利用第二個累加器來提供一個穩定增加的變量。先進DDS可將該變量增加到基本頻率調諧字上,從而獲得一個頻率穩定變化的信號。也可以將其與POW結合以實現相位掃描。或者將其與ASF結合

2018-08-01 07:29:23

FPGA+DA怎么實現調相呢,不是數字調制。就是用一個正弦波的峰值來控制載波的相位,這個要怎么在FPGA中實現呢?希望大神能給個思路,我開始是想調制波直接用DDS IP核生成,然后用起幅值作為地址去查找表,表中存的是載波幅值,然后輸出,但是結果一直不對。

2017-06-29 16:00:24

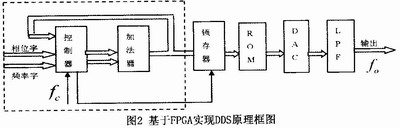

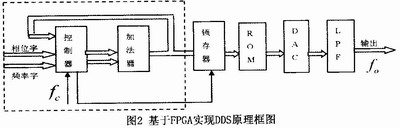

FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法介紹了利用現場可編程邏輯門陣列FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法。重點介紹了DDS技術在FPGA中的實現

2012-08-11 18:10:11

/u/97edd21e883.【相位累加器】相位累加器DDS的第二招就是相位累加器。它能讓來自DDS輸出的信號頻率變得非常靈活。我們用以下的例子來查看其原理,先以一個簡單的代碼開始。[code]reg [10:0] cnt;// 11位計數器always @(posedge clk) cnt

2019-08-02 16:09:06

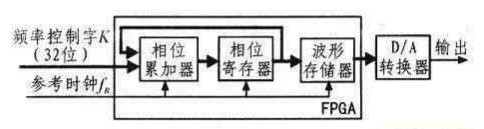

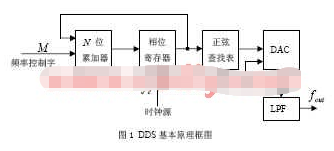

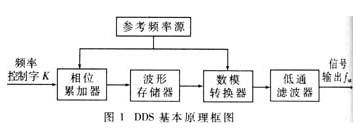

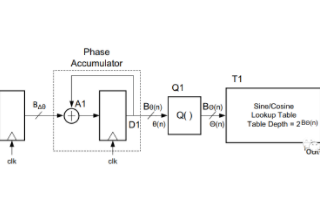

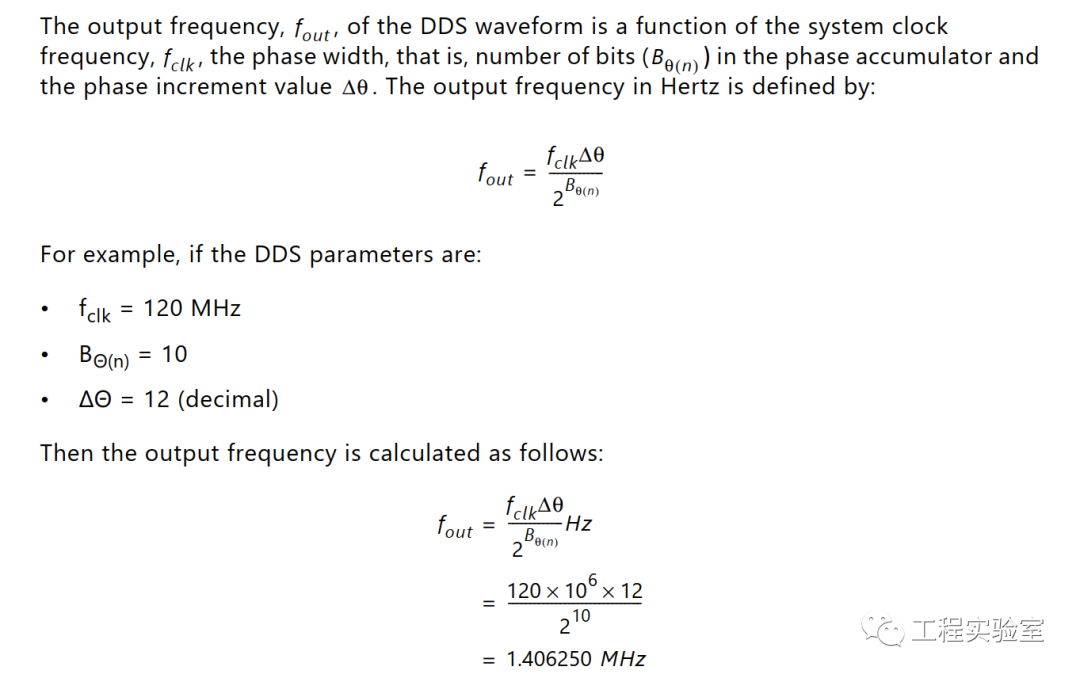

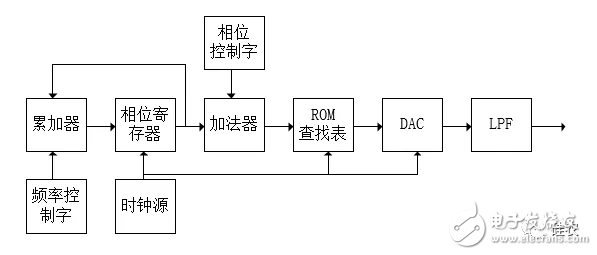

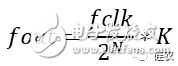

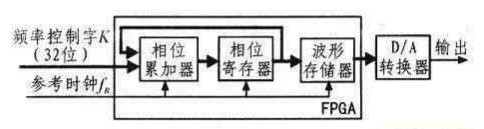

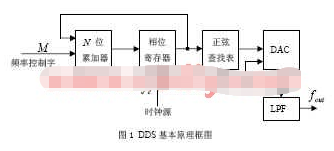

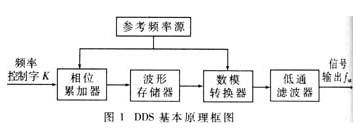

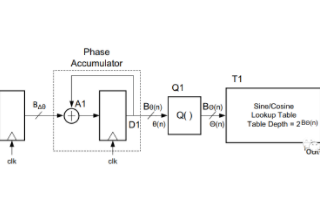

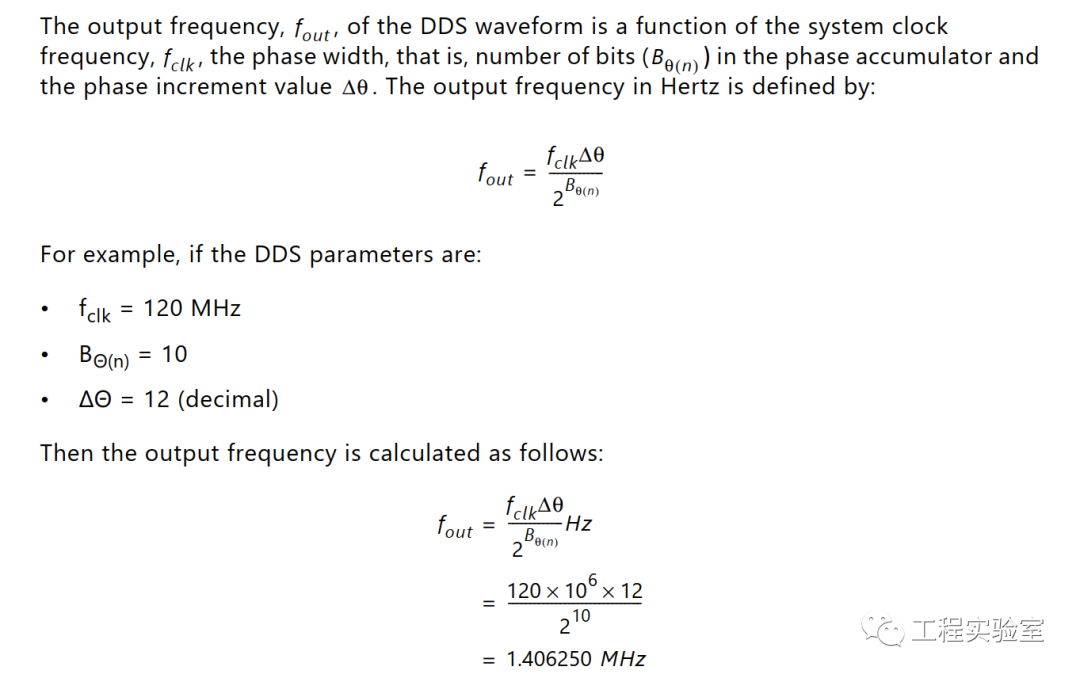

的數字處理理論與方法引入頻率合成技術,通過數/模轉換器將一系列數字量形式的信號轉換成模擬量形式的信號。圖1DDS實現原理DDS的輸入是頻率控制字,其用來控制相位累加器每次增加的相位值,也相當于一個步進值

2020-06-15 11:25:38

IC或FPGA或ASIC中的數字正弦波模式送給DAC來實現。在現代DDS設計中,數字相位誤差可以遠低于DAC誤差,而且DDS相位噪聲測量通常受限于DAC的性能。最簡單和最常見的測試設置如圖3所示。一個

2018-10-17 10:57:21

如題,現在在學mega64,想用它產生一個頻率,占空比可調的方波,要求頻率在5hz到1500hz可調,且分辨率到0.05hz,占空比調節分辨率越小越好,我用它的相位修正模式產生了一個pwm方波,頻率

2013-07-31 23:46:05

發生器。函數信號發生器的實現方法通常是采用分立元件或單片專用集成芯片,但其頻率不高,穩定性較差,且不易調試,開發和使用上都受到較大限制。隨著可編程邏輯器件(FPGA)的不斷發展,直接頻率合成(DDS)技術

2012-05-12 23:01:54

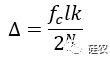

`十一、四通道幅頻相可調DDS信號發生器本文由山東大學研友袁卓貢獻,特此感謝實驗目標實現多通道可調信號發生器實驗平臺芯航線FPGA核心板、ADDA模塊實驗現象實現基于FPGA的多通道可調信號發生器

2017-02-21 09:54:10

任意波形頻率、相位、幅值可調輸出

2017-09-26 15:26:23

最近在使用dds芯片時遇到一個問題,理論上dds輸出信號的最小分辨率是fs/2N,即時鐘頻率/相位累加器大小,通過改變控制字M的大小就可以得到想要的頻率,那么假設使用ad9833,時鐘頻率25MHz

2018-08-03 07:56:59

直接數字頻率合成(DDS)在過去十年受到了頻率合成器設計工程師極大的歡迎,它被認為是一種具有低相位噪聲和優良雜散性能的靈活的頻率源,基于DDS的頻率合成器在許多應用中能比基于鎖相環(PLL)頻率

2019-07-08 07:26:17

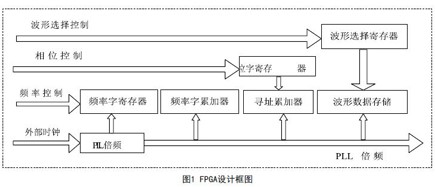

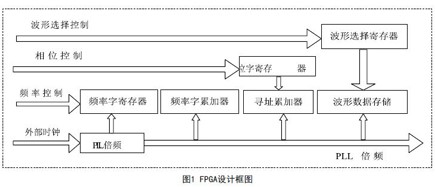

基于FPGA 的DDS 調頻信號的研究與實現

2012-08-17 11:41:11

數據通信中應用廣泛。DDS頻率合成技術通過頻率控制字、相位控制字及參考時鐘的控制來實現輸出信號的調頻調相,并且輸出信號具有頻率轉換快、頻率分辨率高和相位噪聲低等優點。綜合上述特點,設計運用PCI9054

2019-07-18 06:35:45

FPGA數字信號處理——基于FPGA和高速DAC的DDS設計與頻率調制(一)——X現如今,隨著高速模數-數模轉換技術和FPGA的發展。FPGA的高速性、并行性、高數據吞吐量與高速數模-模數轉換技術

2021-07-23 08:06:59

FPGA dds的全套設計資料分享給51hei的朋友們,有需要可以下載學習。 下面是DDS頻率合成器視頻教程內容截圖(代碼講解): 部分源程序如下: `timescale 1ns / 1ps

2018-07-03 06:06:17

求一個基于FPGA的DDS信號發生器設計,最好有DA模塊和相位累加器模塊的代碼。

2019-03-18 22:09:03

本帖最后由 kandy286 于 2013-11-8 00:33 編輯

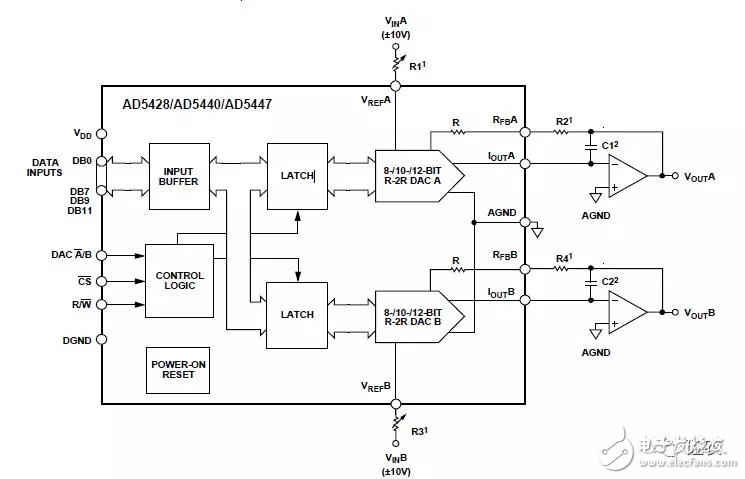

剛學FPGA,用FPGA+DAC設計的DDS,已實現調頻,調相功能。可是調幅該怎么控制呢?有種方案是改變DAC的參考電壓

2013-11-08 00:32:04

中優勢明顯。FPGA資源豐富、速度快、開發方便快捷,因此在高速數據通信中應用廣泛。DDS頻率合成技術通過頻率控制字、相位控制字及參考時鐘的控制來實現輸出信號的調頻調相,并且輸出信號具有頻率轉換快、頻率

2012-09-06 12:40:54

FPGA 合成DDS是一個較好的解決方法,具有良好的實用性和靈活性。2.正弦直接數字頻率合成器設計原理合成器由頻率控制字N,相位控制字M分別控制輸出正弦波的頻率與相位。其中相位累 加器為合成器的關鍵

2018-10-18 16:29:13

基于labview和fpga的信號發生器要求:【1】正弦波、方波、鋸齒波、三角波。【2】頻率、幅值、相位可調,調節步進值:頻率0.1,幅值0.1,相位1;【3】頻率最高:20k;峰值最高:3.3

2022-01-18 07:35:42

通過對平均值相位差計原理的分析和程序設計、仿真,用FPGA芯片實現了一個高精度、寬頻率范圍的相位差計。該測量方法的最大優點是系統電路簡單,不需要鎖相環,占用的邏輯資源少,選用低端FPGA芯片完全能滿足要求,大大提高了被測信號的頻率范圍及測量精度,具有一定的應用價值。

2021-05-10 06:04:50

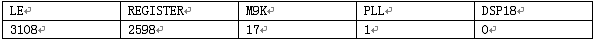

介紹了利用現場可編程邏輯門陣列FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法。重點介紹了DDS技術在FPGA中的實現方法,給出了采用ALTERA公司的ACEX系列FPGA芯片EP1K30TC進行直接數字頻率合成的VHDL源程序。

2021-04-30 06:29:00

地重新定位輸出相位(我們某些產品的步進小到0.0055度)。該功能的數字性質使它能完美重復,極為可靠。能夠切換多個相位偏移字(POW)選項以實現相移鍵控(PSK)。能夠讓兩個依賴同一系統時鐘源的DDS

2018-10-31 10:53:03

現今設計一個系統,需要使用到一個實時相位校準的參考,大概需要滿足1°的信號用于FPGA,請問有哪類DDS可以滿足該要求,不勝感激!

2018-10-10 15:31:27

介紹了DDS的發展歷史及其兩種實現方法的特點,論述了DDS的基本原理,并提出一種基于FPGA的DDS信號發生器的設計方法,使DDS信號發生器具有調頻、調相的功能,最后對其性能進行了分析。實驗表明該系統具有設計合理、可靠性高、結構簡單等特點,具有很好的實用價值。

2021-05-11 06:58:58

。與傳統的頻率合成器相比,DDS具有低成本、低功耗、高分辨率和快速轉換時間等優點,廣泛使用在電信與電子儀器領域,是實現設備全數字化的一個關鍵技術。 ——國外生產DDS芯片的公司較多,目前國內

2012-06-20 15:51:30

頻率合成有哪幾種方法?如何采用相位累加控制實現DDS?如何采用比例乘法器控制實現DDS?

2021-05-07 06:06:58

2.設計一個DDS信號發生器,能夠產生三角波,要求頻率、相位可調。設系統時鐘為40MHz。設計參數: (1) 頻率分辨率為312.5KHz。(2) 頻率兩檔可調,分別為1250KHz、2500KHz

2013-07-04 17:03:28

1.1.1 概述 學習了明德揚至簡設計法和明德揚設計規范,本人設計了一個基于FPGA的可調頻調相而且可以輸出不同波形的DDS信號發生器。該信號發生器實現了通過按鍵控制輸出不同類型的波形,并可以通過按鍵

2020-03-02 11:15:28

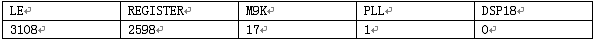

Optimize10(速度),并設定Global Project Logic Synthesis Style為FAST,經寄存器性能分析最高頻率達到100MHz以上。用FPGA實現的DDS能工用在如此之高的頻率主要

2011-07-13 14:13:56

想要使用DDS芯片實現兩個或多個不同頻率(幅度相位相同)信號的混合,DDS能直接實現嗎?還是需要混頻器來實現?DDS芯片單個通道能實現兩個或多個頻率疊加嗎?DDS線性掃描的作用是?

2018-09-20 14:45:30

西安交通大學電信學院 周俊峰 陳濤摘要:介紹了Altera公司的即FPGA器件ACEXEPlK50的主要特點,給出了由ACEXEPlK50實現直接數字頻率合成的工作原理、設計思路、電路結構和改進優化

2019-06-18 06:05:34

通過提取數字調相信號的特征,實現對不同數字調相信號的識別。由于已調信號的初相反映了不同調相信號的特征,提出從瞬時相位中提取初相參數實現數字調相信號識別的基本方

2009-04-11 09:32:16 31

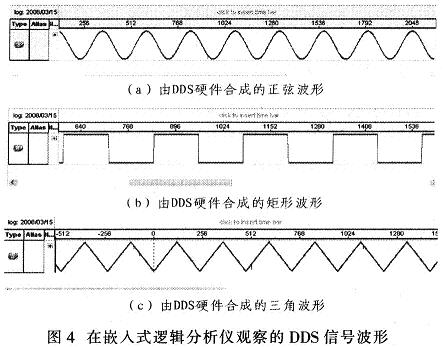

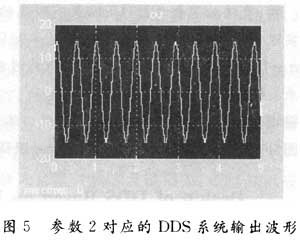

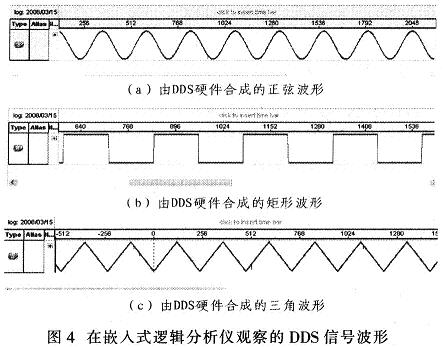

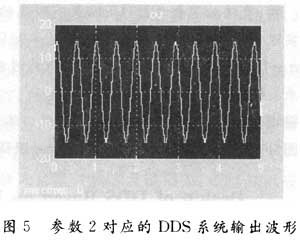

31 本文從DDS 基本原理出發,利用FPGA 來實現DDS 調頻信號的產生,重點介紹了其原理和電路設計,并給出了FPGA 設計的仿真和實驗,實驗結果表明該設計是行之有效的。直接數字頻率

2009-06-26 17:29:09 72

72 基于PLD及FPGA的頻率與相位測量系統設計與實現:摘 要:本測量系統由頻率相位測量儀和DDS 雙路移相信號發生器兩部分組成。頻率相位測量由Altera EPM7128S84 CPLD 完成,雙路移相信號

2009-09-25 15:50:03 31

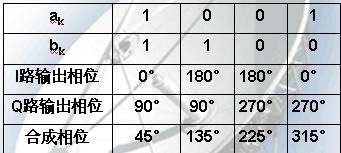

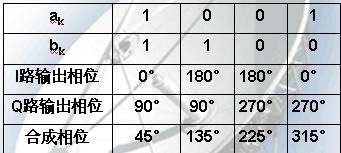

31 提出了一種基于FPGA 實現QPSK 調制器的方法。以FPGA 實現DDS,通過對DDS 信號輸出相位的控制實現調相。仿真結果表明方案是可行的。

2009-12-18 11:57:08 66

66 基于FPGA的DDS信號源設計與實現

利用DDS和 FPGA 技術設計一種信號發生器.介紹了該信號發生器的工作原理、 設計思路及實現方法.在 FPGA 器件上實現了基于 DDS技

2010-02-11 08:48:05 228

228 雜散特性限制著直接數字頻率合成(DDS)技術的應用和發展,其中相位舍位、幅度量化和DAC的非理想特性等是影響DDS輸出頻譜質量的主要雜散源。文中主要研究相位舍位對DDS輸出頻

2010-10-20 16:35:31 28

28 相位噪聲是制約DDS用于高穩定頻率源的的關鍵指標。文中定量給出了DDS內部相位截斷誤差、幅度量化誤差、DAC以及參考時鐘源對相位噪聲的影響,并著重分析了DDS外圍電路對相位

2010-10-20 16:36:17 26

26 提出了一種基于DDS (Direct Digital Synthesize) AD9850的頻率、相位、幅值均可調節的正弦信號發生器。該正弦信號發生器采用AT89S52單片機為控制器,D/A轉換器TLC5615與乘法器AD534相結合,實

2010-12-16 16:14:38 0

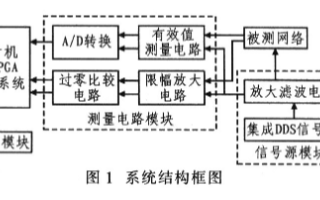

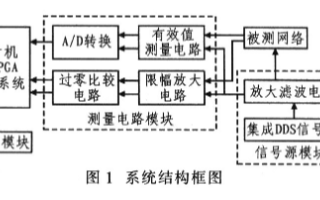

0 摘要:介紹基于89S51單片機和FPGA的頻率特性測試儀的設計。該系統設計利用DDS原理由FPGA經D/A轉換產生掃頻信號,再經待測網絡實現峰值檢測和相位檢測,從而完成了待測網絡幅頻和

2010-12-19 23:01:41 55

55 摘要:為了調節兩路相同頻率正弦信號之間的相位差,采用DDS技術設計了相位關系可調的雙通道信號發生器。該信號發生器的輸出頻率范圍為0Hz~150MHz,頻率分辨率

2006-03-24 13:14:51 2423

2423

四進制調相的原理

四相絕對調相(4BPSK):雙比特碼元ak ,bk與載波相位的關

2008-10-21 13:04:57 2332

2332

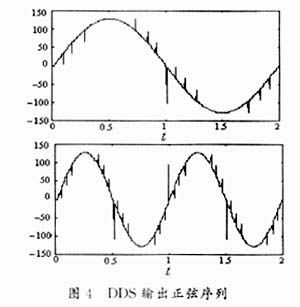

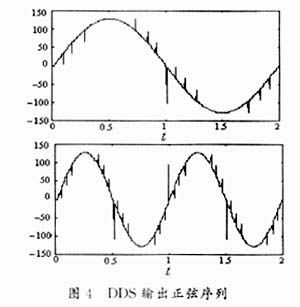

【摘 要】 描述了直接數字頻率合成器(DDS)的原理和特點,并給出了用FPGA實現DDS的方法及仿真結果。 關鍵詞:直接數

2009-05-11 19:52:15 1169

1169

摘要: 介紹了利用現場可編程邏輯門陣列FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法。重點介紹了DDS技術在FPGA中的實現方法,給出了采用ALTERA公

2009-06-20 14:14:36 989

989

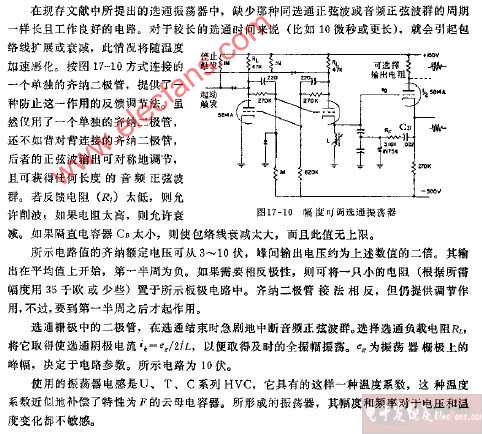

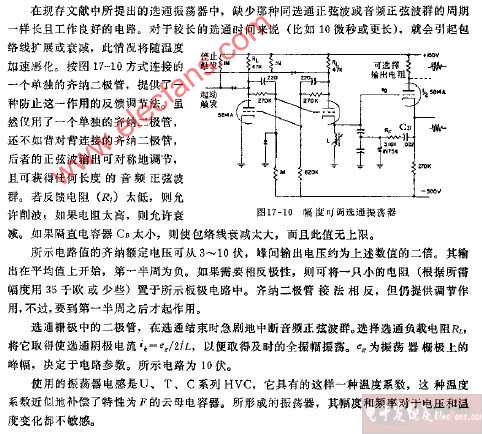

可調相位鎖定的選通振蕩器電路圖

2009-07-03 13:04:34 694

694

基于DSP Builder的DDS設計及其FPGA實現

直接數字合成器,是采用數字技術的一種新型頻率合成技術,他通過控制頻率、相位增量的步長,產生各種不同頻率的信號。他具

2010-01-14 09:43:55 1753

1753

在低成本FPGA中實現動態相位調整

在FPGA中,動態相位調整(DPA)主要是實現LVDS接口接收時對時鐘和數據通道的相位補償,以達到正確接收的目的。ALTERA

2010-03-25 11:45:07 3072

3072

直接數字頻率合成技術(Direct Digital Synthesis,DDS)是一種從相位概念出發直接合成所需要的波形的新的全數字頻率合成

2010-12-01 09:44:21 6826

6826

針對高性能DDS芯片AD9858設計寬帶 頻率合成器 , 分析DDS的工作原理,給出寬帶頻率合成器的原理框圖和實現過程,并對軟件控制流程進行了詳細說明,結合理論對系統的相位噪聲和雜散

2011-06-22 10:49:03 51

51 文中提出一種基于FPGA的DDS信號發生器。信號發生電路采用直接數字頻率合成技術,即DDS(Direct Digital Frequency Synth-esis)。它是以全數字技術,從相位概念出發,直接合成所需波形的一種新的

2011-07-16 10:24:22 2342

2342

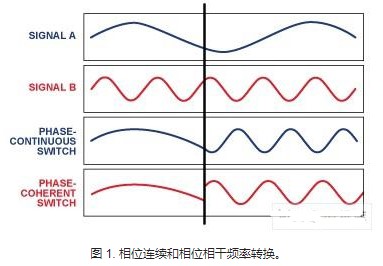

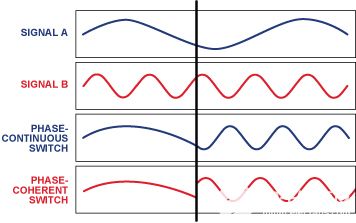

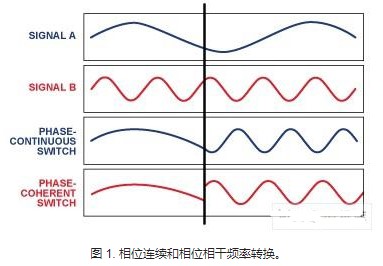

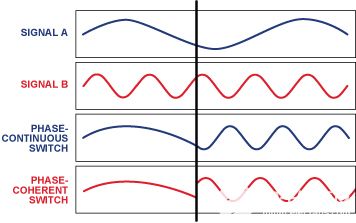

在傳統的 FSK 調制方式中, 兩個載波頻率轉換期間, 已調信號存在相位和頻率突變, 造成系統頻帶利用率不高和信號頻譜衰減太慢。用DDS 進行標準FSK 調制, 可使其相位連續, 但由于存在頻

2011-08-04 15:16:57 72

72 直接數字頻率合成器(DDS) 相位截斷誤差序列是DDS 輸出信號誤差的主要來源,很有必要對DDS 相位截斷誤差序列的譜進行研究。文獻[1 ]提出了DDS 相位截斷雜散譜的精確分析方法,該文對DDS

2011-08-29 16:41:52 21

21 實現了一種基于單片機+DDS可編程低噪聲頻率源,輸出信號范圍46.5~75 MHz。實驗結果表明,該頻率源具有頻率分辨率高、相位噪聲低等優點,滿足短波射頻通信系統對頻率源的設計要求。

2011-11-30 17:04:36 61

61 首先介紹了采用直接數字頻率合成(DDS)技術的正弦信號發生器的基本原理和采用FPGA實現DDS信號發生器的基本方法,然后結合DDS的原理分析了采用DDS方法實現的正弦信號發生器的優缺點

2012-11-26 16:23:32 49

49 基于DAC芯片的DDS,頻率通過按鍵可調,有興趣的同學可以下載學習

2016-04-27 15:51:58 19

19 利用現場可編程門陣列(FPGA)設計并實現直接數字頻率合成器(DDS)。結合DDS 的結構和原理,給出系統設計方法,并推導得到參考頻率與輸出頻率間的關系。DDS 具有高穩定度,高分辨率和高轉換速度,同時利用Altera 公司FPGA 內的Nios 軟核設置和顯示輸出頻率,方便且集成度高。

2016-04-01 16:14:19 28

28 多路同步數字調相信號源一般采用單片機和多片專用DDS芯片配合實現。該技術同步實現復雜,成本高。給出了一種基于FPGA的多路同步信號源的設計方法,通過VHDL語言硬件編程實現了基于單片FPGA

2016-05-27 13:47:49 9190

9190

DDS是直接數字式頻率合成器(Direct Digital Synthesizer)的英文縮寫,是一項關鍵的數字化技術。與傳統的頻率合成器相比,DDS具有低成本、低功耗、高分辨率和快速轉換時間等優點

2017-09-20 09:17:29 9870

9870 和仿真,從仿真和測試結果看,該頻率合成器達到了設計目標。該頻率合成器的輸出頻率范圍為 594~999 MHz,頻率步進為5 Hz,相位噪聲為-91dBc。 DDS的參考信號由晶振產生,其頻率為fref。DDS輸出的信號頻率為fDDS,頻率值由頻率控制字(FTW)控制。鎖相環(PLL)的參考

2017-10-27 17:54:21 10

10 介紹了直接數字頻率合成(DDS)的結構和原理,并將DDS技術應用于短波射頻通信頻率源中。實現了一種基于單片機+DDS可編程低噪聲頻率源,輸出信號范圍46.5~75 MHz.實驗結果表明,該頻率源具有

2017-11-08 14:39:29 19

19 直接數字頻率合成器(DDS)技術,是根據相位的概念出發直接合成所需的波形的一種 新的頻率合成原理,是一種把一系列數字形式的信號通過DAC轉換成模擬形式信號合成技術。具有頻率切換速度快,很容易提高頻率

2017-11-23 11:28:45 2297

2297 DDS是從相位的概念直接合成所需波形的一種頻率合成技術。不僅可以產生不同頻率的正弦波,而且可以控制波形的初始相位。本文為大家介紹基于Verilog實現的DDS任意波形發生器。

2018-01-08 11:58:19 7098

7098

常見的單通道直接數字頻率合成器(DDS)可產生如圖1所示的相位連續頻率轉換。但在相干脈沖多普勒雷達和用于醫療和材料分析的NMR/MRI波譜等應用中,相位相干轉換是首選。本文說明如何配置AD9958/AD9959多通道DDS,通過疊加DDS輸出實現穩定的相位相干頻移鍵控(FSK)調制器。

2019-06-12 08:02:00 12061

12061

DDS頻率合成器具有頻率分辨率高,輸出頻點多,可達2N個頻點(假設DDS相位累加器的字長是N);頻率切換速度快,可達us量級;頻率切換時相位連續的優點,可以輸出寬帶正交信號,其輸出相位噪聲低,對參考頻率源的相位噪聲有改善作用;可以產生任意波形;全數字化實現,便于集成,體積小,重量輕。

2019-04-24 08:30:00 3919

3919

直接數字頻率合成DDS(Direct Digital Synthesizer)是基于奈奎斯特抽樣定理理論和現代器件生產技術發展的一種新的頻率合成技術。與第二代基于鎖相環頻率合成技術相比,DDS具有

2019-04-19 07:50:00 6652

6652

DDS( Direct Digital Sy nthesis) 的概念由美國學者J. T ier ncy、C. M. Rader 和B. Gold 在1971 年提出。該技術是從相位的概念進行頻率

2018-10-07 11:34:34 12576

12576 針對信號發生器對輸出頻率精度高和幅值可調的要求,采用直接數字頻率合成(DDS)技術,提出一種基于FPGA的幅值、頻率均可調的、高分辨率、高穩定度的信號發生器設計方案。采用AT89S52單片機為控制器

2018-11-06 19:35:28 21

21 本視頻將首先介紹是DDS的優缺點,然后是DDS頻率合成的基本原理,相位噪聲和雜散,系統時鐘的實現,產品介紹,最后是在線仿真工具ADIsimDDS。

2019-07-29 06:01:00 6469

6469 直接數據頻率合成器(DDS)因能產生頻率捷變且殘留相位噪聲性能卓越而著稱。另外,多數用戶都很清楚DDS輸出頻譜中存在的雜散噪聲,比如相位截斷雜散以及與相位-幅度轉換過程相關的雜散等。此類雜散是實際DDS設計中的 有限相位和幅度分辨率造成的結果。

2019-11-14 17:10:08 6715

6715

在電路測試中。常常需要測試頻率特性。電路的頻率特性體現了放大器的放大性能與輸入信號頻率之間的關系。頻率特性測試儀是顯示被測電路幅頻、相頻特性曲線的測量儀器。在此,采用集成的直接數字合成器(DDS)AD985l,現場可編程門陣列(FPGA)及外圍測量電路設計了一個頻率特性測試儀。

2020-08-05 15:01:59 1837

1837

直接數字頻率合成(Direct Digital Frequency Synthesis)是從相位概念出發直接合成所需波形的一種新的頻率合成技術。目前各大芯片制造廠商都相繼推出采用先進的CMOS工藝

2020-08-07 17:59:22 1759

1759

實現基于 FPGA 的多通道可調信號發生器,其中頻率、相位以及幅值均可通過 PC 端串口發送數據對應調節,并可實現 4 路信號的同步。

2020-08-13 08:00:00 30

30 本文檔的主要內容詳細介紹的是DDS的FPGA實現電路原理圖免費下載。

2020-10-22 12:07:17 29

29 本文討論了基于FPGA芯片的直接數字頻率合成器(DDS)的設計方法。因為DDS 的實現依賴于高速、高性能的數字器件,使用現場可編程器件FPGA,利用其高速、高性能及可重構性的特性,就能根據需要方便地實現各種不同頻率的信號輸出。

2021-03-02 17:11:32 36

36 和載波相位估計.采用該方案,可縮短或完全去除傳統的采用突發模式傳輸的通信系統訓練序列中用于載波頻率估計的部分,有效地提高時分多址系統的頻譜利用率.在FPGA 平臺上對該方案做了硬件實現,綜合結果表明其最大工作時鐘頻率

2021-03-10 17:13:00 15

15 AN-1396: 如何預測直接數字頻率合成器(DDS)輸出頻譜中主相位截斷雜散的頻率和幅度

2021-03-21 00:44:05 2

2 革命。DDS具有相對帶寬很寬、頻率捷變速度快、頻率分辨率高、輸出相位連續、可輸出寬帶的正交信號、可編程、全數字化和便于集成等優越性能。

2021-05-20 11:10:11 8349

8349

基于FPGA的DDS設計方案1 DDS技術簡介隨著電子技術的不斷發展,傳統的頻率合成技術逐漸不能滿足人們對于頻率轉換速度、頻率分辨率等方面的追求,直接數字頻率合成技術應運而生。 直接數字頻率合成技術

2021-06-10 17:54:47 3354

3354

利用DDS IP實現線性調頻信號1 DDS技術簡介隨著電子技術的不斷發展,傳統的頻率合成技術逐漸不能滿足人們對于頻率轉換速度、頻率分辨率等方面的追求,直接數字頻率合成技術應運而生。

2021-07-02 10:27:28 8770

8770

FPGA實現,按鍵控制,四個按鍵實現波形轉換(三角波,正弦波,方波),頻率可調,電壓可調。

2023-08-07 11:47:04 3

3 DDS基于FPGA的DDSSPI系統結構功能實現:在SPI接口下掛接上DDS模塊,通過單片機向FPGA發送頻率字實現任意頻率正弦波的波形,并通過DAC模塊輸出單片機部分通過按鍵輸入待產生的信號頻率

2021-12-01 17:36:17 10

10 多通道DDS幾乎消除了同步多個單通道器件時遇到的通道間溫度和時序問題。多通道DDS輸出雖然獨立,但共享相同的系統時鐘,因此與多個單通道器件的輸出相比,它們能夠更好地跟蹤溫度和電源偏差。因此,多通道DDS更適合在求和輸出處產生相位相干頻率轉換。

2023-01-30 11:33:43 2563

2563

DDS,Director Digital Synthesis,直接頻率合成技術,是指通過固定頻率的參考時鐘(采樣時鐘)生成指定頻率的正余弦信號。采用FPGA配合DAC芯片,可以實現頻率、相位可調的模擬信號用于一些特定的領域。

2023-08-22 16:30:24 9015

9015

電子發燒友網站提供《基于FPGA 的DDS正弦信號發生器的設計和實現.pdf》資料免費下載

2024-03-24 09:34:50 10

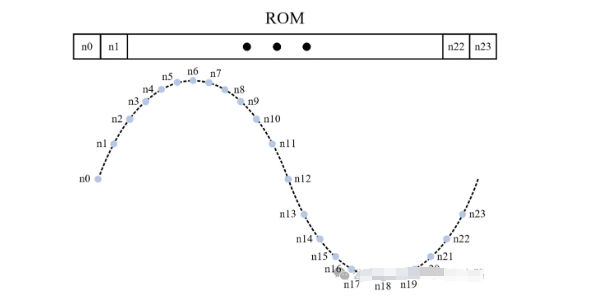

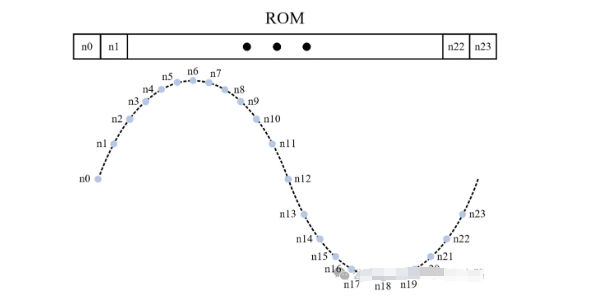

10 系統時鐘,以產生所需的頻率。DDS系統的核心部件包括相位累加器、波形存儲器(ROM查詢表)、數模轉換器(DAC)和低通濾波器。其工作原理可以概括為:在每個時鐘周期,相位累加器根據頻率控制字累加相位值,累加的結果作為地址去查詢波形存儲器中的波形數據,然后將波形數據通過

2024-10-06 15:27:00 3309

3309

等優點。 一、DDS數字頻率合成原理 DDS技術的基本思想是通過控制相位的變化速度來直接產生各種頻率的信號。具體來說,DDS系統主要由相位累加器、相位調制器、波形數據表ROM(只讀存儲器)、數模轉換器(DAC)和低通濾波器(LPF)等部分組成。 相位累加器 :相位累加器是

2024-10-06 15:33:00 2448

2448 在調相(Phase Modulation, PM)過程中, 相位偏移量與調制信號的幅度成正比 。調相是一種將低頻信號的幅度變化映射到高頻載波信號的相位變化上的調制方式。在調相過程中,載波的幅度和頻率

2024-09-11 14:34:26 2062

2062 標題中所提到的DDS,我感覺這兩個放一起也可以,因為DDS的核心思想就是使用的相位累加器。那么這玩意兒的作用是啥?簡單來說就是在FPGA工作主頻之下,可以生成任意頻率的周期信號出來。

2025-05-16 13:56:12 967

967

電子發燒友App

電子發燒友App

評論