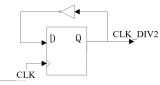

分頻器是數字系統設計中的基本電路,根據不同設計的需要,我們會遇到偶數分頻、奇數分頻、半整數分頻等,有時要求等占空比,有時要求非等占空比。在同一個設計中有

2010-09-03 17:04:20 2861

2861

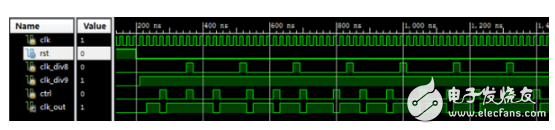

本文首先介紹了各種分頻器的實現原理,并在FPGA開發平臺上通過VHDL文本輸入和原理圖輸入相結合的方式,編程給出了仿真結果。最后通過對各種分頻的分析,利用層次化設計思想,綜合設計出了一種基于FPGA的通用數控分頻器,通過對可控端口的調節就能夠實現不同倍數及占空比的分頻器。

2015-05-07 09:43:16 5706

5706

本文主要帶領大家來了解一下分頻器的計算和調整,首先來了解一下分頻器原理及是分頻點,其次詳細了解分頻器計算的順序以及調整方法。

2018-05-29 09:59:00 137861

137861

70MHz的時候,只改變AD9912的輸出,HMC833寄存器不改變。 現在遇到的問題如下: 1.在低頻段(1.5GHz內)有一大片鑒相頻率整數倍的雜散信號存在,雜散信號與主信號間的差距大概在

2019-02-22 12:27:30

LABVIEW諧波處理模塊中的諧波失真分析只能分析諧波(整數倍的),有沒有哪個模塊可以分析間諧波(非整數倍的)。。。。。。。。。。。。。。。。。。。。或者有沒有測量(間諧波)的模型。。。。。跪求

2016-02-29 17:24:55

調試發現每一次點擊X-Y的值都不一樣,但是會小于1000.這是因為前面板右邊的毫秒計時器出現的數字到下一個1000的整數倍的時候還差598毫秒,所以該次定時時間為598.那么怎樣讓“等待下一個整數倍

2018-06-30 20:28:02

關于 USB3014 寫入 1024 字節或其整數倍的問題,我了解到以下信息:

文檔中提到,如果外部主設備始終寫入滿數據包(如 1024 字節或其整數倍),則無需使用 PKTEND# 信號

2025-07-28 08:28:57

詞匯誤導大家。首先我們參考LabVIEW幫助當中對這兩個函數的解釋。等待:等待指定長度的毫秒數,并返回毫秒計時器的值。連線0至毫秒計時值輸入,可迫使當前線程放 棄對CPU的控制。等待下一個整數倍毫秒:等待

2015-04-13 10:49:54

為什么ME909無法發送TCP大小為64的整數倍呢?如何去解決?

2022-02-14 06:39:30

大家好,問一個問題,在做一個測介電常數的系統,需要先測得電容,下午測試了一下雜散電容,然后對信號做頻譜分析發現里面的噪聲有工頻干擾,還有是信號頻率整數倍的噪聲,比如我的有用信號時100Hz的話,夾雜的噪聲有200、300、400Hz....請問什么情況下會有這類的噪聲產生,如何有效地去消除。謝謝。

2016-04-11 19:48:19

分頻器是FPGA設計中使用頻率非常高的基本設計之一,盡管在目前大部分設計中,廣泛使用芯片廠家集成的鎖相環資源,如賽靈思(Xilinx)的DLL.來進行時鐘的分頻,倍頻以及相移。但是對于時鐘要求不高

2019-06-14 06:30:00

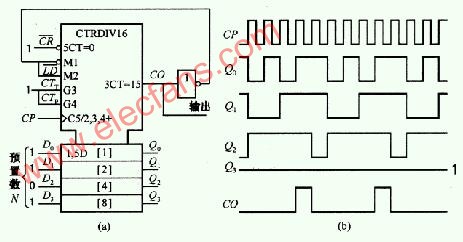

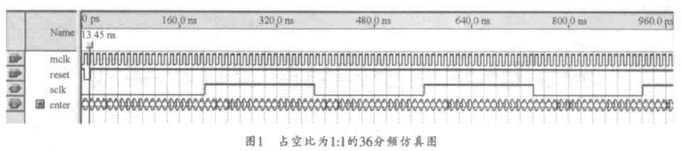

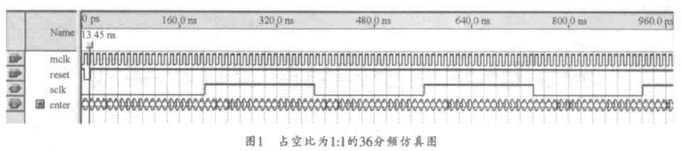

基于FPGACPLD的占空比為1∶n的n分頻器的設計

2017-09-30 09:11:08

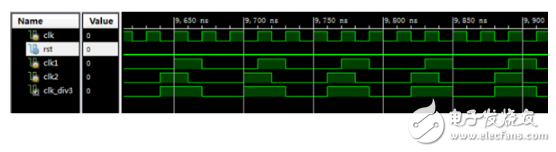

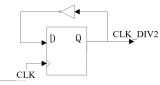

這種方式只消耗不多的邏輯單元就可以達到對時鐘的操作目的。2、整數倍分頻器的設計2.1 偶數倍分頻 偶數倍分頻器的實現非常簡單,只需要一個計數器進行計數就能實現。如需要N分頻器(N為偶數),就可以由待分頻

2014-06-19 16:15:28

【摘要】:介紹了基于FPGA的任意分頻系數的分頻器的設計,該分頻器能實現分頻系數和占空比均可以調節的3類分頻:整數分頻、小數分頻和分數分頻。所有分頻均通過VHDL語言進行了編譯并且給出了仿真圖。本

2010-04-26 16:09:01

中從電子設計的外圍器件逐漸演變為數字系統的核心。伴隨著半導體工藝技術的進步,FPGA器件的設計技術取得了飛躍發展及突破。分頻器通常用來對某個給定的時鐘頻率進行分頻,以得到所需的時鐘頻率。在設計數

2019-10-08 10:08:10

分頻器在CPLD/FPGA設計中使用頻率比較高,盡管目前大部分設計中采用芯片廠家集成的鎖相環資源 ,但是對于要求奇數倍分頻(如3、5等)、小數倍(如2.5、3.5等)分頻、占空比50%的應用場合卻往往不能滿足要求。利用CPLD/FPGA設計多功能分頻器,我們具體該怎么做呢?

2019-08-12 07:50:25

分頻器是FPGA設計中使用頻率非常高的基本設計之一,盡管在目前大部分設計中,廣泛使用芯片廠家集成的鎖相環資源,如賽靈思(Xilinx)的DLL.來進行時鐘的分頻,倍頻以及相移。但是對于時鐘要求不高

2019-07-09 09:11:47

要設計小數分頻PLL,基本架構已經確定:使用基于MASH111的DSM,雙模預分頻器+PScounter實現。現在遇到的問題是,不知道怎么把小數分頻控制字經過DSM后的輸出與整數分頻控制字結合起來去控制(雙模分頻器+PScounter)可編程分頻器此前沒做過小數分頻PLL,求助大佬們點撥一二

2021-06-24 07:20:38

[0] afbdc must 16 align, width: 1080顯示屏能點亮,但極不穩定,一會就黑了,想問下RK3399顯示屏分辨率是否要16的整數倍?

2022-06-09 09:44:38

所示。該器件具有一個輸出分頻器(在VCO之后),但輸出頻率和VCO頻率都接近20MHz的整數倍。這種設置將迫使任何PLL產生分數雜散。…

2022-11-18 07:51:05

使用VHDL語言怎樣實現數控半整數分頻器,就當輸入為3時,就實現3.5分頻,當輸入為4時,就實現4.5分頻,同時要求占空比為50%。

2014-12-02 18:28:57

我想對2GHz的正弦波(相位噪聲很低)進行16分頻,分頻出來的125M信號輸入給FPGA,想選用ADi的分頻器實現分頻功能,我有以下幾個問題:1.我查了ADi的分頻器,分為(1)時鐘分頻器,(2

2019-01-11 13:39:43

請問ESP8266中使用system_param_load來讀取保存的數據,必須是4的整數倍嗎?

我一個數據結構中有六個字節,讀取會死機,擴為8個字節,才能運行

2023-11-03 07:35:14

數據, 這個地址必須是4的整數倍?類似這樣:{ int* a; int* b; a = (int*)(0x20000410); *a = 0;//okay b = (int*)(0x20000421

2018-11-19 08:51:36

我需要在Labview中判斷循環次數是否為20的整數倍,如何寫呀 各位大神求指教

2016-03-15 11:08:10

在復雜數字邏輯電路設計中,經常會用到多個不同的時鐘信號。介紹一種通用的分頻器,可實現2~256 之間的任意奇數、偶數、半整數分頻。首先簡要介紹了FPGA 器件的特點和應用范

2009-11-01 14:39:19 78

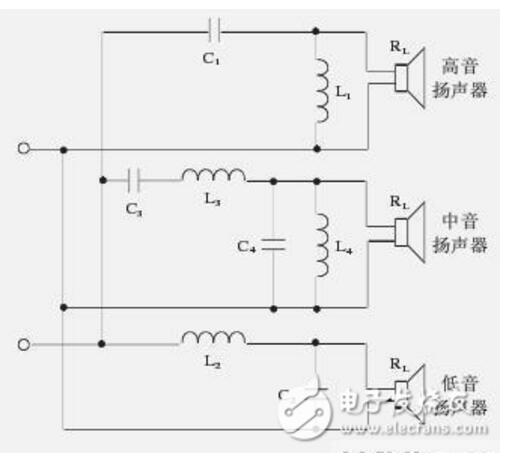

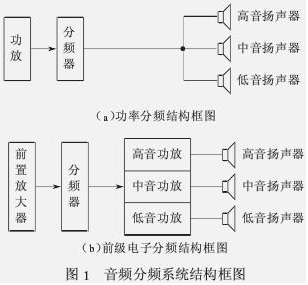

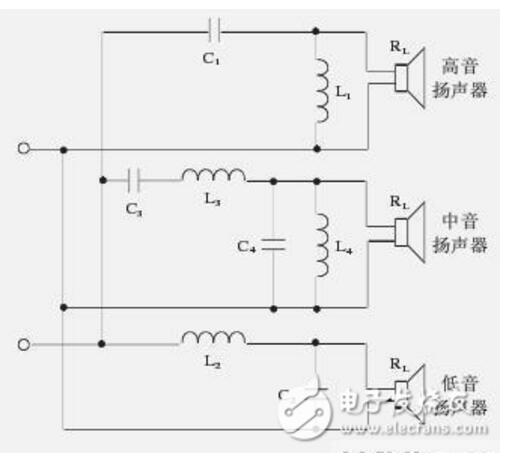

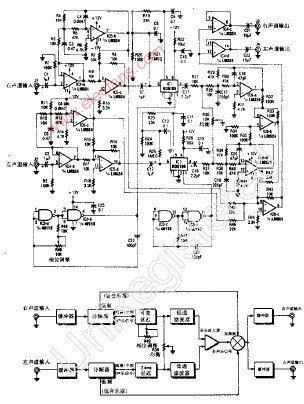

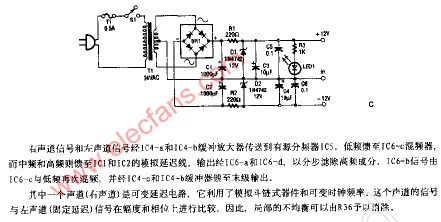

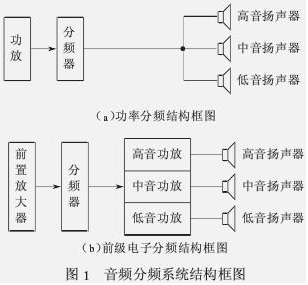

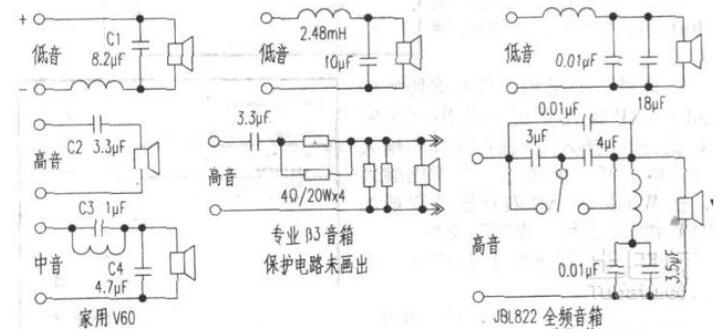

78 Hi-Fi三路有源分頻器:此立體聲三路有源分頻器與三路揚聲器系統配用,可避免無源分頻網絡的缺點,使揚聲器獲得最佳的功率電平。什么是有源分頻器?為什么需要有源分頻器 絕大多

2009-11-27 16:36:03 931

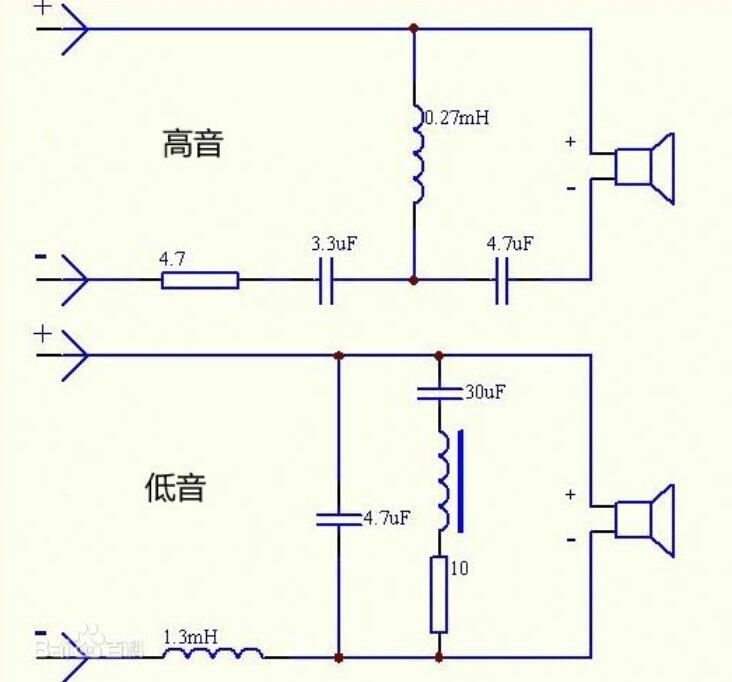

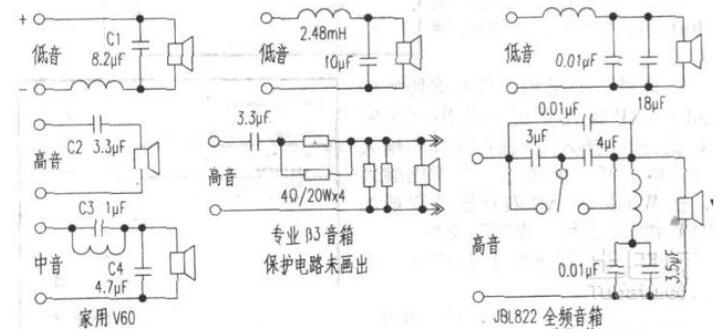

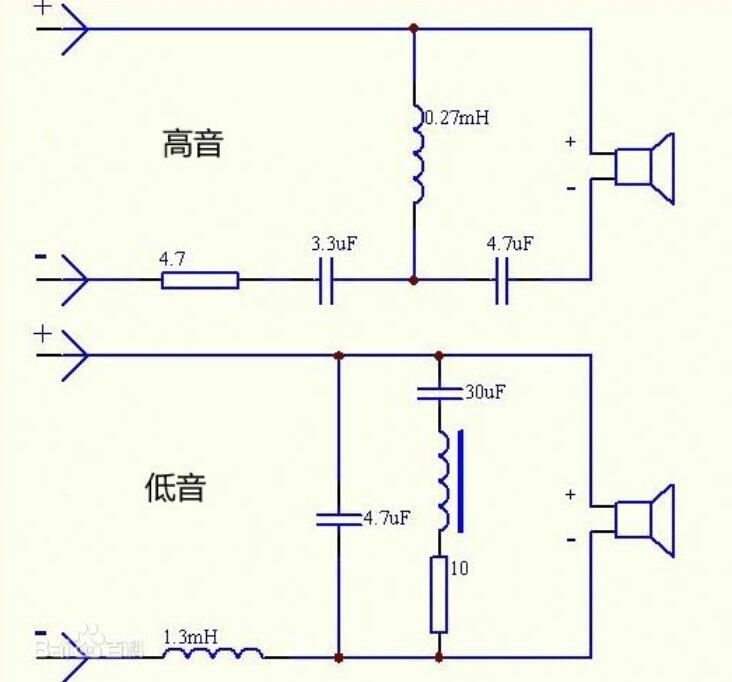

931 定阻型功率分頻器的設計與制作(四)-分頻器元器件的選取與制作:制作分頻器所需的電阻,一律用金屬膜電阻為宜,但要根據不同的需要適當選取相應大小的額定功率。2 電容器的

2009-12-02 15:46:59 73

73 定阻型功率分頻器的設計與制作(三)-二階功率分頻器

2009-12-02 15:48:19 88

88 本文介紹了一種能夠完成半整數和各種占空比的奇/偶數和的通用的分頻器設計,并給出了本設計在Altera公司的FLEX10K系列EPF10K10LC84-3型FPGA芯片中實現后的測試數據和設計硬件的測

2009-12-19 16:25:09 65

65 基于FPGA 的等占空比任意整數分頻器的設計

給出了一種基于FPGA 的等占空比任意整數分頻電路的設計方法。首先簡要介紹了FPGA 器件的特點和應用范圍, 接著討論了一

2010-02-22 14:22:32 39

39 分頻器設計與制作 (電子書):分頻器的基本原理,分頻器設計,分頻頻率和截止帶衰減率的選擇與使用,元件的選配及要求等內容,電感線圈的設計與制作。

2010-03-29 10:53:02 722

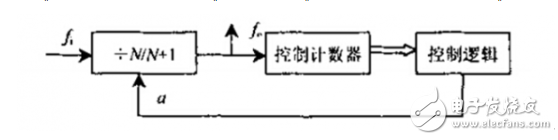

722 提出了一種通用的可編程雙模分頻器,電路主要由3 部分組成: 9/8 預分頻器,8 位可編程計數器和ΣΔ調制器構成。通過打開或者關斷ΣΔ 調制器的輸出來實現分數和整數分頻兩種工作

2010-04-23 08:39:35 30

30 簡要介紹了CPLD/FPGA器件的特點和應用范圍,并以分頻比為2.5和1.5的分頻器的設計為例,介紹了在MaxPlusII開發軟件下,利用VHDL硬件描述語言以及原理圖的輸入方式來設計數字邏輯電路的過

2010-07-17 17:55:57 36

36 UXN14M32K預分頻器15 GHz、32位有效分頻器UXN14M32KSuperDivider是一款DC-15 GHz、高度瞬時的整數分頻器,頂部1和4,294,967,295

2024-02-29 13:59:41

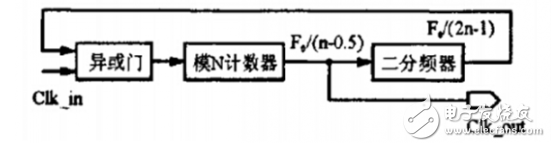

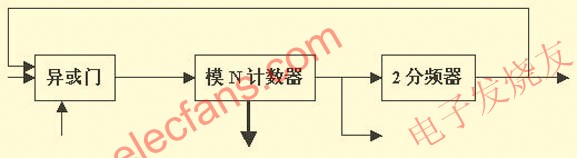

摘要:簡要介紹了CPLD/FPGA器件的特點和應用范圍,并以分頻比為2.5的半整數分頻器的設計為例,介紹了在MAX+plus II開發軟件下,利用VHDL硬件描述語言以及原理圖的輸

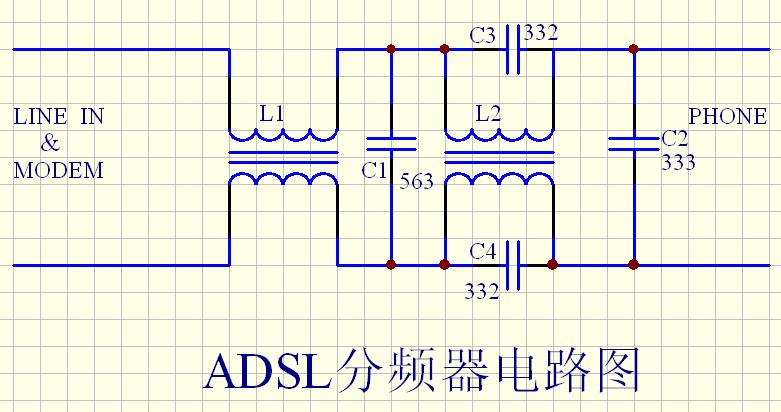

2006-03-13 19:36:44 1072

1072

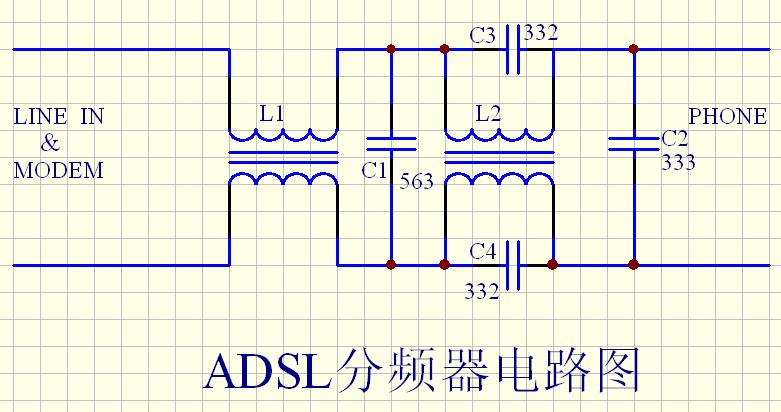

ADSL分頻器電路圖從電路上可以看出,該分頻器的作用只是針對電話座機,而非針對MODEM。在一般

2007-09-30 19:53:24 2567

2567

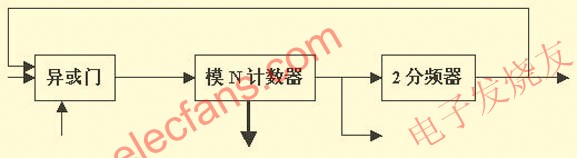

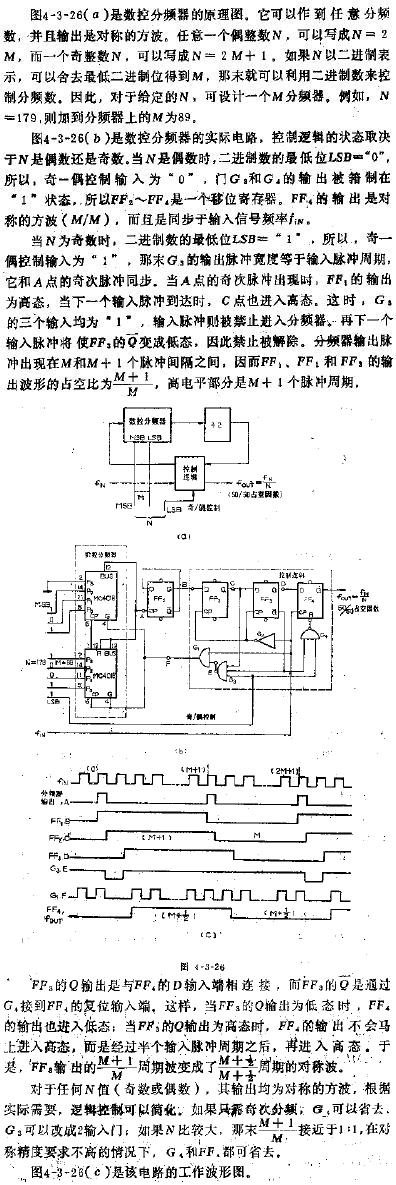

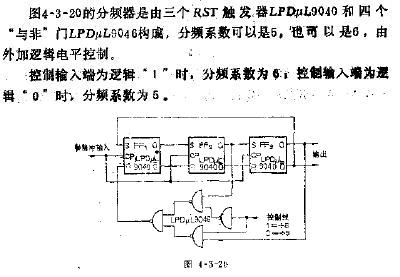

分頻系數可變的分頻器

2009-04-11 10:18:26 1553

1553

具有奇次和偶次分頻的分頻器

2009-04-11 10:22:12 1141

1141

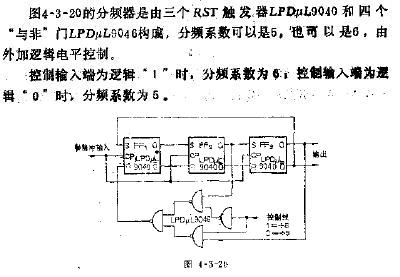

可由邏輯電平控制分頻系數的分頻器

2009-04-11 10:23:09 1463

1463

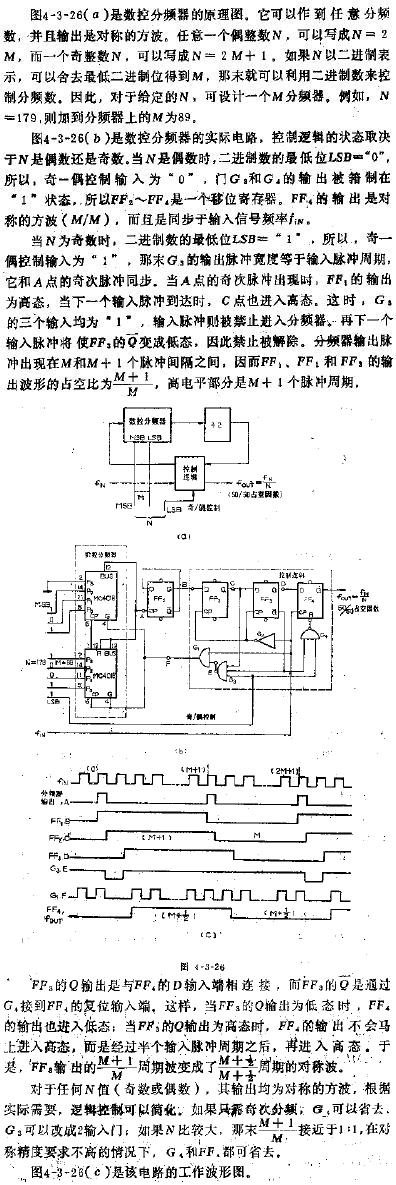

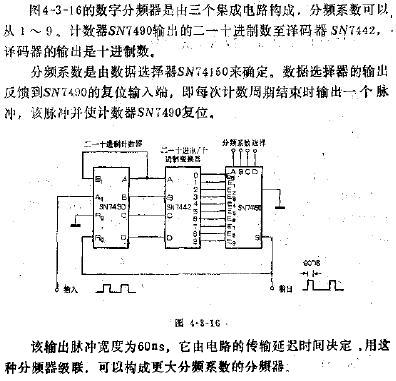

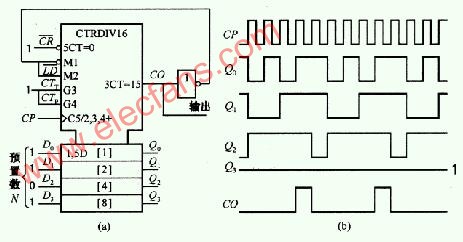

數控分頻器

2009-04-11 10:25:27 1507

1507

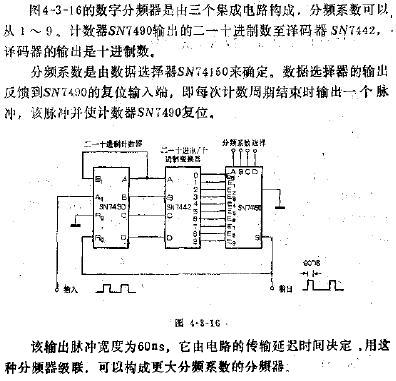

數字分頻器

2009-04-11 10:26:21 3463

3463

摘 要: 本文通過在QuartursⅡ開發平臺下,一種能夠實現等占空比、非等占空比整數分頻及半整數分頻的通用分頻器的FPGA設計與實現,介紹了利用VHDL硬件描

2009-06-20 12:43:07 731

731

摘要:簡要介紹了CPLD/FPGA器件的特點和應用范圍,并以分頻比為2.5的半整數分頻器的設計為例,介紹了在MAX+plus II開發軟件下,利用VHDL硬件描述語言以及原理圖的輸

2009-06-20 12:45:00 884

884

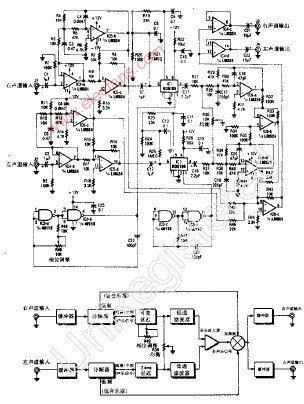

聲樂分頻器

2009-10-07 11:54:17 928

928

聲樂分頻器(續)

2009-10-07 11:55:27 664

664

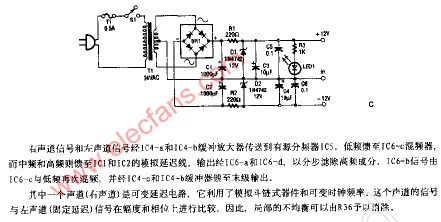

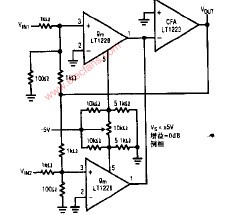

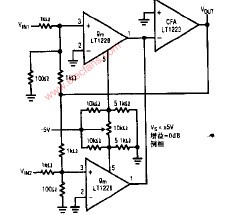

視頻分頻器

在電流反饋

2009-10-10 15:37:17 1291

1291

基于CPLD/FPGA的多功能分頻器的設計與實現

引言

分頻器在CPLD/FPGA設計中使用頻率比較高,盡管目前大部分設計中采用芯片廠家集成的鎖相環資源 ,但是對于要求

2009-11-23 10:39:48 1599

1599

可編程分頻器電路

可編程分頻器:計數器可以對計數脈沖分頻,改變計數器的模便可以改變分頻比。根據這個原理,可以用集成計數

2010-01-12 13:58:07 3927

3927

什么是分頻器 分頻器介紹

分頻器是指將不同頻段的聲音信號區分開來,分別給于放大,然后送到相應頻段的揚聲器中再進行重放

2010-02-05 17:51:10 5000

5000 分析了應用于倍頻電路的預置可逆分頻器的工作原理,推導了觸發器的驅動函數。并建立了基于simulink 和FPGA 的分頻器模型,實驗結果表明分頻器可以實現預置模和可逆分頻功能,滿足倍

2011-08-17 16:50:45 2407

2407

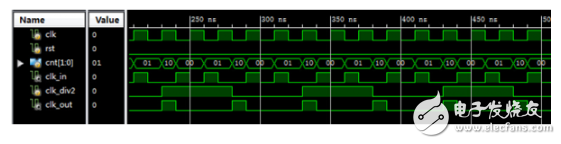

介紹了一種基于FPGA的雙模前置小數分頻器的分頻原理及電路設計,并用VHDL編程實現分頻器的仿真.

2011-11-29 16:43:06 48

48 用 Verilog實現基于FPGA 的通用分頻器的設計時鐘分頻包括奇數和偶數分頻

2016-07-14 11:32:47 46

46 音響分頻器原理,感興趣的可以看看。

2016-09-27 15:19:03 15

15 非整數倍路徑時延下的OMP信道估計方法_王東梅

2017-01-07 16:00:43 0

0 什么是分頻器 分頻器是指將不同頻段的聲音信號區分開來,分別給于放大,然后送到相應頻段的揚聲器中再進行重放。在高質量聲音重放時,需要進行電子分頻處理。 分頻器是音箱內的一種電路裝置,用以將輸入的模擬

2017-11-18 11:49:30 56916

56916 分頻器一般常用于擁有高音和低音的單元,或者帶有中音單元的音箱中,若缺少分頻器這種擁有多單元的音箱就不能將不同頻段的聲音進行回放。而且分頻器的種類以及質量的差異,也同時影響到音箱能否回放出更好的聲音表現。

2017-11-24 14:16:18 18707

18707 分頻器分為主動式、被動式、脈沖分頻器三種。主動式電子分音器的原理就是要把適當頻率訊號傳給適當的單體,被動式分音器“功能、用途”是介于擴大器與喇叭之間,由于單一喇叭無法達到“全頻段響應”,脈沖分頻器利用漢穩態電路的計數功能實現分頻的電路,又稱為數字分頻器。

2018-01-10 15:36:20 15977

15977 本文為大家帶來電子分頻器的各功能旋鈕、調節方法及注意事項。

2018-01-10 15:47:58 25952

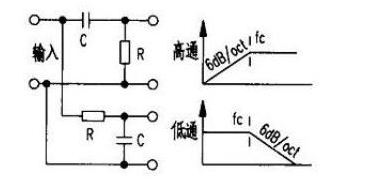

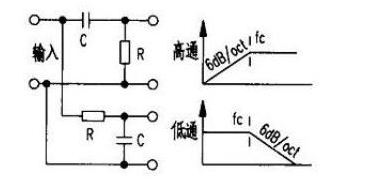

25952 音箱分頻器可以將聲音信號分成若干個頻段。如二分頻器就是由一個高通濾波器和一個低通濾波器組成。三分頻則又增加了一個帶通濾波器。分頻器是音箱中的“大腦”,對音質的好壞至關重要。可以看出,分頻器充分利用的電容器和線圈的特性達到分頻。

2018-02-06 10:54:03 17853

17853 音箱分頻器可以將聲音信號分成若干個頻段。如二分頻器就是由一個高通濾波器和一個低通濾波器組成。三分頻則又增加了一個帶通濾波器。分頻器是音箱中的“大腦”,對音質的好壞至關重要。

2018-03-01 16:25:54 49465

49465 本文首先介紹了音箱分頻器概念,其次介紹了音箱分頻器結構與作用,最后介紹了_音箱分頻器制作方法與圖解。

2018-04-13 08:50:18 196007

196007 本文開始介紹了音箱分頻器原理,其次介紹了音箱分頻器分類與特點以及音箱分頻器電路及作用,最后介紹了音箱分頻器接線方法圖解。

2018-04-13 09:32:27 121473

121473 本文首先介紹了為什么要使用電子分頻器,其次闡述了電子分頻器工作原理及作用、特點,最后介紹了電子分頻器的調整方法、使用注意事項及發展趨勢。

2018-05-24 14:46:53 28407

28407 本文首先介紹了什么是分頻器,其次闡述了音箱箱體及音箱分頻器結構和原理,最后介紹了音箱分頻器特點和作用。

2018-05-25 17:47:16 15572

15572

本文主要介紹的是汽車音響的分頻器,首先介紹了汽車音響的分頻器的種類,其次介紹了分頻器的作用及分頻點的選擇,最后分析了汽車音響分頻器安裝位置,具體的跟隨小編一起來了解一下。

2018-05-28 11:54:38 14358

14358 本文首先介紹了分頻器的分類及電子分頻器的工作原理,其次介紹了主動分頻器的優缺點,最后介紹了被動分頻器的優缺點,具體的跟隨小編一起來了解一下。

2018-05-28 14:52:31 53338

53338 設計背景: 分頻在 fpga的設計中一直都擔任著很重要的角色,而說到分頻,我相信很多人都已經想到了利用計算器來計算達到想要的時鐘頻率,但問題是僅僅利用計數器來分頻,只可以實現偶數分頻,而如果我需要

2018-06-13 11:21:48 13569

13569

采用有源分頻器可以降低對功放帶寬的要求;省去了大功率的LC元件;分頻點也易于調整,且可以獲得比功率分頻更佳的效果。這里介紹兩種有源二分頻器電路。如圖9-4所示為有源二分頻器組成的功放電路

2018-08-10 16:19:37 25918

25918

分頻器是FPGA設計中使用頻率非常高的基本單元之一。盡管目前在大部分設計中還廣泛使用集成鎖相環(如altera的PLL,Xilinx的DLL)來進行時鐘的分頻、倍頻以及相移設計,但是,對于時鐘要求

2019-08-07 08:00:00 10310

10310

缺點:當分頻倍數很大時,需要的寄存器也是倍增。當然你也可以采用復用的方式去減少所需寄存器數目,例如,36分頻,可以做兩個6分頻器相連,則所需寄存器為6個,需要的寄存器數大大減少。

2018-12-08 10:40:57 10750

10750

分頻器主要分為偶數分頻、奇數分頻、半整數分頻和小數分頻,如果在設計過程中采用參數化設計,就可以隨時改變參量以得到不同的分頻需要。

2019-02-01 01:28:00 18914

18914

分頻器是一種基本電路,通常用來對某個給定頻率進行分頻,得到所需的頻率。整數分頻器的實現非常簡單,可采用標準的計數器,也可以采用可編邏輯器件設計實現。但在某些場合下,時鐘源與所需的頻率不成整數倍關系,此時可采用小數分頻器進行分頻。

2019-11-20 07:05:00 7995

7995 音箱分頻器可以將聲音信號分成若干個頻段。如二分頻器就是由一個高通濾波器和一個低通濾波器組成。三分頻則又增加了一個帶通濾波器。分頻器是音箱中的“大腦”,對音質的好壞至關重要。

2019-10-08 10:11:32 9984

9984 優點是在于多路揚聲器中,每一只都可視為獨立的部分。如果采用了串聯式的分頻器,任一個零件都可能會影響到高通與低通的特性。汽車音響里所應用的都是并聯式分頻器。

2019-10-09 09:12:56 5894

5894

分頻器的功能則相當于音箱中的“大腦”,分頻器對音質的好壞起到了至關重要的作用。使用分頻器可以將高頻信號送到高音揚聲器中,低頻信號送到低音揚聲器中,使高、低頻信號各行其道,盡可能的發揮各自揚聲器的工作

2019-12-02 08:47:27 22061

22061 本文主要闡述了音箱分頻器的選擇方法。

2019-12-02 09:08:01 48251

48251

本文主要闡述看音箱分頻器的維修方法及音箱分頻器接喇叭的方法。

2020-03-28 11:09:59 19022

19022

簡要介紹了CPLD/FPGA器件的特點和應用范圍,并以分頻比為2.5和1.5的分頻器的設計為例,介紹了在MaxPlusII開發軟件下,利用VHDL硬件描述語言以及原理圖的輸入方式來設計數字邏輯電路的過程和方法。該設計具有結構簡單、實現方便、便于系統升級的特點。

2021-03-16 09:45:53 10

10 簡要介紹了 CPLD/FPGA器件的特點和應用范圍,并以分頻比為2.5和15的分頻器的設計為例,介紹了在 Maxplusll開發軟件下,利用ⅤHDL硬件描述語言以及原理圖的輸入方式來設計數字邏輯電路的過程和方法。該設計具有結構簡單、實現方便、便于系統升級的特點。

2021-03-22 16:52:15 5

5 一種基于FPGA的分頻器的實現說明。

2021-05-25 16:57:08 16

16 基于CPLD/FPGA的半整數分頻器設計方案

2021-06-17 09:37:02 21

21 在進行USB CDC類開發時 無法發送64整數倍的數據(通信電源技術審稿費用)-在向客戶推STM32F4芯片的時候,客戶反饋使用CDC類無法發送64個字節,于是通過深入研究問題,發現問題之所在,到

2021-08-04 17:57:57 19

19 在進行USB CDC類開發時 無法發送64整數倍的數據(續)(核達中遠通電源技術)-此文延續之前相同文章的話題,是對上篇文章的補充,之所以會有此文,主要是之前發現問題是在STM32F4上,解決方案

2021-08-04 18:15:50 17

17 偶數倍分頻器的實現非常簡單,只需要一個計數器進行計數就能實現。如需要N分頻器(N為偶數),就可以由待分頻的時鐘觸發計數器進行計數,當計數器從0計數到N/2-1時,將輸出時鐘進行翻轉,并給計數器一個復位信號,以使下一個時鐘開始從零計數。

2022-11-21 09:41:24 1368

1368 所謂“分頻”,就是把輸入信號的頻率變成成倍數地低于輸入頻率的輸出信號。數字電路中的分頻器主要是分為兩種:整數分頻和小數分頻。其中整數分頻又分為偶分頻和奇分頻,首先從偶分頻開始吧,入門先從簡單的開始!

2023-03-23 15:06:22 3014

3014

上一篇文章介紹了偶分頻,今天來介紹一下奇數分頻器的設計。

2023-03-23 15:06:49 1858

1858

倍頻器(frequency multiplier)使輸出信號頻率等于輸入信號頻率整數倍的電路。輸入頻率為f1,則輸出頻率為f0=nf1,系數n為任意正整數,稱倍頻次數。

2023-04-24 10:34:59 3961

3961 FPGA分頻器是一種常用于數字信號處理、通信系統、雷達系統等領域的電路,其作用是將信號分成多個頻段。

2023-05-22 14:29:44 3076

3076

是用于滿足設計的需求。 分頻:產生比板載時鐘小的時鐘。 倍頻:產生比板載時鐘大的時鐘。 二:分頻器的種類 對于分頻電路來說,可以分為整數分頻和小數分頻。 整數分頻:偶數分頻和奇數分頻。 小數分頻:半整數分頻和非半整數分頻。 三:分頻器的思想 采用計數器的思想實

2023-11-03 15:55:02 3266

3266

鎖相環整數分頻和小數分頻的區別是什么? 鎖相環(PLL)是一種常用的電子電路,用于將輸入的時鐘信號與參考信號進行同步,并生成輸出信號的一種技術。在PLL中,分頻器模塊起到關鍵作用,可以實現整數分頻

2024-01-31 15:24:48 5373

5373 分頻器是一種電子設備,用于將輸入信號分成不同頻率的輸出信號。其主要作用是將原始輸入信號分離成多個頻率范圍內的信號,以供不同的電路進行處理。分頻器廣泛應用于通信、測量和音頻系統中。 分頻器的主要

2024-02-01 11:19:51 6196

6196

電子發燒友App

電子發燒友App

評論