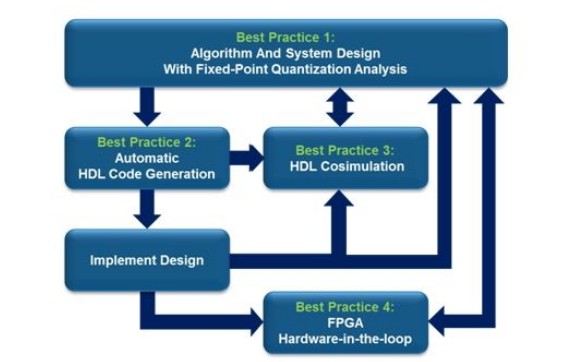

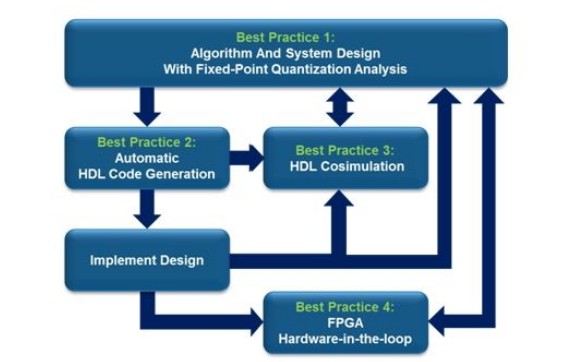

本文將介紹使用MATLAB和Simulink創(chuàng)建FPGA原型的最佳方法。這些最佳方法包括:在設(shè)計過程初期分析定點量化的效應并優(yōu)化字長,產(chǎn)生更小、更高效的實現(xiàn)方案;利用自動HDL代碼生成功能,

2013-01-28 11:08:08 17103

17103

自動白平衡模塊的設(shè)計是使用 HDL Coder 在 MATLAB 和 Simulink 中創(chuàng)建的。HDL Coder能夠生成 HDL 文件,這些文件可以作為 IP 在我們的目標 FPGA 中運行。

2023-11-13 09:27:03 2179

2179

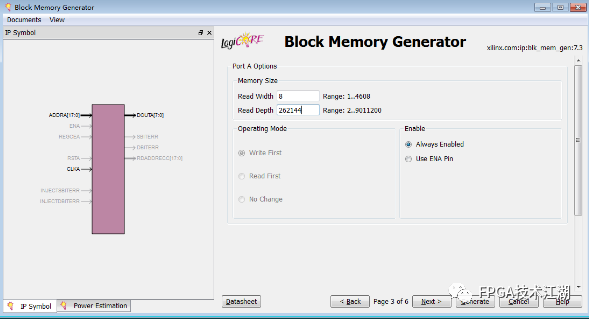

初始化時存入數(shù)據(jù)。那在IP核rom中存放大量數(shù)據(jù)對FPGA有什么影響,比如我想存65536個16位的數(shù),然后在64M或者128M的時鐘下讀出來。會不會導致FPGA速度過慢?

2013-01-10 17:19:11

有某試驗數(shù)據(jù),用matlab求fft之后再求得的功率譜密度是這樣的:圖1但是用fft ip核,取前4096個數(shù)據(jù),得到fft之后的結(jié)果是這樣的:圖2求功率譜密度得到的是這樣的:圖3試驗數(shù)據(jù)都是零點幾

2016-04-21 20:36:18

的基礎(chǔ)上,給出了一種仿真調(diào)試方 案;利用該方案指出了其中若干邏輯錯誤并對其進行修改,最終完成了修改后IP核的FPGA下載測試。1 OC8051結(jié)構(gòu)分析OpenCores網(wǎng)站提供的OC8051 IP核

2012-08-11 11:41:47

FPGA嵌入8051單片機 IP核編程,編寫的c語言矩陣鍵盤程序可以在stc89c54單片機上正常工作,但是下載到FPGA中8051單片機ip核的rom中,不能正常工作,求指教

2013-07-25 21:27:44

設(shè)計早期系統(tǒng)規(guī)劃 365.3.綜合和仿真技巧 375.3.1 綜合工具XST的使用 375.3.2 基于ISE的仿真 425.3.3 和FPGA接口相關(guān)的設(shè)置以及時序分析 455.3.4 綜合高手揭秘

2009-04-09 18:28:46

本帖最后由 jf_25420317 于 2023-11-17 11:10 編輯

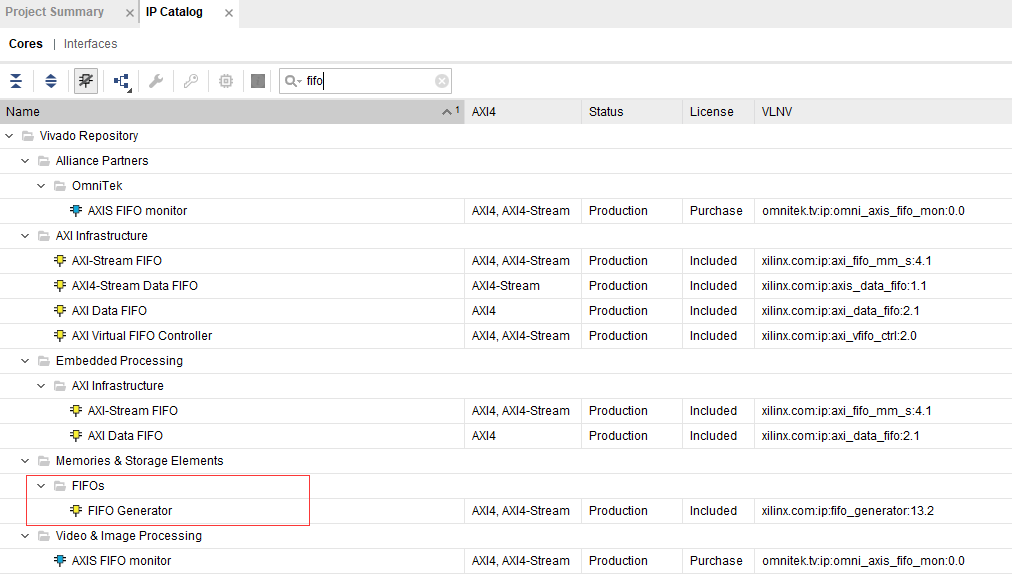

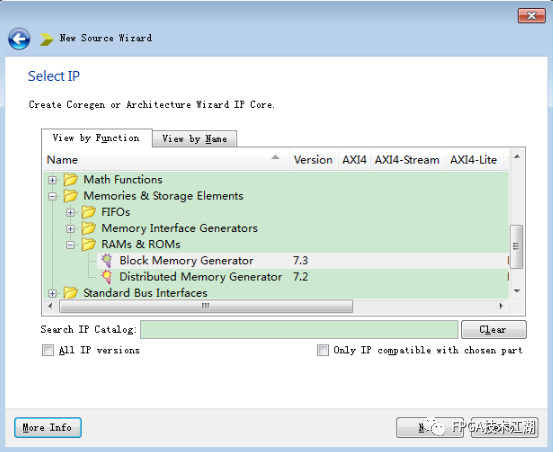

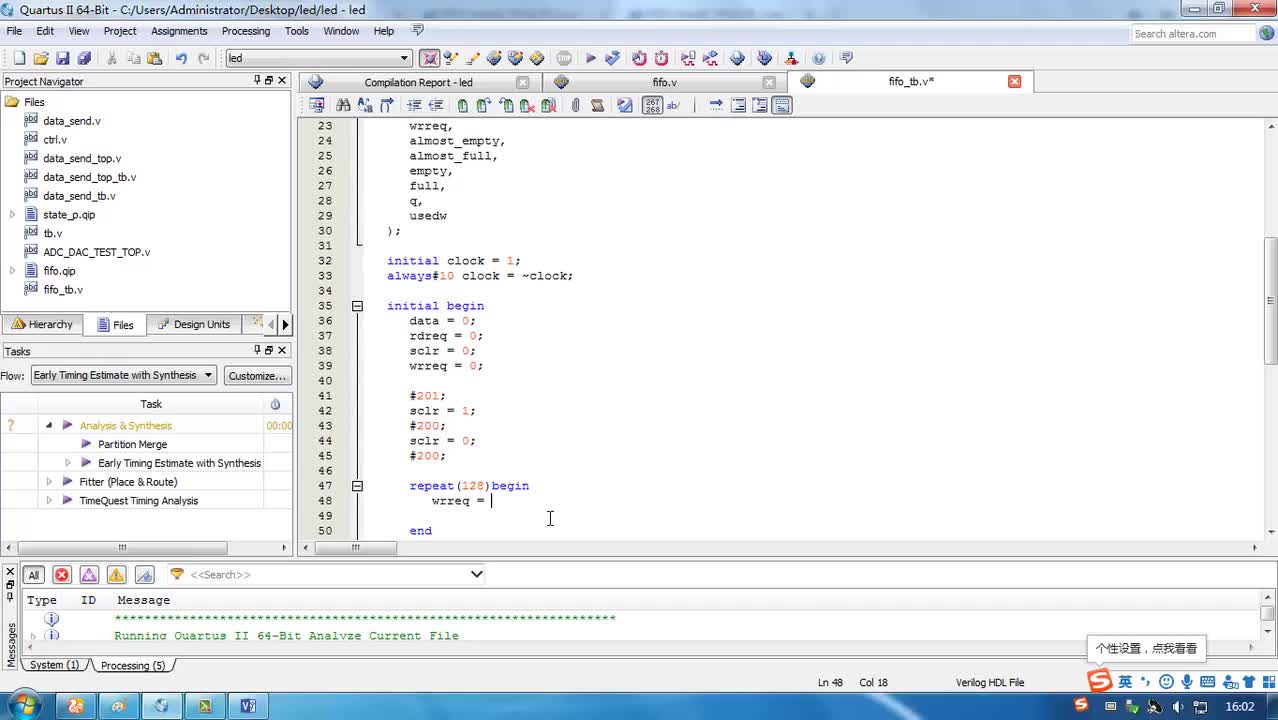

FPGA開發(fā)過程中,利用各種IP核,可以快速完成功能開發(fā),不需要花費大量時間重復造輪子。

當我們面對使用新IP核

2023-11-17 11:09:22

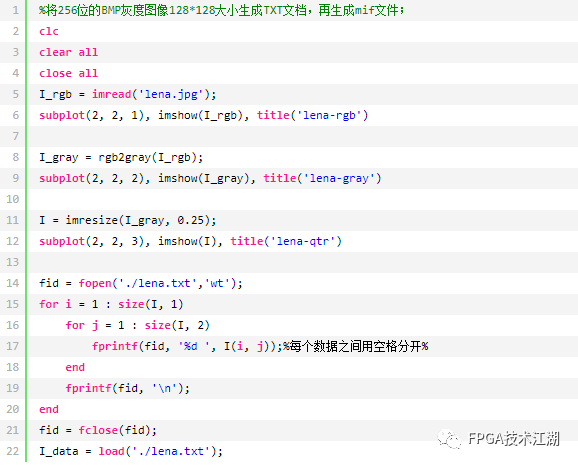

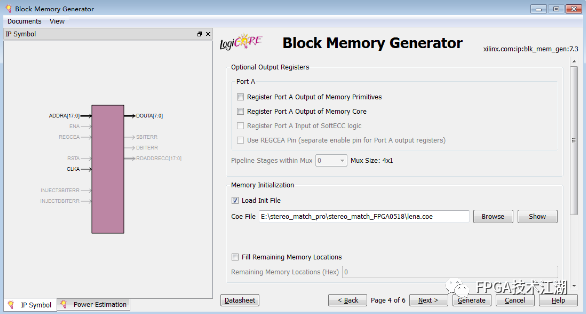

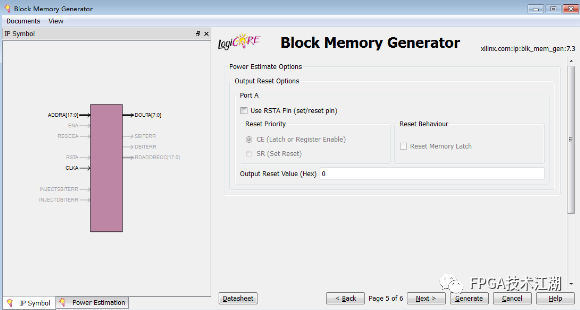

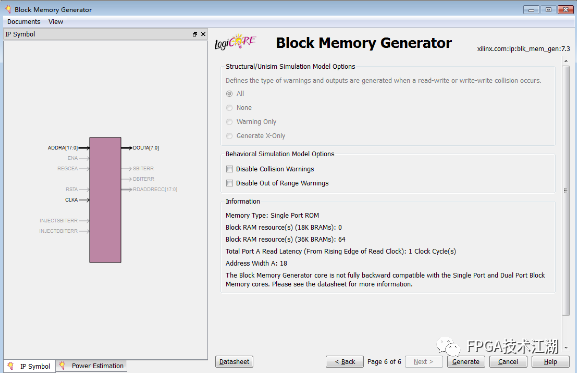

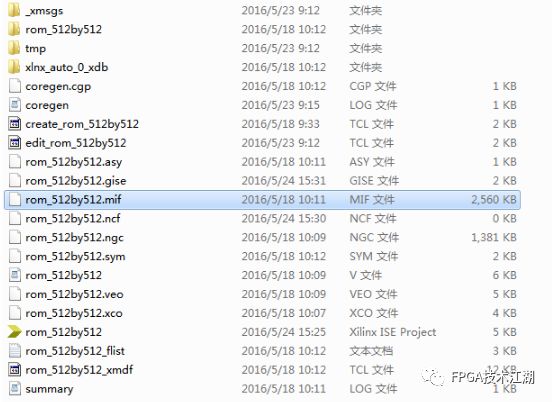

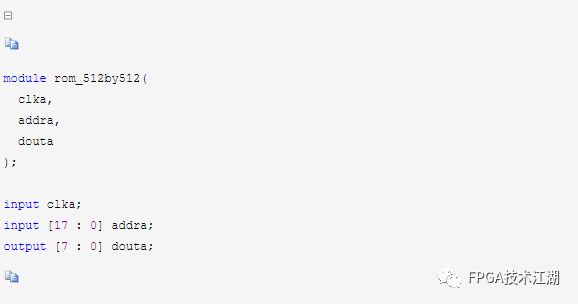

文檔創(chuàng)建既然是ROM,那么我們就必須實現(xiàn)給它準備好數(shù)據(jù),然后在FPGA實際運行時,我們直接使用這些預存儲好的數(shù)據(jù)就行。Xilinx FPGA的片內(nèi)ROM支持初始化數(shù)據(jù)配置。如圖所示,我們可以創(chuàng)建一個名為

2019-04-08 09:34:43

和性能測試。確保IP軟核能夠正常工作,并滿足項目的性能要求。

在驗證過程中,可以使用仿真工具進行模擬測試,或者使用實際的FPGA硬件進行驗證。

優(yōu)化和調(diào)試 :

如果在驗證過程中發(fā)現(xiàn)問題或性能瓶頸

2024-05-27 16:13:24

說,上貨。

ROM使用教程

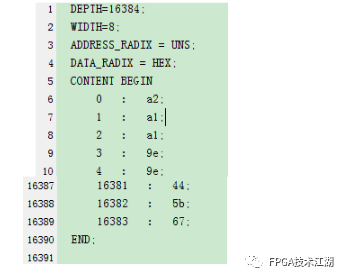

ROM的英文全稱為Read-Only Memory,即只讀存儲器。可以從任意地址上讀取數(shù)據(jù),但是不能寫入。那么我們ROM中的數(shù)據(jù),就需要我們提前存放進去,在IP核中

2023-06-15 16:57:22

是利用FPGA片內(nèi)嵌入的M9K構(gòu)成的,所以不能夠?qū)崿F(xiàn)掉電不丟失。 由于設(shè)計ROM深度為256,故而地址的寬度為8位。 本次構(gòu)建為ROM,所以在構(gòu)建ROM之前應當首先設(shè)計好初始化文件(mif文件

2023-03-13 15:46:42

不多說,上貨。IP CORE 之 ROM 設(shè)計- ISE 操作工具本篇實現(xiàn)基于叁芯智能科技的SANXIN -B02 FPGA開發(fā)板,如有入手開發(fā)板,可以登錄官方淘寶店購買,還有配套的學習視頻

2023-04-07 20:09:59

本帖最后由 elecfans跑堂 于 2015-9-7 13:54 編輯

一個項目里有IP核rom,想改其中的參數(shù)重新生成,結(jié)果打開失敗,然后我把它移除了,在項目里邊新添加不了,提示如下錯誤

2015-09-07 12:21:59

ise FFT ip核的datasheet文檔打不開什么原因

2015-08-27 14:46:45

請問哪位高手有ise軟件中的各個ip核的功能介紹

2013-10-08 16:41:25

大家好,我正在尋找AWGN IP核,AWGN IP核似乎自2009年起停產(chǎn)。我相信在2009年之前下載早期版本的ISE應該有AWGN IP核,但在ise 9.1i它不存在。誰有任何建議可以找到已停產(chǎn)

2019-02-26 11:11:59

這次利用Xilinx公司的芯片做FPGA開發(fā)的時候用到了ROM,肯定要對ROM做仿真,經(jīng)過了一天的努力,總算可以做仿真了,現(xiàn)在把過程寫出來,供大家參考一下。1.首先需要編譯XINLINX的庫文件

2012-02-29 10:44:56

文件HRV_top。通過測試文件對設(shè)計文件進行功能仿真,仿真結(jié)果正確。但是當我對設(shè)計完成布局布線之后,沒有其它錯誤,接著進行時序仿真,見圖2. 在圖2中,測試文件調(diào)用的RAM IP核(也就是RAM_fangzhen)怎么找不到啊??求高手解答。

2015-08-29 16:55:16

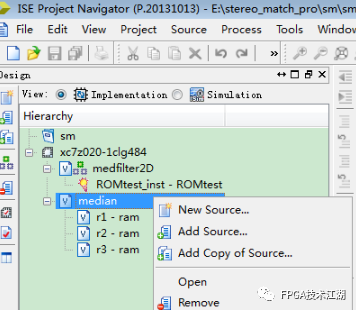

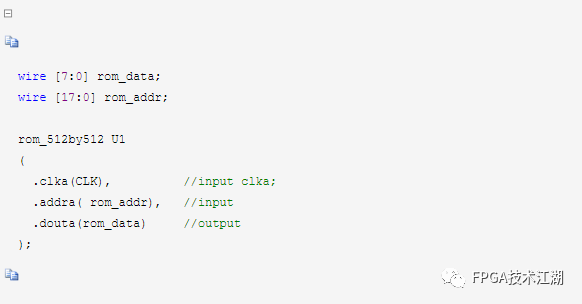

如圖所示。●Pll_controller.v模塊產(chǎn)生FPGA內(nèi)部所需時鐘信號。●Rom_test.v模塊例化FPGA片內(nèi)ROM,并產(chǎn)生FPGA片內(nèi)ROM讀地址,定時遍歷讀取ROM中的數(shù)據(jù)。●Chipscope_debug.cdc模塊引出ROM的讀取信號總線,通過chipscope在ISE中在線查看ROM讀取時序。

2016-01-06 12:22:53

文檔創(chuàng)建既然是ROM,那么我們就必須實現(xiàn)給它準備好數(shù)據(jù),然后在FPGA實際運行時,我們直接使用這些預存儲好的數(shù)據(jù)就行。Xilinx FPGA的片內(nèi)ROM支持初始化數(shù)據(jù)配置。如圖所示,我們可以創(chuàng)建一個

2016-01-08 13:12:44

路徑。設(shè)定完成后點擊“OK”回到ISE主界面。 2 功能仿真如圖所示,雙擊“Simulate Behavioral Model”開始仿真。接著,Modelsim中我們可以查看讀ROM的波形。這里需要

2016-01-11 12:17:28

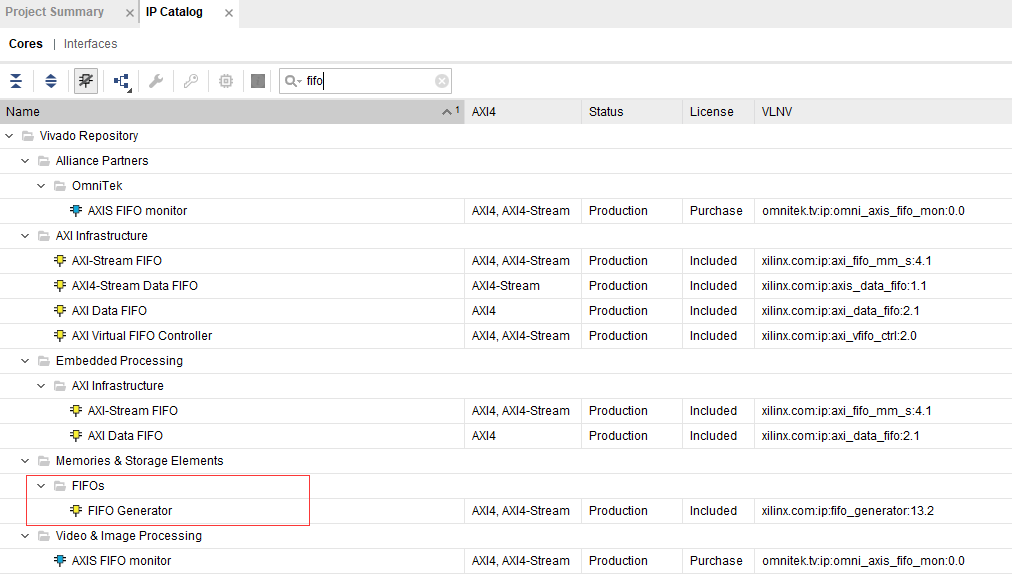

/1jGjAhEm 1 功能概述該工程實例內(nèi)部系統(tǒng)功能框圖如圖所示。我們通過IP核分別例化了ROM、FIFO和RAM,ROM有預存儲的數(shù)據(jù)可供讀取,將其放入FIFO中,隨后再讀出送到RAM供讀取。通過ISE集成

2016-03-16 12:43:36

`Xilinx FPGA入門連載60:FPGA 片內(nèi)ROM FIFO RAM聯(lián)合實例之功能仿真特權(quán)同學,版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2016-03-18 09:20:25

1 功能概述該工程實例內(nèi)部系統(tǒng)功能框圖如圖所示。我們通過IP核分別例化了ROM、FIFO和RAM,ROM有預存儲的數(shù)據(jù)可供讀取,將其放入FIFO中,隨后再讀出送到RAM供讀取。通過ISE集成的在線

2019-01-10 09:46:06

文檔創(chuàng)建既然是ROM,那么我們就必須實現(xiàn)給它準備好數(shù)據(jù),然后在FPGA實際運行時,我們直接使用這些預存儲好的數(shù)據(jù)就行。Xilinx FPGA的片內(nèi)ROM支持初始化數(shù)據(jù)配置。如圖所示,我們可以創(chuàng)建一個名為

2019-01-09 16:02:21

在仿真fft ip核時 輸出信號一直為0,檢查了輸入波形,應該沒有問題,大家?guī)兔纯窗奢斎胧怯?b class="flag-6" style="color: red">rom里面的mif文件產(chǎn)生的信號。

2017-11-21 10:44:53

我用quartus II調(diào)用modelsim仿真fft ip核,仿真結(jié)束后我想驗證下數(shù)據(jù)是否正確,結(jié)果是:我用matlab生成同樣的整形數(shù)據(jù),然后用modelsim仿出的結(jié)果txt文件與用

2012-09-20 12:48:37

modelsim 仿真 altera IP核(ROM,RAM實例)急求大神們ROM和RAM 的綜合仿真代碼

2015-11-19 21:02:57

有沒有大神可以提供xilinx FPGA的FFT IP核的調(diào)用的verilog 的參考程序,最近在學習FFT的IP核的使用,但是仿真結(jié)果有問題,所以想找些參考設(shè)計,謝謝

2016-12-25 17:05:38

本帖最后由 lee_st 于 2017-11-2 15:01 編輯

《FPGACPLD設(shè)計工具──Xilinx+ISE使用詳解》第 1 章 ISE 系統(tǒng)簡介

2017-11-02 10:02:32

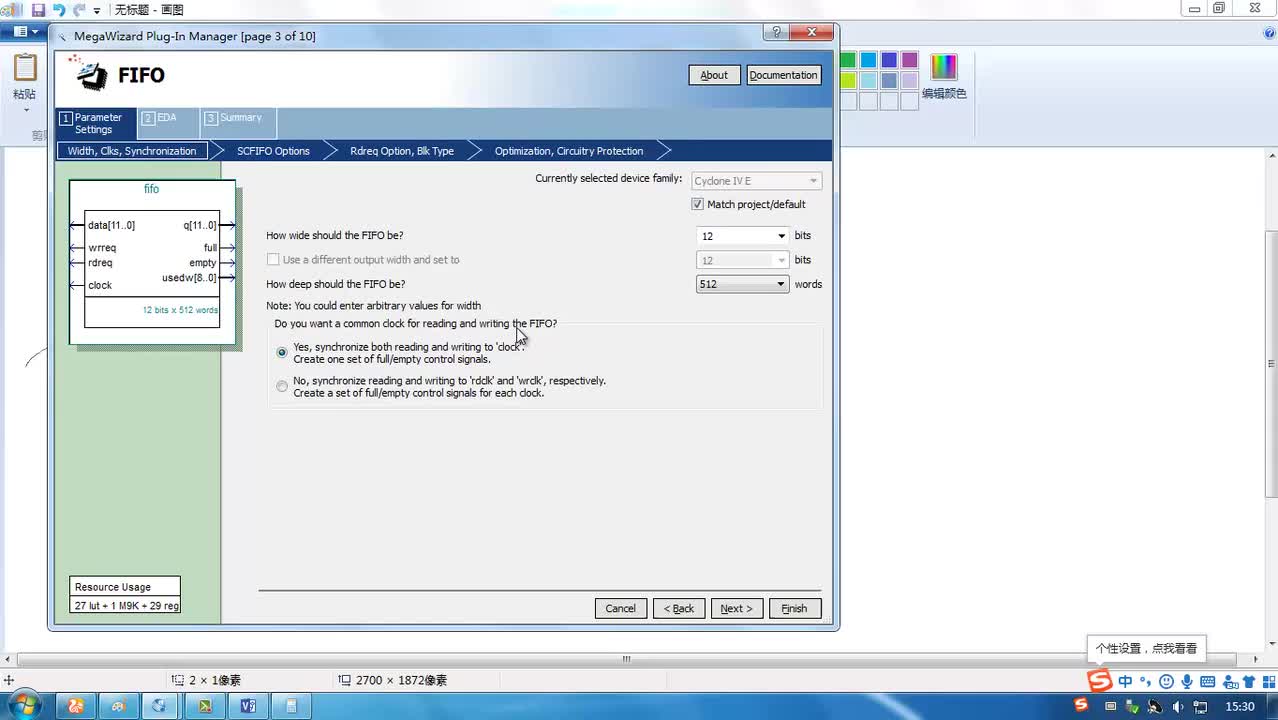

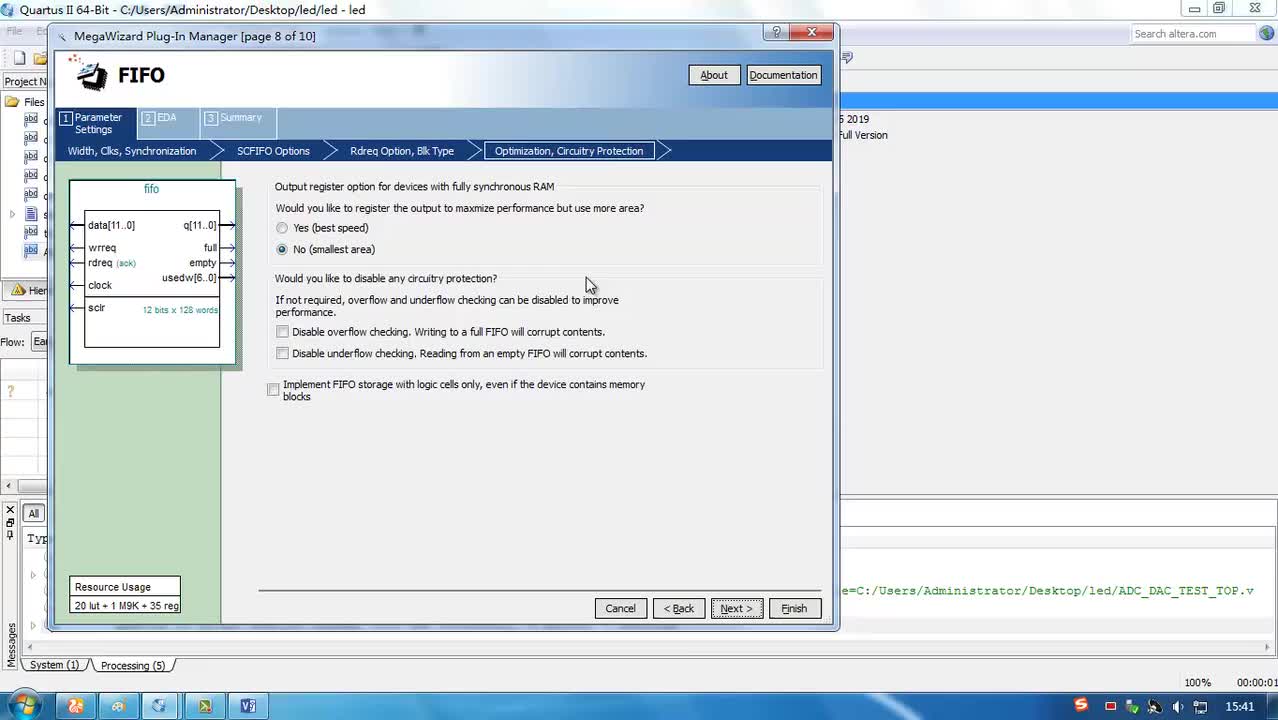

和創(chuàng)建包含定制IP核的設(shè)計文件,然后在設(shè)計文件中例化IP核。在Mega Wizard插件管理器中可以創(chuàng)建、定制和例化Altera IP核、參數(shù)化模型庫(LPM)模塊以及在Quartus II軟件、EDA

2016-12-22 23:37:00

增加1,所以此時的mif文件中存放的是0到255)。在右側(cè)的IP核搜索的編輯區(qū),輸入rom,在菜單欄找到并雙擊rom(在這里我們使用單端口的rom,雙端口的rom,自己感興趣的話,可以自己調(diào)用試一試

2019-12-16 17:18:30

,手把手演示工程創(chuàng)建,IP核調(diào)用、Testbench編寫以及仿真驗證,讓每一個0基礎(chǔ)的朋友都能快速跟上節(jié)奏。另外,有一定基礎(chǔ)的朋友,其實也可以觀看,因為在設(shè)計中,我已經(jīng)將很多的設(shè)計小技巧穿插在視頻中了。請

2015-09-22 14:06:56

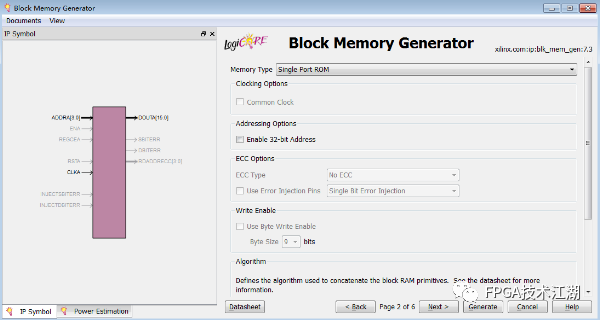

的存儲單元中,然后系統(tǒng)正常工作時,讀出其中存儲的數(shù)據(jù)。配置一人ROM的IP核,有三個步驟:參數(shù)設(shè)置、電子設(shè)計自動化、總結(jié)。理論的內(nèi)容可以再仔細研讀其他資料,這里以實踐為主。新建一個mif文件,mif文件就是

2016-09-24 23:36:31

or negedge RST_N)beginif(!RST_N)addressRun Simulation Tool-- > RTL Simulation可以看到,數(shù)據(jù)的讀取在第0ns時就讀取,這是由于在配置ROM IP核時的Regs/Clken/Aclrs頁面把q outputport.設(shè)置去掉了。

2016-09-25 09:58:23

前面建好了mif文件,下面就要創(chuàng)建ROM IP核了。首先,我們新建一個工程。菜單欄:Tools --> MegaWizardPlug-InManager ,點擊“Next”選擇ROM的IP核

2016-09-25 09:38:33

內(nèi)建的示波器。SignalTapⅡ的使用要新建一個仿真調(diào)試文件。SignalTapⅡ可以設(shè)定信號的觸發(fā)方式。其他請補充。另,FPGA的IP核并不是只有這幾種,從新建IP核的界面可以看到,IP核還有很多。

2016-10-11 22:24:16

總是出來后幾個地址的結(jié)果。。。如圖,圖一是ise仿真結(jié)果,addr為242時的結(jié)果為-1400(ip核有時延),但在matlab里看rom的內(nèi)容242對應的是-1408(圖二),-1400是后面3位

2018-12-08 11:37:00

新手見諒使用IP核設(shè)計了一個10階3級的CIC濾波器,輸入數(shù)據(jù)位寬12位,輸出最大22位但是仿真出來的結(jié)果有種溢出的感覺,想不通是怎么回事,求各位前輩幫忙分析~~貼出來IP核設(shè)置界面,還有matlab處理的結(jié)果{:4_108:}

2013-10-13 16:56:12

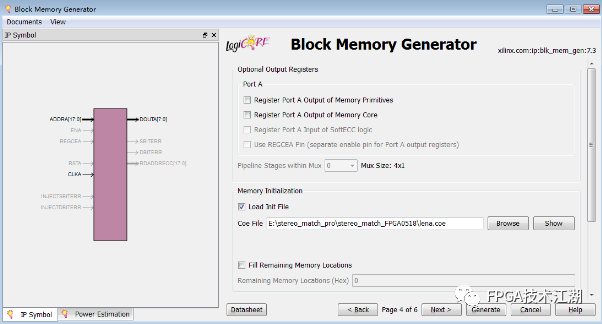

本例程主要使用Vivado 調(diào)用ROM IP核,用含有正弦曲線的.coe文件初始化ROM,最終通過仿真實現(xiàn)波形的顯示 一、首先建立工程 二、選擇芯片的型號 我

2021-01-08 17:16:43

對于深入學習使用FPGA的小伙伴們,特別是一些復雜的、大規(guī)模的設(shè)計應用,適宜的IP核對開發(fā)能起到事半功倍的作用。IP核的概念與我們sdk里庫的概念相似。IP即電路功能模塊,用戶可以直接調(diào)用這些模塊

2024-04-29 21:01:16

現(xiàn)在在做一個任意波形發(fā)生器的設(shè)計,先是用正弦波波形數(shù)據(jù)初始化的rom,能夠顯示出正弦波,后來用鋸齒波的數(shù)據(jù),再次初始化rom,仿真出來的波形還是正弦波。不知道為什么???

2015-09-29 11:46:35

利用system generator將ISE和MATLAB關(guān)聯(lián),但是打開simulink的過程中出現(xiàn)如下圖情況 求問為何?過程中完全按照流程,分別給MATLAB以管理員權(quán)限,而且版本匹配,ISE14.7和MATLAB13a。

2017-12-26 21:51:55

用quartus ii 中自帶的ip核創(chuàng)建了一個rom,并加載了初始的hex數(shù)據(jù)。當我從rom中讀出數(shù)據(jù)的時候,發(fā)現(xiàn)前面兩個地址(0000,0001)的輸出數(shù)據(jù)不正確,0002輸出數(shù)據(jù)是地址0000對應的數(shù)據(jù),即地址偏移了2位,請教給位大蝦這是怎么回事?應該如何解決?

2013-05-14 14:38:21

我在電子發(fā)燒友上看了小梅哥的fpga學習視頻。看到rom那一節(jié)時,我按照視頻講解的方式調(diào)用了一個rom的ip核,編寫了testbench文件。但是,得到的仿真結(jié)果rom中的數(shù)據(jù)全是0,mif文件沒有問題,已經(jīng)設(shè)置好了,請問問題出在哪里?求各位大神指教

2018-03-07 11:31:24

`最近做仿真需要用到Quartus ii里的ROM IP核,為了驗證功能,我新建了工程,生成IP核,數(shù)據(jù)深度512,位寬8bit,用MATLAB產(chǎn)生512個隨機整數(shù),新建hex文件,將512個隨機數(shù)

2015-12-22 23:14:53

本帖最后由 Laputa_fly 于 2013-11-23 13:46 編輯

用quartus9.0調(diào)用了altera FFT IP 核 生成了modisim 和 matlab 的仿真文件。用modelsim 仿真有結(jié)果。但是按照官方的使用說明用matlab仿真時出現(xiàn)問題。請大家?guī)兔鉀Q一下。謝謝!

2013-11-23 13:43:41

最近在做一個FIR低通濾波器,利用Matlab 產(chǎn)生濾波系數(shù),導入到Quartus中,再利用其中的FIR IP核進行濾波器設(shè)計,在采用分布式全并行結(jié)構(gòu)時,Modelsim 仿真有輸出;如果改為分布式

2018-07-05 08:33:02

最近進行FPGA學習,使用FIR濾波器過程中出現(xiàn)以下問題:使用FIR濾波器IP核中,輸入數(shù)據(jù)為1~256,濾波器系數(shù)為,coef =-1469,-14299 ,-2185,10587

2018-11-02 17:17:57

FPGA片內(nèi)ROM,并產(chǎn)生FPGA片內(nèi)ROM讀地址,定時遍歷讀取ROM中的數(shù)據(jù);此外,圖中未示意,該工程實例還包括了SignalTapII的IP核模塊,該模塊引出ROM的讀取信號總線,可以在線查看ROM讀取時序。 圖9.20 ROM實例模塊互聯(lián)接口 `

2018-06-16 19:39:24

嗨,我想在EDK中使用ISE中提供的PCI Express IP核,這意味著我應該將所有ISE IP核的verilog模塊導入EDK。這是可能的,如果可能的話請發(fā)送相關(guān)文件。謝謝&問候,Madhu.B

2020-03-24 08:14:50

飛舞,這里就不贅述了,以免有湊字數(shù)的嫌疑。下面我們就Matlab和FPGA兩個工具雙管齊下,比對Vivado的FFT IP核生成的數(shù)據(jù)。2 Matlab產(chǎn)生測試數(shù)據(jù),繪制cos時域和頻域波形

2019-08-10 14:30:03

受到業(yè)內(nèi)人士的青睞。本文在分析OpenCores網(wǎng)站提供的一款OC8051IP核的基礎(chǔ)上,給出了一種仿真調(diào)試方案;利用該方案指出了其中若干邏輯錯誤并對其進行修改,最終完成了修改后IP核的FPGA下載測試。

2019-07-04 06:02:19

核的分類和特點是什么?基于IP核的FPGA設(shè)計方法是什么?

2021-05-08 07:07:01

現(xiàn)有基于candence的AD的模擬電路,還有在ISE上用Verilog寫的51單片機的IP核,怎樣將AD掛載到51上進行仿真呀,謝謝各位大蝦!!!

2012-07-13 15:45:11

入RAM。本實驗將為大家介紹如何使用FPGA內(nèi)部的ROM以及程序?qū)υ?b class="flag-6" style="color: red">ROM的數(shù)據(jù)讀操作。1.實驗原理Xilinx在VIVADO里為我們已經(jīng)提供了ROM的IP核, 我們只需通過IP核例化一個ROM,根據(jù)

2021-01-07 15:48:39

本文在分析OpenCores網(wǎng)站提供的一款OC8051IP核的基礎(chǔ)上,給出了一種仿真調(diào)試方案;利用該方案指出了其中若干邏輯錯誤并對其進行修改,最終完成了修改后IP核的FPGA下載測試。

2021-05-08 06:22:32

本人現(xiàn)在有基于candence的10位AD模擬電路,怎樣能轉(zhuǎn)換成類似IP核的東西,整合到ISE工程中,給點思路,謝謝各位大神!

2012-07-13 20:40:36

本帖最后由 tony歐 于 2016-6-3 13:36 編輯

我用ISE編寫的工程,如果涉及ROM IP核,第一次仿真時是完全好使的,輸出端能輸出波形。但是當我關(guān)電腦,重啟再次打開這個工程時,仿真輸出端就變成了ZZZZZ,請問這個是什么原因啊。。很急很急。。

2016-06-03 13:17:15

ISE中自帶的乘法器IP核如何設(shè)置延時2個時鐘周期?為什么我生成的時候沒有l(wèi)atency這個選項,生成后的xco文件中貌似也沒有延時,但是生成的vhd文件中卻有這么一句“c_latency =>

2015-03-28 12:16:31

Vivado的FFT IP核生成的數(shù)據(jù)。 2 Matlab產(chǎn)生測試數(shù)據(jù),繪制cos時域和頻域波形使用projectzstar_ex67matlab文件夾下的Matlab源碼fft_1line.m,運行產(chǎn)生1組

2020-01-07 09:33:53

沒用過ISE,不知道生成的IP核文件夾中 ,哪些是需要添加到modelsim中用于仿真的文件 。拿ram舉例,仿真庫文件還應該添加哪些內(nèi)容。希望大神們指導下 多謝

2018-12-18 17:58:32

本文設(shè)計了一種基于 FPGA 的UART 核,該核符合串行通信協(xié)議,具有模塊化、兼容性和可配置性,適合于SoC 應用。設(shè)計中使用Verilog HDL 硬件描述語言在Xilinx ISE 環(huán)境下進行設(shè)計、仿真,

2009-11-27 15:48:51 20

20 FPGA設(shè)計開發(fā)軟件ISE使用技巧

本章目標熟悉 ISE 軟件的安裝與啟動掌握 ISE 下FPGA的設(shè)計流程掌握 ISE 下創(chuàng)建工程的方式掌握 ISE 下如何編譯和仿真掌

2010-02-09 09:32:29 121

121 mif文件的創(chuàng)建與使用是在基于FPGA的系統(tǒng)設(shè)計中引入ROM的關(guān)鍵環(huán)節(jié)。對mif文件的創(chuàng)建與使用展開詳細討論,給出兩種可行性方法,并引入實例在MAX+PLUS Ⅱ環(huán)境下做了詳細的仿真

2010-12-13 17:47:29 42

42 以Altera公司的Quartus Ⅱ 7.2作為開發(fā)工具,研究了基于FPGA的DDS IP核設(shè)計,并給出基于Signal Tap II嵌入式邏輯分析儀的仿真測試結(jié)果。將設(shè)計的DDS IP核封裝成為SOPC Builder自定義的組件,結(jié)合

2012-04-05 16:04:34 85

85 FPGA中IP核的生成,簡單介紹Quartus II生成IP核的基本操作,簡單實用挺不錯的資料

2015-11-30 17:36:15 12

12 利用FPGA的IP核設(shè)計和實現(xiàn)FFT算法

2016-05-24 14:14:47 37

37 在ISE中打開以前做的一個工程時,總是不停地提示 INFO:sim:760 - You can use the CORE Generator IP upgrade flow to upgrade

2017-02-11 10:58:52 4772

4772

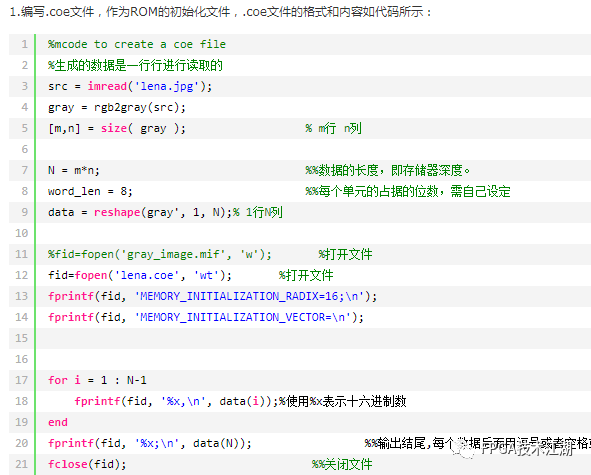

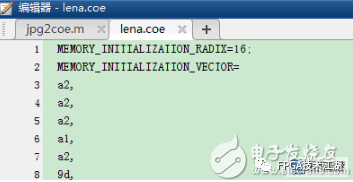

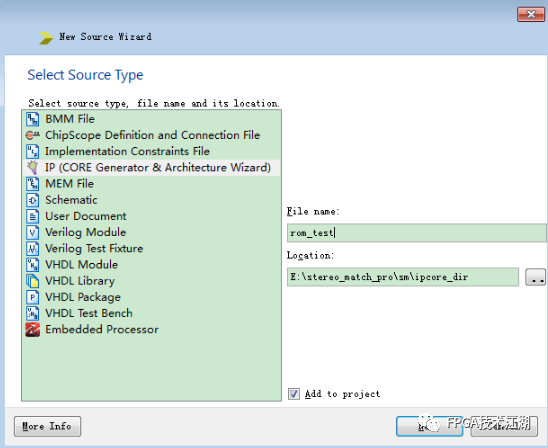

大家好,又到了每日學習的時間了,今天我們來聊一聊使用matlab和ISE 創(chuàng)建并仿真ROM IP核。本人想使用簡單的中值濾波進行verilog相關(guān)算法的硬件實現(xiàn),由于HDL設(shè)計軟件不能直接處理圖像

2018-10-25 20:20:35 4559

4559

介紹了在大型工業(yè)模擬仿真系統(tǒng)中,利用FPGA和軟IP核實現(xiàn)數(shù)據(jù)采集及收發(fā)控制的方案,并對其進行設(shè)計實現(xiàn)。重點闡述了在發(fā)送指令和采集接收兩種數(shù)據(jù)流模式下.該IP核的控制處理邏輯及工作狀態(tài)機的設(shè)計及實現(xiàn)

2018-11-07 11:14:19 20

20 該篇不僅講解了如何使用Quartus II軟件、ModelSim和SignalTap II軟件,還講解了PLL、ROM、RAM和FIFO IP核的使用。從第一個新工程建立,管腳分配,程序下載及工程

2019-12-06 07:04:00 5745

5745

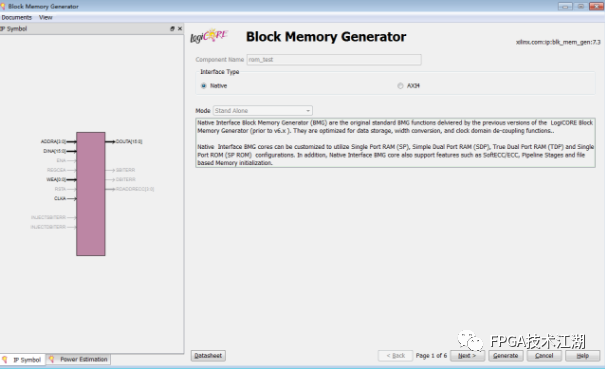

? Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數(shù)學類的IP核,數(shù)字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM ?IP核

2020-12-29 15:59:39 13270

13270 本講使用matlab產(chǎn)生待濾波信號,并編寫testbench進行仿真分析,在Vivado中調(diào)用FIR濾波器的IP核進行濾波測試,下一講使用兩個DDS產(chǎn)生待濾波的信號,第五講或第六講開始編寫verilog代碼設(shè)計FIR濾波器,不再調(diào)用IP核。

2021-04-27 18:18:51 5091

5091

在FPGA實際的開發(fā)中,官方提供的IP并不是適用于所有的情況,需要根據(jù)實際修改,或者是在自己設(shè)計的IP時,需要再次調(diào)用時,我們可以將之前的設(shè)計封裝成自定義IP,然后在之后的設(shè)計中繼續(xù)使用此IP。因此本次詳細介紹使用VIvado來封裝自己的IP,并使用IP創(chuàng)建工程。

2022-04-21 08:58:05 7941

7941 今天介紹的是vivado的三種常用IP核:時鐘倍頻(Clocking Wizard),實時仿真(ILA),ROM調(diào)用(Block Memory)。

2023-02-02 10:14:01 5002

5002 在仿真Vivado IP核時分兩種情況,分為未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 2875

2875

仿真和驗證是開發(fā)任何高質(zhì)量的基于FPGA的RTL編碼過程的基礎(chǔ)。在上一篇文章中,我們介紹了面向?qū)嶓w/塊的仿真,即通過在每個輸入信號上生成激勵并驗證RTL代碼行為是否符合預期,對構(gòu)成每個IP核

2022-06-15 17:31:20 1373

1373

FPGA開發(fā)過程中,利用各種IP核,可以快速完成功能開發(fā),不需要花費大量時間重復造輪子。

2023-08-07 15:43:19 1992

1992

,一旦寫入不能再修改或刪除,斷電不丟失。我們知道FPGA只有RAM,因此事實上在 FPGA 中通過 IP 核生成的 ROM 或 RAM掉電內(nèi)容都會丟失。用 IP 核生成的 ROM 模塊只是提前添加

2023-08-22 15:06:38 7616

7616

Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數(shù)學類的IP核,數(shù)字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 3291

3291 本文介紹了Vidado中FFT IP核的使用,具體內(nèi)容為:調(diào)用IP核>>配置界面介紹>>IP核端口介紹>>MATLAB生成測試數(shù)據(jù)>>測試verilogHDL>>TestBench仿真>>結(jié)果驗證>>FFT運算。

2024-11-06 09:51:43 5640

5640

電子發(fā)燒友App

電子發(fā)燒友App

評論