對于基于鎖存器的設計,靜態時序分析會應用一個稱為時間借用的概念。本篇博文解釋了時間借用的概念,若您的設計中包含鎖存器且時序報告中存在時間借用,即可適用此概念。

2025-12-31 15:25:51 4740

4740

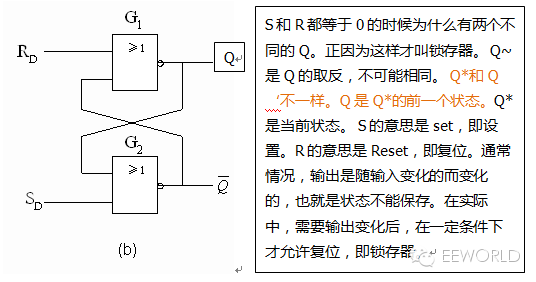

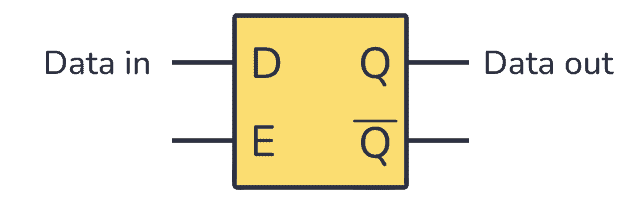

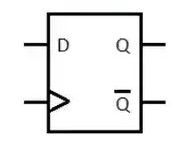

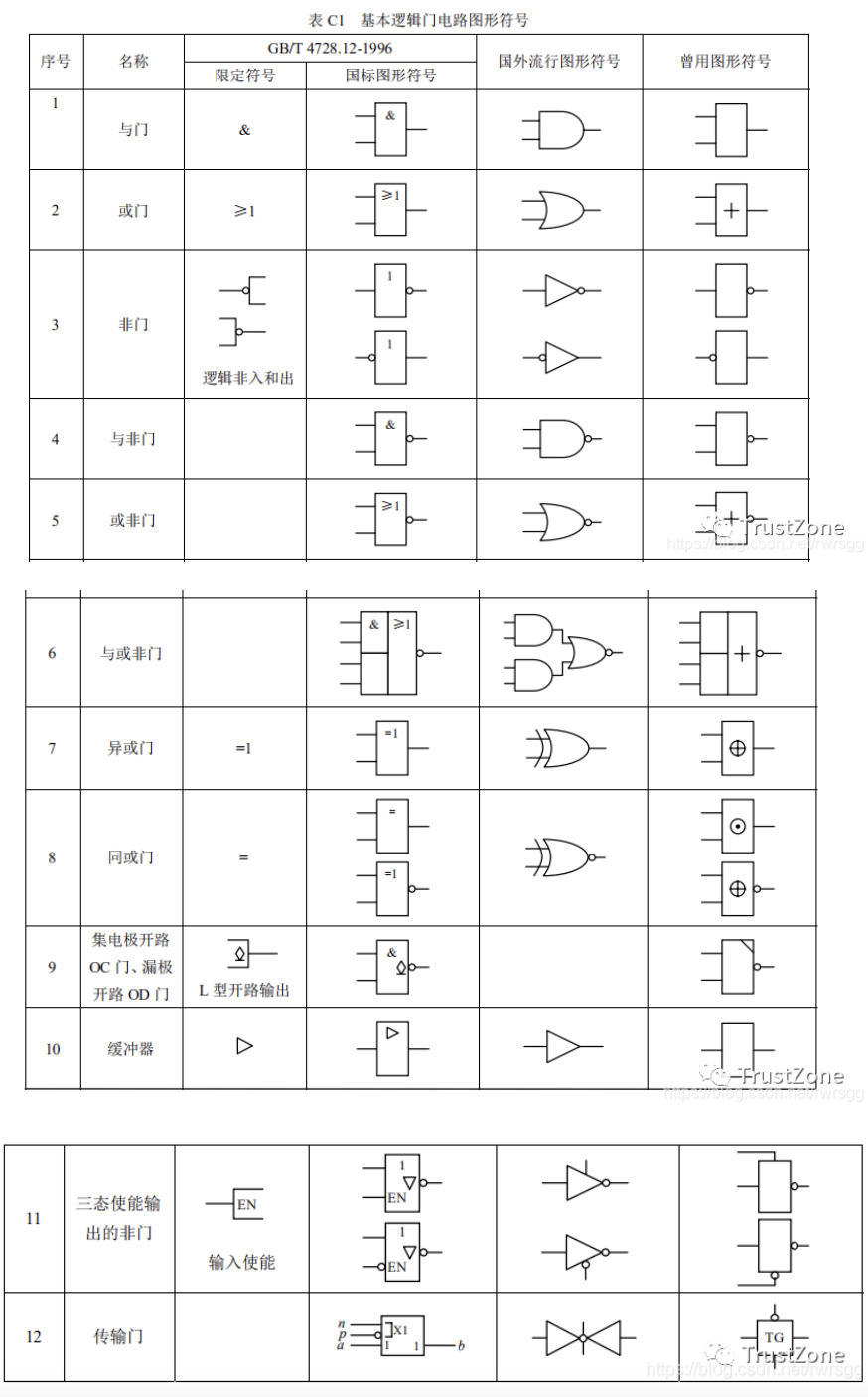

所謂鎖存器,就是輸出端的狀態不會隨輸入端的狀態變化而變化,僅在有鎖存信號時輸入的狀態被保存到輸出,直到下一個鎖存信號到來時才改變。典型的鎖存器邏輯電路是 D 觸發器電路。 PS:鎖存信號(即對LE賦高電平時Data端的輸入信號)。鎖存,就是把信號暫存以維持某種電平狀態。

2017-10-30 14:35:53 63605

63605

鎖存器辨析所謂鎖存器,就是輸出端的狀態不會隨輸入端的狀態變化而變化,僅在有鎖存信號時輸入的狀態被保存到輸出,

2017-10-31 06:04:00 13295

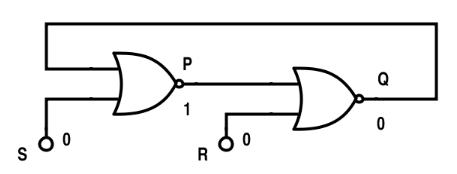

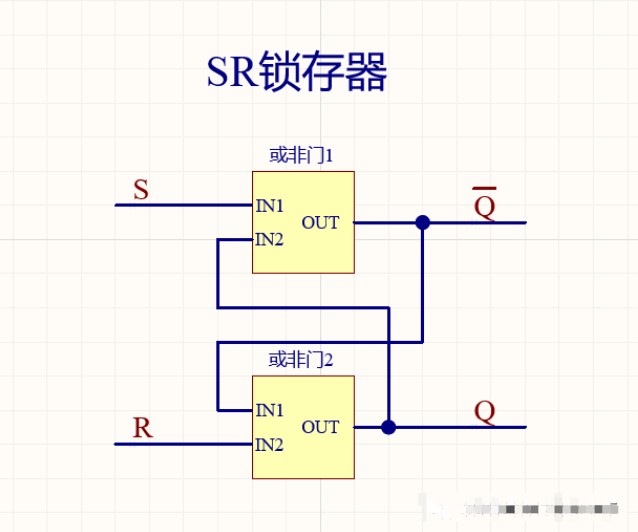

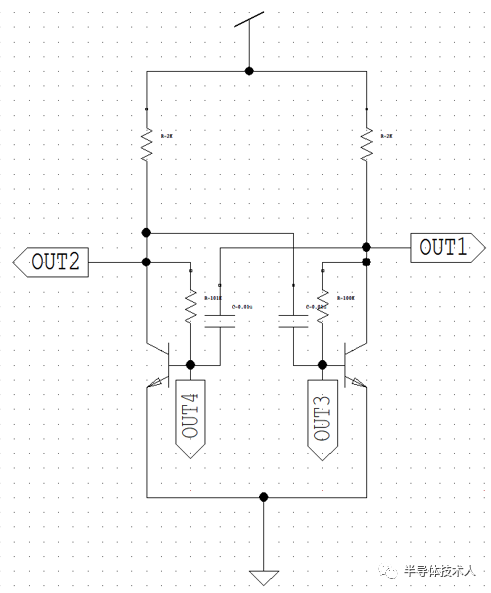

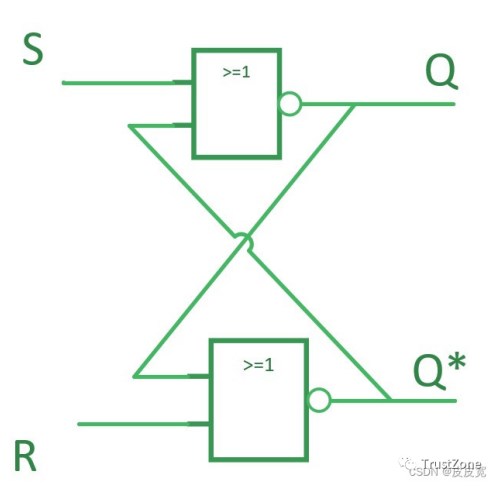

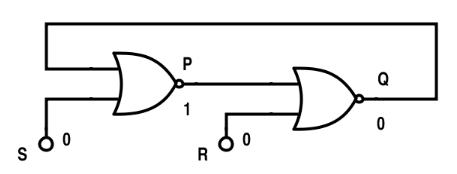

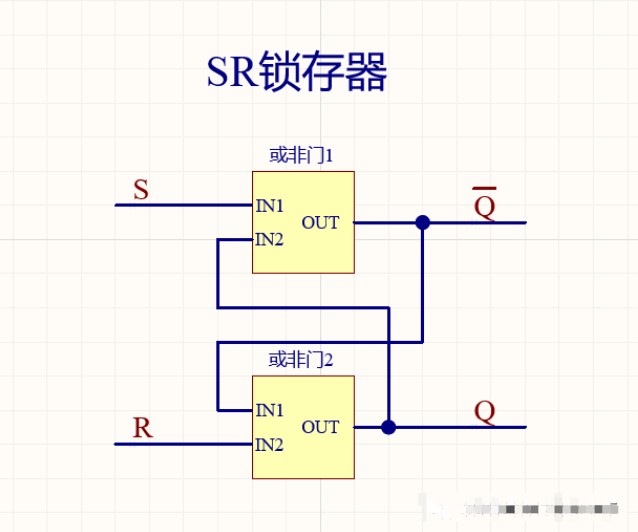

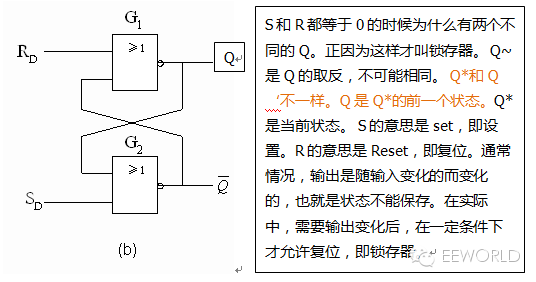

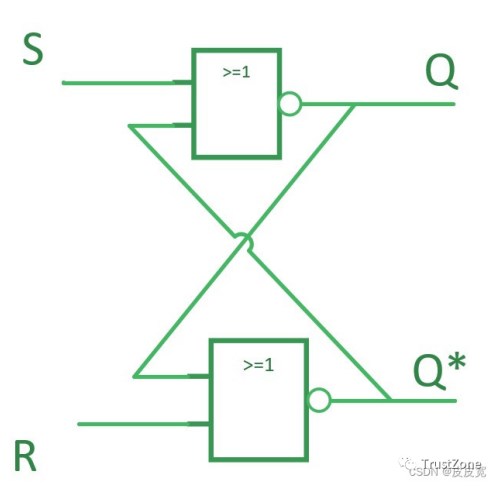

13295 一、SR鎖存器 1、RS鎖存器的電路結構及工作原理 RS鎖存器是一兩輸入、兩輸出的電路,其電路如圖1(a),其有兩個互相交叉反饋相連的兩個與非門構成,其兩個輸出為兩個相反的輸出(或稱為互補輸出),圖

2020-10-07 15:24:00 53206

53206

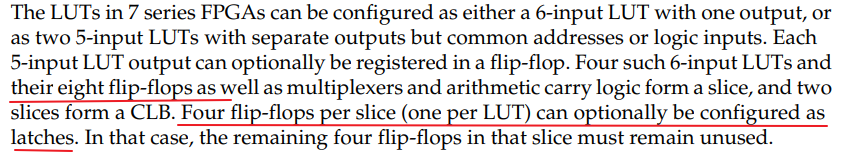

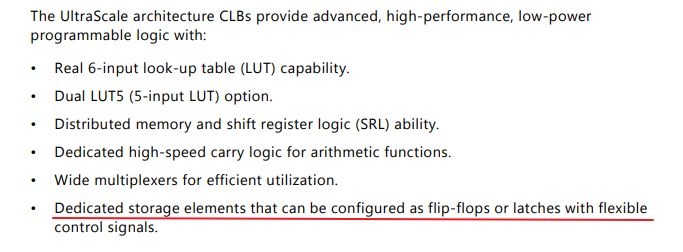

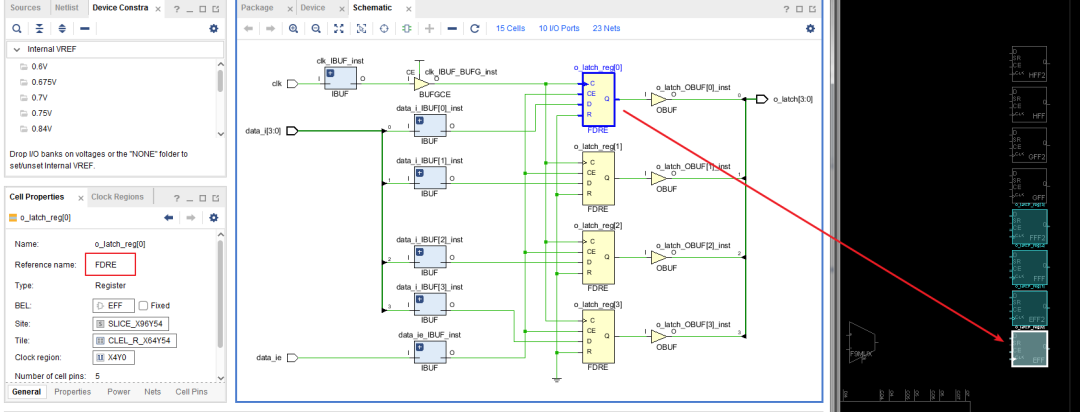

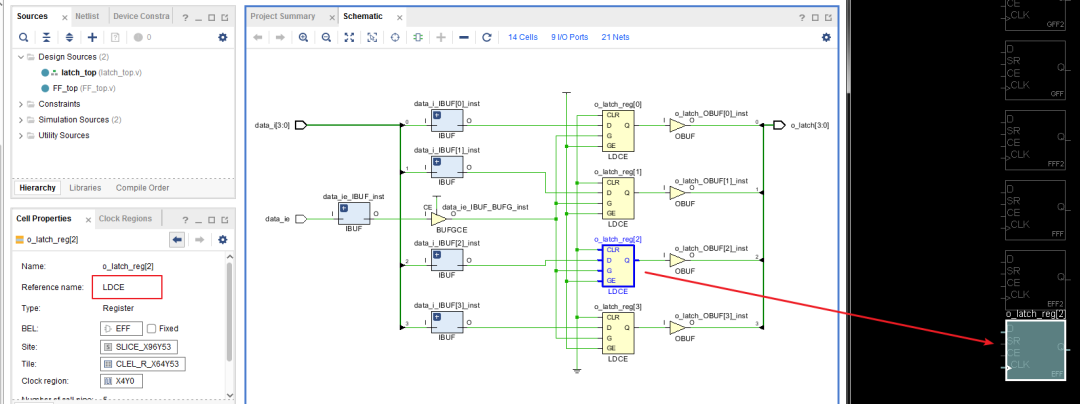

前言 在FPGA的設計中,避免使用鎖存器是幾乎所有FPGA工程師的共識,Xilinx和Altera也在手冊中提示大家要慎用鎖存器,除非你明確知道你確實需要一個latch來解決問題。而且目前網上大多數

2020-11-16 11:42:00 9314

9314

鎖存器是具有兩個穩定狀態的時序邏輯電路,即它是雙穩態多諧振蕩器。鎖存器有一個反饋路徑來保留信息。因此,鎖存器可以是存儲設備。只要設備處于開機狀態,鎖存器就可以存儲一位信息。當使能啟用時,鎖存器會在輸入更改時立即更改存儲的信息,即它們是電平觸發設備。當使能信號打開時,它會持續對輸入進行采樣。

2022-09-12 16:13:00 12306

12306

上學時,老師說判斷語句要把條件寫全, **不然會生成鎖存器,做項目時又說多比特寄存器信號的賦值一定要加if條件,不讓出現else的賦值** 。就很矛盾,本文主要講下什么是鎖存器,**什么情況下會出現鎖存器,以及鎖存器的危害。**

2023-11-09 12:28:31 2856

2856

說明rs鎖存器的思想來源,或者說怎么想起來,求具體過程,即一步一步的過程

2013-10-13 09:38:12

請問,鎖存器的工作原理是什么?

2013-10-15 19:35:26

,數據信號后到。在某些運算器電路中有時采用鎖存器作為數據暫存器。缺點:時序分析較困難。不要鎖存器的原因有二:1、鎖存器容易產生毛刺,2、鎖存器在ASIC設計中應該說比ff要簡單,但是在FPGA的資源中

2011-10-09 16:19:46

鎖存器的工作原理是什么?鎖存器的動態特性及其應用有哪些?觸發器的工作原理是什么?觸發器的電路結構是如何構成的?

2021-11-03 06:48:50

鎖存器和觸發器1.什么情況要用到鎖存器?狀態不能保持?現在的單片機狀態都是可以保持的吧2.看到很多產品用施密特觸發器作為門極驅動器(柵極驅動器),是隔離的作用還是其他?這種觸發器和專用的門極驅動器有哪些異同

2022-03-10 17:52:14

數碼管的動態顯示截取了部分程序,使用了74hc573鎖存器,但是我覺得去掉鎖存器程序照樣可以執行,那么這里使用鎖存器的意義是什么呢?還是說只是用一下沒有什么特殊的含義? for( i=0; i

2013-03-11 16:59:52

數碼管的動態顯示截取了部分程序,使用了74hc573鎖存器,但是我覺得去掉鎖存器程序照樣可以執行,那么這里使用鎖存器的意義是什么呢?還是說只是用一下沒有什么特殊的含義?

for( i=0

2023-10-26 07:18:07

的處理時間,消耗了處理器的處理能力,還浪費了處理器的功耗。 鎖存器的使用可以大大的緩解處理器在這方面的壓力。當處理器把數據傳輸到鎖存器并將其鎖存后,鎖存器的輸出引腳便會一直保持數據狀態直到下一次鎖存

2011-03-26 20:41:22

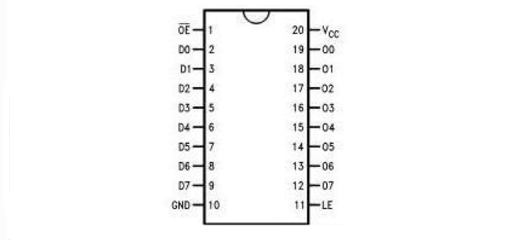

P0口作為分時復用接口,既要作為數據總線口,又要作為地址總線口 輸出的低8位地址需要用8位鎖存器鎖存 ALE的下降沿將P0口輸出的低8位地址鎖存? 對于鎖存器:○ /OE為輸出使能端 § /OE有效

2021-12-13 08:23:27

前言在學習了基本鎖存器原理后,剩下就是對各個外設以及對單片機寄存器的相關學習,如果沒有看過之前對鎖存器原理的講解的同學,可以回看一下。藍橋杯基礎教程之鎖存器操作(非常重要!)學習藍橋杯必看

2021-12-03 08:05:27

ASIC設計中應該說比ff要簡單,但是在FPGA的資源中,大部分器件沒有鎖存器這個東西,所以需要用一個邏輯門和ff來組成鎖存器,這樣就浪費了資源。優點:面積小。鎖存器比FF快,所以用在地址鎖存是很合適

2019-04-23 03:35:28

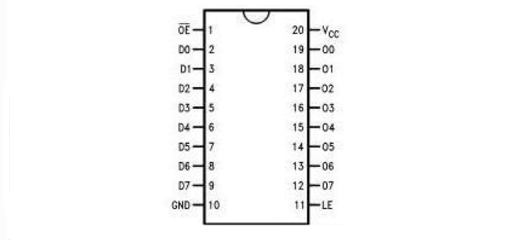

未知未能而求知求能謂之學;已知已能而行之不已謂之習;溫故而知新;故寫而記之;鎖存器74HC373:在學習和使用過程中,一般將OC直接接地,當LE為高時,此時將鎖存器引腳打開;當LE為低時,此時將鎖存器引腳關閉;其他引腳正常連接;//寫該文章僅僅只為將學過的知識學之,習之。...

2021-12-06 07:24:22

關于鎖存器問題的討論很多同學提問到鎖存器的相關問題,說明大家對這方面知識還不是很了解,今天我們就來探討一下。上面是兩個沒有else的代碼,其等效于下面的代碼。也就是說,當if條件里面沒有寫else

2020-03-02 00:25:31

光立方必須是74ALS573這種鎖存器嗎?我現在有這種74hc373d的鎖存器能用嗎?

2013-11-22 00:18:53

本帖最后由 xvjiamin 于 2021-9-26 20:46 編輯

如圖,在編寫TDC延時鏈的時候,結果通過D觸發器做鎖存。但是出現了紅色的不定態,這是為什么?該怎么解決呢?可以看到,信號

2021-09-26 20:46:03

哪位高手可以詳細講解下段鎖存和位鎖存的原理和用法?!!!!!!{:23:}

2013-04-26 21:43:16

經常看到各種寫HDL代碼時說要避免生成鎖存器,但是在某些情況,我不關心那種情況即使它生成了鎖存器,對我的工程實現也沒有什么影響啊,想請教下各位大神,既然這樣,為什么還要避免生成鎖存器(if和case

2018-01-08 23:54:39

邏輯可構成時序邏輯電路,簡稱時序電路。現在討論實現存儲功能的兩種邏輯單元電路,即鎖存器和觸發器。雙穩態:電子電路中。其雙穩態電路的特點是:在沒有外來觸發信號的作用下,電路始終處于原來的穩定狀態。在外

2016-05-21 06:50:08

你好什么是FPGA IO引腳的扇出....我正在使用LVTTL 3.3信號電平...我想將FPGA連接到比較器的鎖存信號....我有32個比較器需要從FPGA給出鎖存信號....問候,維諾德

2020-06-02 14:22:53

暫存器。缺點:時序分析較困難。不要鎖存器的原因:1、鎖存器容易產生毛刺,2、鎖存器在ASIC設計中應該說比ff要簡單,但是在FPGA的資源中,大部分器件沒有鎖存器這個東西,所以需要用一個邏輯門和ff來組成

2018-07-03 11:50:27

`請問鎖存器下面3個針腳怎么接線?`

2014-12-28 15:45:25

位鎖存和段鎖存的區別是什么怎么用

2014-03-01 10:49:27

怎樣處理單片機與鎖存器的關系? 為何要用串行口擴展 I/O?

2017-03-13 23:43:07

預放大鎖存比較器是什么工作原理?運放鎖存器的電路結構分析如何使用Spectre預放大鎖存比較器進行仿真?

2021-04-08 06:56:02

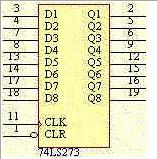

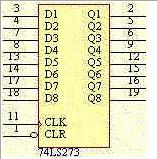

地址鎖存器--74LS273

74LS273是帶清除端的八D觸發器,只有清除端為高電平時才具有鎖存功能,鎖存控制端為11腳CLK,在上升沿鎖存。單片機的ALE端輸出的鎖存控制信號必須經反

2009-03-14 15:37:57 5418

5418

鎖存器,鎖存器是什么意思

鎖存器定義一位鐘控D觸發器只能傳送或存儲一位二進制數據,而在實際工作中往往是一次傳送或存

2010-03-09 09:44:12 12791

12791 鎖存器和緩沖器的作用是什么?

鎖存器廣泛用于計算機與數字系統的輸入緩沖電路,其作用是將輸入信號暫時寄存,等待處理,這一方

2010-03-09 09:48:02 25567

25567 地址鎖存器,地址鎖存器是什么意思

地址鎖存器就是一個暫存器,它根據控制信號的狀態,將總線上地址代碼暫存起來。8086/8088數

2010-03-09 09:49:49 5250

5250 鎖存器的原理分析

鎖存器就是把單片機的輸出的數先存起來,可以讓單片機繼續做其它事.. 比如74HC373就是一種鎖存器 它的LE為高

2010-03-09 09:54:52 67812

67812 SL74hc573中文資料(三態輸出的八D透明鎖存器),原理圖及各篇573詳細介紹。

2015-12-31 14:26:51 25

25 鎖存器(latch)---對脈沖電平敏感,在時鐘脈沖的電平作用下改變狀態 鎖存器是電平觸發的存儲單元,數據存儲的動作取決于輸入時鐘(或者使能)信號的電平值,僅當鎖存器處于使能狀態時,輸出才會隨著數據輸入發生變化。

2017-11-02 09:24:41 95604

95604

鎖存器(Latch)是一種對脈沖電平敏感的存儲單元電路,它們可以在特定輸入脈沖電平作用下改變狀態。鎖存,就是把信號暫存以維持某種電平狀態。鎖存器的最主要作用是緩存,其次完成高速的控制器與慢速的外設的不同步問題

2018-01-31 13:57:22 12766

12766

本文開始介紹了什么是鎖存器與鎖存器的工作原理,其次介紹了鎖存器的作用與鎖存器的應用實例,最后介紹了常用74系列鎖存器芯片介紹。

2018-01-31 16:30:53 84093

84093

本文首先介紹了鎖存器的工作原理,其次闡述了鎖存器的作用,最后闡述了鎖存器應用場合。

2018-08-21 18:57:52 92125

92125 當復位輸入為假且鎖存輸入為真時,輸出為真。無論鎖存器輸入如何,輸出仍然是真實的,直到復位輸入為真。

2019-02-11 08:00:00 6

6 鎖存器(有時也稱為S/R鎖存器)是最小的存儲器塊。它們可以使用兩個NOR邏輯門(S和R為高電平有效)或兩個NAND門(輸入為低電平有效)構建,并用于構建更復雜的鎖存器和觸發器。

2019-07-30 11:23:28 7316

7316

鎖存器是一種在異步時序電路系統中,對輸入信號電平敏感的單元,用來存儲信息。一個鎖存器可以存儲1bit的信息,通常,鎖存器會多個一起出現,如4位鎖存器,8位鎖存器。

2020-10-05 14:28:00 11246

11246 作者:電子工程師小李 1)鎖存器 鎖存器(latch)是電平觸發的存儲單元,數據存儲的動作取決于輸入時鐘(或者使能)信號的電平值,僅當鎖存器處于使能狀態時,輸出才會隨著數據輸入發生變化。 簡單地說

2020-11-29 11:02:11 26376

26376 未知未能而求知求能謂之學;已知已能而行之不已謂之習;溫故而知新;故寫而記之;鎖存器74HC373:在學習和使用過程中,一般將OC直接接地,當LE為高時,此時將鎖存器引腳打開;當LE為低時,此時將鎖存器引腳關閉;其他引腳正常連接;//寫該文章僅僅只為將學過的知識學之,習之。...

2021-11-23 18:06:42 6

6 P0口作為分時復用接口,既要作為數據總線口,又要作為地址總線口 輸出的低8位地址需要用8位鎖存器鎖存 ALE的下降沿將P0口輸出的低8位地址鎖存? 對于鎖存器: ○ /OE為輸出使能端 § /OE

2021-11-26 20:51:04 13

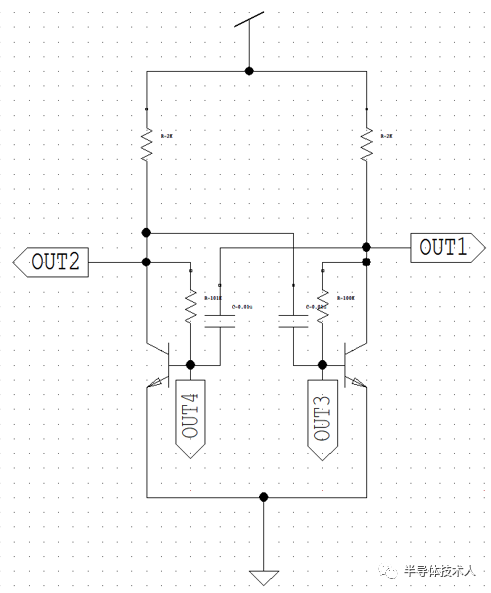

13 在ASIC中用到鎖存器的地方很多,Time Borrowing是使用鎖存器的典型應用之一,在深度流水線的設計中可以極大地提高處理性能。另外鎖存器和寄存器相比能夠顯著的減小面積:寄存器占用的硅片面積是鎖存器的兩倍,在ASIC設計中一個典型的主從寄存器是由兩個鎖存器級聯來實現的。

2022-06-14 16:56:44 2633

2633 作為電路設計者,鎖存器很多場合都會用到,今天和大家分析一下SR鎖存器的原理。

2022-08-20 17:30:23 7980

7980

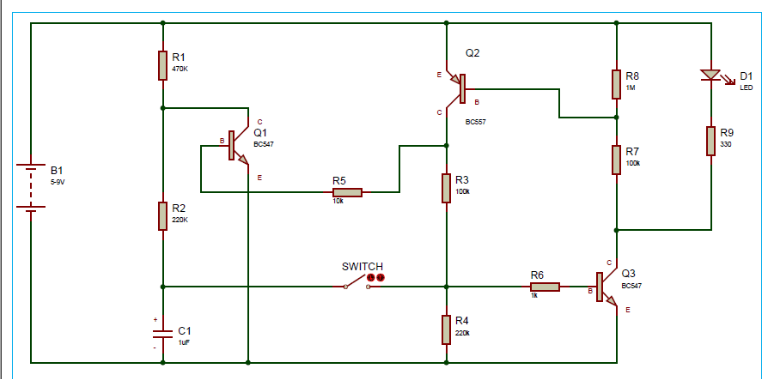

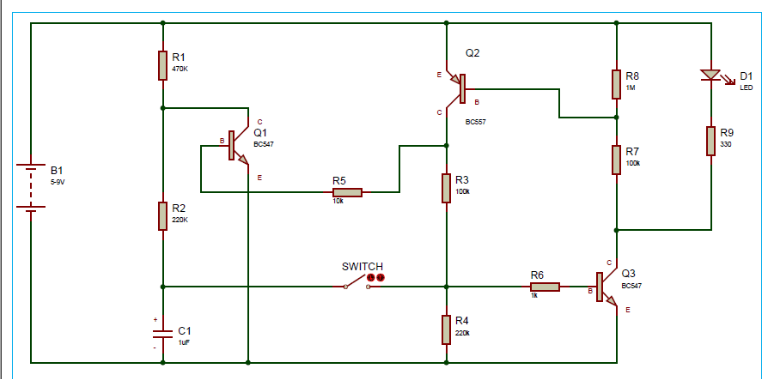

在這個項目中,我們將制作一個軟鎖存電路,通過按一個按鈕來打開和關閉電子設備。該電路稱為軟鎖存開關。軟鎖存電路與普通鎖存電路不同,在軟鎖存器中,可以使用外部手段(按鈕)改變開啟和關閉狀態,但在普通鎖存

2022-08-25 16:32:47 6418

6418

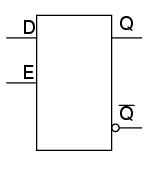

鎖存器(Latch)是數字邏輯電路中很重要的一種基本電路,常見的鎖存器包括三個端口:數據輸入口、數據輸出口、使能端。當使能端為高電平時,輸入口的數據直接送到輸出口,此時輸入輸出口可以看成是直接

2023-02-09 21:05:05 3073

3073 用或非門組成的基本SR鎖存器。

2023-02-27 10:29:42 11262

11262

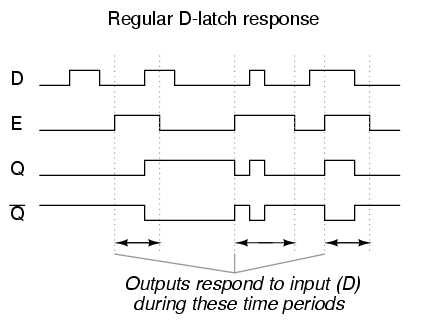

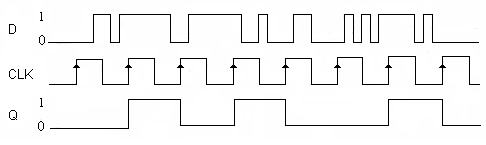

鎖存器(latch)---對脈沖電平敏感,在時鐘脈沖的電平作用下改變狀態,當Gate輸入為高電平時,輸入D透明傳輸到輸出Q;當Gate從高變低或者保持低電平時,輸出Q被鎖存保持不變。鎖存器是電平觸發的存儲器。

2023-03-23 14:48:54 4270

4270

鎖存器是構成各種時序電路的基本元件,它的特點是具有0和1兩種穩定的狀態,一旦狀態被確定,就能自行保持,即長期存儲1位的二進制碼,直到有外部信號作用時才有可能改變。鎖存器是一種對電平敏感的存儲單元電路,它們可以在特定輸入電平作用下改變狀態。

2023-03-23 16:03:32 2530

2530

鎖存器(Latch)是一種基本的數字電路元件,用于存儲二進制數字的狀態信息,并能夠在需要時通過加電或控制信號的作用保持狀態。它通常由幾個邏輯門組成,可以實現簡單的存儲、移位、計數等功能。鎖存器在數

2023-04-09 18:45:34 11494

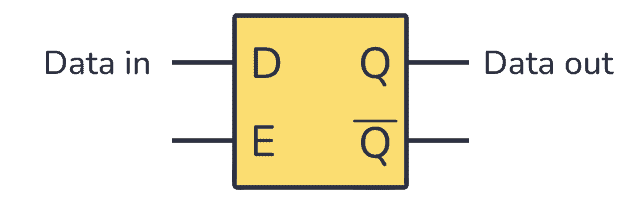

11494 D鎖存器是最常用于在數字系統中存儲數據的邏輯電路。它基于 S-R鎖存器,但沒有“未定義”或“無效”狀態問題。在本教程中,您將了解它的工作原理、其真值表以及如何使用邏輯門構建一個。

2023-06-29 14:14:03 12297

12297

鎖存器(Latch)是一種對脈沖電平敏感的存儲單元,它們可以在特定輸入脈沖電平作用下改變狀態。鎖存,就是把信號暫存以維持某種電平狀態。

2023-07-06 15:10:39 1882

1882

鎖存器的工作原理? 鎖存器(latch)是一種用于存儲和記憶數字信號的電路。它被廣泛用于計算機和數字電子電路中,用于實現內存存儲、寄存器和其他計算單元。 鎖存器的工作原理是通過反饋電路和放大

2023-12-08 11:18:03 9259

9259 數字IC設計里,常會出現鎖存器,D觸發器和寄存器,很多人(比如我)老傻傻分不清,搞不懂他們的區別是什么。

2024-02-17 15:04:00 3911

3911

在數字電子學中,鎖存器(Latch)和觸發器(Flip-Flop)是兩種基本的存儲元件,它們在數字系統中扮演著至關重要的角色。它們的主要功能是存儲和保持數據狀態,以供后續處理。然而,它們在實現方式

2024-07-23 10:16:31 1093

1093 鎖存器(Latch)是一種存儲電路,用于存儲一位二進制信息。鎖存器在數字電路設計中非常常見,它可以用來保持數據狀態、實現同步等功能。鎖存器的工作原理和觸發方式是數字電路設計的基礎之一。 1. 鎖存器

2024-07-23 10:17:50 1387

1387 在數字電路中,鎖存器和觸發器是兩種非常重要的存儲元件,它們在邏輯功能上有著明顯的區別。鎖存器和觸發器都是用于存儲二進制信息的基本元件,但它們在結構、工作原理、應用場景等方面都存在差異。 一、鎖存器

2024-07-23 10:19:20 1891

1891 鎖存器(Latch)是一種存儲單元,用于存儲一位二進制信息。在數字電路中,鎖存器是一種基本的存儲元件,廣泛應用于寄存器、計數器、觸發器等電路中。鎖存器的原態和新態是描述鎖存器狀態變化的兩個重要概念

2024-07-23 10:21:06 1532

1532 鎖存器電路概述 定義與功能 鎖存器(Latch)是數字電路中的一種基本存儲元件,用于存儲一個位(1或0)的狀態。它能夠在特定輸入脈沖電平作用下改變狀態,并保持該狀態直到下一個脈沖電平到來。鎖存器

2024-07-23 11:29:39 1072

1072 鎖存器(Latch)是一種在數字電路中廣泛使用的存儲元件,它能夠存儲一位二進制信息。鎖存器電路的觸發方式有很多種,包括同步觸發、邊沿觸發、電平觸發等。 一、鎖存器的基本概念 鎖存器是一種具有記憶功能

2024-07-23 11:31:06 1262

1262 鎖存器(Latch)是一種具有記憶功能的數字電路元件,用于存儲和保持數字信號的狀態。鎖存器在數字電路設計中扮演著重要的角色,廣泛應用于各種電子設備和系統中。本文將介紹鎖存器的組成、功能及應用。 一

2024-07-23 11:32:56 5355

5355 RS鎖存器和SR鎖存器是數字電路中兩種常見的存儲單元,它們在功能和應用上有一些區別。 RS鎖存器 RS鎖存器,即Reset-Set鎖存器,是一種具有兩個穩定狀態的存儲單元。它有兩個輸入端,分別

2024-07-23 14:15:52 2982

2982 鎖存器(latch)是數字電路中的一種基本存儲單元,用于存儲和保持一個或多個位的狀態。鎖存器在數字邏輯設計中扮演著重要的角色,它們可以用于實現各種功能,如數據存儲、信號同步、狀態保持等。 鎖存器

2024-08-28 09:09:00 2433

2433 鎖存器(Latch)是一種存儲設備,用于在數字電路中存儲和保持數據。鎖存器的主要作用是將輸入信號的電平狀態保持一段時間,直到下一個輸入信號到來。鎖存器在數字電路設計中具有廣泛的應用,包括數據存儲

2024-08-28 09:11:46 2925

2925 D鎖存器是一種常見的數字邏輯電路,用于存儲一個二進制位的狀態。以下是一些常用的D鎖存器型號及其特點: 74LS74:這是一種低功耗的正觸發D鎖存器,具有4個獨立的鎖存器。它具有數據輸入、時鐘輸入

2024-08-28 09:13:51 2828

2828 D鎖存器(Data Latch)和SR鎖存器(Set-Reset Latch)是數字電路中常見的兩種存儲元件。它們在數字系統中扮演著重要的角色,用于存儲和傳遞信息。然而,這兩種鎖存器在設計和應用上

2024-08-28 09:16:42 1795

1795 在SR鎖存器中,輸出信息(Q和Q')是根據輸入信息(S和R)來確定的。SR鎖存器是一種雙穩態電路,它可以保持一個二進制狀態,直到輸入信號改變。以下是根據S和R的輸入信息判斷Q和Q'輸出的解釋: 1.

2024-08-28 09:20:15 1778

1778 常常見,尤其是在寄存器、計數器和其他存儲設備中。在這篇文章中,我們將詳細討論SR鎖存器的特性表、工作原理、應用和優缺點。 SR鎖存器特性表 SR鎖存器的特性表是一個表格,用于描述輸入信號與輸出狀態之間的關系。特性表通常包括四個部分:S(置位輸入)、R(復位輸入)、

2024-08-28 09:27:03 8985

8985 RS鎖存器的R和S端分別代表 Reset(復位) 和 Set(置位) 端。 R(Reset)端 功能 :當R端接收到有效信號(通常是低電平,但具體取決于鎖存器的實現方式,有時高電平也可能為有效信號

2024-08-28 10:25:27 2822

2822 RS鎖存器,也稱為RS觸發器,是一種具有兩個穩定狀態的電路,能夠存儲一位二進制數據。關于RS鎖存器中具體使用到的管子數量,這個問題實際上涉及到了電路設計的細節和復雜度,因為不同的RS鎖存器實現方式

2024-08-28 10:30:28 1126

1126 端口鎖存器和引腳是微控制器和數字電路中常見的概念,它們在硬件設計和編程中扮演著重要的角色。 端口鎖存器 端口鎖存器(Port Latch)是一種存儲數字信號的電路元件,它通常用于微控制器或數字電路中

2024-08-28 10:36:47 1656

1656 RS鎖存器(Reset-Set Latch)中的不定狀態,是指在特定輸入條件下,鎖存器的輸出狀態變得不確定或不可預測的現象。這種不定狀態主要源于RS鎖存器的輸入邏輯和電路特性,具體含義可以從以下幾個

2024-08-28 10:42:09 2088

2088 SR鎖存器是一種常見的數字邏輯電路,它具有保持信號狀態的功能。在設計和分析SR鎖存器時,我們需要了解其約束條件。 一、引言 在數字邏輯電路設計中,鎖存器是一種非常重要的組件。它能夠存儲一位二進制信息

2024-08-28 10:47:51 2312

2312 信號滿足一定的條件時,SR鎖存器可以將輸入信號存儲在內部,并通過輸出端將存儲的信息傳遞給其他電路。 保持功能 SR鎖存器具有保持功能,即在沒有輸入信號的情況下,它可以保持內部存儲的狀態不變。這種特性使得SR鎖存器在數字電路中具有廣

2024-08-28 10:55:56 2492

2492 時序邏輯電路本身并不直接“產生”鎖存器,但鎖存器是時序邏輯電路中的重要組成部分。時序邏輯電路(Sequential Logic Circuits)與組合邏輯電路(Combinational

2024-08-28 11:03:47 1319

1319 鎖存器(Latch)是數字電路中的一種重要組件,其工作時序對于理解其功能和在電路中的應用至關重要。鎖存器的工作原理主要基于電平敏感的特性,它能夠在特定輸入脈沖電平作用下改變狀態,將信號暫存以維持某種電平狀態。

2024-08-30 10:42:58 1997

1997 在深入探討鎖存器的輸出時序時,我們需要詳細分析鎖存器在不同控制信號下的行為表現,特別是控制信號(如使能信號E)的電平變化如何影響數據輸入(D)到輸出(Q)的傳輸過程。以下是對鎖存器輸出時序的詳細描述,旨在全面覆蓋其工作原理和時序特性。

2024-08-30 10:43:44 1767

1767 在Verilog HDL中實現鎖存器(Latch)通常涉及對硬件描述語言的基本理解,特別是關于信號如何根據控制信號的變化而保持或更新其值。鎖存器與觸發器(Flip-Flop)的主要區別在于,鎖存器

2024-08-30 10:45:03 2394

2394 鎖存器(Latch)作為數字電路中的一種基本存儲單元,具有對脈沖電平敏感的特性,能夠在特定條件下保持或更新其存儲的數據狀態。其技術參數是評估鎖存器性能、適用性和可靠性的重要指標。

2024-08-30 10:45:50 1744

1744

image

image image

image image

image image

image image

image image

image image

image image

image 電子發燒友App

電子發燒友App

評論