在SR鎖存器中,輸出信息(Q和Q')是根據(jù)輸入信息(S和R)來確定的。SR鎖存器是一種雙穩(wěn)態(tài)電路,它可以保持一個二進(jìn)制狀態(tài),直到輸入信號改變。以下是根據(jù)S和R的輸入信息判斷Q和Q'輸出的解釋:

1. 輸入情況與輸出關(guān)系

| S | R | Q | Q' | 功能描述 |

|---|---|---|---|---|

| 0 | 0 | 保持 | 保持 | 鎖存器保持當(dāng)前狀態(tài)不變 |

| 1 | 0 | 1 | 0 | 置位(Set),Q被設(shè)置為1 |

| 0 | 1 | 0 | 1 | 復(fù)位(Reset),Q被設(shè)置為0 |

| 1 | 1 | X | X | 非法狀態(tài),輸出不確定 |

注意 :在SR鎖存器中,S代表置位(Set),R代表復(fù)位(Reset)。Q和Q'是輸出端,其中Q'是Q的取反。當(dāng)S和R都為1時,SR鎖存器處于非法狀態(tài),因?yàn)榇藭r輸出狀態(tài)不確定,應(yīng)避免這種情況。

2. 工作原理

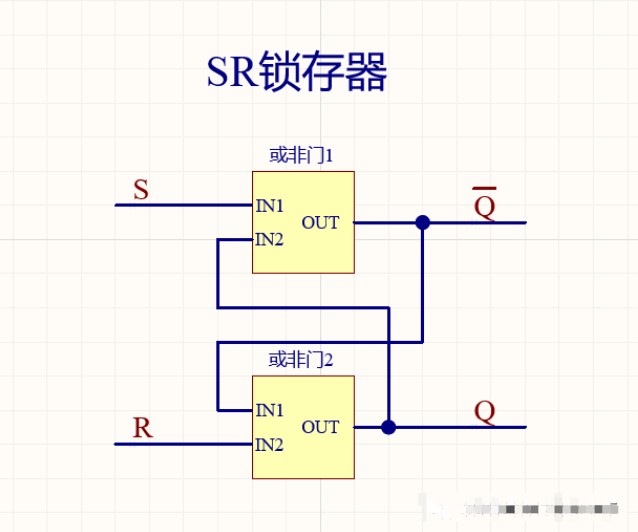

SR鎖存器通常由兩個或非門(NOR gate)或與非門(NAND gate)組成。以下以或非門組成的SR鎖存器為例說明其工作原理:

- 當(dāng)S=1且R=0時,不管Q的初始狀態(tài)如何,通過或非門的邏輯運(yùn)算,Q將被置為1,Q'被置為0,實(shí)現(xiàn)置位功能。

- 當(dāng)S=0且R=1時,不管Q的初始狀態(tài)如何,通過或非門的邏輯運(yùn)算,Q將被置為0,Q'被置為1,實(shí)現(xiàn)復(fù)位功能。

- 當(dāng)S=0且R=0時,鎖存器保持當(dāng)前狀態(tài)不變,即如果Q為1,則Q'為0;如果Q為0,則Q'為1。

- 當(dāng)S=1且R=1時,鎖存器處于非法狀態(tài),因?yàn)榇藭rQ和Q'的輸出不確定。為了避免這種情況,通常在設(shè)計時會加入額外的邏輯來確保S和R不會同時為1。

3. 實(shí)際應(yīng)用中的注意事項

- 在實(shí)際應(yīng)用中,應(yīng)避免S和R同時為1的非法狀態(tài),因?yàn)檫@會導(dǎo)致輸出不確定。

- SR鎖存器常用于需要記憶或鎖存數(shù)據(jù)的場合,如寄存器、計數(shù)器等數(shù)字電路中。

- 可以通過添加使能信號(Enable, En)來控制SR鎖存器的操作時機(jī),從而實(shí)現(xiàn)更靈活的數(shù)據(jù)鎖存和釋放功能。

綜上所述,SR鎖存器的輸出信息是根據(jù)輸入信息(S和R)來確定的,并且需要遵循特定的邏輯規(guī)則來避免非法狀態(tài)的出現(xiàn)。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

鎖存器

+關(guān)注

關(guān)注

8文章

956瀏覽量

44916 -

雙穩(wěn)態(tài)電路

+關(guān)注

關(guān)注

1文章

29瀏覽量

15351 -

SR

+關(guān)注

關(guān)注

1文章

38瀏覽量

24018 -

與非門

+關(guān)注

關(guān)注

1文章

141瀏覽量

13425

發(fā)布評論請先 登錄

相關(guān)推薦

熱點(diǎn)推薦

輸入信號消失 SR鎖存器如何實(shí)現(xiàn)存儲

“信號消失”,我估計指的是將S、R均置為0的意思。我有時也會說給某個輸入加個信號或者撤掉某個信號,指的是給這個輸入置1或置0。所以題主想問的是,為什么SR鎖

兩種SR鎖存器的約束條件

基本約束條件: SR鎖存器是一種基本的數(shù)字邏輯電路,用于存儲一位二進(jìn)制信息。它有兩個輸入端:S(

sr鎖存器不定狀態(tài)的產(chǎn)生原因

一、引言 SR鎖存器(Set-Reset Latch)是數(shù)字電路中的一種基本存儲元件,用于存儲一個比特(bit)的數(shù)據(jù)。它由兩個互補(bǔ)的門電路組成,通常是兩個非門(或非門、與非門)構(gòu)成,

SR鎖存器的特性表、工作原理及應(yīng)用

SR鎖存器(Set-Reset Latch)是一種基本的數(shù)字邏輯電路,用于存儲一位二進(jìn)制信息。它具有兩個穩(wěn)定狀態(tài):置位狀態(tài)(Set)和復(fù)位狀

sr鎖存器約束條件怎樣得出的

,并且能夠在輸入信號發(fā)生變化時保持其輸出狀態(tài)。SR鎖存器(Set-Reset Latch)是一種基本的鎖

SR鎖存器有約束項的原因

SR鎖存器由兩個交叉連接的反饋環(huán)組成,通常包含兩個邏輯門(如或非門或非門),通過控制輸入信號S(Set,置位)和R(Reset,復(fù)位)來控

SR鎖存器的Q非和Q*是什么關(guān)系

SR鎖存器是一種基本的數(shù)字邏輯電路,用于存儲一位二進(jìn)制信息。它由兩個觸發(fā)器(Set和Reset)

怎么根據(jù)sr鎖存器的輸入信息

怎么根據(jù)sr鎖存器的輸入信息

評論