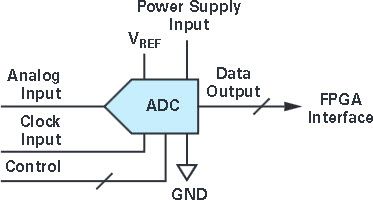

本文介紹FPGA與高速ADC接口方式和標準以及JESD204與FPGA高速串行接口。

2025-06-12 14:18:21 2881

2881

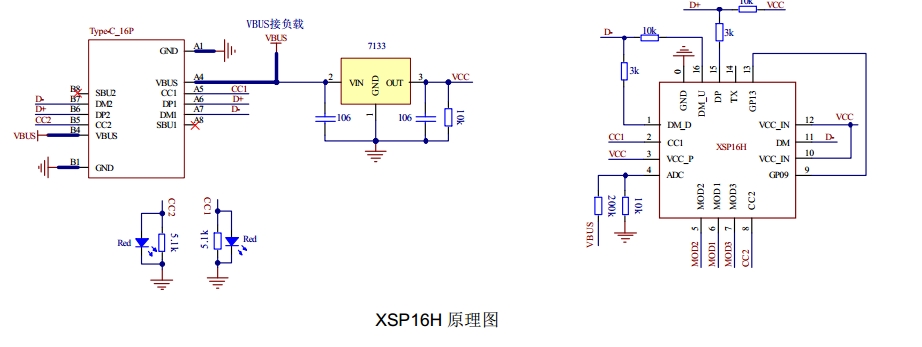

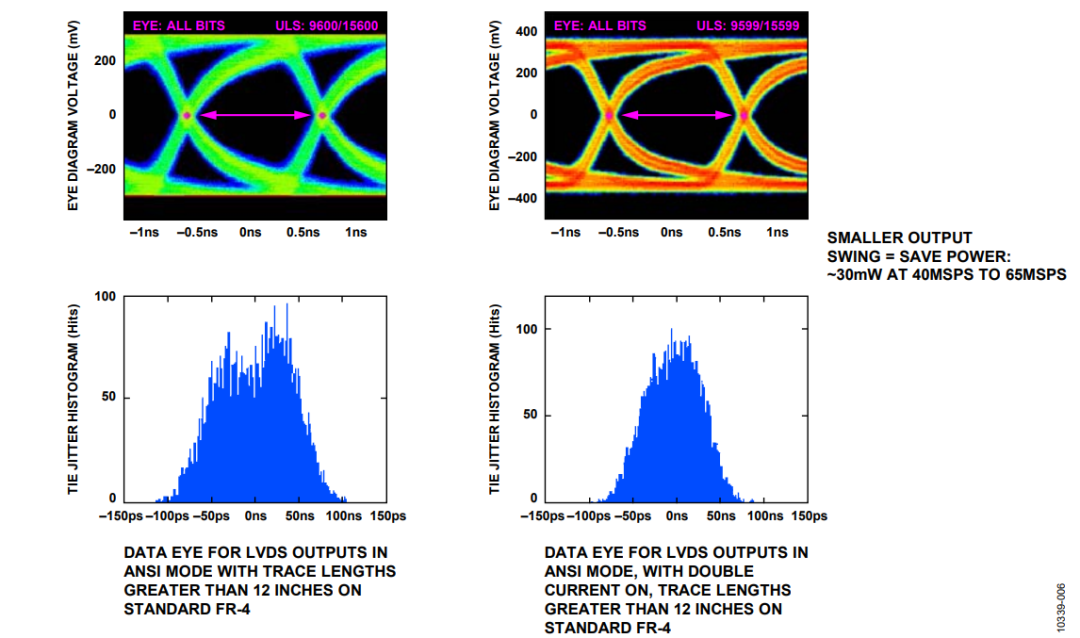

本文描述了ADC和FPGA之間LVDS接口設計需要考慮的因素,包括LVDS數據標準、LVDS接口數據時序違例解決方法以及硬件設計要點。

2025-07-29 10:01:26 5141

5141

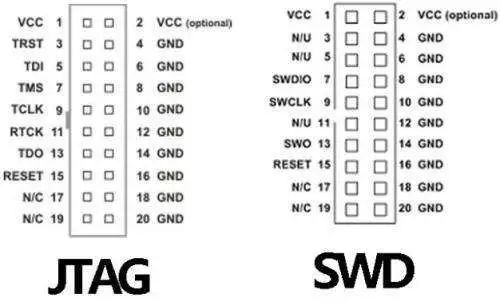

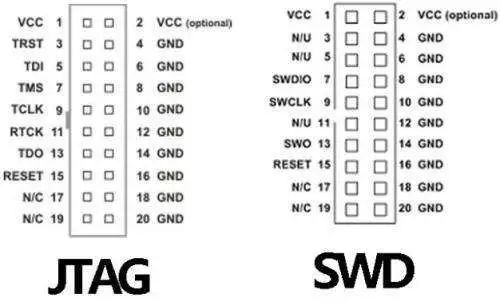

、DSP、FPGA器件等。標準的JTAG接口是4線:TMS、 TCK、TDI、TDO,分別為模式選擇、時鐘、數據輸入和數據輸出線。相關JTAG引腳的定義為:

2022-07-13 09:25:35 6754

6754 最近準備采用Xilinx FPGA進行多機通信,即主FPGA芯片將采集到的不同層的圖像數據流分別輸出給對應的4塊從FPGA芯片中,主從FPGA之間的連接機制采用星形拓撲結構。經計算,圖像數據流接口速率需要數百兆比特/秒,因此需要調研FPGA支持的常見IO接口標準,及每種接口的應用場合。

2022-10-17 09:14:18 6399

6399

根據ADC3663手冊,輸出格式為SLVDS,VCM=1.0V, VOD=500mV(min),700mV(typ), 850mV(max). 而FPGA通常LVDS接口(輸入)VIDIFF最大

2024-11-27 06:23:32

ADC為LTC2175_14,FPGA為ALTERA Cyclone4 FPGA

2021-10-28 11:17:54

,我們不得不多提兩句,畢竟可以兼容非常多的I/O電壓標準是FPGA的一大優勢,尤其是各種高速差分信號的支持。圖3.15中列出了我們這款器件支持的各種I/O電平標準。(特權同學,版權所有)圖3.15

2019-01-10 09:34:18

,并使用正確的連接線將它們連接起來。

按照規格書的要求進行連接,確保連接的穩固性和可靠性。

在FPGA和通信設備上配置SRIO接口的軟件驅動程序和相關設置,確保兩端的通信協議和參數設置一致

2024-06-27 08:33:13

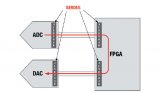

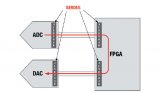

驅動并行ADC和并行DAC芯片。并行接口包括兩種數字編碼方式:帶符號數signed與無符號數unsigned。本文還將介紹使用不同編碼方式的ADC與DAC時需要注意的問題。接口協議以ADI公司的32M

2020-09-27 09:40:08

,如ARM、DSP、FPGA器件等。標準的JTAG接口是4線:TMS、 TCK、TDI、TDO,分別為模式選擇、時鐘、數據輸入和數據輸出線。...

2021-12-14 06:47:54

請教各位前輩,AD9764和FPGA的數據口采用哪種接口?對應的接口協議是什么?謝謝。

2023-12-18 08:12:04

DPHY接口協議和CPHY接口協議有何不同呢?CPHY物理層到底是怎么實現嵌入時鐘這一關鍵步驟的呢?

2021-11-01 07:55:42

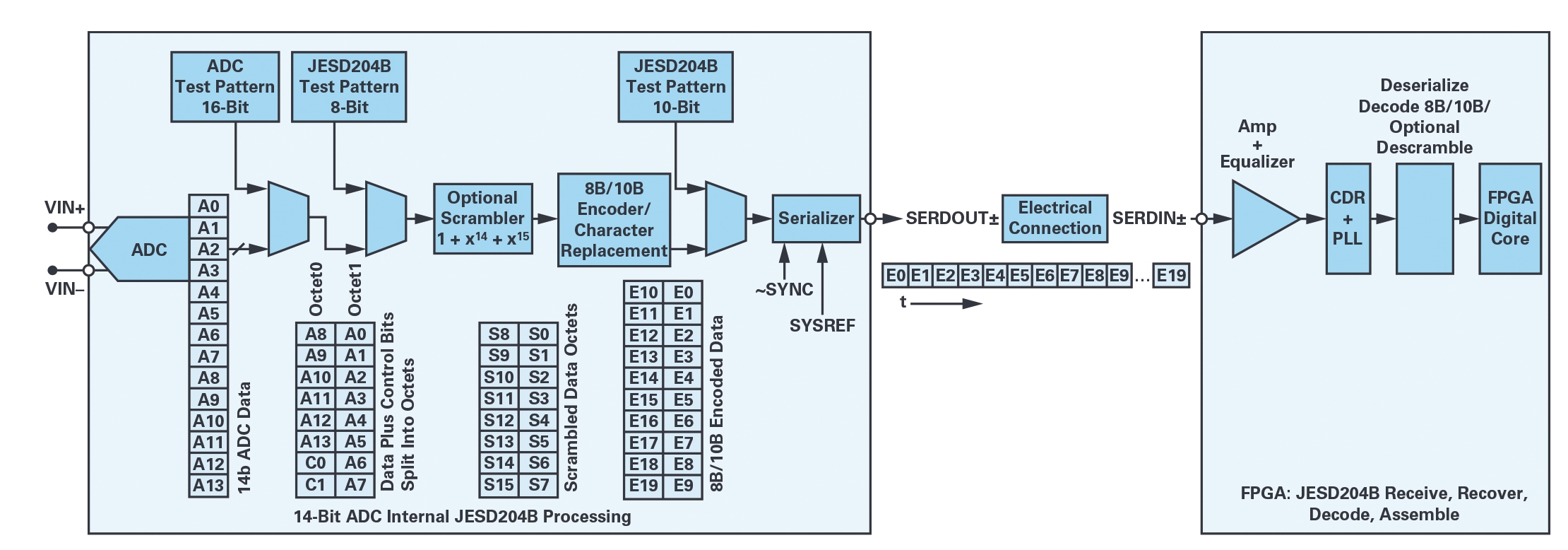

在使用最新模數轉換器 (ADC) 和數模轉換器 (DAC) 設計系統時,我已知道了很多有關 JESD204B 接口標準的信息,這些器件使用該協議與 FPGA 通信。那么在解決 ADC 至 FPGA

2021-04-06 06:53:56

當前許多精密模數轉換器(ADC)具有串行外設接口(SPI)或某種串行接口,用以與包括微控制器單元(MCU)、DSP和FPGA在內的控制器進行通信。控制器寫入或讀取ADC內部寄存器并讀取轉換碼。SPI

2021-11-04 07:49:49

SD卡的傳輸協議和讀寫程序SD/MMC 卡是一種大容量(最大可達4GB)、性價比高、體積小、訪問接口簡單的存儲卡。SD/MMC 卡大量應用于數碼相機、MP3 機、手機、大容量存儲設備,作為這些便攜式設備的存儲載體,它還具有低功耗、非易失性、保存數據無需消耗能量等特點。[hide][/hide]

2009-12-08 09:53:05

計算機網絡簡答題1、TCP 協議和 UDP 協議的區別有哪些?(1)TCP 屬于面向連接的協議,UDP 屬于面向無連接的協議 ;(2)TCP 可以保證數據可靠、有序的傳輸,可以進行流量控制,UDP

2021-08-06 08:43:52

TCP協議和UDP協議的區別有哪些?IP地址與MAC地址的區別是什么?ARP協議的工作原理是什么?二層交換機與路由器有什么區別?

2021-11-12 06:34:38

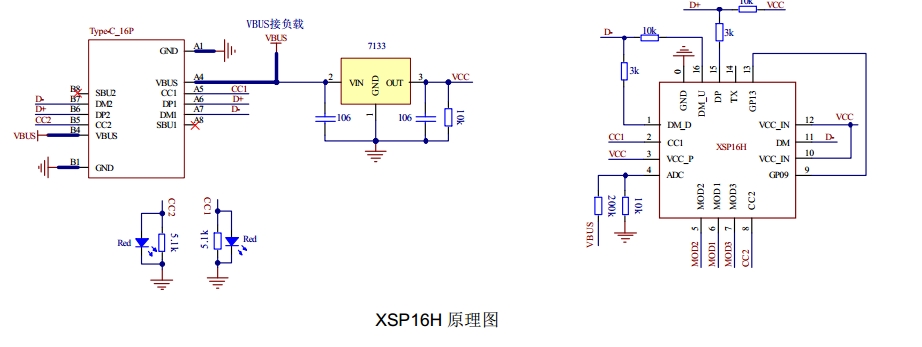

pd充電協議和qc充電協議兼容嗎

2023-09-26 08:04:20

文章目錄文章目錄文章目錄一、串口協議和RS-232標準1.串口通訊2.RS-2323.RS232電平與TTL電平的區別(1).TTL電平標準(2)具體區別二、USB/TTL轉232"模塊

2022-01-25 08:06:54

文章目錄一、串口協議和RS-232標準(一)、TTL電平標準(二)、RS232標準二、搭建STM32開發環境1.安裝jdk2.安裝STM32CubeMX一、串口協議和RS-232標準串口通信指串口按

2022-02-15 07:38:47

本是基于完成嵌入式開發實驗,具體內容為:1、了解串口協議和RS-232標準,以及RS232電平與TTL電平的區別;了解"USB/TTL轉232"模塊(以CH340芯片模塊為例

2022-02-21 07:09:33

本篇主要敘述串口協議和RS-232標準,以及RS232電平與TTL電平的區別;了解"USB/TTL轉232"模塊(以CH340芯片模塊為例)的工作原理。

2022-02-11 06:51:13

本文主要講解串口協議和RS-232標準,以及RS232電平與TTL電平的區別;介紹"USB/TTL轉232"模塊(以CH340芯片模塊為例)的工作原理。一、串口協議1.1 串口

2022-02-18 07:15:18

文章目錄前言一、什么是串口協議和RS-232標準?1. 電平標準2.STM32的USART二、使用步驟1.引入庫2.讀入數據總結前言一. 了解串口協議和RS-232標準,以及RS232電平與TTL

2022-02-15 07:50:44

本文逐一介紹三種視頻數字接口的標準。

2021-06-03 06:24:31

IEEE802.3協議和Ethernet II協議有什么區別?怎樣去識別IEEE802.3協議和Ethernet II協議呢?

2021-11-03 06:03:04

作者:王毅 管會生 劉斌彬 梅順良引言本文采用FPGA實現了IDE硬盤接口協議。系統提供兩套符合ATA-6規范的IDE接口,一個與普通IDE硬盤連接,另一個與計算機主板上的IDE接口相連。系統采用

2019-04-18 07:00:10

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現數字設計。除了這些數字功能之外,FPGA和CPLD還可以使用LVDS輸入、簡單的電阻電容(RC)電路和一些FPGA或CPLD的數字邏輯單元實現共模功能,從而構建模數轉換器(ADC)。

2019-09-19 06:18:40

的接口是LVDS2. FPGA驅動FSMC接口所需的最低內部時鐘為40MHz3. 14位ADC(7個差分對)支持并行和LVDS接口,1個差分輸入時鐘,1個差分輸出時鐘4.目前的計劃安排如下。a)時鐘樹b)與MMCM1抖動c)與MMCM2的抖動

2020-08-25 09:23:10

IDE接口協議簡介用FPGA實現接口協議的方法介紹

2021-04-08 06:39:49

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現數字設計。除了這些數字功能之外,FPGA和CPLD還可以使用LVDS輸入、簡單的電阻電容(RC)電路和一些FPGA或CPLD的數字邏輯單元實現共模功能,從而構建模數轉換器(ADC)。

2019-08-19 06:15:33

。這些技術還能用來保持聲音質量。與數字音頻一同發展的還有音頻標準和協議,其目的是簡化不同設備之間的音頻數據傳輸,例如音頻播放器與揚聲器之間、DVD播放器與AVR之間,而不必將數據轉換為模擬信號。本文將討論與音頻行業相關的各種標準和協議,同時也會探究不同平臺的音頻系統結構以及各種音頻算法和放大器。

2011-03-02 21:54:39

,請問ad7763所使用的接口不是標準的SPI協議嗎?或者ad7763的spi是ad作為主機而控制器只是從機?

2023-12-12 08:23:09

,請問ad7763所使用的接口不是標準的SPI協議嗎?或者ad7763的spi是ad作為主機而控制器只是從機?

2018-08-07 06:59:51

在STM32中怎么實現SPI協議和IIC協議轉換啊?

2020-04-13 23:44:04

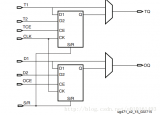

CLK,DATA,LOAD和 LDAC等控制信號,這些信號將驅動 DAC的工作,將數字控制量轉換成模擬電壓值。結束語FPGA接口設計需要綜合考慮硬件連接,工作流程,接口協議和邏輯模塊等多方面因素,是一項

2020-08-19 09:29:48

Iub/Iur/Iu/Uu都為標準的接口,可以連接不同設備供應商提供的設備。一般將Iub/Iur/Iu接口統稱為UTRAN地面接口。根據RNC連接的CN設備的不同,Iu接口又可以分Iu-CS接口、Iu-PS接口和Iu-BC

2009-05-30 16:24:58 2

2 CAN 的較高層協議和子協議

本文主要介紹了幾個基于CAN 的較高層協議CAL/CANopen DeviceNet SDS 并且對這幾個較高層協議的重要功能作了一些比較使讀者更深入地了解

2010-03-22 15:31:39 34

34 基于CAN的較高層協議和子協議

2010-10-18 16:38:37 21

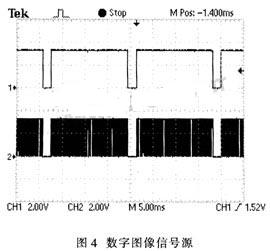

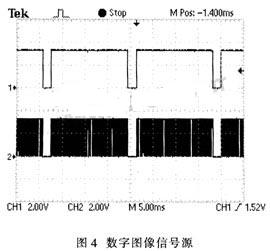

21 介紹一種基于Camera Link協議和FPGA設計數字圖像信號源的方法。該設計將圖像數據和接口信號轉換成與Camera Link協議相匹配的低壓差分信號(LVDS)進行傳輸。提高了信號的傳輸

2010-12-17 15:58:04 43

43 Camera Link協議和FPGA的數字圖像信號源設計

1 引言

目前,各種圖像設備已廣泛應用到航空航天、軍事、醫療等領域。圖像信號源作為地面圖像采集裝置測試系

2010-02-04 09:41:55 4090

4090

基于FPGA和CPLD數字邏輯實現ADC技術

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現

2010-05-25 09:39:10 1844

1844

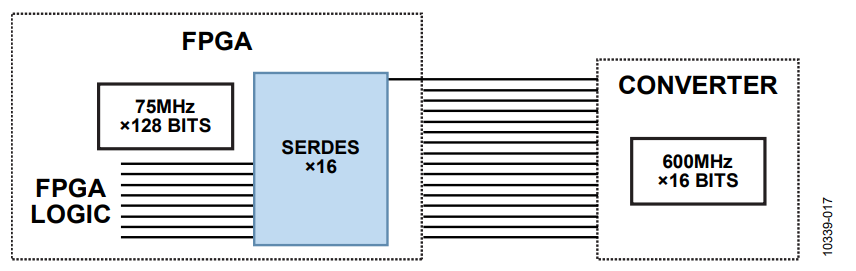

和FPGA之間的數字通信豎立了一個簡單的新基準。LTC2274的新型高速二線式品行接口極大地減少了一個16位ADC和FPGA之間所

2011-03-15 14:23:45 50

50 數字電源開放標準協議-PMBus的介紹

2011-11-10 16:35:28 161

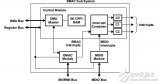

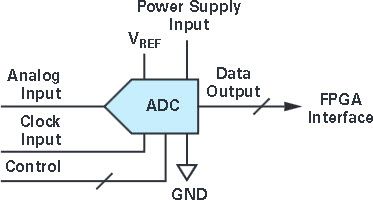

161 現場可編程門陣列(FPGA)與模數轉換器(ADC)數字數據輸出的接口是一項常見的工程設計挑戰。此外,ADC使用多種多樣的數字數據樣式和標準,使這項挑戰更加復雜。本資料將告訴您有

2012-04-26 14:59:12 96

96 在當今的模數轉換器(ADC)領域,ADC制造商主要采用三類數字輸出,本文將討論如何實現這些接口,以及各類輸出的實際應用,并探討選擇和使用不同輸出時需要注意的事項。

2012-10-10 10:34:39 15065

15065

為逐次逼近型ADC 設計可靠的數字接口

2016-01-04 17:45:26 0

0 Camera+link協議和FPGA的數字圖像信號源設計

2016-08-29 15:02:03 34

34 基于CAN的較高層協議和子協議

2016-12-14 16:39:16 13

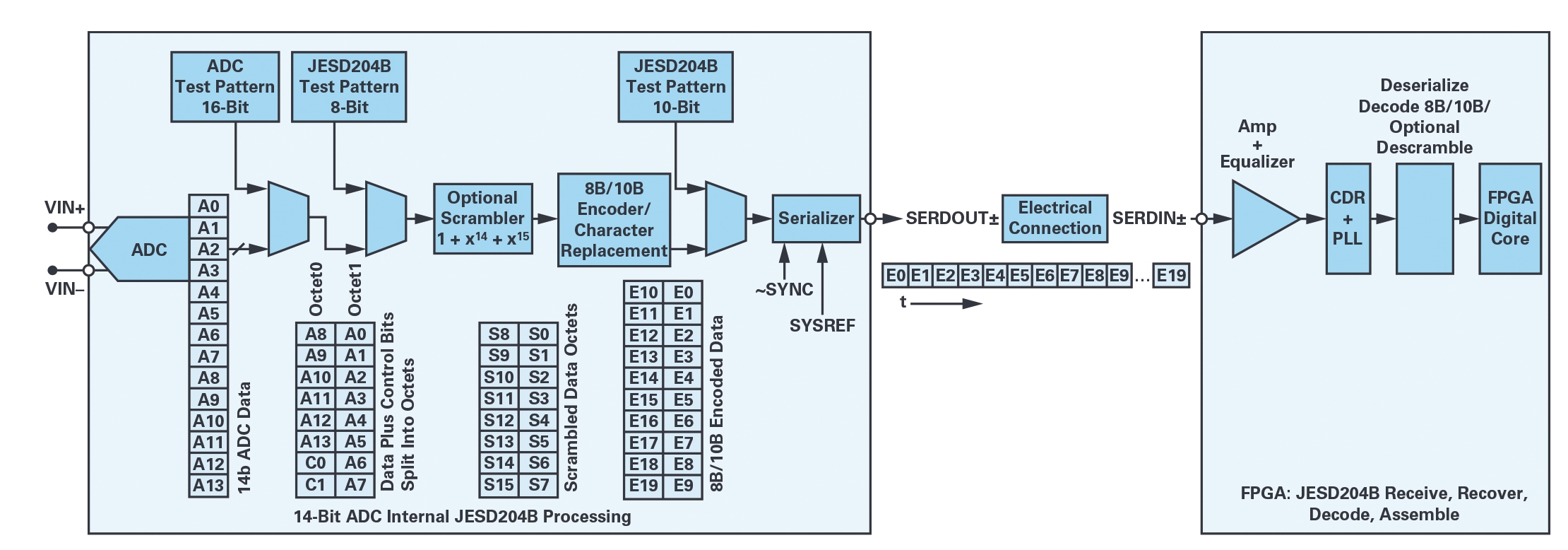

13 JESD204B為業界標準序列通信鏈接,數據轉換器與現場可編程門陣列(FPGA)、數字信號處理器(DSP)、特定應用集成電路(ASIC)等裝置間的數字數據接口因此能化繁為簡,這項標準減少裝置間路由

2017-11-17 14:45:16 3921

3921

在使用我們的最新模數轉換器(ADC)和數模轉換器(DAC)設計系統時,我已知道了很多有關 JESD204B接口標準的信息,這些器件使用該協議與FPGA 通信。

2017-11-18 04:10:55 3410

3410

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現數字設計。除了這些數字功能之外,FPGA和CPLD還可以使用LVDS輸入、簡單的電阻電容(RC)電路和一些FPGA或CPLD的數字邏輯單元實現共模功能,從而構建模數轉換器(ADC)。

2018-04-26 11:53:00 1765

1765

LVDS 即Low-Voltage Differential Signaling。FPGA的selecteIO非常強大,支持各種IO接口標準,電壓電流都可以配置。其接口速率可以達到幾百M甚至上千M

2018-06-30 10:23:00 25583

25583

CAN協議和標準規范 1、 由ISO標準化的CAN協議 CAN協議已經由ISO標準化,有2個版本,如ISO11898和ISO11519-2,它們之間在數據鏈路層沒什么不同,但是在物理層有些區別

2017-12-30 05:01:13 36779

36779

本文將重點介紹各種標準接口,并揭示它們對不同嵌入式芯片廠商的區別所在。了解基本接口可幫助設計人員優先考慮哪些接口應為片上。另外,雖然標準接口具有很高的使用價值,但為了提供額外的片上資源,也需要可定制化的片上接口。本文將介紹兩種這樣的外設塊。

2018-06-04 03:38:00 21639

21639

ADI和Xilinx的專家解釋了JESD204B接口標準的重要性,并說明了該標準如何用于ADC到FPGA設計中。

2019-08-01 06:15:00 3813

3813 SDIO—當進行讀操作時,SDIO作為輸出口SDO,串行數據從ADC輸出,進入FPGA;當進行寫操作時,SDIO作為輸入口SDI,串行數據從FPGA輸出,進入ADC;

2020-09-07 17:07:01 5957

5957

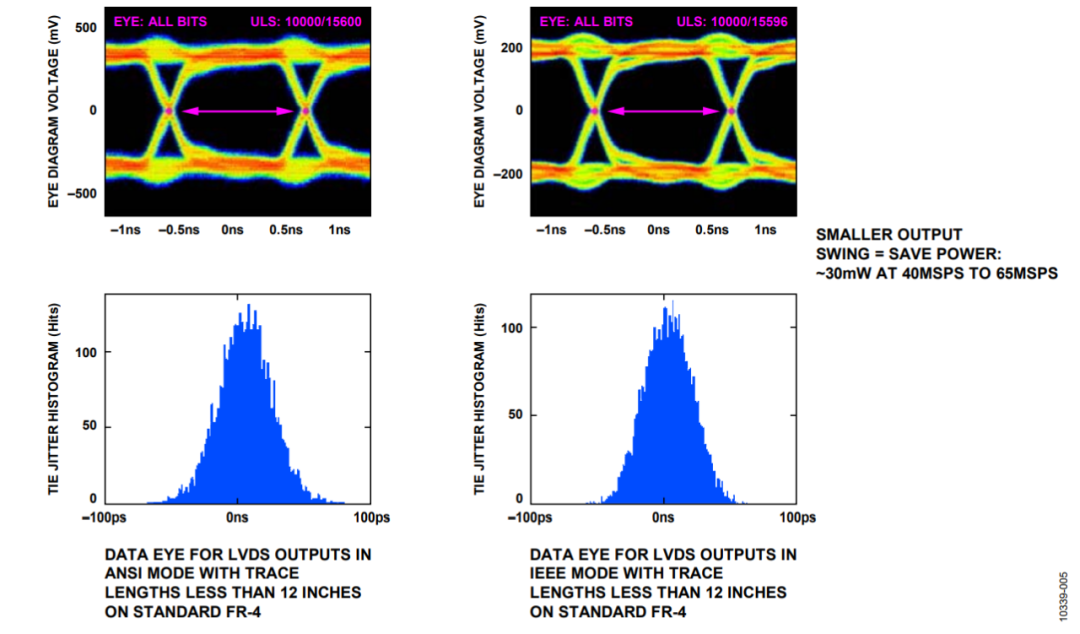

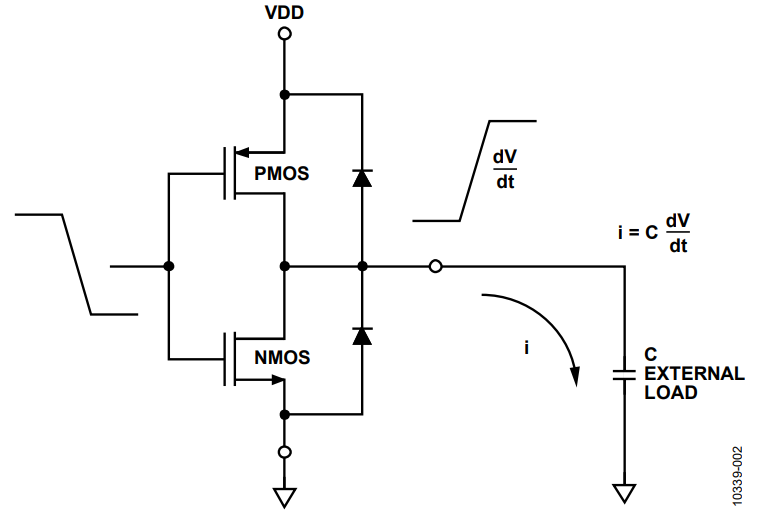

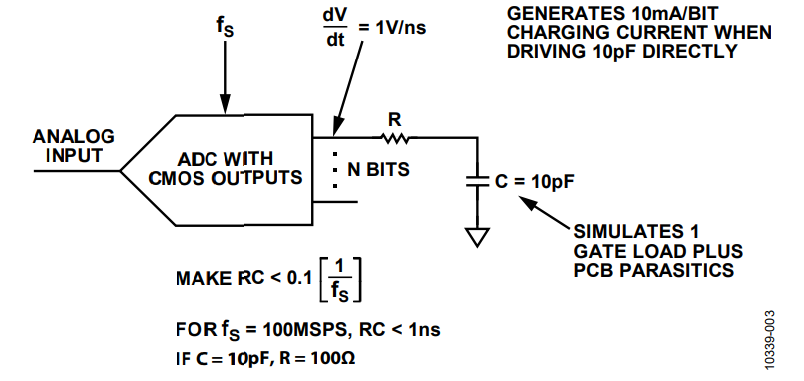

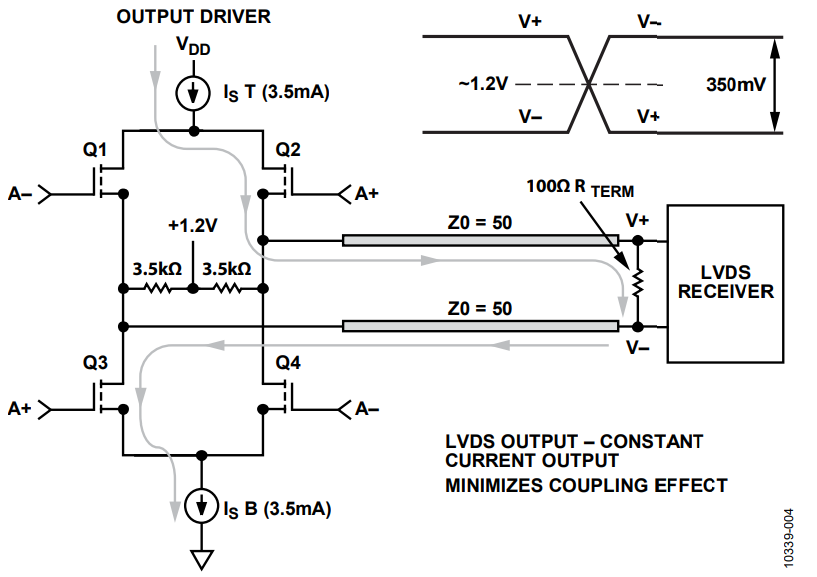

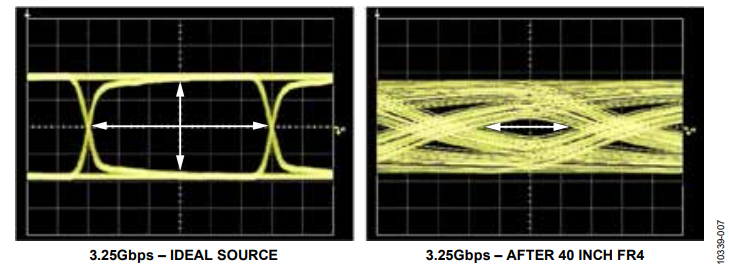

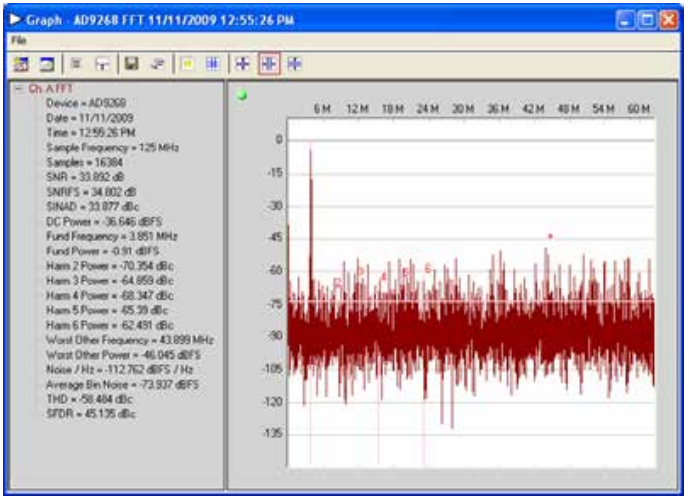

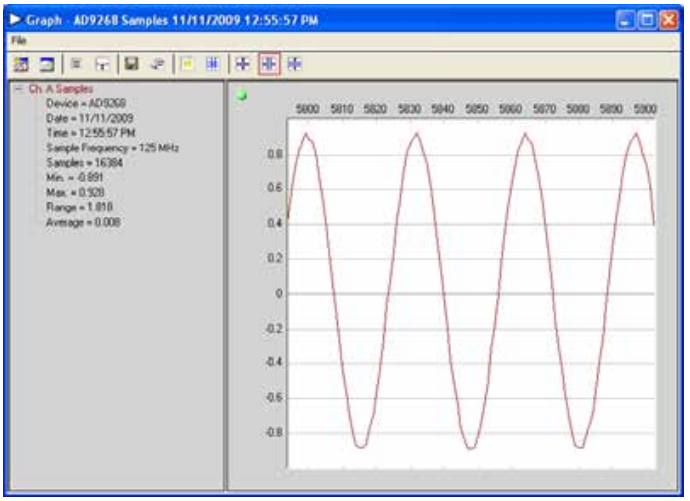

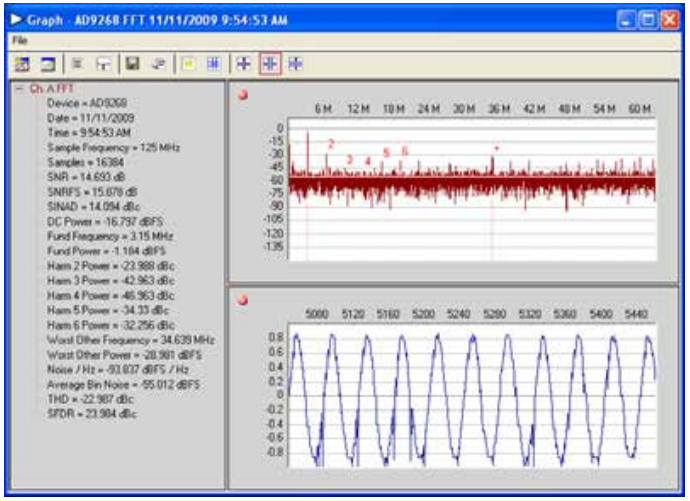

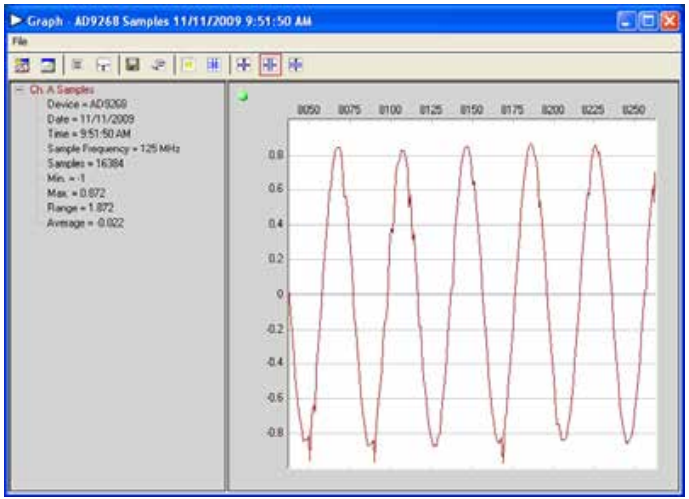

場可編程門陣列(FPGA)與模數轉換器(ADC)輸出的接口是一項常見的工程設計挑戰。本文簡要介紹各種接口協議和標準,并提供有關在高速數據轉換器實現方案中使用LVDS的應用訣竅和技巧。

2020-09-15 10:29:10 6705

6705

LVDS常常用在具有“源同步”時鐘系統的數據轉換器中,不過這并不是LVDS標準的一部分。在這種設置中,時鐘與數據同相,并且與數據一同發送。這樣,接收器就能使用該時鐘更輕松地捕捉數據,因為它現在知道數據傳輸何時發生。

2020-09-21 16:42:08 9297

9297

介紹一種基于Camera Link協議和FPGA設計數字圖像信號源的方法。該設計將圖像數據和接口信號轉換成與Camera Link協議相匹配的低壓差分信號(LVDS)進行傳輸。提高了信號的傳輸距離

2021-01-26 15:02:00 30

30 MT-201:FPGA與ADC數字數據輸出的接口

2021-03-21 09:52:10 7

7 電子發燒友網為你提供FPGA與ADC數字數據輸出的接口資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-18 08:51:53 27

27 具有LVDS輸出的LTM9011 ADC的AN147-Altera Stratix IV FPGA接口

2021-05-09 21:19:53 15

15 基于FPGA的_ADC數字抽取濾波器Sinc_3設計(現代電源技術基礎楊飛)-該文檔為基于FPGA的_ADC數字抽取濾波器Sinc_3設計總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-09-16 13:58:04 27

27 當前許多精密模數轉換器(ADC)具有串行外設接口(SPI)或某種串行接口,用以與包括微控制器單元(MCU)、DSP和FPGA在內的控制器進行通信。控制器寫入或讀取ADC內部寄存器并讀取轉...

2021-10-28 21:06:03 10

10 當前許多精密模數轉換器(ADC)具有串行外設接口(SPI)或某種串行接口,用以與包括微控制器單元(MCU)、DSP和FPGA在內的控制器進行通信。控制器寫入或讀取ADC內部寄存器并讀取轉換碼。SPI

2021-10-29 09:51:36 8

8 typora-copy-images-to: typora_picture基于FPGA與MCU通信的SPI協議設計1. SPI總線協議介紹及硬件設計1.1 SPI總線協議介紹及硬件設計SPI總線

2021-11-05 15:35:59 17

17 眾所周知通信協議就是一種數據傳輸的協議規范,從軟硬件層面可以分為硬件層通信協議和軟件層通信協議,本文通過對通信的硬件層協議和軟件層協議的簡單介紹使大家更好的理解什么是通信。

2021-12-05 15:51:03 9

9 常用的串行通訊方式,因為它簡單、便捷,因此大部分電子設備都支持該通訊方式,電子工程師在調試設備時也經常使用該通 訊方式輸出調試信息。2.RS-232 標準RS-232 標準主要規定了信號的用途,通訊接口以及信號的電平標準。在上面的通訊方式中,兩個通訊設備的“DB9接口”之間通過串.

2021-12-20 19:18:26 1

1 當前許多精密模數轉換器(ADC)具有串行外設接口(SPI)或某種串行接口,用以與包括微控制器單元(MCU)、DSP和FPGA在內的控制器進行通信。控制器寫入或讀取ADC內部寄存器并讀取轉換碼。

2022-02-09 11:28:02 5

5 該標準包括兩個通信規程中使用的 MODBUS 應用層協議和服務規范:

·串行鏈路上的 MODBUS

MODBUS 串行鏈路取決于 TIA/EIA 標準:232-F

2022-04-13 14:57:32 2

2 ADC和DAC是FPGA與外部信號的接口,從數據接口類型的角度劃分,有低速的串行接口和高速的并行接口。FPGA經常用來采集中高頻信號,因此使用并行ADC和DAC居多。本文將介紹如何使用FPGA驅動并行ADC和并行DAC芯片。

2022-04-21 08:55:22 8245

8245 與現有接口格式和協議相比,JESD204B接口更復雜、更微妙,必須克服一些困難才能實現其優勢。像其他標準一樣,要使該接口比單倍數據速率或雙倍數據速率CMOS/LVDS等常用接口更受歡迎,它必須能無縫地工作。

2022-04-21 14:28:07 5912

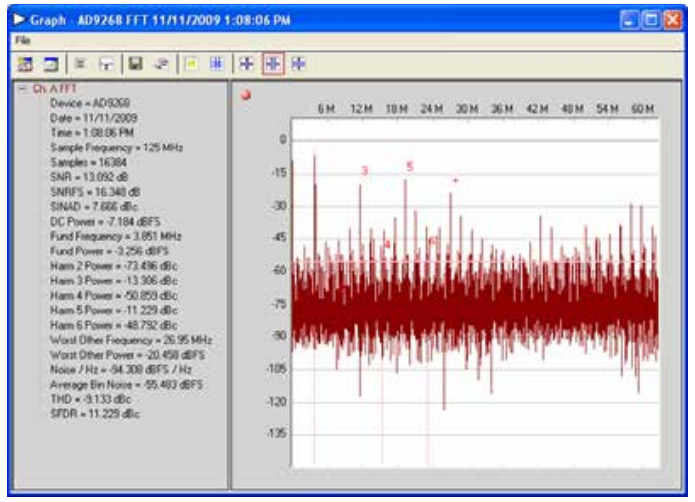

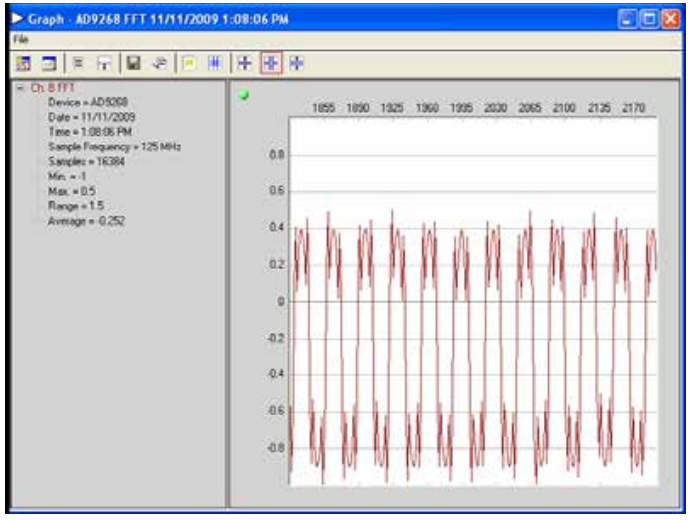

5912 本文闡釋了JESD204B標準的ADC與FPGA的接口,如何判斷其是否正常工作,以及可能更重要的是,如何在有問題時排除故障。文中討論的故障排除技術可以采用常用的測試與測量設備,包括示波器和邏輯分析儀

2022-08-02 08:03:34 2470

2470

由于高速ADC的迅速發展,傳輸速率已經邁入GSPS,因此JESD204B標準協議將會成為應用范圍最廣的接口傳輸協議。

2022-09-05 09:21:15 4568

4568 一整套的協議以及標準,包含了各種子系統獨特的要求,這整個的規定和標準,我們稱之為MIPI協議。 作者:明德揚FPGA科教 https://www.bilibili.com/read/cv19861450 出處:bilibili

2022-11-21 10:26:19 1280

1280 本文討論了標準接口 — SPI、I2C、SPORT、LVDS 和 JESD204A——用于將 FPGA 連接到 ADC。隨著數據速率的進一步提高,FPGA與ADC的接口仍將是一個共同的挑戰。JESD204B支持12.5 Gbps,JESD204C將遷移到32 Gbps。

2022-12-21 10:57:30 9200

9200

TCP/IP協議中有兩個具有代表性的傳輸層協議,分別是TCP協議和UDP協議。TCP協議全稱傳輸控制協議,是一種面向連接的、可靠的、基于字節流的傳輸層通信協議。UDP協議全稱用戶數據報協議

2023-03-21 10:39:01 1710

1710 、DSP、FPGA器件等。標準的JTAG接口是4線:TMS、 TCK、TDI、TDO,分別為模式選擇、時鐘、數據輸入和數據輸出線。相關JTAG引腳的定義為:

* TMS:測試模式選擇,TMS用來設置JTAG接口

2023-05-25 15:20:41 5171

5171

對于TCP協議和UDP協議,大家應該都有所耳聞。TCP協議和UDP協議都工作在傳輸層,他們的目標都是在應用之間傳輸數據。

2023-06-15 09:37:25 1265

1265

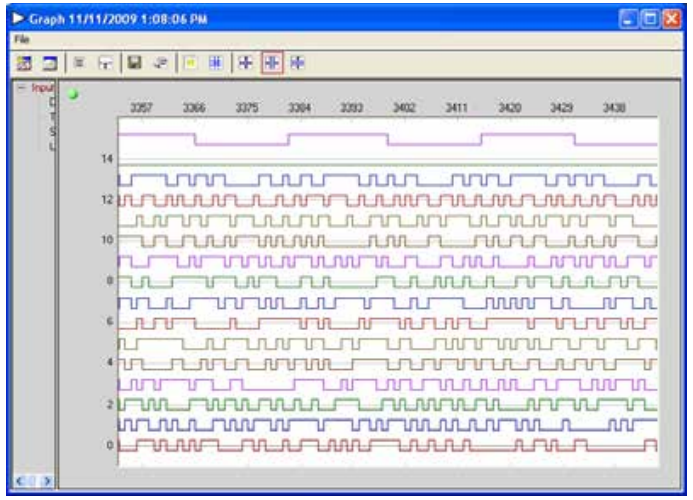

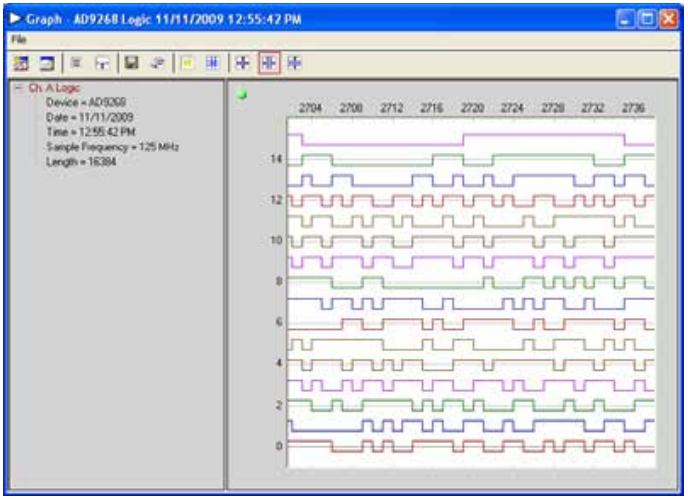

:通道A數字信號輸出 ?D7B~D0B:通道B數字信號輸出 DCO+-:數字差分時鐘輸出,信號頻率為125MHz ? S1:數據格式選擇,該接口電

2023-08-28 14:30:01 3075

3075 TCP/IP協議和OPC協議是兩種重要的網絡協議,它們在不同的網絡層級上運行,并為數據傳輸和通信提供了不同的功能。

2023-10-21 10:11:49 2248

2248 電子發燒友網站提供《FPGA與ADC數字數據輸出的接口指南.pdf》資料免費下載

2023-11-28 09:40:00 0

0 電子發燒友網站提供《LIN協議和物理層要求.pdf》資料免費下載

2024-08-30 09:36:45 1

1 數字輸出接口是電子設備中用于傳輸數字信號到外部設備的關鍵部分。這些接口種類繁多,各有特點,適用于不同的應用場景。以下是一些常見的數字輸出接口:

2024-10-01 15:55:00 3653

3653 電子發燒友網站提供《同步與多個FPGA接口的千兆樣本ADC.pdf》資料免費下載

2024-10-10 11:32:35 0

0 區分在于它們在充電過程中的角色和功能不同。充電端協議定供電設備如(充電器)的輸出標準和通信方式。而受電端協議則定義了用電設備(如手機、平板電腦等)的輸入標準和通信方式。 充電端協議是供電設備(如充電器、車充等)所采

2024-10-17 16:14:38 2260

2260

ADC和DAC是FPGA與外部信號的接口,從數據接口類型的角度劃分,有低速的串行接口和高速的并行接口。FPGA經常用來采集中高頻信號,因此使用并行ADC和DAC居多。本文將介紹如何使用FPGA驅動并行ADC和并行DAC芯片。

2025-03-14 13:54:12 1979

1979

HART協議和RS485協議都是用于工業領域通信的協議,但它們有不同的應用場景和特點。

2025-03-27 10:07:56 2413

2413

溫度傳感器常用的通信協議和接口可根據應用場景(如工業控制、智能家居、物聯網等)和傳輸需求(距離、速度、功耗等)分為有線和無線兩大類,具體協議和接口的選擇需結合傳感器類型、系統架構及成本等因素綜合考量

2025-09-23 17:22:20 1090

1090 電子發燒友網站提供《SIP協議和私有協議廣播區別.docx》資料免費下載

2025-11-06 16:31:21 1

1

電子發燒友App

電子發燒友App

評論