六零年代,隨著電信數(shù)字載波系統(tǒng)T1和E1的出現(xiàn),數(shù)字重定時(shí)器開(kāi)始受到關(guān)注。這些系統(tǒng)在屏蔽雙絞線上承載多條語(yǔ)音電路信道,每隔幾千英尺需安裝一個(gè)數(shù)字重定時(shí)器。當(dāng)時(shí)這些設(shè)備比較先進(jìn),它們采用的技術(shù)與現(xiàn)在的高速重定時(shí)器類似,包括均衡、時(shí)鐘數(shù)據(jù)恢復(fù)(CDR)、線路編碼和成幀。

對(duì)于每一種串行器/解串器(SerDes),總有應(yīng)用需要更長(zhǎng)的連接距離。轉(zhuǎn)接驅(qū)動(dòng)器或重定時(shí)器芯片的典型應(yīng)用包括:

到達(dá)大型PCB的最遠(yuǎn)端

使用額外的連接器

支持子卡

連接擴(kuò)展架

使用低端PCB材料

允許擁有較短距SerDes的芯片支持需要較長(zhǎng)距離SerDes的應(yīng)用

增強(qiáng)設(shè)備功能

轉(zhuǎn)接驅(qū)動(dòng)器和重定時(shí)器的比較

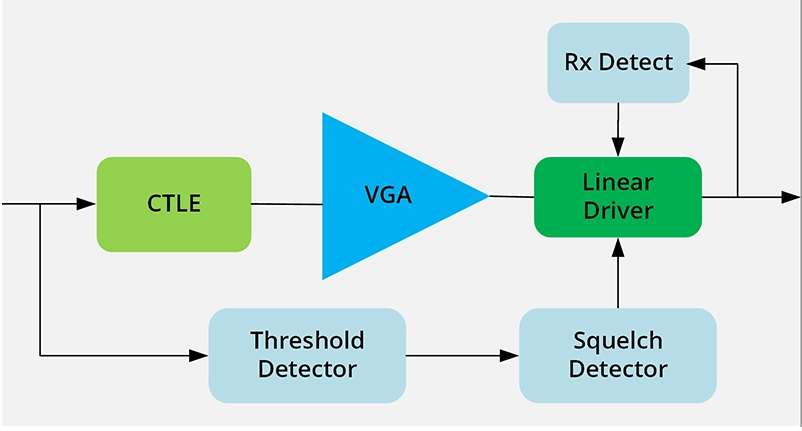

典型的轉(zhuǎn)接驅(qū)動(dòng)器數(shù)據(jù)通路包含連續(xù)時(shí)間線性均衡器(CTLE)、可變?cè)鲆娣糯笃?/u>(VGA)和線性驅(qū)動(dòng)器。CTLE用于均衡信道中由頻率引起的損耗,VGA用于恢復(fù)信號(hào)幅度,線性驅(qū)動(dòng)器則以適合的阻抗驅(qū)動(dòng)信道。

轉(zhuǎn)接驅(qū)動(dòng)器通常提供輸入信號(hào)損耗閾值和輸出接收器(Rx)檢測(cè)功能,同時(shí)還有一個(gè)靜噪檢測(cè)器,可以差分檢測(cè)低速信道上是否存在通信信號(hào)。圖1給出了典型的轉(zhuǎn)接驅(qū)動(dòng)器的功能框圖。

圖1:典型的轉(zhuǎn)接驅(qū)動(dòng)器功能框圖,包括一個(gè)CTLE,用于均衡信道中由頻率引起的損耗;一個(gè)VGA,用于恢復(fù)信號(hào)幅度;一個(gè)線性驅(qū)動(dòng)器,以合適的阻抗驅(qū)動(dòng)信道。

模擬轉(zhuǎn)接驅(qū)動(dòng)器的局限

模擬轉(zhuǎn)接驅(qū)動(dòng)器有三個(gè)主要缺點(diǎn):

1. 轉(zhuǎn)接驅(qū)動(dòng)器會(huì)放大信號(hào)及其內(nèi)部噪聲。發(fā)送器通過(guò)不可靠信道發(fā)送高信噪比(SNR)信號(hào),轉(zhuǎn)接驅(qū)動(dòng)器中的CTLE和放大器都具有本底噪聲,當(dāng)信號(hào)被放大時(shí),這兩種本底噪聲會(huì)隨著信號(hào)一起增強(qiáng)。當(dāng)接收器恢復(fù)數(shù)據(jù)時(shí),必須與放大的噪聲抗衡,這減弱了轉(zhuǎn)接驅(qū)動(dòng)器所具備的優(yōu)勢(shì)。

2. 轉(zhuǎn)接驅(qū)動(dòng)器僅清除部分碼間干擾(ISI)。通帶中與信道頻率相關(guān)的損耗會(huì)在多個(gè)位時(shí)間內(nèi)對(duì)位產(chǎn)生干擾。CTLE可以均衡一部分ISI,但是CTLE永遠(yuǎn)無(wú)法精確配置以完全糾正所有ISI,而不均衡的通帶紋波又會(huì)留下ISI。最后接收器不得不與這些殘留的ISI抗衡。

3. 轉(zhuǎn)接驅(qū)動(dòng)器無(wú)法恢復(fù)眼寬和相關(guān)抖動(dòng)。接收器具有良好的眼寬對(duì)于實(shí)現(xiàn)無(wú)差錯(cuò)性至關(guān)重要。但很多因素都會(huì)降低眼寬,例如熱噪聲、偏移、模擬失調(diào)、上升/下降時(shí)間不匹配、終端失配、ISI和電源噪聲等。而轉(zhuǎn)接驅(qū)動(dòng)器的存在進(jìn)一步加劇了這些因素的不良影響,使信號(hào)恢復(fù)更具挑戰(zhàn)性。

因此,轉(zhuǎn)接驅(qū)動(dòng)器之前和之后的完整鏈路長(zhǎng)度不能得到利用,每個(gè)位置都必須采用較短的走線,以最大程度地降低附加噪聲、殘留ISI和狹窄眼寬造成的影響。由于這些問(wèn)題,在所有可能的應(yīng)用中,系統(tǒng)開(kāi)發(fā)人員都將承受巨大壓力,以了解和表征轉(zhuǎn)接驅(qū)動(dòng)器對(duì)最終系統(tǒng)的復(fù)雜影響。

重定時(shí)器如何工作

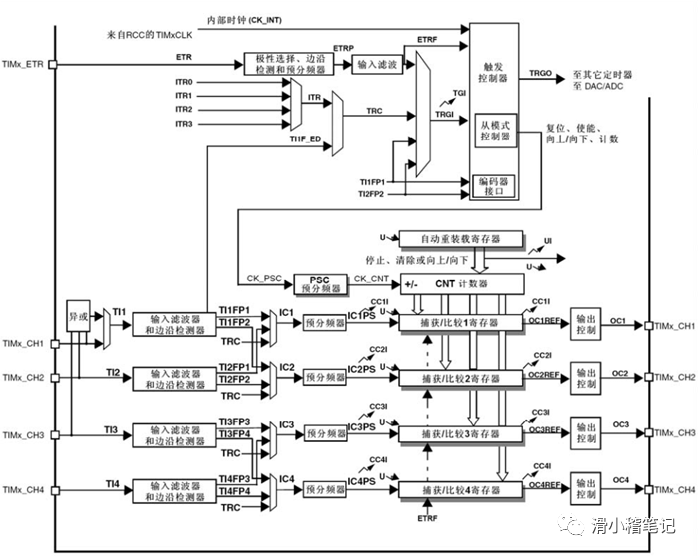

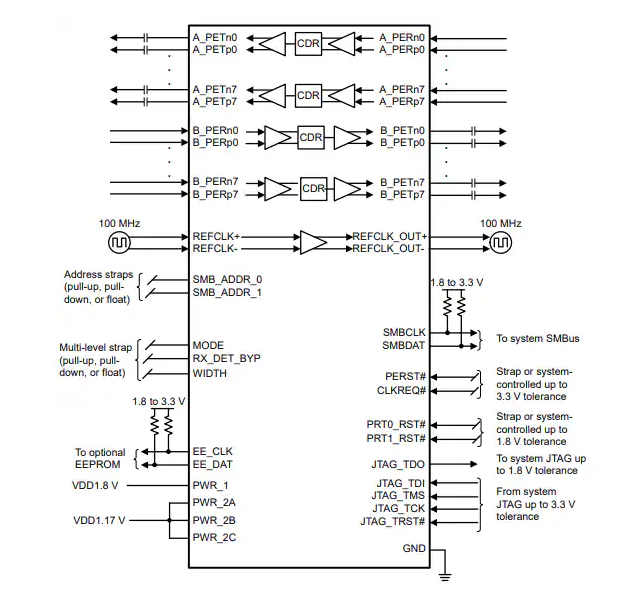

典型的重定時(shí)器是一種混合信號(hào)模擬/數(shù)字器件,它具備協(xié)議感知能力,能夠提取嵌入式時(shí)鐘,完全恢復(fù)數(shù)據(jù),并使用干凈的時(shí)鐘重新傳輸新的數(shù)據(jù)副本。轉(zhuǎn)接驅(qū)動(dòng)器中包含了CTLE、VGA和驅(qū)動(dòng)級(jí),而重定時(shí)器中則包含CDR電路、長(zhǎng)尾均衡器(LTE)和判決反饋均衡器(DFE)。

LTE用于補(bǔ)償長(zhǎng)期脈沖響應(yīng)受損,DFE則作為非線性均衡器,抑制由高頻損耗和陷波之類的信道缺陷而導(dǎo)致的ISI。

另外,內(nèi)部數(shù)字邏輯、狀態(tài)機(jī)和/或微控制器用于管理CTLE、VGA、LTE和DFE塊的自動(dòng)適配,并實(shí)現(xiàn)協(xié)議鏈路訓(xùn)練和狀態(tài)更新。圖2給出了典型的重定時(shí)器功能框圖。

圖2:轉(zhuǎn)接驅(qū)動(dòng)器中包含CTLE、VGA和驅(qū)動(dòng)級(jí),典型的重定時(shí)器則包含CDR電路、LTE和DFE。

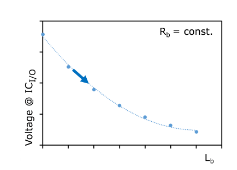

簡(jiǎn)而言之,轉(zhuǎn)接驅(qū)動(dòng)器僅放大信號(hào),而重定時(shí)器則可完全恢復(fù)數(shù)據(jù)并發(fā)送全新的數(shù)據(jù)副本。圖3對(duì)此進(jìn)行了圖形表述,顯示了被衰減的眼開(kāi)放(eye opening)如何被轉(zhuǎn)接驅(qū)動(dòng)器增強(qiáng),以及如何由重定時(shí)器完全重新生成。

圖3:經(jīng)信道衰減的眼圖(左)、通過(guò)轉(zhuǎn)接驅(qū)動(dòng)器后的眼圖(中)和通過(guò)重定時(shí)器后的眼圖(右),顯示出轉(zhuǎn)接驅(qū)動(dòng)器對(duì)信號(hào)的增強(qiáng),以及重定時(shí)器對(duì)信號(hào)的重新生成。

重定時(shí)器必須具備協(xié)議感知能力,才能實(shí)現(xiàn)信號(hào)的重新生成。它監(jiān)視鏈路配置事務(wù),并將自身設(shè)置為正確的模式。在某些情況下,重定時(shí)器也會(huì)參與鏈路設(shè)置。由于采用了這些自動(dòng)步驟,因而無(wú)需手動(dòng)調(diào)整具體的信道、線纜和波形因數(shù),以更高數(shù)據(jù)速率進(jìn)行系統(tǒng)集成也變得更加簡(jiǎn)單。

符合高速接口規(guī)范的重定時(shí)器

業(yè)界近日頒布了一系列較難實(shí)現(xiàn)的高速SerDes規(guī)范,包括USB4、PCIe5.0、CEI-28G和CEI-56G規(guī)范,以及仍在開(kāi)發(fā)階段的PCI6.0和CEI-112G規(guī)范。這些新標(biāo)準(zhǔn)旨在滿足不斷提高的數(shù)據(jù)吞吐量需求。

二十多年來(lái),光互聯(lián)論壇(OIF)和IEEE 802.3以太網(wǎng)委員會(huì)已聯(lián)合發(fā)布了八代SerDes及前期規(guī)范。針對(duì)每一代SerDes規(guī)范,供應(yīng)商都開(kāi)發(fā)出了兼容多種協(xié)議的比特級(jí)重定時(shí)器產(chǎn)品,促進(jìn)了系統(tǒng)制造商的產(chǎn)品開(kāi)發(fā)。

這些SerDes技術(shù)和相應(yīng)的重定時(shí)器已被采用并產(chǎn)生了廣泛的影響,其應(yīng)用領(lǐng)域包括電信、以太網(wǎng)、Interlaken、RapidIO、串行高級(jí)技術(shù)附件(SATA)、串行連接小型計(jì)算機(jī)系統(tǒng)接口SAS、光纖通道、InfiniBand,以及眾多專有系統(tǒng)。但轉(zhuǎn)接驅(qū)動(dòng)器芯片在OIF/以太網(wǎng)系列生態(tài)系統(tǒng)中從未得到廣泛應(yīng)用,這是由于鏈路的設(shè)計(jì)通常更精細(xì),耗盡了鏈路資源。

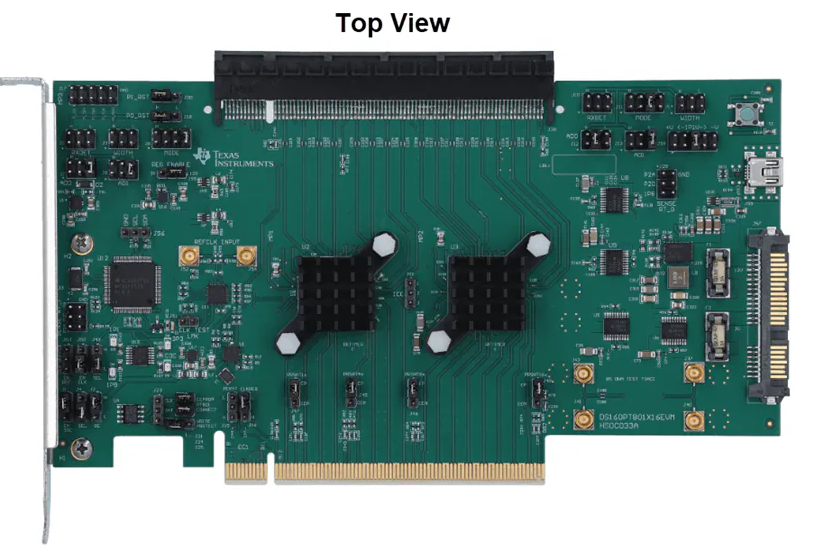

PCI Express(PCIe)是一種高速串行計(jì)算機(jī)擴(kuò)展總線標(biāo)準(zhǔn)。它是個(gè)人計(jì)算機(jī)圖形卡、硬盤(pán)驅(qū)動(dòng)器、SSD、Wi-Fi和以太網(wǎng)硬件連接的標(biāo)準(zhǔn)主板接口。轉(zhuǎn)接驅(qū)動(dòng)器可以完全滿足PCIe3.0規(guī)范,數(shù)據(jù)速率達(dá)8Gbps/通道。而PCIe4.0將速率提高了一倍,達(dá)到16Gbps/通道,轉(zhuǎn)接驅(qū)動(dòng)器也盡力滿足其速率要求,為系統(tǒng)實(shí)施者帶來(lái)了好處。

2019年5月,PCI-SIG標(biāo)準(zhǔn)機(jī)構(gòu)正式發(fā)布了PCIe5.0規(guī)范,其數(shù)據(jù)通道運(yùn)行速率高達(dá)32Gbps。速率不斷提高,對(duì)擴(kuò)展能力的需求也不斷增加,PCIe轉(zhuǎn)接驅(qū)動(dòng)器的發(fā)展似乎已經(jīng)到頭。在即將推出的PCIe6.0標(biāo)準(zhǔn)中,PAM4的脆弱甚至使設(shè)計(jì)者放棄采用轉(zhuǎn)接驅(qū)動(dòng)器。

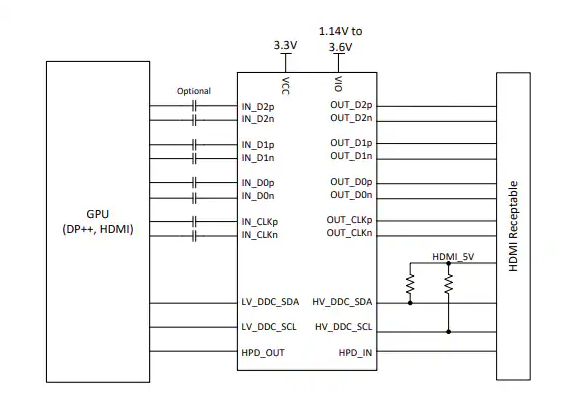

再來(lái)看通用串行總線(USB),它是計(jì)算機(jī)、外圍設(shè)備和其他計(jì)算機(jī)之間的行業(yè)接口標(biāo)準(zhǔn)。USB1.0于1996年發(fā)布,USB2.0隨后于2000年發(fā)布。即便USB-IF未將轉(zhuǎn)接驅(qū)動(dòng)器標(biāo)準(zhǔn)化,但轉(zhuǎn)接驅(qū)動(dòng)器在擴(kuò)展連接和電壓兼容性方面所具有的優(yōu)勢(shì)仍使其不可或缺。

2010年,隨著USB3.0的發(fā)布,USB的信號(hào)完整性問(wèn)題變得更加明顯,這推動(dòng)了轉(zhuǎn)接驅(qū)動(dòng)器產(chǎn)品投放市場(chǎng),以便擴(kuò)展Superspeed 5Gbps鏈路連接。USB3.1和Superspeed+10Gbps鏈路延續(xù)了這一趨勢(shì)。USB3.2規(guī)范通過(guò)USB-C連接器將USB3.0中的單通道模式擴(kuò)展為雙通道,進(jìn)一步促進(jìn)了轉(zhuǎn)接驅(qū)動(dòng)器的應(yīng)用。

USB-IF于2019年8月正式發(fā)布了USB4規(guī)范,將鏈路性能進(jìn)一步提高到了20Gbps/通道(雙通道達(dá)到40Gbps)。20Gbps信號(hào)較之前脆弱很多,更容易受到ISI、通帶紋波、抖動(dòng)源、模擬失調(diào)、終端失配、對(duì)內(nèi)偏移、反射、熱噪聲和電源噪聲的影響。結(jié)果,轉(zhuǎn)接驅(qū)動(dòng)器應(yīng)用于USB的時(shí)代又將終結(jié)。

更新的高速互連規(guī)范將推動(dòng)新一代信號(hào)調(diào)節(jié)解決方案的發(fā)展。數(shù)字重定時(shí)器是在極具挑戰(zhàn)的信道上發(fā)送超高速數(shù)據(jù)同時(shí)保持信號(hào)完整性的關(guān)鍵因素。當(dāng)速率高于10Gbps時(shí),使用轉(zhuǎn)接驅(qū)動(dòng)器將面臨許多困難,因此,業(yè)界期望推進(jìn)重定時(shí)器的使用,并將其寫(xiě)入了最新規(guī)范。

總而言之,諸如轉(zhuǎn)接驅(qū)動(dòng)器和重定時(shí)器這類信號(hào)調(diào)節(jié)技術(shù)在許多系統(tǒng)環(huán)境中都非常有用。但當(dāng)數(shù)據(jù)速率超過(guò)10Gbps時(shí),轉(zhuǎn)接驅(qū)動(dòng)器便不再適合許多應(yīng)用。在OIF/以太網(wǎng)生態(tài)系統(tǒng)中,重定時(shí)器已成為首選的信號(hào)調(diào)節(jié)器。在PCIe生態(tài)系統(tǒng)中,PCI4.0是轉(zhuǎn)接驅(qū)動(dòng)器的最后一搏,重定時(shí)器則可提供更好的解決方案。在USB生態(tài)系統(tǒng)中,USB4是一個(gè)轉(zhuǎn)折點(diǎn),此時(shí)轉(zhuǎn)接驅(qū)動(dòng)器已不是系統(tǒng)的最好選擇;而具有協(xié)議感知能力的重定時(shí)器則實(shí)現(xiàn)了所需的信號(hào)完整性,提供了穩(wěn)健、明確的發(fā)展線路以及低成本的系統(tǒng)解決方案,可以充分滿足消費(fèi)者的需求。

? ? ? ?責(zé)任編輯:pj

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論