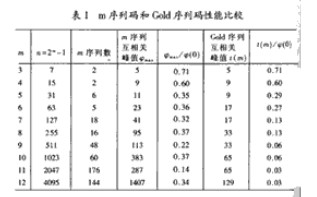

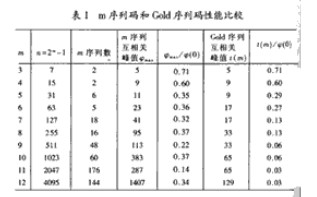

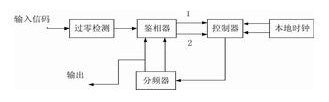

本文介紹一種基于現場可編程門陣列(FPGA)的通信系統同步提取方案的實現。本文只介紹了M序列碼作為同步頭的實現方案,對于m序列碼作為同步頭的實現,只要稍微做一下修改,即加一些相應的延時單元就可以實現。

2013-04-11 10:53:23 5696

5696

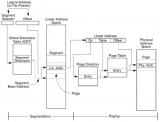

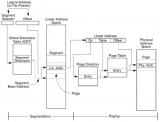

的數據可能不在內存中。 Linux內核地址映射模型 x86 CPU采用了段頁式地址映射模型。進程代碼中的地址為邏輯地址,經過段頁式地址映射后,才真正訪問物理內存。 段頁式機制如下圖。 linux內核地址空間劃分 通常32位Linux內核地址空間劃分0~3G為用戶空

2018-05-08 10:33:19 3776

3776

大家好,51單片機 位地址 單元地址 字節地址?我對著三個概念比較模糊,有懂的朋友請講,越詳細越好。

2013-08-09 11:15:41

如何獲知寫數據所在的地址和數據長度?有沒有寄存器可供查詢?是否必須自定義一個寄存器,用來存儲地址和長度,當發送完畢后,dsp讀該寄存器,然后進行操作?問題3:以下流程是否正確?為提高帶寬?是否需要完善?1

2019-01-09 10:58:04

FPGA已經在I/O路徑中加入了可編程的硬件模塊。這些模塊很容易使設計人員在FPGA中實現邏輯功能。為支持更高的數據率, LatticeECP2M器件中的SERDES模塊進一步在硬件中實現一些高速協議功能。而FPGA內的結構則用來實現更高層的數據處理功能。

2018-11-26 11:17:24

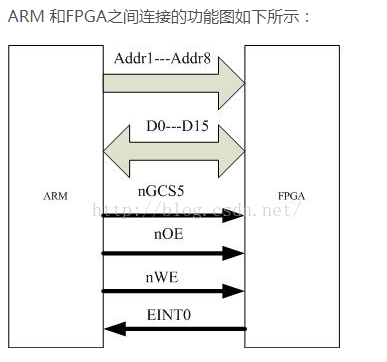

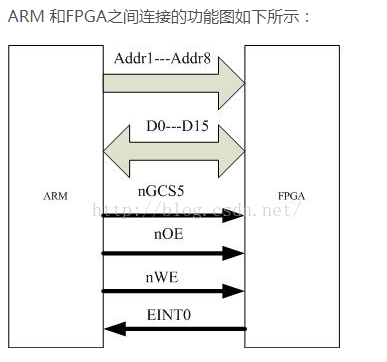

1 前言現場可編程邏輯器件(FPGA)在高速采集系統中的應用越來越廣,由于FPGA對采集到的數據的處理能力比較差,故需要將其采集到的數據送到其他CPU系統來實現數據的處理功能,這就使FPGA系統與其

2011-11-24 16:10:01

功能框圖。它內部分為兩條,每條 1M 字節,數據寬度為 8 位,故存儲總容量為 2M 字節。所有輸入和輸出操作都是在時鐘 CLK 上升沿的作用下進行的,刷新時鐘交替刷新內部的兩條 RAM

2020-04-23 08:00:00

文章目錄一、地址映射和寄存器映射原理1.地址映射2.寄存器映射二、GPIO端口的初始化三、實現LED燈參考文獻一、地址映射和寄存器映射原理首先要清楚的一點,所有操作,最終目的都是操作寄存器1.地址

2022-03-02 06:36:34

ARM跟FPGA通信,要采用8位地址總線、8位數據總線、讀寫控制線,怎么實現,地址總線是要映射到FPGA的內部還是直接ARM的內存空間?最好有ARM端簡單的C程序描述下,謝謝。

2022-11-22 14:58:26

51單片機串口不同尋常的特征是包括第9位方式(在串口模式2和模式3下)。它允許把在串行口通信增加的第9位用于標志特殊字節的接收。一般約定第9位為高時表示該字節為地址字節,第9位為低時為數據字節。

2020-03-16 07:15:29

為了能直接操作 ODR 的某個 Bit 位,在內核中開辟了一塊地址區域(位帶別名):可將 ODR這類 Bit 位(位帶區)映射到位帶別名區域對應的地址,只需操作映射后的地址,就可實現操作 ODR1 位

2025-11-18 07:03:05

mode讀取數據(按照datasheet33頁的介紹做的),發現數據字節數不對,后用示波器測量此時DRDYB管腳變成200Hz方波了;

3、使用的配置DRDYB_SRC_REG(地址0x27)的值是0x08, CH_CNFG_REG(地址0x2F)值是0x70。

不知道是哪里出了問題,還請各位幫忙解答下,謝謝。

2025-01-13 08:32:48

;amp;quot;memset/memcpy"函數。FPGA連接到ARM的GPMC總線CS1的起始地址為0x1000000,GPMC數據線位寬為16bit,數據線地址線復用

2018-05-16 14:28:40

本文檔描述了ARM用于A級系統的地址映射,來自模型和模擬器到開發板和復雜的SoC。

它解釋了存儲器、外圍設備和擴展的地址分區選擇空間。

它描述了當32位平臺操作系統使用36位或40位地址空間,以及32位總線主控器和外圍設備。

它將存儲器映射擴展到未來64位ARM系統的48位地址空間,

2023-08-02 08:19:29

有哪位大神知道AT24CXX的器件地址和數據地址是怎么確定的

2016-10-24 20:21:34

你好!設置 RB_ROM_CODE_OFS 位時的閃存地址映射是什么?CodeFlash 向下移動了 0x8000 字節,但 DataFlash 尋址是否以相同的方式移動(即變為

2022-08-30 07:31:04

期望的是,NDEF 消息是外部類型,ID = 0x06,長度為 1 和 3 個數據字節(0x12、0x34、0x56)我得到的是一個類型為外部 (OK) 和 3 個數據字節 0x12、0x00

2023-01-31 08:46:57

。7、32為源IP,目的IP,十六進制表示。8、選項和數據表示IP層之上的數據包。UDP報文1、16位UDP長度,表示整個UDP包字節數。2、16為校驗和,偽頭部( 4byte源IP地址

2014-03-25 12:46:56

目錄1:前言2:地址(門牌號)3:STM32地址映射4:位帶操作原理5:位操作代碼實現1:前言 以前學51的時候,沒有注重地址的這個概念,因為51寄存器少,一個reg52.h里面涵蓋了你要用到的所有

2021-08-13 06:05:28

這里寫目錄標題STM32(CM3內核) 內存映射一.CM3內核簡介二.CM3內核地址映射三.搭建代碼,實現映射STM32(CM3內核) 內存映射一.CM3內核簡介《CM3權威指南》摘抄一段簡介

2022-02-11 07:48:56

:地址和數據的各個字節首先通過LSB傳輸。命令字節、地址字節和數據字節的8位CRC由bq2024計算并由主機讀回,以確認接收到正確的命令字、起始地址和數據字節。 如果主機讀取的CRC不正確,則必須

2020-07-06 09:18:02

hyperLink_cfg.address_map.rx_priv_id_sel = RX_PRIVID_SEL_ADDR_31_28; //接收端接收到數據后高四位為特權ID

2018-12-28 11:09:22

段長度隨功能碼變化,典型結構包含:

寄存器地址:2字節,指定操作目標(如讀取從40001開始的寄存器)

數據長度:2字節,定義讀取/寫入的寄存器數量

寫入值:根據功能碼不同,可為1位線圈值或16位寄存器值

2025-11-17 08:15:29

和常量數據,全局變量數據以及運行時動態申請內存所分配的實際物理內存存放位置。MMU采用頁表(page table)來實現虛實地址轉換,頁表項除了描述虛擬頁到物理頁直接的轉換外,還提供了頁的訪問權限(讀

2020-11-03 16:20:06

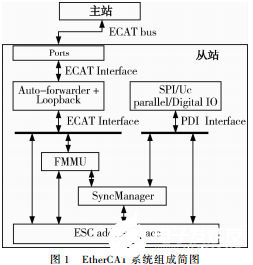

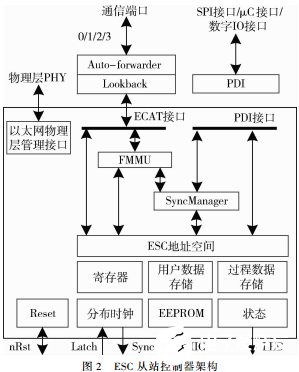

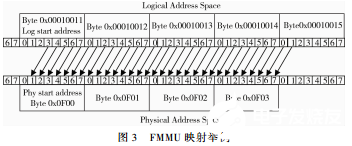

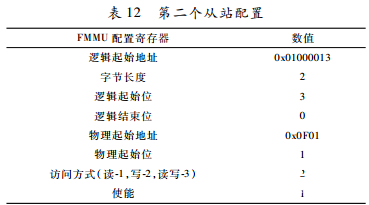

三、EtherCAT 主站 SOEM 源碼解析----IOmapSOEM 通過函數 ec_config_map(&IOmap)完成邏輯地址和物理地址的映射,應用程序需要定義一個數

2023-04-20 14:35:51

在STM32中,RAM、CODE、寄存器等都共用一個32位的地址總線32位線性地址空間總容量為4GB,數據字節以小端形式存放在存儲器中。一個字里的最低字節被認為是該字的最低有效字節。?以0x4000

2021-08-19 06:38:58

的半導體電路具現的,具體的實現的方式我們現在不管。存儲單位一般是字節。這樣,每個字節的存儲單元對應一個地址,當一個合法地址從存儲器的地址總線輸入后,該地址對應的存儲單元上存儲的數據就會出現在數據總線上面。圖

2022-05-23 15:03:37

我知道可以與Thingspeak 通信,但是是否可以將數據字符串發送到另一個網站(在我的項目中是端口 4600)正在等待 38 字節的數據字符串?收到此字符串后,服務器將向同一 IP 地址發回一條短消息。目前這可能嗎?我應該使用 wget 命令嗎?

2023-04-26 08:41:37

),它與SPI IP core define的寄存器映射不匹配(見圖3)。另外,當主端口(Avalon MM)的數據寬度為8位時,無論SPI如何設置數據位寬,QSYS自動分配的字節數為8個字節。當主端口

2018-06-19 14:26:57

通過編程來改變內部結構的芯片。FPGA 功能實現:需要通過編程即設計硬件描述語言,經過 EDA 工具編譯、

2022-01-25 06:45:52

192.168.1.254。FPGA將接收的數據在發回PC端,實現回環。其中TCP server和TCP client模塊需要先建立連接,之后才能發送數據。測試結果如下圖所示,可見以太網功能正確實現。

四、總結

2025-10-30 07:45:31

中的從 FIFO 2 位異步示例,我們在發送二進制文件時遇到了一個問題。

文件詳細信息:

二進制文件包含從地址 0x1400 到 0x27FF 的數據。

文件大小為 10240 字節。

問題: 在

2025-05-21 07:31:00

1MB大小的空間,所以全映射時,條目總數(全映射時頁表所占內存空間)=4GB / 1MB =4096條(每條32位,即4字節,共 4 KB)。其中,所謂的每個條目大小為1MB,意思是,CPU發出的一段

2016-12-08 09:37:55

描述SBC-85 8085總線監視器,單步,二進制和十六進制顯示,斷點缺少在線仿真器,總線監視器是最強大的診斷工具之一。總線監視器提供以下功能:地址和數據字節的二進制和十六進制顯示所有 8085

2022-08-22 06:27:43

由RS232接口接收十六進制數據字符串如下:FF80 8080 0080 FF80 8080 20A0.................每組數據如上兩組數據格式相同,請問如何提取最后一組數據,即將最后一組FFxx xxxx xxxx分別提取出來,并變為十進制數值輸出。。。。。。。。。。。。。。。。

2014-07-23 11:32:06

的研究中大多進行仿真實驗,無法保證硬件實際輸出PN序列的產生及其性能的測試。為此,基于FPGA技術,利用Logistic混沌映射作為隨機信號源對實現PN序列的硬件進行了深入研究,提取Logistic數值

2019-07-05 07:33:06

的數據傳輸。該設計主要采用硬件描述語言VerilogHDL在可編程邏輯器件FPGA上實現,由于數據采集功能模塊繁多,而Wishbone總線可以與任何類型的ROM或RAM相連,因此需在SDX總線與數據采集模塊

2019-05-31 05:00:07

、QDR_SA、QDR_BW_n 和 QDR_D)的布線長度必須完全匹配,以將控制、地址及數據線接至具備充足建立與保持余量的存儲器器件。物理接口的實現可確保這些信號在離開 FPGA 器件輸出時與QDR_K

2019-04-22 07:00:07

在串口的應用中,9位數據格式保含著8位的數據字節及1位的奇偶校驗位。另外在RS485應用中利用奇偶校驗位指出這是數據字節還是地址字節。在初始化串口之后,如下表所示,依照奇偶校驗位的電平,設定

2023-06-15 10:17:54

與FPGA上實現的總線接口基礎設施保持一致。雙QSPI配置接口為減少FPGA配置時間,許多現代FPGA允許將配置位流分區至兩個QSPI器件(圖3)。這兩個QSPI器件以并行方式連接,其中位流的低半字節

2021-05-26 07:00:00

CPU的按字節尋址和按字尋址的范圍分別是多少?如何去計算CPU的地址線和數據線?

2021-10-09 08:08:39

在FPGA中,動態相位調整(DPA)主要是實現LVDS接口接收時對時鐘和數據通道的相位補償,以達到正確接收的目的。那么該如何在低端FPGA中實現DPA的功能呢?

2021-04-08 06:47:08

我創建了具有正常優先級的單個任務。該任務具有三個功能。在一個函數中,我將 2 字節數據寫入內部 SRAM(例如 0x20010204 的起始地址)。2 字節數據分別寫入內存地址 0x20010204

2022-12-27 08:18:13

,已知一次數據傳輸為一個字節,既八位二進制的數據,傳輸一個字節數據即可實現功能。故定義其高四位作為從機地址,低四位作為數據位。RS485通信#include "reg52.h" typedef unsigned int u16; //對數據類型進行聲

2021-12-02 07:21:31

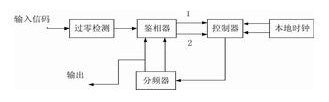

本文主要研究了一種基于FPGA、自頂向下、模塊化、用于提取位同步時鐘的全數字鎖相環設計方法。

2021-05-06 08:00:46

一個4GB的線性地址空間。數據字節以小端模式存放在存儲器中。地址空間分8塊,每塊512MB。注: 小端模式:與大端模式相對應,將數據的低字節保存在內存的低地址中,高字節保存在高地址中。其中:?...

2021-12-09 07:51:09

9中的流程圖說明主機發出Write Status命令55h,然后是地址低字節,然后是地址高字節,最后是要編程的數據字節。注意地址和數據的各個字節首先通過LSB傳輸。命令字節、地址字節和數據字節的16位

2020-09-14 17:36:04

映射以及SRAM存取,DMA模式控制;OBCI3接口控制;線路端編解碼功能。圖1 網關接口板功能結構圖設計描述FPGA的主要功能模塊如圖2所示。處于框圖上端的部分主要是數據流處理部分,主要完成數據

2019-04-23 07:00:08

高電平,發送完成把TXENABLE

管腳置為低電平,這樣就ok?

(3)AD9779A的SPI接口: 當使用單字節傳輸的時候,指令字節和數據字節之間是否可以把CSB管腳拉高?

謝謝!

2023-12-20 07:12:27

STM8 UART發送器根據M位的狀態發送8位或9位的數據字

2020-11-11 06:35:06

圖一是“接收內容”創建字符串類的屬性-顯示樣式(因為十六進制顯示才能正常接收,否則亂碼),圖二是modbus rtu 協議的數據傳輸,圖三是我接收的傳感器傳輸的其中一組數據,請問如何實現數據位的提取?謝謝

2019-03-30 15:07:31

在串口的應用中,9位數據格式保含著8位的數據字節及1位的奇偶校驗位。另外在RS485應用中利用奇偶校驗位指出這是數據字節還是地址字節。在初始化串口之后,如下表所示,依照奇偶校驗位的電平,設定

2023-06-20 08:07:09

通過51單片機寫數據到SD卡后如何統計寫入的數據字節的大小

2020-04-18 01:03:56

控制FPGA實現的邏輯控制功能包括與上位機軟件iMPACT和串口工具通信、燒寫Flash以及配置FPGA器件。基于模塊化的設計思想將具體功能分解成多個模塊,如圖3所示,數據與地址通道上的下標為其通道寬度

2019-05-30 05:00:05

對齊、多通道對齊)是必須的 。字節對齊:設計確定在數據流的哪里是10位數據字節的開始和結束。在FPGA結構中使用有限狀態機(FSM)來完成這一任務。把數據流的第一個和第二個 10位組合在一起,形成一個

2019-06-06 05:00:34

和常量數據,全局變量數據以及運行時動態申請內存所分配的實際物理內存存放位置。MMU采用頁表(page table)來實現虛實地址轉換,頁表項除了描述虛擬頁到物理頁直接的轉換外,還提供了頁的訪問權限(讀

2020-11-19 10:52:17

針對報文解析過程中存在的數據存儲無序、查詢和調用不便等問題,提出應用XML 數據字典進行數據存儲的方案。根據給定的數據表,設計XML 形式的數據字典。實現XML 字典數據的解

2009-03-28 09:38:52 36

36 ARM啟動代碼及地址映射

2010-02-11 11:00:27 104

104 基于FPGA的提取位同步時鐘DPLL設計

在數字通信系統中,同步技術是非常重要的,而位同步是最基本的同步。位同步時鐘信號不僅用于監測輸入碼元信號,確保收發

2010-01-25 09:36:18 3699

3699

基于fpga的鎖相環位同步提取電路

該電路如圖所示,它由雙相高頻時鐘

2010-10-08 12:00:23 1743

1743

介紹 AES 中的字節替換算法原理并闡述基于FPGA的設計和實現。為了提高系統工作速度,在設計中應用了流水線技術。最后利用MAXPLUS-II開發工具給出仿真結果,并分析了系統工作速度。

2011-09-27 15:54:04 6641

6641

位同步提取實驗的實驗報告,位同步提取實驗的實驗報告,位同步提取實驗的實驗報告

2016-05-26 10:58:41 0

0 現場可編程邏輯門陣列(FPGA)應用于圖像處理時,需要對數據中的圖像信息進行準確的提取。設計中,FPGA中解壓縮功能需要對壓縮數據中的圖像信息進行提取。根據壓縮格式,設計了一種基于狀態機的圖像

2017-11-17 06:04:02 2595

2595

原文鏈接:freescale 16位單片機的地址映射--(1)前言 freescale 16位單片機的地址映射--(2)飛思卡爾16位單片機的資源配置 freescale16位單片機的地址映射

2017-11-24 07:43:33 1402

1402 本文將詳細地討論簡化UART功能在FPGA中的實現方法。簡單回顧一下異步串行通信的數據格式。圖2表明在異步傳送中串行發送一個數據字節的位定時關系(圖中沒有包括奇偶校驗位)。發送一個完整的字節信息

2018-04-04 12:45:00 28418

28418

眾多領域。在圖像檢測系統中,應具備一個高速的子圖像提取和輸出模塊,本文采用FPGA 器件EP3C25F256C8 和CCD 線陣圖像傳感器RL1024P,實現線陣CCD 圖像檢測系統中的子圖像提取和輸出功能。

2019-04-29 08:22:00 3526

3526

一般的位同步電路大多采用標準邏輯器件按傳統數字系統設計方法構成,具有功耗大,可靠性低的缺點。用FPGA設計電路具有很高的靈活性和可靠性,可以提高集成度和設計速度,增強系統的整體性能。本文給出了一種基于fpga的數字鎖相環位同步提取電路。

2019-04-19 08:24:00 4278

4278

視頻中展示了各種連接至FPGA開發系統并受其控制的MEMS傳感器和數據轉換器件。Avnet Xilinx Spartan?-6 FPGA LX9 MicroBoard、Digilent Pmods?和Arrow Altera Cyclone IV BeMicro SDK。

2019-07-05 06:00:00 2652

2652 我們可以把存儲器看成一個具有輸出和輸入口的黑盒子。如下圖所示,輸入量是地址,輸出的是對應地址上存儲的數據。當然這個黑盒子是由很復雜的半導體電路具現的,具體的實現的方式我們現在不管。存儲單位一般是字節

2019-08-16 17:31:00 0

0 MCS-51單片機的內部數據存儲器(RAM)共有128個字節,地址為00H~7FH 。其中的20H~2FH單元是可作為可位尋址的一個區域,共128位,用位地址00H~7FH與之對應。例如:位7FH

2019-07-25 17:36:00 0

0 2、 主機先發送一幀地址信息,其中8位地址,第9為為地址/數據信息的標志位,該位置1表示該幀為地址信息。

2020-04-05 11:42:00 6607

6607

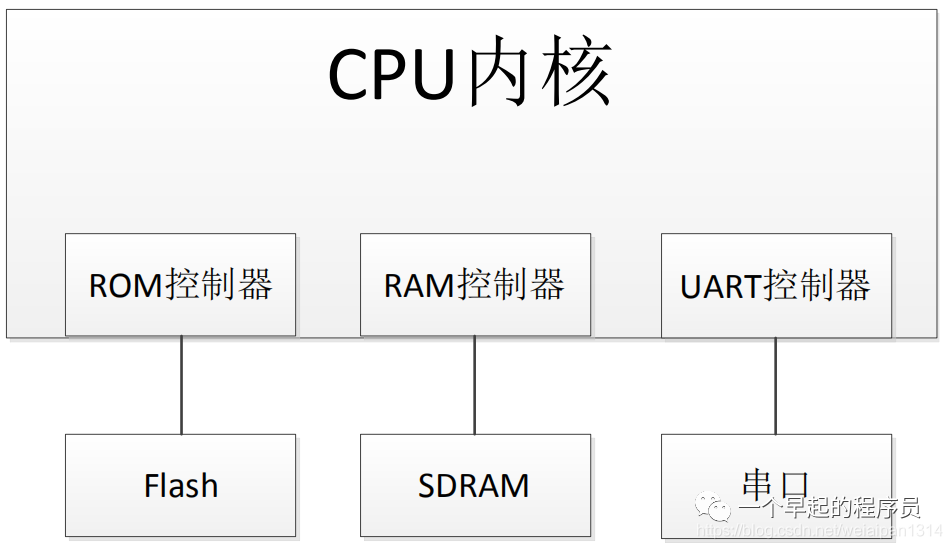

從CPU的總體結構到局部功能的實現采用了自頂向下的設計方法和模塊化的設計思想,利用Xilinx 公司的Spartan II 系列FPGA,設計實現了八位CPU軟核。在FPGA內部不僅實現了CPU必需

2020-08-03 17:58:56 13

13 從CPU的總體結構到局部功能的實現采用了自頂向下的設計方法和模塊化的設計思想, 利用Xilinx 公司的Spartan II 系列FPGA, 設計實現了八位CPU軟核。在FPGA 內部不僅實現了

2020-08-19 17:43:19 7

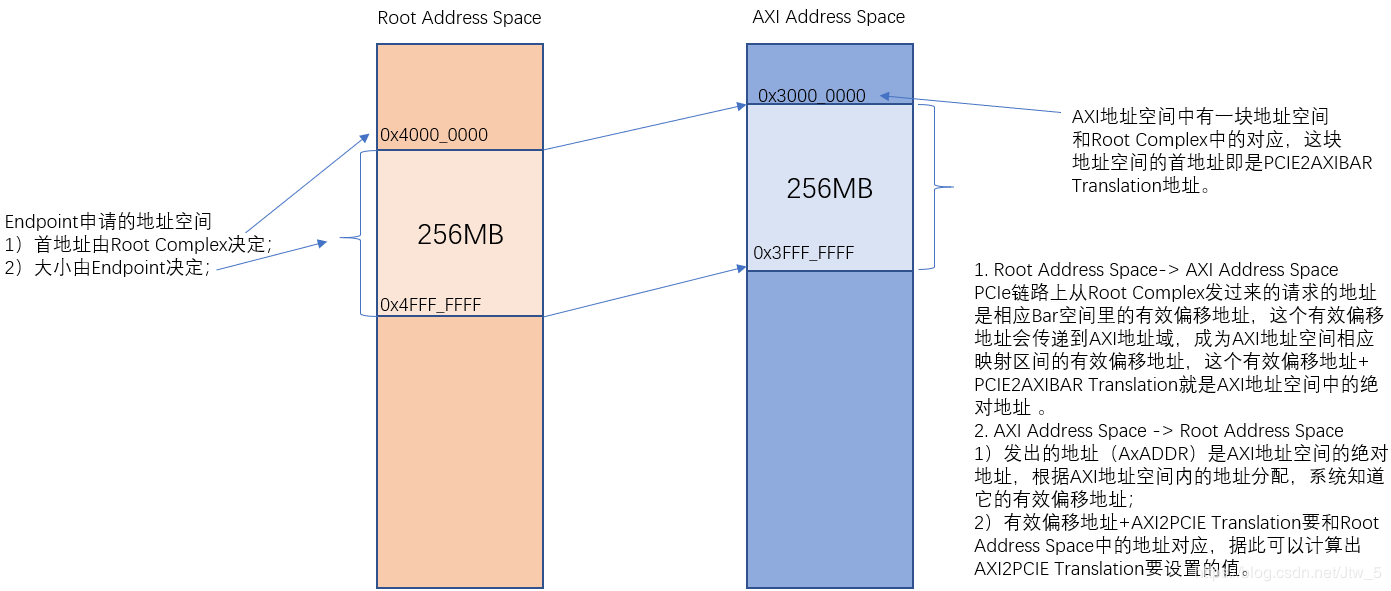

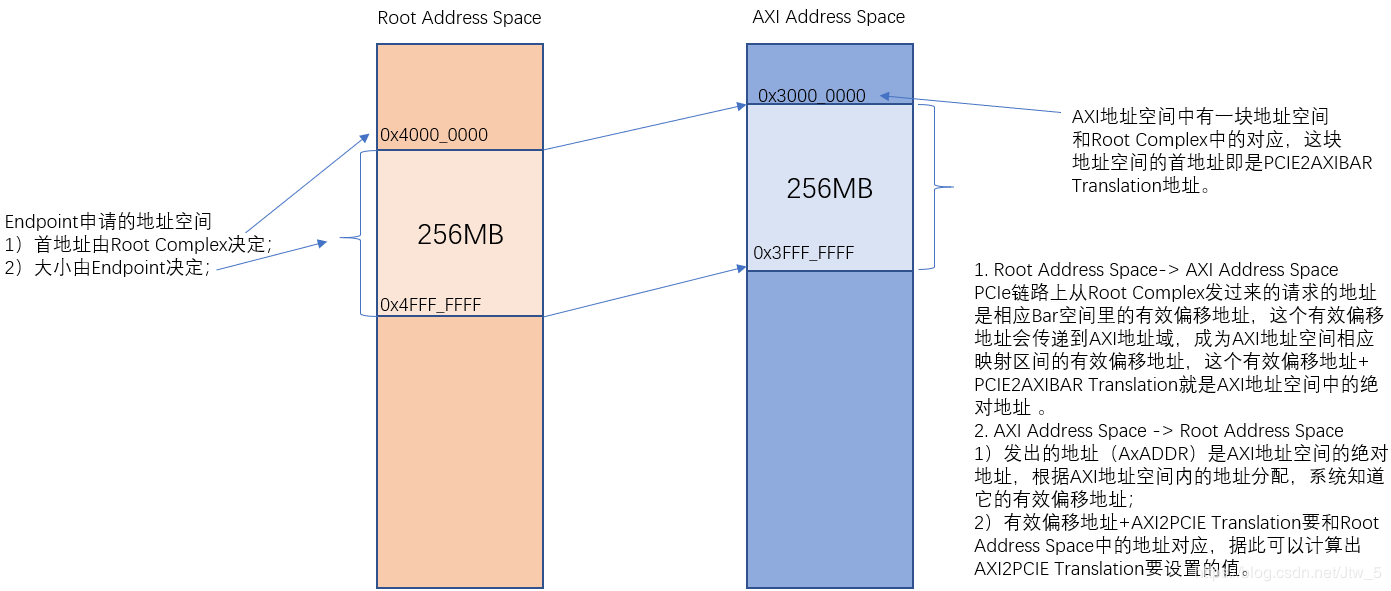

7 (Root Complex中的系統地址空間)到AXI域(FPGA邏輯中的AXI地址空間)。PCIe發起的對Endpoint的訪問應在Endpoint申請的BAR空間內,Endpoint申請BAR空間

2020-11-20 15:28:52 8159

8159

到局域網絡上的所有主機,并接收返回消息,以此確定目標的物理地址;收到返回消息后將該IP地址和物理地址存入本機ARP緩存中并保留一定時間,下次請求時直接查詢ARP緩存以節約資源。地址 ARP映射方式 靜態映射 靜態映射的意思是要手動創建一張ARP表,把邏輯(IP)地址和物理地址關聯起來。 動態

2021-08-22 10:47:54 3958

3958 CAN總線上日益增長的帶寬需求。相比于CAN2.0主要有2點增強:將數據位段增加到最多64數據字節(CAN 2.0最大為8個數據字節)。標稱位和數據位使用不同的比特率,標稱位的比特率和CAN...

2021-10-29 11:21:11 19

19 ArmCortex-M4處理器采用哈佛結構,可以使用相互獨立的總線來讀取指令和加載/存儲 數據。指令代碼和數據都位于相同的存儲器地址空間,但在不同的地址范圍。程序存儲器, 數據存儲器,寄存器和I/O

2021-12-04 13:51:04 13

13 STM32F103系列芯片的地址和寄存器映射原理、LED輪流閃爍實現文章目錄STM32F103系列芯片的地址和寄存器映射原理、LED輪流閃爍實現1 寄存器介紹1 寄存器介紹寄存器是中央處理器內

2021-12-05 15:21:04 3

3 這里寫目錄標題STM32(CM3內核) 內存映射一.CM3內核簡介二.CM3內核地址映射三.搭建代碼,實現映射STM32(CM3內核) 內存映射一.CM3內核簡介《CM3權威指南》摘抄一段簡介

2021-12-07 19:21:12 9

9 位待操作是如何實現的代碼代碼解讀基地址映射偏移地址映射例程STM32地址基地址、總線地址、寄存器地址是什么基地址以及偏移地址這是stm32的系統結構圖,只需要看一下紅線框出來的地方即可從下圖可以看到

2022-01-12 18:21:32 1

1 本文介紹如何試用MediaPipe實現人臉3D點云數據提取,提取的數據為人臉468點位。

2023-02-23 17:47:23 2490

2490 。這些關系通常不明確,并且可以跨越數據庫。Dataedo將數據庫中的外鍵讀取到數據字典中,允許您使用手動定義的關系擴展此信息,并使用ER圖將它們可視化。 提取外鍵 定義額外的表關系 可視化ERD中的表關系 定義跨數據庫和數據集的關系 用學科領域

2023-06-19 09:52:32 1244

1244

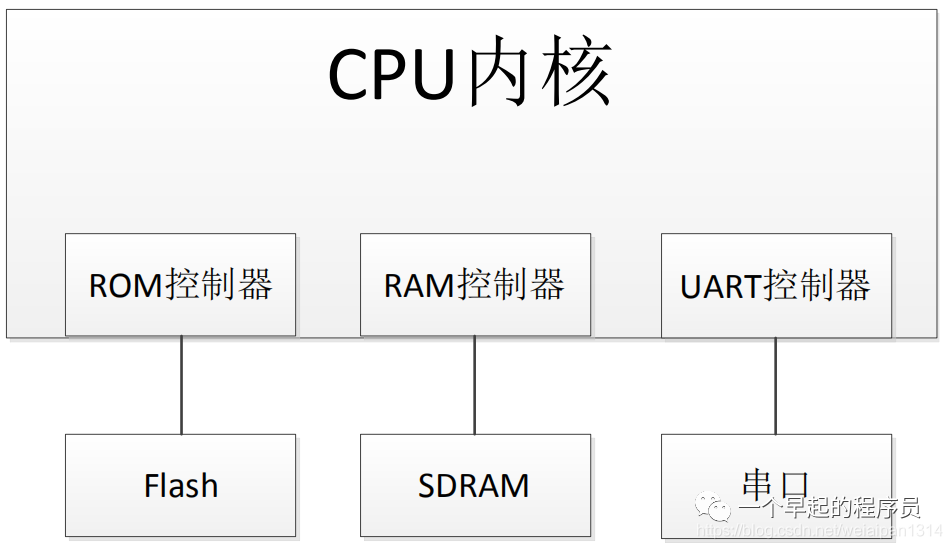

很多人對總線和地址映射的概念都是一頭霧水,但是我們如果知道為何需要總線和地址映射,他們是在什么背景下被衍化出來的,自然而然對此概念就清清楚楚了。

2023-07-24 11:14:59 1880

1880

can總線的數據幀中數據長度碼和數據字節數的關系? CAN總線是一種常用于數據通信的協議,它使用數據幀來傳輸信息。在CAN數據幀中,數據長度碼(DLC)和數據字節數是緊密相關的。 首先,我們來了

2024-01-31 11:31:52 4199

4199 fpga和數字ic區別 FPGA(現場可編程邏輯門陣列)和數字IC(集成電路)在設計、功能、應用等方面存在顯著的區別。 FPGA和數字IC在設計上有不同的特點。FPGA是一種可以重構電路的芯片,其

2024-03-14 18:08:23 4332

4332

電子發燒友App

電子發燒友App

評論