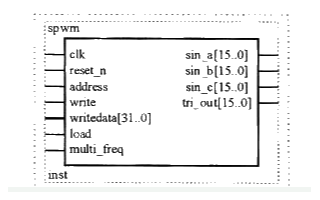

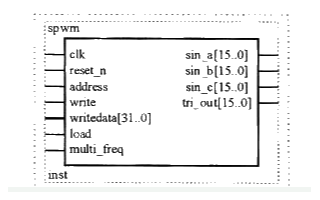

1. 背景 這篇文章主要介紹了DDR3IP核的寫實現。 2. 寫命令和數據總線介紹 DDR3 SDRAM控制器IP核主要預留了兩組總線,一組可以直接綁定到DDR3 SDRAM芯片端口,一組是留給

2020-12-31 11:17:02 6783

6783

有誰需要ALTERA的ip核,qq57694560,cjfwindy@163.com [此貼子已經被作者于2009-10-14 14:26:18編輯過]

2008-11-16 19:50:33

我用的是CYCLONEIII的芯片,定制DDR2 IP核,之后直接用SINALTAP進行信號抓取,發現無法讀寫的原因是local_init_done 一直為低,就像XILINX里

2013-04-27 09:46:54

本帖最后由 dybttkl 于 2015-11-1 13:26 編輯

用的cycloneiii 里面的ddr2 ip核。感覺網上的資料很少,仿真的倒很多,但是真正到用戶接口那段時序的解釋卻一個也沒有。為何沒人寫個教程

2015-11-01 13:24:54

研究了很久,實在弄不出來了,有沒有人用過Altera的PCIe IP核???急求!!!謝謝!!!求大神幫忙......

2016-05-26 09:12:33

小弟用的quartus ii軟件,調用altera公司的一個乘法器lpm_mult,無結果輸出,是不是調用的IP核都要收費呢,有沒有辦法破解呢????

2015-06-05 11:23:31

以下主題概述了Altera的外部內存接口解決方案。

Altera提供最快、最高效、延遲最低的內存接口IP核。Altera的外部存儲器接口IP設計用于方便地與當今更高速的存儲器設備接口。

Altera

2023-09-26 07:38:12

Altera系列FPGA芯片IP核詳解

2020-06-28 13:51:01

Altera_IP核,僅供參考

2016-08-24 16:57:15

實現特權同學的例程 特權FPGA VIP視頻圖像開發套件例程詳解2——DDR2控制器讀寫測試 時,進行IP核配置時,進入下一步配置參數時,變成黑屏重裝軟件也不行

2018-01-24 08:23:17

使用altera的FFTIP核的可變流結構進行FFT時,輸出為什么跟實際情況是倍數關系

2016-09-20 19:18:10

最近在使用altera的FIR IP核做半帶濾波器,quartus ii軟件也破解了,firIP核也破解了,modelsin仿真也通過了,但是下載不了.sof文件到開發板,大家有用FIR IP核成功實現下板的經驗嗎,求大神指點呀。謝謝!

2018-05-11 16:01:15

altera公司IP核使用手冊

2012-08-15 13:11:24

altera公司IP核使用手冊,分享給想學習altera公司FPGA的IP核使用的親們~~

2013-02-16 22:40:19

問題:采用altera公司的ep4ce6e22c8控制器的一對差分引腳實現差分輸入輸出配置功能嘗試方法:嘗試配置LVDS IP核,但發現只有單獨的輸入輸出,如圖

2019-10-20 22:13:05

機制對當前變長分組骨干網的流量控制還是具有重要的參考價值,所以有必要對ATM的流量控制及其實現方式進行深入的研究。 IP核是一段具有特定電路功能的硬件描述語言代碼,該程序與集成電路工藝無關,因而

2011-09-27 11:54:25

CAN控制器IP核(可直接在Nios II中使用)

2016-08-24 16:54:21

(Intellectual Property Core)。本文介紹USB 2.0設備控制器IP中的AHB接口部分設計。1設計概述1.1協議概述 設計前首先需要了解USB和AHB數據傳輸的特點

2019-05-13 07:00:04

大家好,有沒有誰比較熟悉ALTERA公司的VIP系列ip核,我們用該系列IP核中的某些模塊(主要是scaler和interlacer)來實現高清圖像轉標清圖像(具體就是1080p50轉576i30

2015-04-13 14:12:18

modelsim 仿真 altera IP核(ROM,RAM實例)急求大神們ROM和RAM 的綜合仿真代碼

2015-11-19 21:02:57

本文介紹一款USB OTG IP核的設計與實現,該設備控制器可作為IP核用于SoC系統中,完成與主機控制器的通信,并能與普通的USB從設備進行通信。

2021-04-29 06:47:00

`例說FPGA連載41:DDR控制器集成與讀寫測試之DDR2 IP核接口描述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 如圖

2016-10-27 16:36:58

用 quartus 生成一個ddr2的ip核,選擇了生成仿真模型,但生成不了,文件目錄下沒有example.v,只有一個對應 的sdc文件 。 另外生成報告里還有 一個warning ,,求指導

2017-09-07 11:48:09

Altera系列FPGA芯片IP核詳解

2016-08-19 17:24:48

工具,經面向硬件電路的仿真驗證,本文的方法可實現OC-48接口(2.5Gb/s)上線速分組的IP碎片重組,并具有硬件開銷小,可擴展性好的特點。關鍵詞: IP碎片;FPGA;RLDRAM控制器;最大傳輸

2008-10-07 11:00:19

PCI接口控制器兆核函數(即接口IP)及相關測試平臺,通過選擇合適的芯片速度,可以滿足運行在33MHz或66MHzPCI時鐘下的時序要求,支持Altera的Stratix II、Stratix

2018-12-04 10:35:21

此提供了新的解決方案。IP核(IP Core)是具有特定電路功能的硬件描述語言程序,可較方便地進行修改和定制,以提高設計效率[3]。本文研究了基于FPGA的數據采集控制器IP 核的設計方案和實現方法,該IP核既可以應用在獨立IC芯片上,還可作為合成系統的子模塊直接調用,實現IP核的復用。

2019-07-09 07:23:09

任務需求來定制顯示控制功能,可以增強系統可靠性和設計靈活性,降低了成本。目前針對LCD 顯示屏設計的控制器IP 核文章較多[1-2],但對于TFT-LCD 觸控屏設計的控制器IP 核文章較少[3],而且

2018-11-07 15:59:27

,以及對應的波形圖和 Verilog HDL 實現。我們調取的 DDR3 SDRAM 控制器給用戶端預留了接口,我們可以通過這些預留的接口總線實現對該 IP 核的控制,本章節將會講解如何根據

2022-02-08 07:08:01

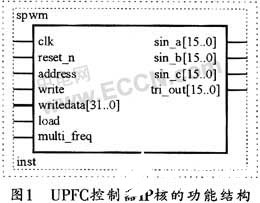

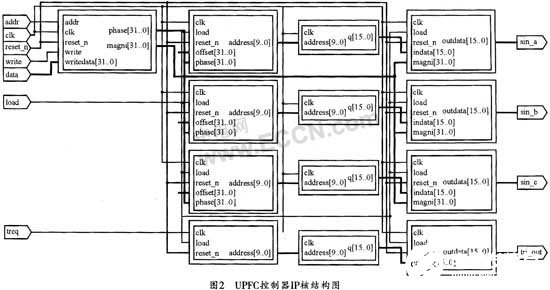

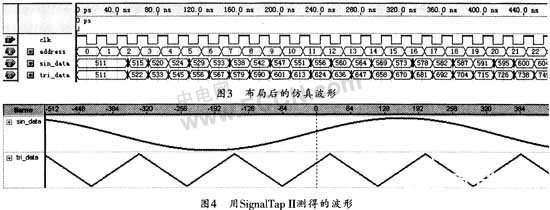

本文利用Altera公司的Quartus開發工具設計了一個基于Avalon總線接口的UPFC控制器IP核,以便于和NiosII組成一個完整的控制系統。

2021-04-08 06:25:12

本人想使用altera的以太網IP核tse核,發現Quartus里面并沒有告訴怎樣控制這個核。請問大家是怎樣控制這個IP核的呢?完全用Verilog代碼編寫控制程序,好像很復雜呀,難道只能通過NiosII軟核嗎

2015-01-22 14:55:31

請問Altera RAM IP核怎么使用?

2022-01-18 06:59:33

本文介紹的在電能質量監測系統中信號采集模塊控制器的 IP核,是采用硬件描述語言來實現的。

2021-04-08 06:33:16

系統級設計,設計人員現在使用SOPC Builder工具時,可以選擇Freescale?、ARM?或者Altera軟核處理器以及50多種其他的知識產權(IP)模塊。 &

2008-06-17 11:40:12

IP核的Verilog程序進行綜合時,可選用Altera公司的CycloneIIEP2C35評估板。該板有33216個邏輯單元,105個M4k存儲模塊,35個18×18乘法單元,4個PLL和475個I

2019-06-03 05:00:05

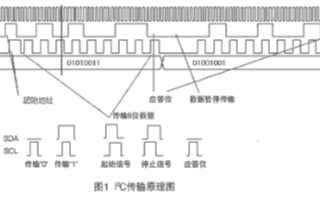

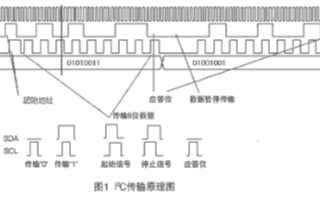

,我國也迫切需要發展自己的IP核。本文針對I2C的主方式串行擴展通信的特點,詳細給出設計過程和結果。1 IP核簡介 IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM

2019-04-12 07:00:09

I2C總線控制器 altera提供

The I2C Controller was designed for the MC68307 uC, provides a simplified

2008-05-20 10:25:01 251

251 TC35C25系列PWM控制器是目前取3525開關電源控制器的理想器件,本文介紹TC35C25系列pWM控制器的優點和特性外,重點講述該控制器的輸出級,振蕩器及其同步軟啟動以及壓鎖定部分的工

2008-11-19 18:18:50 19

19 本文提出了一種運動控制器軟IP 的設計方案,該控制器可以控制4 個軸的步進電機或數字伺服電機,可以進行各軸獨立的定位控制、速度控制,也可任選2 軸或3 軸來進行直線、圓弧

2009-07-07 15:22:50 21

21 研究了C8051 微控制器IP 軟核的參數化設計。首先介紹了指令系統的設計,其次從可重配置的存儲器容量、可取舍的并行輸入/輸出端口、是否產生UART 和定時/計數器模塊,以及可重

2009-07-30 11:12:33 17

17 本文介紹一款USB 設備控制器IP CORE 的設計與實現。論文首先介紹了USB 設備控制器的設計原理,模塊劃分及每個模塊的功能。然后介紹了該IP CORE 在ModelsimSE 中的功能仿真及FPGA 驗證結

2009-08-06 11:39:00 8

8 介紹了基于MicroBlaze 軟核處理器的可編程片上系統結構。提出了一種LCD 控制器IP 核的設計方法。該控制器具有片上外設總線接口,和其它標準IP 核一起組成以MicroBlaze 為核心的片上系

2009-08-31 10:58:53 11

11 本文討論了基于Avalon 總線流傳輸的配置LCD 顯示控制器IP 核的設計,根據自頂向下的設計思想,將IP 核進行層次功能劃分設計,并對IP 核的仿真驗證,最后加入到NiosII 系統中。該I

2009-11-30 14:33:46 16

16 介紹了基于IP 的可重用的SOC 設計方法;選用MC8051 IP 核為核心控制器,自主開發了UART IP 核、I2C IP 核、USB IP 核,采用Wishbone 片上總線架構,集成了一個MCU 系統;同時設計了針對此MCU

2009-11-30 15:06:20 33

33 本文提出了一種運動控制器軟IP 的設計方案,該控制器可以控制4 個軸的步進電機或數字伺服電機,可以進行各軸獨立的定位控制、速度控制,也可任選2 軸或3 軸來進行直線、圓弧

2009-12-04 11:52:52 14

14 用硬件描述語言verilog HDL 設計實現了一種MCU&USB 設備控制器IP 核。論文首先簡要介紹了設計的背景,重點對自主研發的將MCU&USB 控制器集成于一個芯片的設計和研究分析。最后

2010-01-20 11:44:09 22

22 基于Avalon總線的可配置LCD 控制器IP核的設計

本文討論了基于Avalon 總線流傳輸的配置LCD 顯示控制器IP 核的設計,根據自頂向下的設計思想,將IP 核進行層次功能

2010-02-09 09:34:44 27

27 本文以改善UPFC 動態性能為出發點,指出了UPFC 研究中存在的問題:1 目前針對UPFC 系統所建立的模型不完整,使得控制系統設計中存在缺陷;2 沒有一個有效、合理的潮流調節器參數

2010-02-22 10:00:31 19

19 介紹了系統芯片SOC的概念和M8051 IP軟核的原理,給出了視頻字符疊加器VAD_SOC中M8051 IP軟核的作用,詳細介紹了I2C主控制器模塊的設計,給出了功能仿真波形,最后對M8051IP軟核在視頻

2010-07-05 14:31:33 47

47 本文詳述了一種基于AMBA總線接口的IIC總線控制器IP核設計,給出了該IP核的系統結構以及各個子模塊的詳細設計方法,并對該IP核進行了功能仿真、FPGA原型驗證,可測性設計以

2010-07-17 16:20:22 21

21 提出了一種采用基于NiosII處理器的通用AD IP核來實現嵌入式數據采集系統的新方案。它能將市面上任意一款AD芯片制作成IP核并集成到NiosII系統中使用,且整個IP核的控制與運算邏輯由

2010-07-30 11:39:16 50

50 I2C器件接口IP核的CPLD設計

根據單片機I2C串行擴展的特點,在EDA軟件MaxplusII的環境下,利用AHDL語言,建立IP核。此設計利用狀態機實現,在給出設計的同時詳細說明IP核的建立

2009-03-28 16:21:35 1351

1351

USB2.0設備控制器IP核的AHB接口技術

介紹了USB2.0設備控制器IP核的AHB接口的設計。解決了雙時鐘域問題;實現了多事務DMA控制,減少了塊傳輸的中斷次數;

2009-03-29 15:14:15 1990

1990

摘 要: 根據單片機I2C串行擴展的特點,在EDA軟件MaxplusII的環境下,利用AHDL語言,建立IP核。此設計利用狀態機實現,在給出設計的同時詳細說明IP核的建立過程,并下載到

2009-06-20 13:36:12 1065

1065

基于PCI IP核的碼流接收卡的設計

本文介紹了一種基于Altera公司的PCI接口IP核的DVB碼流接收系統的硬件設計方案及設計要點的分析。該設計采用Altera公司的新一代FPGA

2009-09-26 18:02:08 912

912

MCU/USB設備控制器IP核的設計

1 引言

在傳統的計算機系統上常采用串口(如RS232)和并口連接外圍設備,但串口和并口都存在著通信速度 慢

2009-12-08 11:11:08 927

927

0 引言

NIOSⅡ是Altera公司推出的第二代IP軟核處理器。它與其他IP核可構成SOPC系統的主要部分。Altera SOPC Builder提供有NiosⅡ處理器及一些常用外設接口,因此,對于一

2010-08-16 09:44:23 1734

1734

提出了一種基于 PicoBlaze 的Nand Flash控制器的實現方法。PicoBlaze是Xilinx公司開發的8位嵌入式微控制器IP核。首先介紹了PicoBlaze的概念和實現方式,接著詳細描述了基于PicoBlaze核心的控制器

2011-06-13 15:48:36 41

41 本內容寫出了CAN總線控制器IP核的代碼,并做出了詳細分析

2011-06-28 11:39:42 6798

6798 為滿足嵌入式系統中專用芯片功能不能達到系統要求的現狀,設計出一種功能可擴展的I2C slave控制器,這種控制器與傳統的專用I2C芯片不同。專用的I2C芯片的功能具有固定性,只能實現

2011-10-25 16:58:02 60

60 本文側重于介紹IP 模塊中組件控制器的設計和實現。一個基于FPGA 的LCD 控制器設計作為例子被介紹。這個組件控制器設計屬于固核IP 設計,也就是軟硬結合的方法。設計內容主要包括電

2011-12-22 14:00:11 1634

1634

根據Nios II處理器的Avalon總線規范,設計了一款面向步進電機的控制器IP核。該定制IP核采用軟、硬件協同設計的方法,功能符合Avalon總線的讀寫傳輸時序,具有完備的步進電機驅動能力。仿

2011-12-23 14:02:32 44

44 隨著可編程邏輯器件的不斷進步和發展,FPGA在嵌入式系統中發揮著越來越重要的作用。本文介紹的在電能質量監測系統中信號采集模塊控制器的 IP核,是采用硬件描述語言來實現的。

2012-05-22 16:01:22 1808

1808

介紹一款基于SOPC的TFT-LCD觸控屏控制器IP核的設計與實現。采用Verilog HDL作控制器的模塊設計,并用ModelSim仿真測試,驗證其正確性;利用嵌入式SOPC開發工具,在開發板上完成觸控屏顯示

2012-08-13 17:22:18 53

53 altera公司IP核使用手冊(英文版),需要的可下載 Chapter 1. About this MegaCore Function Release Information

2012-08-15 15:15:31 0

0 IP核生成文件:(Xilinx/Altera 同) IP核生成器生成 ip 后有兩個文件對我們比較有用,假設生成了一個 asyn_fifo 的核,則asyn_fifo.veo 給出了例化該核方式(或者在 Edit-》Language Template-》C

2012-08-15 15:57:09 35

35 本設計基于FPGA的彩色觸摸屏控制器能夠實現顏色深度為24 bit,分辨率為480×272的TFT-LCD控制和ADS7843芯片的時序控制,為后續IP核的編寫工作打下了基礎。

2013-01-07 11:08:20 3441

3441

基于SOPC的步進電機加減速PWM控制器IP核設計

2016-05-03 13:52:59 18

18 TC35C25系列PWM控制器是目前取代3525開關電源控制器的理想器件。本文除介紹TC35C25系列PWM控制器的優點和特性外,重點講述該控制器的輸出級、振蕩器及其同步、軟啟動以及欠壓鎖定部分的工作原理;同時還給出了有關的重要參數及典型電路。

2016-05-10 14:24:39 8

8 基于Avalon總線的非標準以太網控制器IP核設計_薛毅

2017-03-19 11:33:11 1

1 提出一種便于用戶操作并能快速運用到產品的DDR2控制器IP核的FPGA實現,使用戶不需要了解DDR2的原理和操作方式的情況下,依然可以通過IP核控制DDR2。簡單介紹了DDR2的特點和操作原理,并

2017-11-22 07:20:50 5930

5930

DMA控制器是常見的總線設備之一,很多廠商都有自己的DMA控制器IP核。比如嵌入式處理器的龍頭ARM公司就有自己的DMA控制器解決方案提供給客戶,另外像Freescale,Fujitsu等芯片

2017-12-06 13:41:59 4363

4363

策略對UPFC性能的影響。首先基于UPFC的基本結構系統介紹了2種控制策略的控制思路,然后利用相對增益矩陣方法和阻尼轉矩分析方法分別比較了兩種控制策略下對UPFC交互影響的情況和其阻尼控制器向系統提供阻尼的情況。最后,通過4機2區域系統的計算,發現相角控制下UPFC交互影響更大

2018-01-31 10:15:37 3

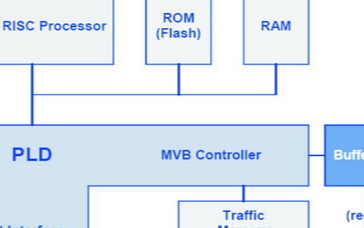

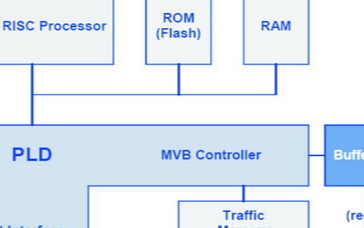

3 本設計正是基于SOPC的思想,開發實現自主知識產權的MVB收發控制器IP核,借助于QuartersII開發工具,集成至Altera FPGA器件內部,構建SOC片上系統實現MVB網卡基本功能,相比傳統國外的MVB網卡,大大簡化了系統的結構,降低了開發難度。

2020-04-18 08:08:00 4682

4682

隨著IC產業的發展,IP核的需求越來越高。微控制器MCU(Micro Control Unit)是嵌入式系統的核心,8位MCU IP核具有很高的通用性和靈活性,廣泛地應用于工業控制、機械設備、家用電器以及汽車等各個領域。本文設計的MCU IP核與Microchip公司的PIC16C57完全兼容。

2020-01-10 07:59:00 3247

3247

該控制器具有Avalon總線接口,可與其它標準IP 核一起構成以NiosⅡ為核心的片上系統,并可編寫驅動程序。 NIOSⅡ是Altera公司推出的第二代IP軟核處理器。它與其他IP核可構成SOPC系統的主要部分。

2018-09-29 08:35:00 7652

7652

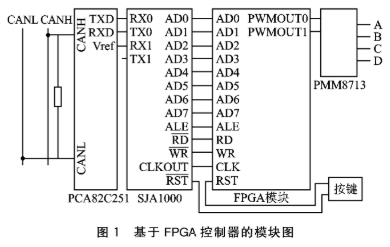

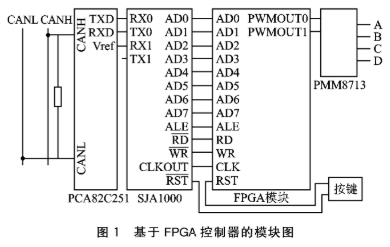

和Altera 公司部分FPGA 上的資源利用和性能情況。此外,基于SOPC技術將處理器軟核和CAN 控制器軟核集成在單片FPGA 中,構建了一種新型的CAN 總線系統,并在該系統中完成了對控制器軟核的測試驗證。

2019-07-19 17:48:41 27

27 學完SDRAM控制器后,可以感受到SDRAM的控制器的書寫是十分麻煩的,因此在xilinx一些FPGA芯片內已經集成了相應的IP核來控制這些SDRAM,所以熟悉此類IP核的調取和使用是非常必要的。下面我們以A7的DDR3 IP核作為例子進行IP核調取。

2019-11-10 10:28:45 5993

5993

統一潮流控制器(Unified Power Flow Con-troller,簡稱UPFC)是一種可以較大范圍地控制電流使之按指定路經流動的設備,它可在保證輸電線輸送容量接近熱穩定極限的同時又不

2020-03-19 10:00:47 2622

2622

由于CPLD數字設計結構化的趨勢,將出現針對CPLD不同層次的IP(Intellectual Property)核。各個IP核可重復利用,可大大提高設計能力和效率。國外各大公司都推出了專門的IP核,我國也迫切需要發展自己的IP核。本文針對I2C的主方式串行擴展通信的特點,詳細給出設計過程和結果。

2020-04-07 09:54:10 4073

4073

分析了CAN控制器SJA1000的特點及CAN協議通信格式。設計了控制器SJA1000的IP軟核,能為應用提供一個性能優良的、易于移植的控制器SJA1000,實現了對步進電機的控制。

2020-04-12 10:55:00 3579

3579

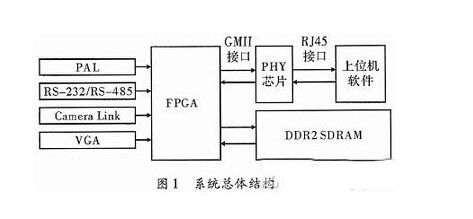

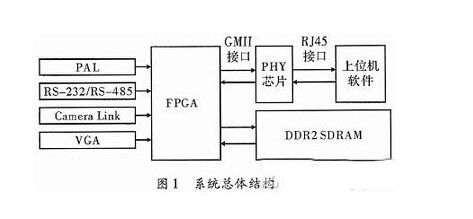

圖2顯示了系統FPGA模塊的具體結構,以及各個子模塊之間的關系。為縮短設計周期,提高設計質量,在模塊中分別調用了Altera公司現有的以太網控制器IP核和DDR2控制器IP核資源。

2020-10-07 10:58:00 2112

2112

2014.4 1、IP Catalog中搜索MIG,點擊相應IP進入如下配置界面。 (1)DDR控制器的個數,根據你的實際需求而定,需要幾個控制器,你心里應該清楚吧。 (2)MIG IP核的用戶側

2020-11-26 15:02:11 10426

10426

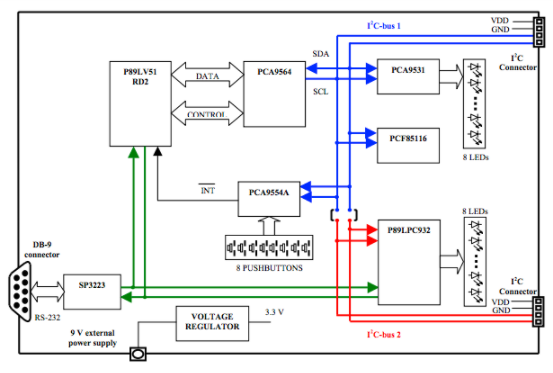

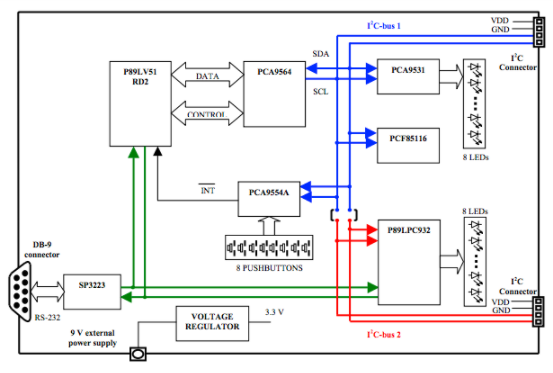

PCA9564 評估板展示了飛利浦 PCA9564 I2 C 總線控制器在主設備(連接到其并行總線及其控制信號)與任何連接到其 I2 C 總線的主設備和從設備之間進行接口的能力。評估板裝有以下器件

2021-06-17 17:26:46 4264

4264

本文的目的是使用基于智能控制器的 UPFC 設備提高電力系統的穩定性和可靠性。 UPFC 設備在各種故障條件下由模糊邏輯控制器控制。 模糊邏輯控制器將電壓、相角等電力系統參數與參考值進行比較,產生

2021-11-29 16:04:59 0

0 電子發燒友網站提供《TPS2359雙插槽ATCA AdvancdMC控制器,帶I2C評估模塊.pdf》資料免費下載

2024-12-20 15:48:07 0

0

![]()

電子發燒友App

電子發燒友App

評論