經歷了串行擾碼器的設計后,我們今天來認真討論一下擾碼器的并行化。

在許多工程項目中,在通信接口的設計中,通信協議對于擾碼器的工作頻率要求非常高,但是由于串行擾碼器是1bit進行的,如果再要求頻率過高的話,FPGA是無法實現如此高頻率的。所以我們要對其進行并行化處理,以此達到高速的要求。

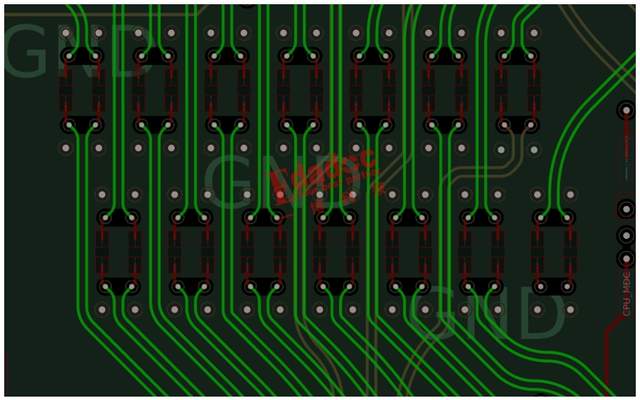

并行擾碼器設計基于串行擾碼器,其對應的本原多項式依然是,而其輸入輸出關系可以由上述擾碼器輸入輸出的邏輯關系推導而出。按規則規范,擾碼器與解擾器數據位的輸入輸出均為64位寬。

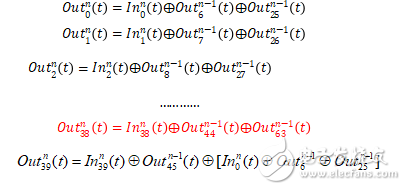

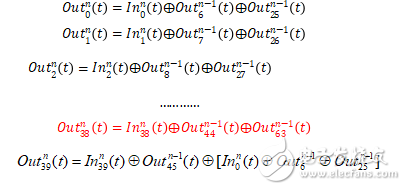

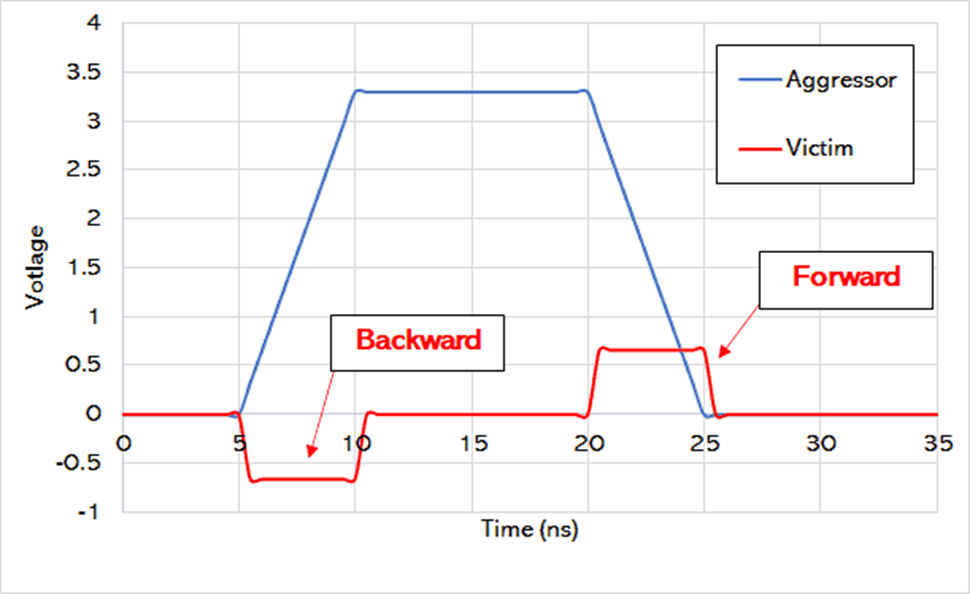

在上述的擾碼器中,將反饋移位寄存器中零時刻存儲值為為,擾碼器輸入與移位寄存器中數據與或的結果,即下一時刻輸入至第一個寄存器的數據為,輸入數據為scram_in。表示第S為寄存器在N時刻的存儲值。由擾碼器的輸入輸出關系可推導出在下一時鐘到來時,各級寄存器中存儲的數值滿足以下關系:

? ? ? ? ? ? ? ? ? ? ? ?(1)

以此類推,在第39個時鐘到來時,第39位寄存器寄存器中已經是,故將公式中迭代為該公式,即可進行下次運算。

?

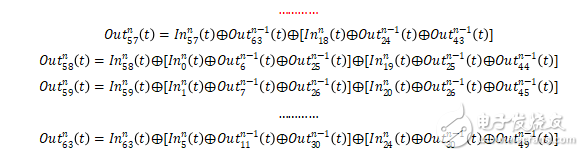

并行擾碼結構就是由上述擾碼多項式經過嚴格推演并進行處理,其結果推導為下式,推導出擾碼結果的每一位輸出都與當前輸入以及在此之前的輸出相關。由于后電路的要求,每一位一個擾碼輸出保持到下一次的擾碼操作,作為下一次擾碼的前一次輸出參與下一輪的擾碼操作,保持了擾碼的連續性。由于擾碼/解擾過程與本原多項式都有關,且擾碼過程中每一位的輸出都與其對應的寄存器數據位有關,故擾碼解碼實現時必須選擇相同的本原多項式和初始值。

?

電子發燒友App

電子發燒友App

評論