高速先生成員--黃剛

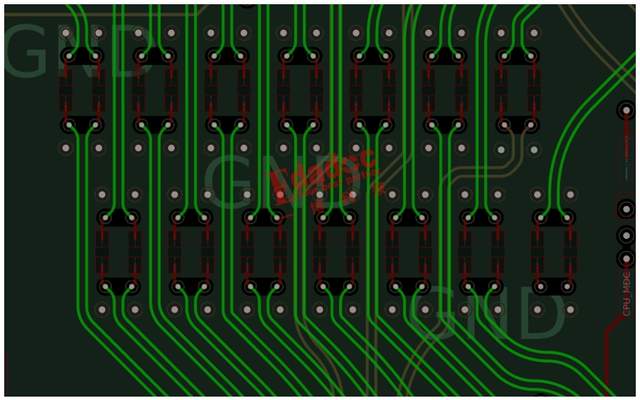

做過類似CPU服務器板PCB設計的朋友都知道,CPU與CPU之間會有很多很多對高速互連的走線,也就是很多圈內人稱為Interlaken的走線。你說這一大把互聯的高速信號對數多也就算了,關鍵是每一對都需要在外面串上交流(AC)耦合電容。當然,我們知道原理上來說是需要的(至于為什么,可以翻翻之前高速先生的文章哈,里面啥都有說!),但是實際操作起來都會讓設計工程師非常的討厭,需要有一片比較空的位置來把它們塞進去擺好,就像下面這樣哈。

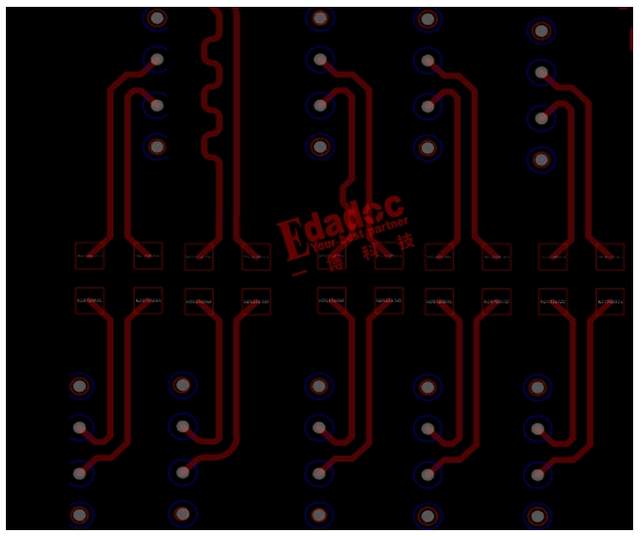

見多識廣的高速先生覺得上面的電容其實算擺的很寬松了,換言之就是設計工程師處理起來的難度已經不是很大了。再看看下圖?這個距離是不是慢慢的讓你們覺得恐懼了?

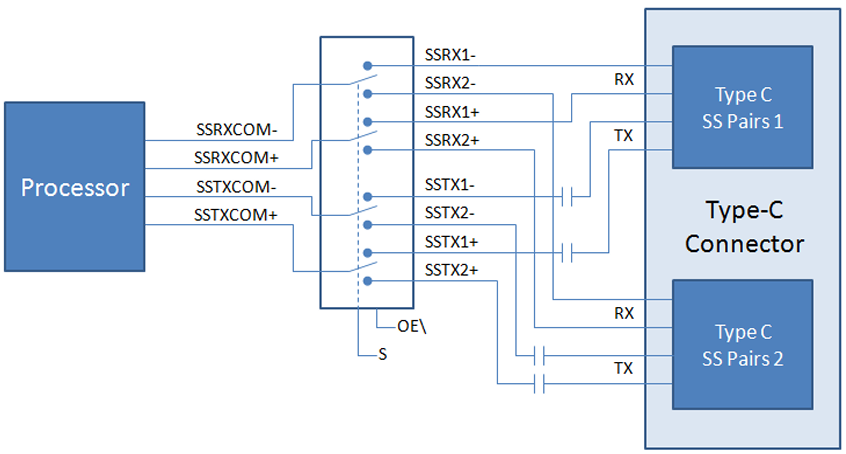

恐懼?恐懼啥呢,那當然是大家都會擔心對與對之間的串擾啊,在滿足物質生活之后(能塞到PCB板之后),肯定要慢慢開始注重精神生活了!鑒于有不少的粉絲,包括公司設計部的同事都來問過Chris這個問題:到底電容之間擺多近信號的串擾能夠被接受啊?Chris不忍心每次都跟他們說“這要看你高速信號跑得速率來定”這句萬能說辭,于是在項目忙到起飛的時候也偷個閑來建個模型驗證下,給大家第一手的量化數據哈!

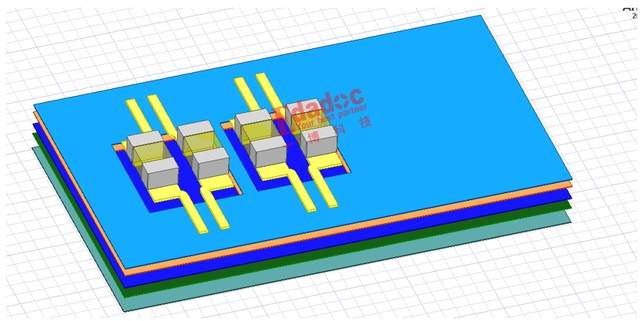

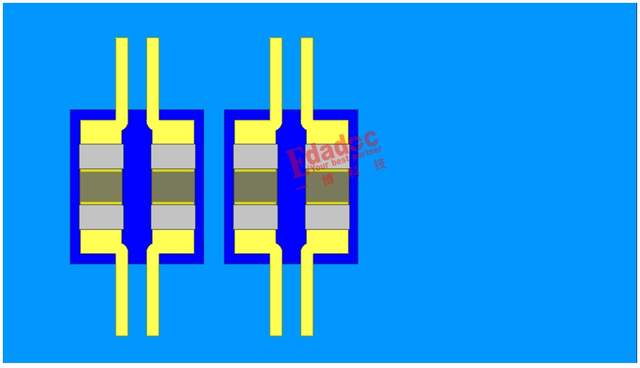

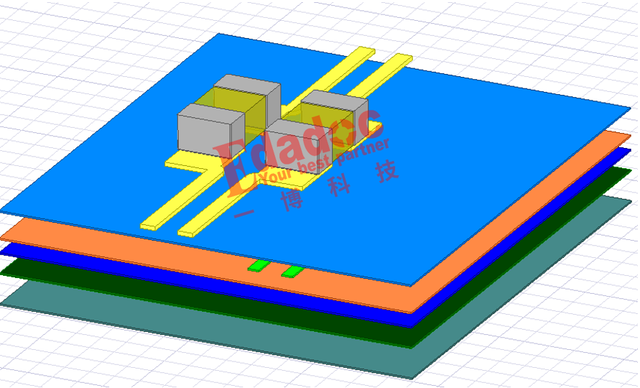

行吧,為了大家能有更直觀的認識,加就加吧。Chris用目前比較通用的0402電容來建模驗證。建立一個初始的3D模型就像下面這樣哈:

也就是兩對0402高速信號的AC耦合電容的模型,我們來研究不同距離下他們的串擾大小,這也就是為什么模型的右邊要留那么多空間的原因咯。因為我們可以改變這兩對電容之間的距離,來不斷的進行掃描,看看不同距離下的串擾結果哈!動態的效果就像下面這樣了,距離從遠到近的變化情況。

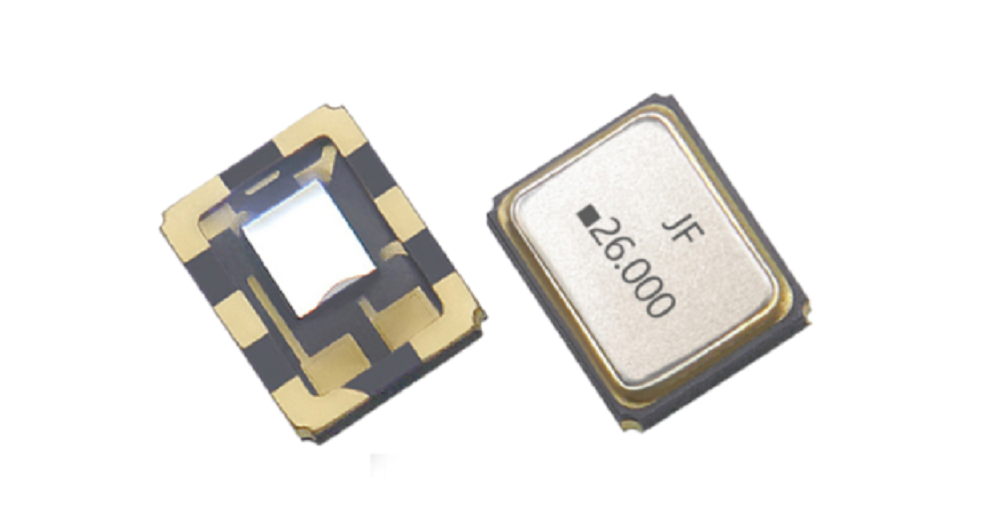

當然,一開始不可能完全挨在一起的嘛,能估計你也不敢吧,哈哈。所以我們最小從這個距離開始掃描,我們把這個距離當作0mil的初始值!估計這個距離應該是你們敢放的最近的距離了吧?這個時候的距離大概25mil,指的是焊盤到焊盤的gap大小。

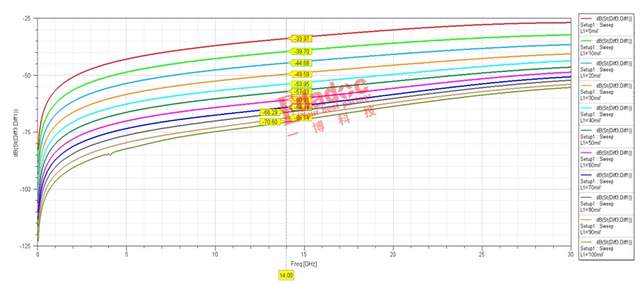

今天文章最重要的一張圖來了哈,那就是不同距離下的電容對間的串擾值,如下所示:

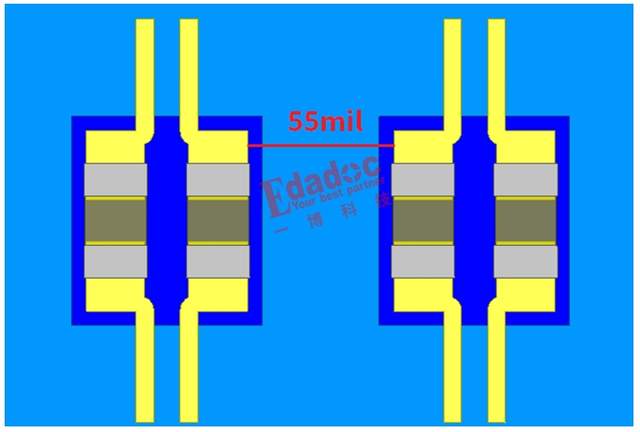

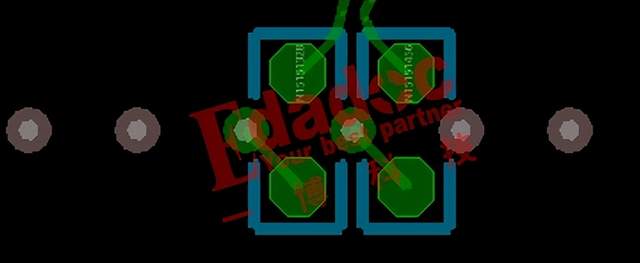

可以看到0mil就是代表這上圖的那個初始的距離,在我們大家做得比較多的28Gbps高速信號這個情況下,基頻在14GHz串擾大概33dB的樣子,當然拉開到100mil那么遠之后串擾直線下降到70dB這個非常非常理想的值了。當然Chris盲猜大多數的你們也真是沒有那么多空間能把兩對電容拉到100多mil的gap吧。那到底拉大到多少才合適呢?這個就看大家對裕量的安全感認知了,當然也看不同高速信號的裕量了。在28Gbps的高速信號中,Chris認為50dB是一個還不錯的門檻。對應到上面的仿真結果,也就是橙色的那一條曲線,大概30mil,加上初始的25mil,也就是55mil的焊盤gap。也就是大概下面這個距離哈,大家可以通過模型上的距離來體會下!

無論如何到最后都需要來個總結是吧?當然單單一個模型肯定沒法覆蓋到所有的疊層,所有的板材類型的case,但是參考意義Chris認為還是比較夠的,高速信號一般也用高速板材,這個case也是按照高速板材來仿真,各位粉絲不嫌棄的話,Chris認為都可以大膽的拿去參考參考!當然如果真的有喜歡挑刺的,或者是想要很確定自己做的這個板電容串擾多大的粉絲的話,Chris不說,大家也知道怎么來幫Chris回答他們了吧?

問題:Chris說了那么多,也讓大家說說唄:大家設計的時候高速AC電容都是按照間距多遠來放的啊?

審核編輯 黃宇

-

pcb

+關注

關注

4411文章

23907瀏覽量

425138 -

AC

+關注

關注

1文章

596瀏覽量

86363 -

耦合電容

+關注

關注

2文章

157瀏覽量

20822

發布評論請先 登錄

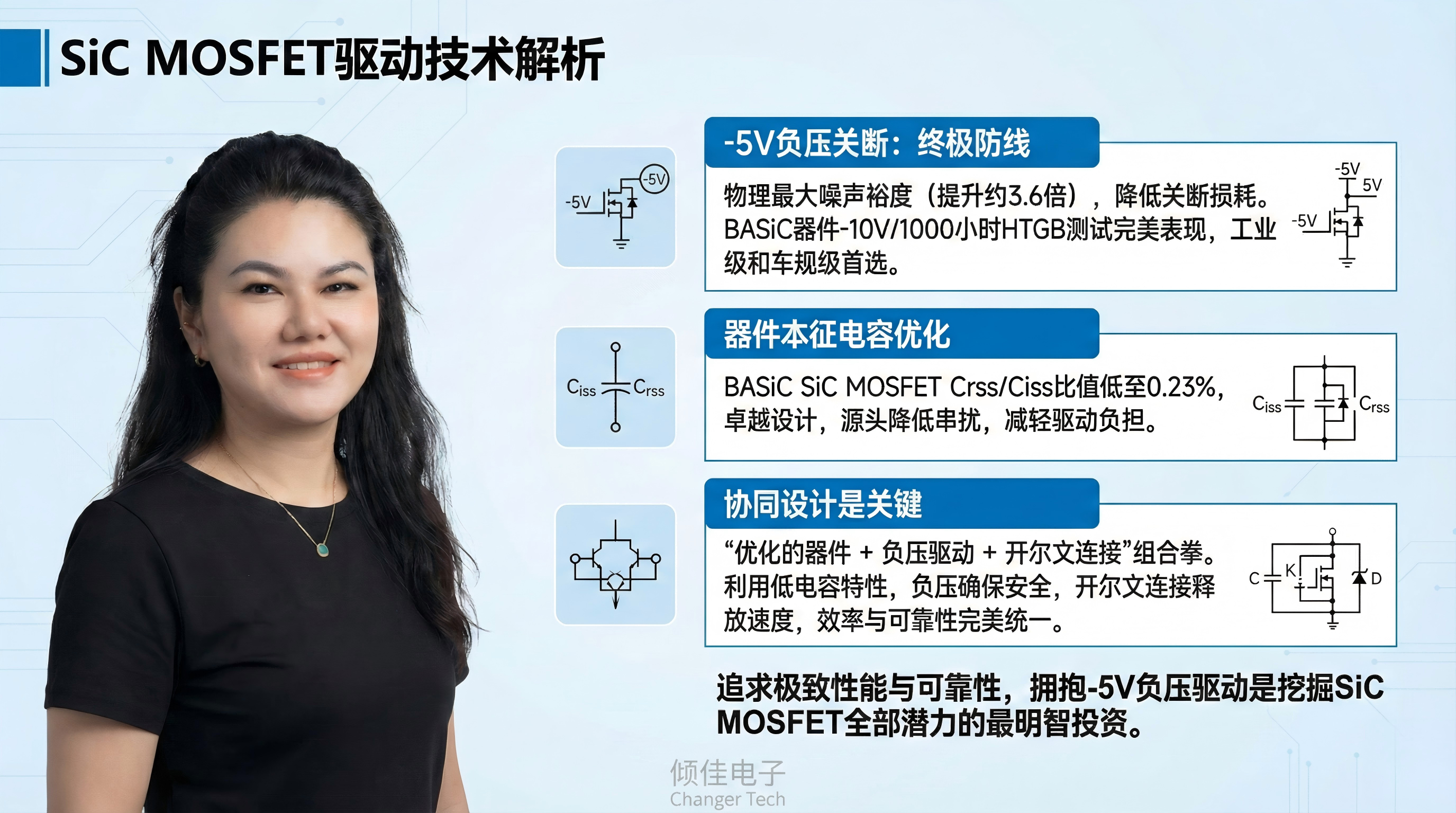

碳化硅MOSFET串擾抑制策略深度解析:負壓關斷與寄生電容分壓的根本性優勢

相同PCB單板,相同信號的AC電容,為啥反焊盤不同?

EXCUSE ME,表層的AC耦合電容和PCB內層的高速線會有串擾?

EXCUSE ME,表層的AC耦合電容和PCB內層的高速線會有串擾?

隔離地過孔要放哪里,才能最有效減少高速信號過孔串擾?

芯詳EMS4100: USB 3.1高速模擬開關芯片,替代ASW3410方案

高速AC耦合電容挨得很近,PCB串擾會不會很大……

NEXT(Near-End Crosstalk,近端串擾)

高頻晶振的信號完整性挑戰:如何抑制EMI與串擾

高速AC耦合電容挨得很近,PCB串擾會不會很大……

高速AC耦合電容挨得很近,PCB串擾會不會很大……

評論