本文深入探討PCB布局布線的專業設計要點與常見挑戰,并介紹上海創馨科技如何憑借資深團隊與豐富經驗,為客戶提供從精密布局、優化布線到生產制造的一站式高可靠性PCB解決方案。

2026-01-04 15:29:21 79

79 高速差分線驅動與接收器:SN75LVDS系列深度剖析 在高速數據傳輸的領域里,差分信號技術憑借其抗干擾能力強、傳輸速率高的優點,成為了眾多電子工程師的首選。今天,我們就來深入了解一下德州儀器(TI

2026-01-04 09:15:02 198

198 高性能產品:SN65LVDM050-Q1和SN65LVDM051-Q1。這兩款器件專為滿足高速、低電壓差分信號傳輸需求而設計,廣泛應用于汽車等對可靠性要求極高的領域。 文件下載

2025-12-30 15:05:06 110

110 SN65LVDS20和SN65LVP20:高速差分信號處理的理想之選 在高速數據傳輸和信號處理領域,選擇合適的芯片對于系統性能至關重要。今天,我們來詳細探討一下德州儀器(TI)的SN65LVDS20

2025-12-29 16:40:03 151

151 SN65LVDS20與SN65LVP20:高速差分收發神器揭秘 在高速信號處理的領域中,差分信號的處理與傳輸一直是工程師們關注的焦點。德州儀器(TI)推出的SN65LVDS20和SN65LVP20這

2025-12-29 16:00:33 131

131 TDK TCM0403T薄膜共模濾波器:高速差分信號的EMC解決方案 在當今的電子設備中,高速差分信號的應用越來越廣泛,如USB、HDMI等接口。然而,這些高速信號容易受到電磁干擾(EMI

2025-12-26 11:00:02 173

173 ANSI TIA/EIA - 644標準的低電壓差分信號(LVDS)要求。在典型的100 - Ω負載下,輸出電壓為350 mV,這種低電壓差分信號

2025-12-24 09:15:09 287

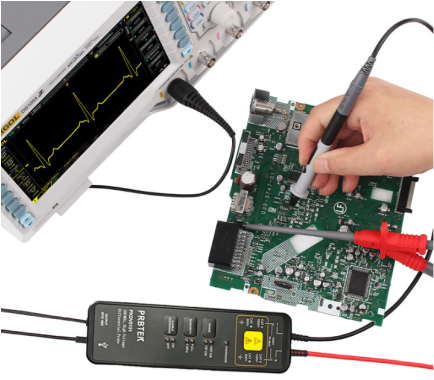

287 在電力電子、電機驅動、開關電源及工業控制系統的調試與分析中,工程師經常需要測量疊加在高直流母線電壓或劇烈共模噪聲之上的小幅度差分信號。 安捷倫(Agilent,現為是德科技Keysight

2025-12-22 10:38:57 125

125

針對新手的灌封膠完整入門指南,從類型選擇、配比攪拌、真空脫泡到灌封固化全流程詳解,幫助你避開常見操作誤區,輕松掌握電子元器件防護技巧。 | 鉻銳特官網

2025-12-17 00:31:02 285

285

TMUXHS4512:高速差分信號處理的理想之選 在當今高速數據傳輸的時代,對于高速、可靠的多路復用器和多路信號分離器的需求日益增長。德州儀器(TI)的TMUXHS4512 1.8V 6通道

2025-12-15 16:15:02 636

636 TMUXHS4612:高速差分信號處理的理想之選 在高速差分接口領域,德州儀器(TI)推出的TMUXHS4612 3.3V 6通道20Gbps差分2:1多路復用器/1:2多路信號分離器備受關注。今天

2025-12-15 16:10:06 465

465 頻段信號分配與合成軍用航空:COTS設備中的差分信號路由,滿足抗輻射、耐溫等嚴苛要求本地振蕩器分配:直接處理差分信號,簡化系統設計,減少組件數量生產友好性封裝形式:支持 磁帶與卷軸(Tape &

2025-12-05 09:19:54

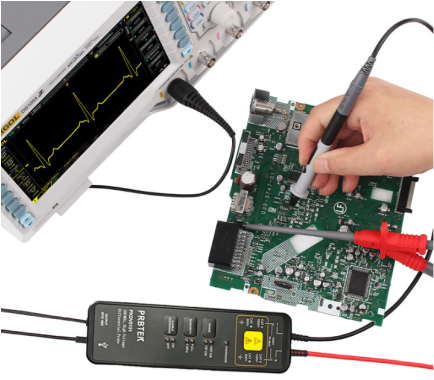

差分探頭是一種專門用于測量差分信號的測試工具,其原理是通過兩個對稱的輸入通道同時采集信號的正負端,并通過內部電路計算兩信號的差值,從而消除共模噪聲干擾,實現高精度測量。 1.1 工作機制 雙端輸入

2025-11-28 16:27:32 580

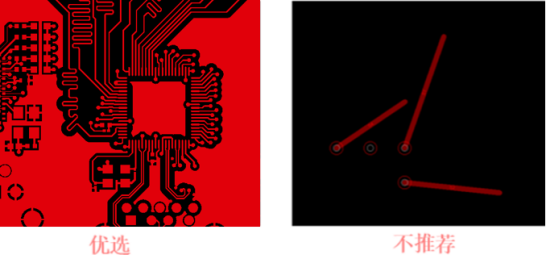

580 一站式PCBA加工廠家今天為大家講講高頻PCB布線設計有什么技巧?高頻PCB設計布線技巧。高頻PCB布線需重點關注信號完整性、抗干擾能力及阻抗匹配,以下是關鍵技巧的詳細說明: ? 高頻PCB設計布線

2025-11-21 09:23:02 278

278

,還可作為收音機天線的電感線圈等等。如2.4G的對講機中就用作電感。

對一些信號布線長度要求必須嚴格等長,高速數字PCB板的等線長是為了使各信號的延遲差保持在一個范圍內,保證系統在同一周期內讀取的數據

2025-11-14 06:11:56

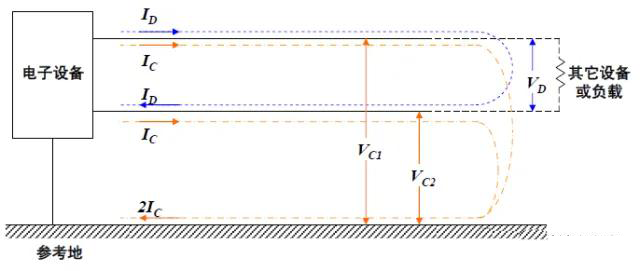

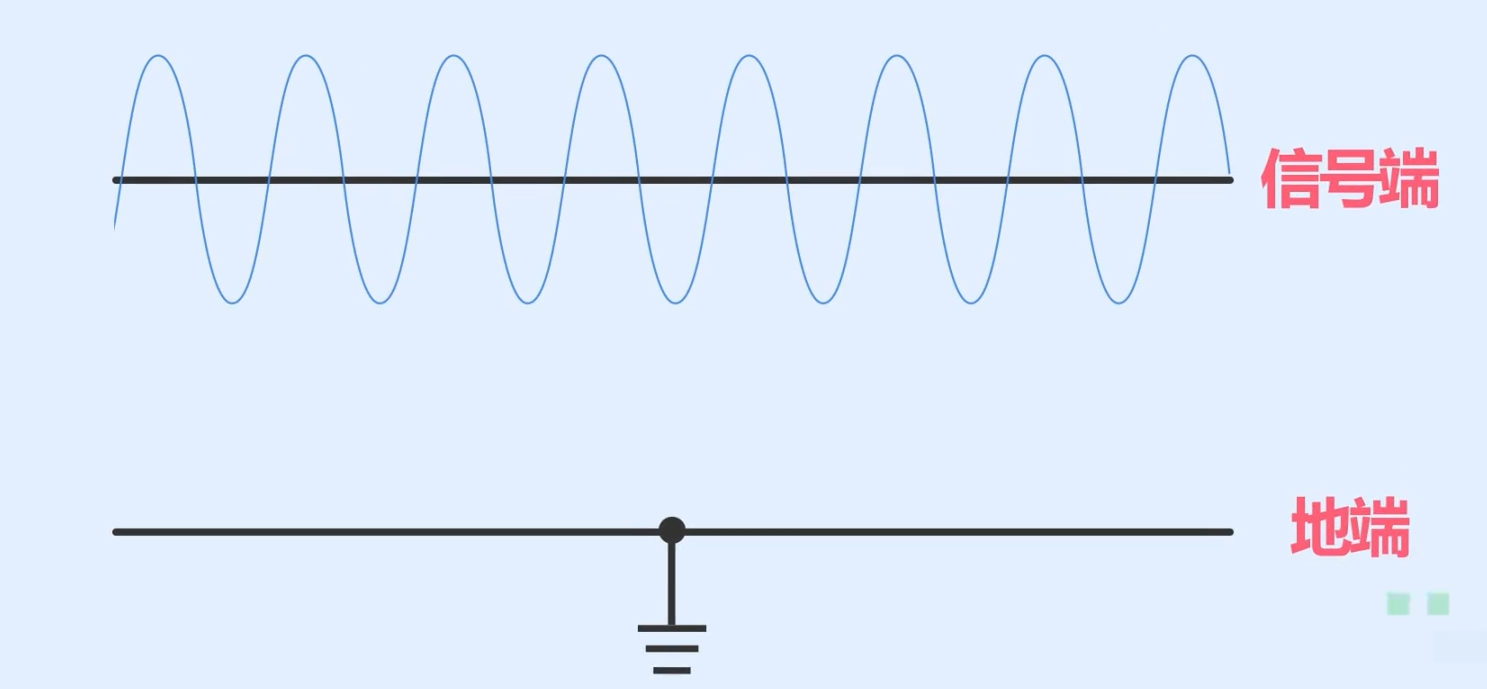

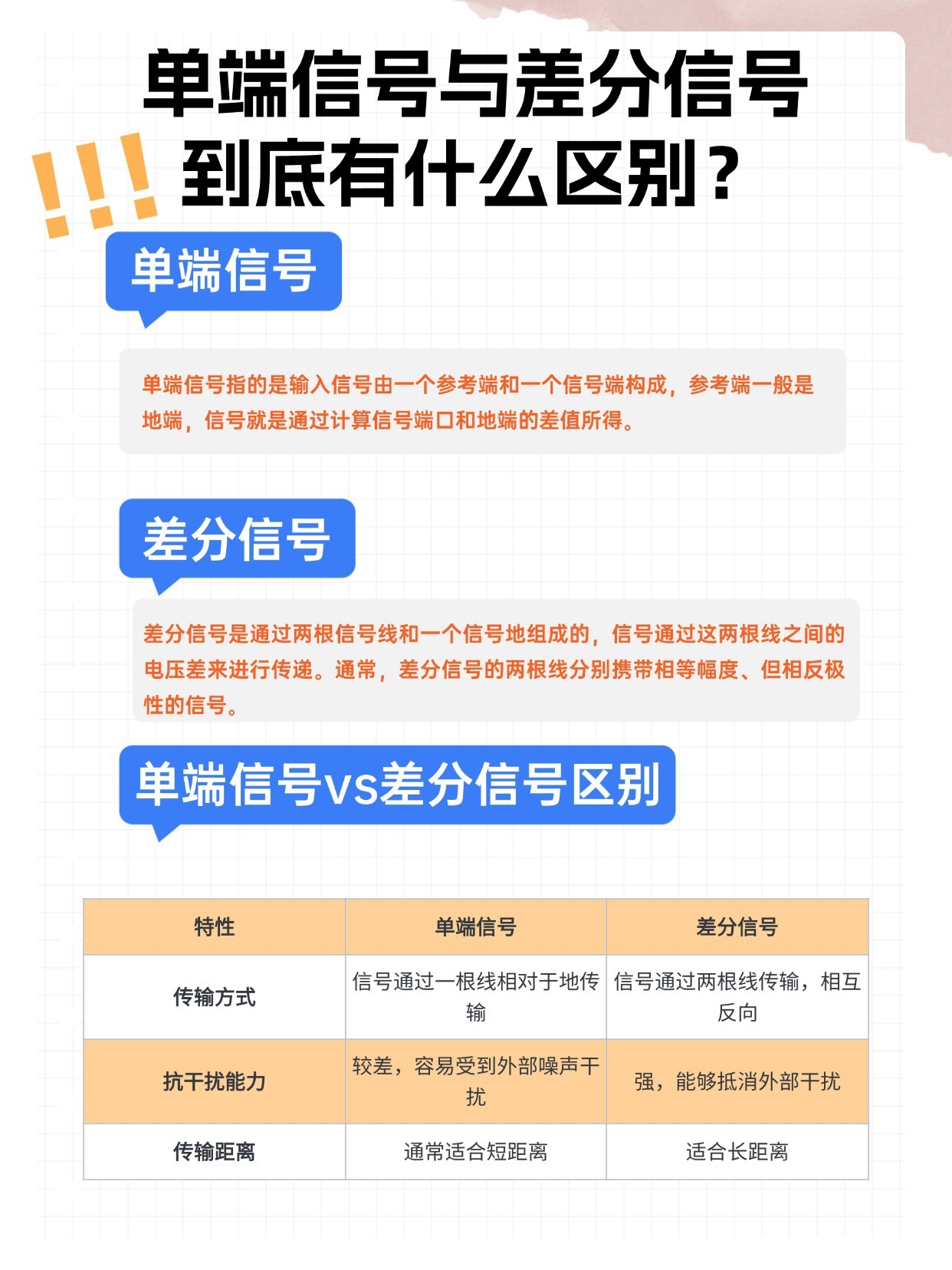

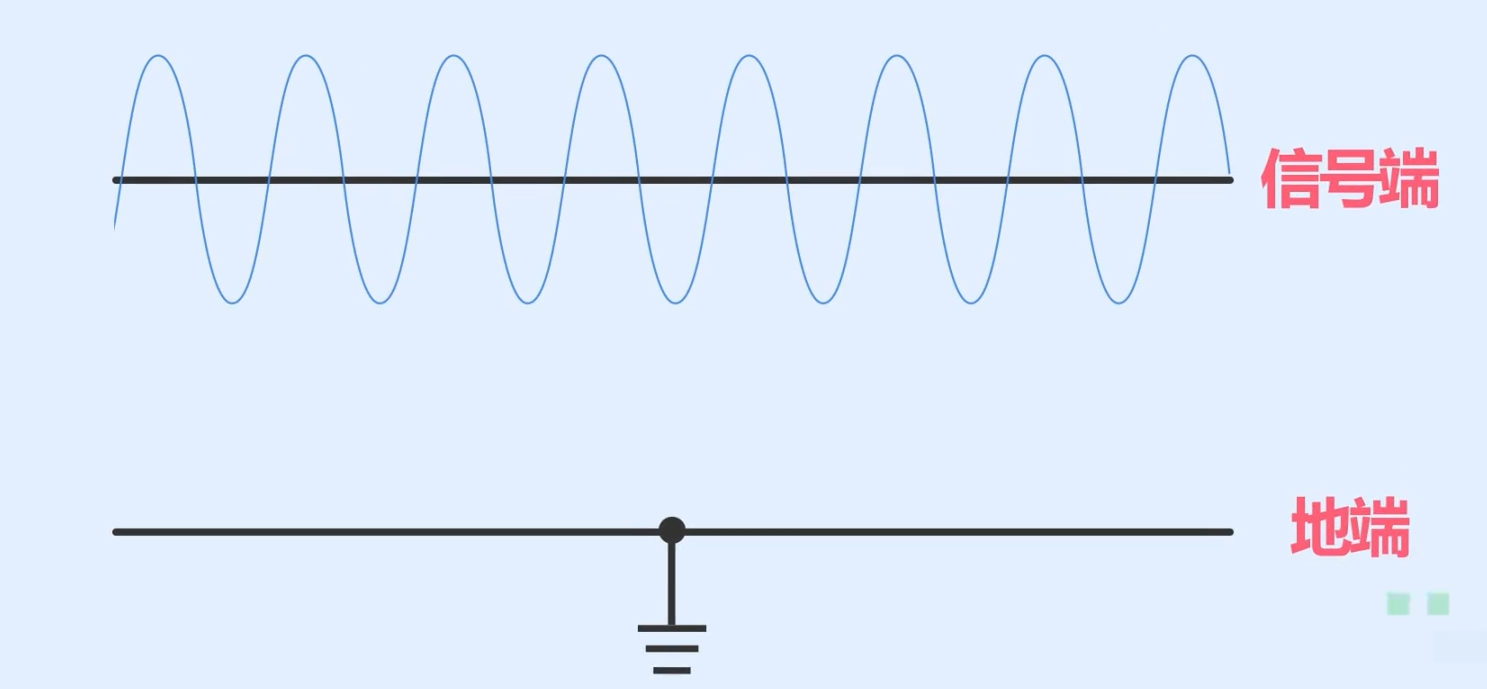

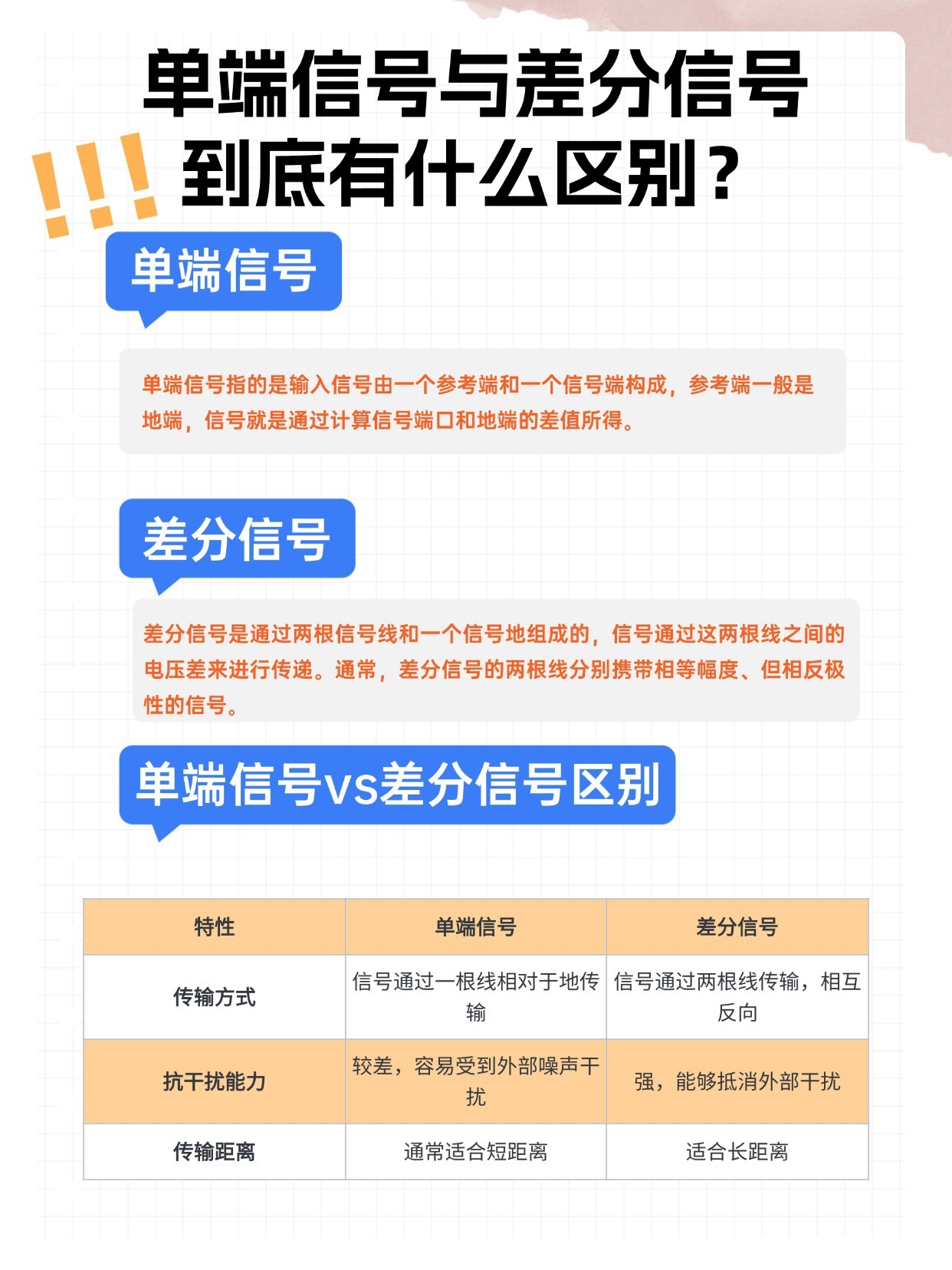

差分信號到底是什么?通俗來講,就是驅動端發送兩個等值、反相的信號,接收端通過比較這兩個電壓的差值來判斷邏輯狀態“0”還是“1”。

差分信號的產生是由輸入源發出信號后經過緩沖器和倒相器后,所產生

2025-11-12 06:44:57

對應固定阻抗值:射頻電路常用 50Ω,視頻信號多為 75Ω,高速差分信號如 DDR4 則需 90Ω。設計前需根據芯片手冊或行業規范確定目標值,這是后續操作的基礎。比如設計藍牙模塊時,若未按 50Ω 標準設計天線線路,會導致信號傳輸效率下降

2025-11-06 15:16:02 227

227 在電子測量領域,示波器差分探頭憑借其出色的抗干擾能力以及精準捕捉差分信號的優勢,被廣泛應用于電源設計、高速電路測試等場景。然而,在實際操作過程中,許多工程師卻常常遇到“測量的信號幅值持續跳變”這一

2025-10-30 09:23:46 344

344

分析負載特性時,很多人會因 “想當然套用經驗”“忽略實際場景細節” 或 “混淆概念” 導致判斷偏差,進而讓報警閾值調整失效(如誤報、漏報)。以下是 6 個最常見的錯誤 / 誤區,附錯誤表現、危害

2025-10-10 17:03:34 633

633 (工作<2mW,關斷<20uW)。通過SEL引腳切換A/B端口,_EN引腳控制開關使能。采用QFN4x4-32L封裝,適用于USB Type-C設備、PC、服務器及視頻信號切換等場景。PCB設計需注意AC耦合電容布局、高速信號等長布線和電源去耦等關鍵要點,確保信號完整性。

2025-09-30 15:36:04 671

671 “ ?本文介紹了在 PCB 上正確布局 USB 差分數據線的關鍵原則和實踐。主要目標是實現 USB 規范中規定的 90 歐姆阻抗匹配。且應考慮 ESD 保護及完整的地平面。 ” USB 速度等級

2025-09-18 12:03:26 5980

5980

M12 電纜接頭的差分信號針腳配置,不是 “死板的圖紙定義”,而是 “貼合場景的傳輸解決方案”。從 D 編碼的以太網適配,到 X 編碼的高速傳輸,每一組引腳的配置,都是為了讓數據在工業現場的復雜環境

2025-09-18 10:10:00 2028

2028

高壓差分探頭專為高共模電壓環境設計,實現安全、精準測量微小差分信號,具備高輸入阻抗、寬頻帶和強共模抑制能力。

2025-09-09 16:46:19 769

769 深圳南柯電子|步進電機EMC整改:不過關?常見誤區你可能正在犯

2025-09-08 09:58:26 500

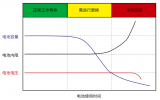

500 和其他工業與電氣設備一樣,蓄電池也需要定期的維護。但不少工程師對于蓄電池維護項目和方法等還存在一些誤解。今天小福為大家深度剖析蓄電池運維的常見4大維護誤區,助你避開雷區,精準預判電池壽命!

2025-09-04 13:58:29 860

860

在工業控制、數據采集與通訊系統等場景中,差分信號因具備抗共模干擾、低傳輸損耗的優勢,成為高精度信號傳輸的首選形式。芯佰微電子(Corebai)推出的CBMG709低壓CMOS差分4:1多路復用

2025-08-27 14:42:01 2768

2768

因汽車智能化發展,ADAS 技術依賴海量視頻數據采集,歐盟GDPR作為全球嚴規,對企業處理歐盟公民數據要求嚴格且違規罰款重!本文對行業常見的 5 個 GDPR 誤區進行逐一拆解,助力企業規避數據違規風險!

2025-08-27 13:36:19 509

509

在電力電子、新能源、工業控制等高壓應用領域,精準測量差分信號是保障設備性能與安全的關鍵環節。高壓差分探頭作為專門針對高壓差分信號測量的精密儀器,能夠在強干擾環境下準確捕獲高壓電路中的微小信號變化,為

2025-08-22 11:58:15 582

582 將差分信號轉換為單端信號的核心目標是提取差分信號中的共模抑制特性,同時保留所需的差模成分,最終輸出一個相對于參考地(如電路板地)的單一電壓信號。這一過程通常需要以下元件或電路模塊的組合:1.

2025-08-14 09:10:18

差分探頭是一種專門用于測量差分信號的儀器,其核心特點是通過抑制共模信號、放大差模信號,來精準捕捉兩個信號之間的電位差。它能測量的信號類型廣泛,涵蓋多個領域,具體如下: 一、差分信號(核心測量對象

2025-08-05 13:02:09 733

733 絕對值編碼器作為精準定位與運動控制的核心部件,其選型直接影響設備的精度、穩定性和壽命。但在實際選型中,由于對技術參數、應用場景和產品特性的理解偏差,很容易陷入誤區。本文針對絕對值編碼器選型的常見誤區之一:混淆“分辨率”與“精度”,盲目追求高分辨率,并提供對應的避坑思路,幫助精準選型。

2025-08-04 11:24:30 928

928

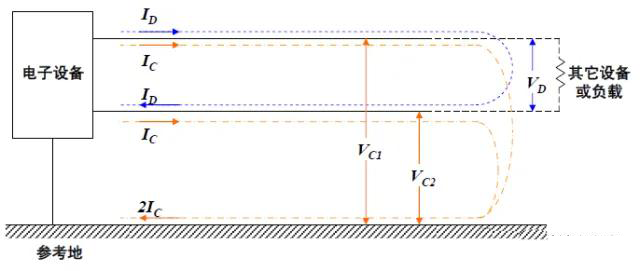

在電氣系統中,信號與干擾的傳輸形態直接影響設備性能。本文將系統解析共模信號與差模信號的特性、干擾產生機制及抑制方法,為電路設計與抗干擾優化提供參考。 一、 共模信號與差模信號的基本定義 單相電

2025-07-28 15:07:15 2118

2118

很多工程師對差分探頭的理解不是很深刻,市場上差分探頭生產廠家也不少,性能指標各不相同,甚至相差甚遠,造成測出的波形也不盡相同,工程師無法看到正確波形。本文將主要講述什么是差分信號,差分信號的測量,高壓差分探頭的主要指標,優缺點和相關使用技巧,以及 高壓差分探

2025-06-26 09:00:12 655

655

優勢明顯,但EMC性能差,信號易受干擾,不適合復雜布線。

設計提示: 在空間允許的情況下,盡量增加地線面積,形成局域參考平面。

2、四層板:性價比之選

對于常見的MCU開發板、工業控制板等中等復雜度

2025-06-24 20:09:53

(Vd-Vs):11 V封裝信息:ESD(靜電放電):< 50 Volts,HBM 0Z規格:3 x 3 mm濕度靈敏度等級:MSL 1應用場景射頻和微波系統:適用于需要單端信號與差分信號

2025-06-19 09:21:24

本文介紹了輸出單端信號或差分信號的設備與采集設備之間應該怎樣接線。

2025-06-17 15:50:05 1763

1763

在現代電子系統中,數據傳輸速度的快速增長帶來了諸多挑戰。當信號頻率達到幾百兆赫茲甚至數千兆赫茲時,傳統的單端信號傳輸方式面臨著信號完整性惡化、電磁干擾增強、功耗增加等問題。差分信號傳輸技術通過

2025-06-13 12:01:28 765

765

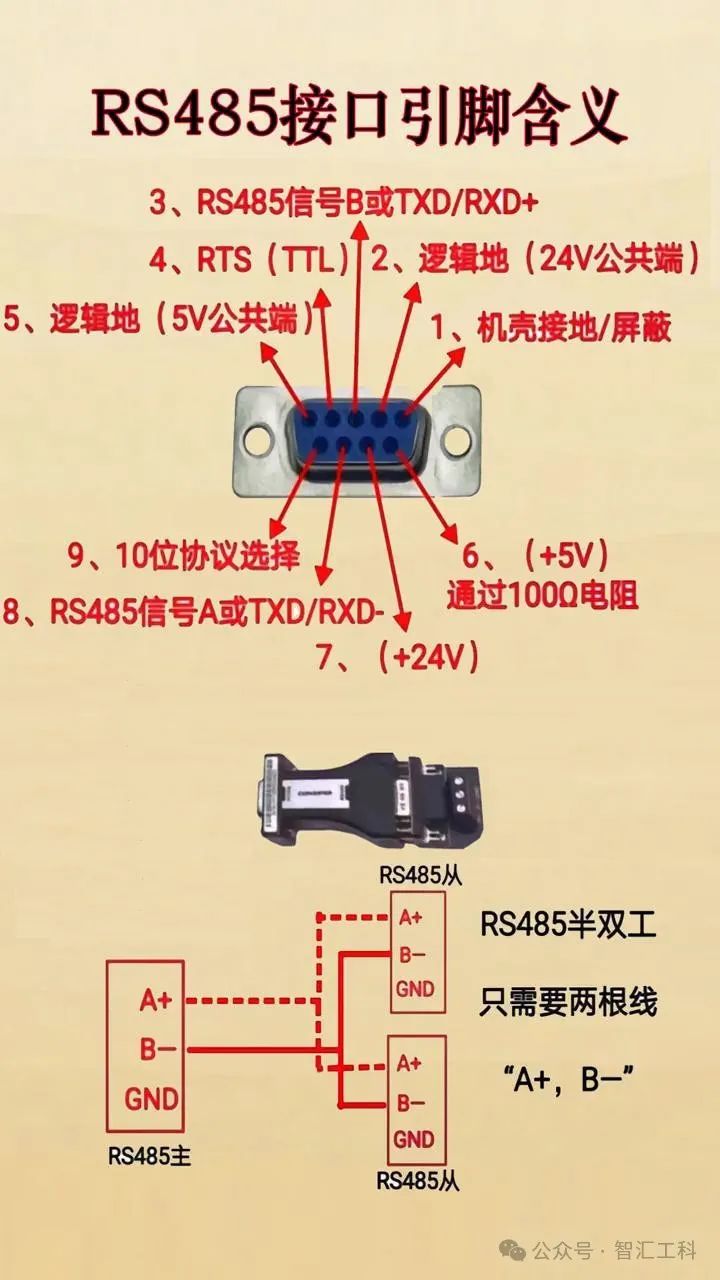

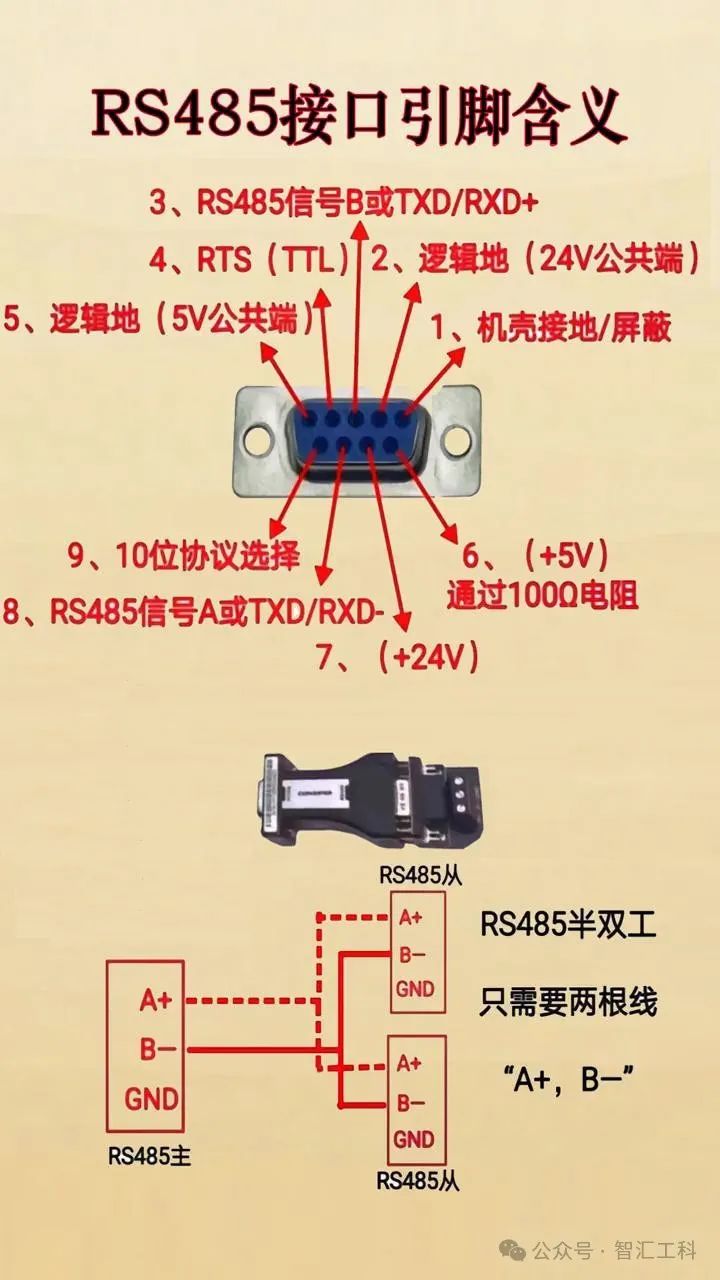

、電氣特性要求 1. 差分信號傳輸 RS-485采用平衡差分傳輸方式,要求驅動器輸出端A/B線間的差分電壓≥1.5V(空載時典型值±5V),接收器需能識別≥200mV的差分信號。這種設計可有效抑制共模干擾,允許最大±7V的共模電壓范圍。 2. 終端阻抗匹配 總線兩端必

2025-06-07 16:33:56 1640

1640

絡中,數據通過雙絞線上的差分信號傳輸。信號質量直接影響節點正確解讀數據的能力。信號質量差可能表現為:

位錯誤 :由于噪聲或信號失真導致的位誤判。 幀錯誤 :CAN幀結構錯誤,導致接收節點拒絕。 總線

2025-06-07 08:46:40

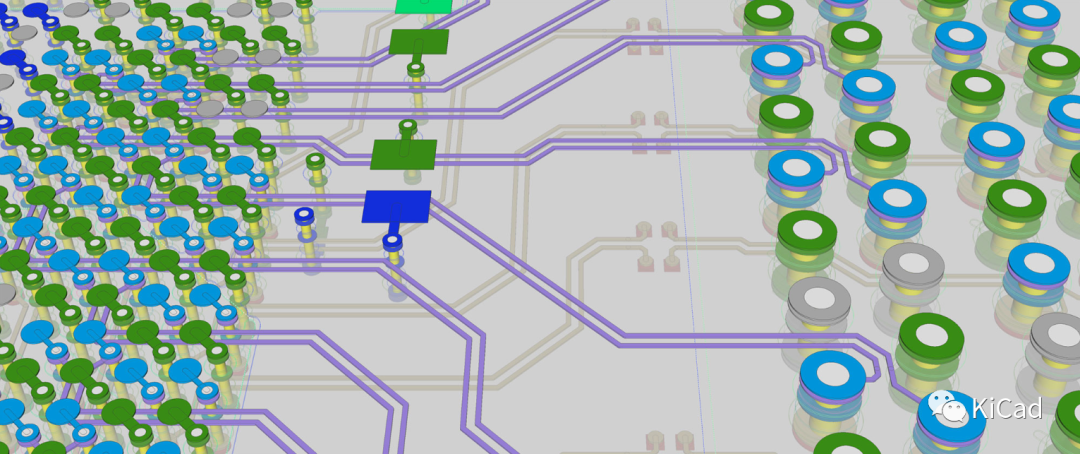

在PCB(PrintedCircuitBoard,印刷電路板)制造過程中,鉆孔是一項極為關鍵的工序。隨著電子產品不斷向小型化、高性能化發展,對PCB鉆孔的精度、效率以及孔壁質量等方面提出了更高要求

2025-06-04 10:00:11 1130

1130

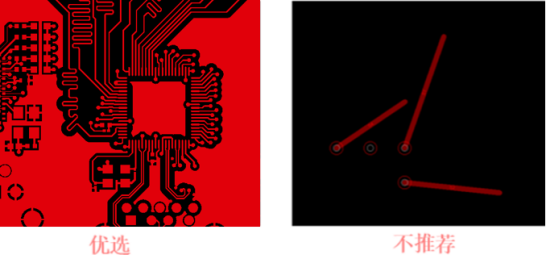

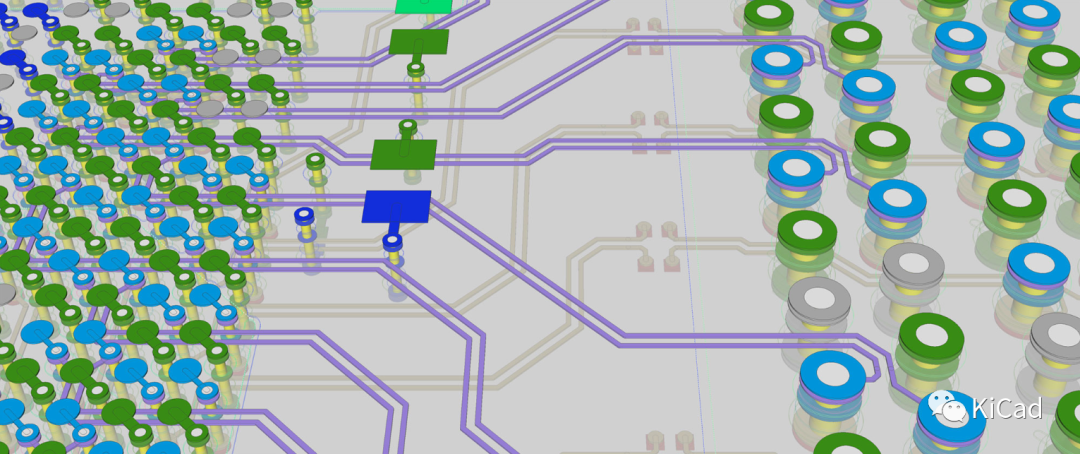

第一篇 PCB布線

在PCB設計中,布線是完成產品設計的重要步驟,可以說前面的準備工作都是為它而做的, 在整個PCB中,以布

線的設計過程限定最高,技巧最細、工作量最大。PCB布線有單面布線、 雙面

2025-05-29 14:38:35

目錄:一、布線的一般原則1、PCB板知識2、5-5原則3、20H原則4、3W/4W/10W原則(W:Width)5、重疊電源與地線層規則6、1/4波長規則7、芯片引腳布線二、信號走線下方添加公共接地

2025-05-28 19:34:36 2044

2044

在高速PCB設計中,差分過孔之間設置禁止布線區域具有重要意義。首先它能有效減少其他信號線對差分信號的串擾,保持差分對的信號完整性。其次禁止布線區域有助于維持差分對的對稱性,確保信號傳輸的平衡性。此外

2025-05-28 15:19:44 923

923

一個輸出端的時鐘信號線,如何實現差分布線?

要用差分布線一定是信號源和接收端也都是差分信號才有意義。所以對只有一個輸出端的時

鐘信號是無法使用差分布線的。

6、接收端差分線對之間可否加一匹配

2025-05-21 17:21:41

PCB 布線規則詳解 走線方向控制規則 相鄰布線層的走線方向應采用正交結構,避免不同信號線在相鄰層沿同一方向走線,以此降低不必要的層間串擾。若因 PCB 板結構限制(例如部分背板)難以避免該情況

2025-05-20 16:28:02 754

754 過孔包圍。

因此,經驗豐富的攻城獅一定會避免讓高速差分信號置于如下的境地:BGA區域差分信號管腳的四周分布多個電源管腳(圖中白色對應差分信號,綠色是GND網絡,黃色是電源PWR網絡),不多不少,一邊一

2025-05-19 14:28:35

確定PCB層數時需要綜合考慮幾個因素:電源和地平面的需求、信號密度、工作頻率、特殊信號布線需求以及成本限制。對于對EMC要求嚴格的產品(如需通過CISPR16CL

2025-05-17 16:17:26 1131

1131

高層數 PCB 的布線策略豐富多樣,具體取決于 PCB 的功能。這類電路板可能涉及多種不同類型的信號,從低速數字接口到具有不同信號完整性要求的多個高速數字接口。從布線規劃和為各接口分配信號層的角度來看,這無疑是一項極具挑戰性的任務。

2025-05-07 14:50:39 1366

1366

隨著集成電路工藝和集成度的不斷提高,集成電路的工作電壓越來越低,速度越來越快。進入新的時代后,這對于PCB板的設計提出了更高的要求。本文正是基于這種背景下,對高速PCB設計中最重要的環節之一一電源

2025-04-29 17:31:04

核心要點受控阻抗布線通過匹配走線阻抗來防止信號失真,從而保持信號完整性。高速PCB設計中,元件與走線的阻抗匹配至關重要。PCB材料的選擇(如低損耗層壓板)對減少信號衰減起關鍵作用。受控阻抗布線

2025-04-25 20:16:07 1101

1101

,導致產品延期和開發成本增加。

本文將提供有關印刷電路板(PCB)布局布線的指南,以幫助設計師避免此類噪聲問題。作為例子的開關調節器布局采用雙通道同步開關控制器 ADP1850,第一步是確定調節器的電流

2025-04-22 09:46:39

1、建議收藏,這31條PCB設計布線技巧相信大家在做PCB設計時,都會發現布線這個環節必不可少,而且布線的合理性,也決定了PCB的美觀度和其生產成本的高低,同時還能體現出電路性能和散熱性能的好壞

2025-04-22 08:05:34 512

512

相信大家在做PCB設計時,都會發現布線這個環節必不可少,而且布線的合理性,也決定了PCB的美觀度和其生產成本的高低,同時還能體現出電路性能和散熱性能的好壞,以及是否可以讓器件的性能達到最優等。本篇

2025-04-19 10:46:54

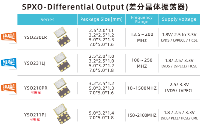

差分晶振通過差分信號輸出,在抗干擾、信號完整性、EMI抑制等方面有顯著優勢,能夠提供更穩定、更高速性能的時鐘信號。

因此差分晶振通常用于高速通信系統、光模塊、高速串行接口(如PCIe、USB 3.x)等場景。

2025-04-16 16:43:06 1017

1017

單端信號與差分信號的主要區別在于信號傳輸方式、抗干擾能力、適用場景等方面。

?單端信號?:適用于短距離、低速、低成本的傳輸場景,如音頻、視頻信號傳輸?。

?差分信號?:適用于長距離、高速、高精度的傳輸場景,如高速數據總線、長距離通信等,特別是在電磁環境復雜的場合表現更佳?。

2025-04-15 16:23:55 1095

1095

純分享帖,需要者可點擊附件獲取完整資料~~~*附件:電機故障診斷常見誤區的剖析.pdf

(免責聲明:本文系網絡轉載,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請第一時間告知,刪除內容!)

2025-04-07 17:35:18

在高速PCB設計中,信號完整性、串擾、信號損耗等問題直接影響電路板的性能穩定性。隨著5G通信、服務器、高速計算、汽車電子等行業對高頻、高速信號傳輸的需求增加,如何優化PCB布線以降低**信號衰減

2025-03-21 17:33:46 781

781 有限,也就是說為了保證性能需要提供的折中措施很有限。

以下是AUDIO音頻接口的PCB布局布線要點:

1、耳機座子應該 按照結構放置 ,如果沒有結構要求,則應將其放置在板邊,以方便插拔。

2、在布局空間

2025-03-19 14:31:06

了。

我們先來簡單看下幾種不同高速差分過孔的基本結構吧,常見的差分過孔結構如下圖所示。

中間兩個紅色的孔為信號孔,兩邊黑色的為地孔,黑色橢圓形的圈為反焊盤,也就是圈內除了孔,所有層的銅皮都是被掏掉

2025-03-17 14:03:54

是至關重要的。下面將針對實際布線中可能遇到的一些情況,分析其合理性,并給出一些比較優化的走線策略。主要從直角走線,差分走線,蛇形線等三個方面來闡述。1. 直角走線直角走線一般是PCB布線中要求盡量避免的情況

2025-03-13 11:35:03

電路板布線設計數字設計電路布局要達到良好效果,仔細布線是完成電路板設計重要關鍵。數字與模擬布線作法有相似處,本文將?述這兩種布線方式比較,另外討論旁路電容、電源供應及接地布線、電壓誤差,以及因電路板

2025-03-12 13:36:26

布線 抗干擾

1 布局

所謂布局就是把電路圖中所有元器件都合理地安排在面積有限的PCB上。從信號的角度講,主要有數字信號電路 板、模擬信號電路板以及混合信號電路板3種。在設計混合信號電路板時,一定

2025-03-12 13:31:16

像圖中的OPAMP6的正相輸入端和反相輸入端,對差分信號的接入距離過遠

2025-03-10 06:55:16

有些小伙伴在pcb布線時,板子到手就是干,由于前期分析工作做的不足或者沒做,導致后期處理時舉步維艱。

比如電源線、雜線拉完了,卻漏掉一組重要的信號線,導致這組線沒辦法同組同層,甚至都沒有完整

2025-03-06 13:53:15

濾波器接地設計對電子設備EMC至關重要,需避免接地線過長、殼體搭接不良、輸入輸出線平行走線、接地線過細及忽視高頻特性等誤區,采用短接地線、良好搭接、分開布線、合適接地材料及優化布局等方法提高濾波器性能。

2025-02-26 17:23:24 721

721

高速數據傳輸需求。

2、低功耗

低電壓傳輸設計,減少功耗和熱量產生。

3、抗干擾能力強

差分信號傳輸有效減少共模干擾和噪聲影響。

4、體積小

節省PCB板空間,適應緊湊型設備設計。

5、高可靠性

高品質

2025-02-18 18:18:36

iW1710驅動設計方案與PCB布線注意事項

2025-02-17 14:19:26 0

0

您好,我用THS4508作為單端轉差分放大器給ADS5500提供差分信號,現在有個奇怪的現象,THS4508不接ADS5500的時候工作正常,但是一連上,差分輸出端只有一端有信號,另一端沒有,或者只有噪聲……不知道為什么?

2025-02-17 06:53:19

以下是一些避免直流負載箱常見操作誤區的方法:

選型與安裝

正確選型:根據實際需求,準確選擇直流負載箱的額定電壓、額定電流等參數,使其與被測設備相匹配,避免因參數不匹配導致過載或欠載現象。

合理安裝

2025-02-13 13:49:40

要的差分信號。而且設計指標提的有點高,要求采樣轉換精度達到0.02mV。

小弟特此向TI的ADC達人求助:如何設計高精度單端轉差分放大電路。請達人幫忙出出主意,小弟不甚感激

2025-02-13 07:04:23

LVDS(Low Voltage Differential Signaling)信號:這是一種低壓差分信號技術接口,常用于液晶顯示器等領域。LVDS利用非常低的電壓擺幅在兩條PCB走線或一對平衡電纜

2025-02-11 11:01:46 1253

1253

你好,我在使用ADS8556時,采集差分信號時效果極差,需要對同一組兩路信號都采集進AD后軟件做減法實現,這個問題該如何解決?而采集一個正常的單端信號則是正常的。我使用的單端轉差分電路

2025-02-11 07:46:50

磁致伸縮位移傳感器利用磁致伸縮效應測位移,結合SSI差分信號協議,實現高精度、抗干擾、長距離穩定傳輸,適用于工業自動化、精密測量,確保數據準確傳輸與控制。

2025-02-10 16:26:43 1389

1389

我用ads1147 輸出一路電流1000uA,對電橋進行激勵,電橋2根差分輸出信號分別接入AIN0和AIN1,但是發現沒有電流輸出怎么回事,請評價一下是否可用這種方案測量電橋輸出的差分信號

2025-02-05 08:46:37

用ADS1230采集3噸稱重傳感器的數據。

調試的時候用電阻和電位器搭了一個模擬傳感器輸出差分信號的電路,此時測量出來的差分電壓準確。不過都是在靜態下測的,也就是輸出的差分信號是一個固定電壓值

2025-02-05 07:45:54

采用數據手冊中典型電路進行設計,希望將16通道設計成6通道的差分和4通道的單端,外部信號調理采用opa2365,如上圖所示,可是

我設計中上圖中對單端信號而言,運放實現單端信號轉差分信號,也就

2025-02-05 07:36:17

接口的基本原理 差分信號傳輸 差分平衡電平接口的核心在于其差分信號傳輸方式。在這種傳輸方式下,信號不是通過單一的電壓線傳遞,而是通過一對電壓線(A和B)的相對電壓差來表示。這種設計巧妙地利用了兩根線上噪聲的相關性,即當噪聲

2025-02-04 16:34:00 1320

1320

我現在用的ADS8481是偽差分輸入的,我把 -IN接地,+IN用來輸入信號,信號是從前級的運放輸出的,請問這種偽差分的AD的 -IN端接地有什么要求,我看一些資料上說為了防止信號

2025-01-23 06:52:30

在現代工業自動化和精密機械領域,諧波減速器因其高效率、高精度和高扭矩密度等優點而受到青睞。然而,在選型過程中,由于缺乏專業知識或對產品特性的誤解,用戶往往會陷入一些常見的誤區。 一、忽視負載特性

2025-01-22 09:21:23 1385

1385 ,但在設計和使用過程中,工程師和技術人員可能會遇到一些誤區。 誤區一:低通濾波器可以完全去除高頻信號 誤區解析: 低通濾波器的設計目的是減少高頻信號的影響,但它們并不能100%地去除所有高頻成分。濾波器的性能受到其截止頻率、濾波器類型(如巴特

2025-01-21 10:02:12 1307

1307

請教一下,兩片ADS8568在PCB布線是應該注意什么,數字地和模擬地的組合方式,或者有多片ADC的布線文檔沒,急用,謝謝。

2025-01-21 08:25:51

現象一:這板子的PCB設計要求不高,就用細一點的線,自動布吧。 點評:自動布線必然要占用更大的PCB面積,同時產生比手動布線多好多倍的過孔,在批量很大的產品中,PCB廠家降價所考慮的因素除了商務因素

2025-01-20 10:44:47 658

658 = +1.8V, IOVDD = +3.3V,VREF=+2.5V,Low-Speed Mode

待采集信號為±5V差分信號,共模電壓為2.5V。

現在需要將±5V差分信號轉換為±2.5V差分信號輸入給

2025-01-20 07:23:25

?本文重點在混合信號PCBLayout上布線在混合信號設計中放置器件。電源分配網絡的混合信號PCB設計要求。以前,電子產品包含多個電路板,每塊電路板負責處理不同的功能。在這些舊系統中,可能包括處理器

2025-01-17 19:25:05 1911

1911

在ADS5407的外圍電路設計中,其差分信號輸入所需要的單端轉差分信號有專用芯片嗎,還是根據自己的要求選擇任意芯片都可以?我設計的原理圖中使用的是AD8138,這款芯片是否可以呢,因為在調試中發現其差分輸出后的信號不是特別好。還有就是其所需的時鐘是否需要專用芯片?

2025-01-17 08:08:32

ADS1118差分信號輸入電路如何搭建?希望得到大家的幫助。參考這樣一個電路可以嗎?

2025-01-17 08:04:51

在功率放大器的設計中,OTL電路因其簡單性和成本效益而受到青睞。然而,這種電路設計也存在一些常見的誤區,這些誤區可能會影響放大器的性能和可靠性。 一、對OTL電路原理的誤解 誤區1:OTL電路不需要

2025-01-16 09:39:41 856

856

關于布局布線DAC5675A器件,由于該器件是高速器件,在PCB方面需要向您請教:

1、差分輸入端差分線長、線距是否有特殊要求?

2、差分時鐘走線是否有特殊要求?

2025-01-14 06:41:20

從這個芯片的產品介紹上看是可以接受CML的差分信號的, 但具體的datasheet里面沒有提及CML的輸入。

想請TI的工程師確認下這個芯片是否可以接受CML。

2025-01-13 07:13:10

請問ADS5474在PCB布線時,數據輸出和時鐘輸出共16對差分線需不需要保持等長,如果要的話誤差可以控制在多少個mil?

2025-01-13 07:01:48

在電子產品設計中,PCB布局布線是重要的一步,PCB布局布線的好壞將直接影響電路的性能。 現在,雖然有很多軟件可以實現PCB自動布局布線。但是隨著信號頻率不斷提升,很多時候,工程師需要了解有關PCB

2025-01-07 09:21:48 1898

1898

如題,請教各位工程師,有將SDI單端輸入信號轉成差分信號輸出的芯片可以推薦嗎?感謝!

2025-01-07 07:46:45

ads1271差分輸入信號走線如何布線?

2025-01-06 07:45:55

電子發燒友App

電子發燒友App

評論