一站式PCBA加工廠家今天為大家講講高頻PCB布線設(shè)計(jì)有什么技巧?高頻PCB設(shè)計(jì)布線技巧。高頻PCB布線需重點(diǎn)關(guān)注信號(hào)完整性、抗干擾能力及阻抗匹配,以下是關(guān)鍵技巧的詳細(xì)說明:

高頻PCB設(shè)計(jì)布線技巧

一、核心布線原則

多層板設(shè)計(jì)

高頻電路集成度高,采用至少四層板(頂層、底層、電源層、地層),利用中間層設(shè)置屏蔽和就近接地,降低寄生電感,縮短信號(hào)傳輸路徑,減少交叉干擾。例如,四層板比雙面板噪聲低20dB。

電源層與地平面相鄰,利用平面電容濾波,增強(qiáng)去耦效果。

引線優(yōu)化

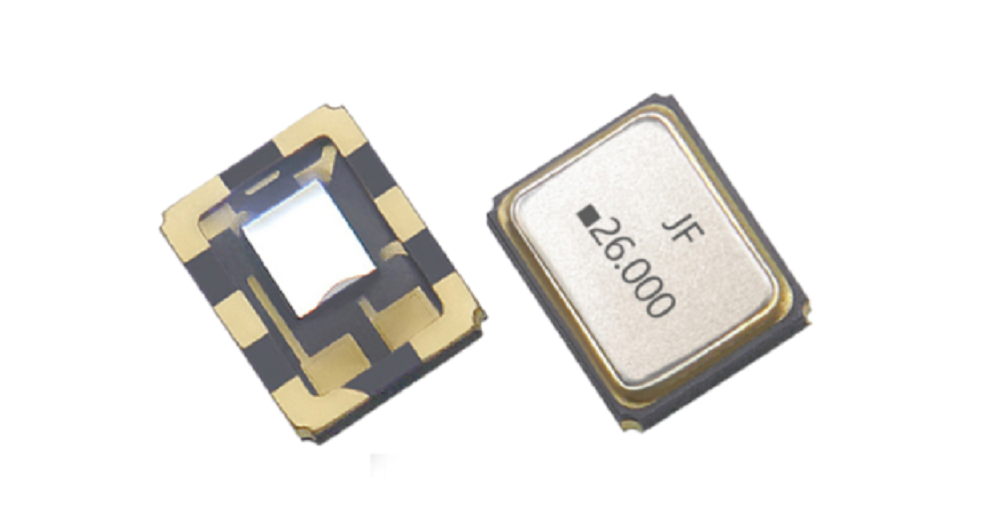

長(zhǎng)度控制:高頻信號(hào)引線(如時(shí)鐘、晶振、DDR數(shù)據(jù)、LVDS、USB、HDMI等)需盡可能短,以減少輻射和耦合。信號(hào)輻射強(qiáng)度與走線長(zhǎng)度成正比,長(zhǎng)引線易耦合到鄰近元件。

彎折處理:引線優(yōu)先采用全直線,轉(zhuǎn)折時(shí)使用45°折線或圓弧,避免直角或銳角轉(zhuǎn)折。低頻電路中彎折僅用于提高銅箔固著強(qiáng)度,而高頻電路中可減少信號(hào)發(fā)射和耦合。

層間交替減少:元件連接時(shí)過孔(Via)越少越好,每個(gè)過孔引入約0.5pF分布電容,減少過孔數(shù)可顯著提高速度。例如,高速信號(hào)線換層時(shí),應(yīng)在過孔附近放置接地過孔提供回流路徑。

串?dāng)_防范

平行走線控制:避免信號(hào)線近距離平行走線,若無法避免,可在平行信號(hào)線反面布置大面積“地”以減少干擾。同一層內(nèi)平行走線不可避免時(shí),相鄰層走線方向需垂直。

間距調(diào)整:增加信號(hào)線間距,減少平行長(zhǎng)度。例如,DDR總線需滿足“2W原則”(線間距≥2倍線寬),以降低串?dāng)_。

二、關(guān)鍵信號(hào)處理

差分對(duì)布線

高速差分信號(hào)(如LVDS、USB、HDMI)需嚴(yán)格等長(zhǎng)、等距、對(duì)稱布線,保持匹配阻抗(如100Ω±15%)。差分對(duì)內(nèi)部間距宜小,對(duì)外間距宜大,避免在差分對(duì)之間放置元件或過孔。

蛇形走線用于時(shí)序等長(zhǎng),但需增加寄生電容,間距應(yīng)≥2倍線寬。例如,DDR3信號(hào)線需通過蛇形走線補(bǔ)償長(zhǎng)度差異,確保信號(hào)同步。

阻抗匹配

信號(hào)傳輸過程中,若阻抗不匹配,會(huì)發(fā)生反射,導(dǎo)致信號(hào)過沖或下沖。需確保傳輸線特性阻抗與負(fù)載阻抗匹配,例如USB 3.0信號(hào)線需控制阻抗為90Ω±10%。

避免傳輸線突變或拐角,保持各點(diǎn)阻抗連續(xù)。例如,高速信號(hào)線拐角應(yīng)采用135°折線,減少信號(hào)反射。

信號(hào)完整性保護(hù)

包地處理:對(duì)重要信號(hào)線(如時(shí)鐘、復(fù)位)或局部單元(如晶振)實(shí)施地線包圍,繪制外輪廓線自動(dòng)生成“包地”,減少干擾。

避免環(huán)路:高頻信號(hào)走線避免形成環(huán)路,若無法避免,需使環(huán)路面積最小化,減少電磁輻射。

三、電源與地設(shè)計(jì)

去耦電容布局

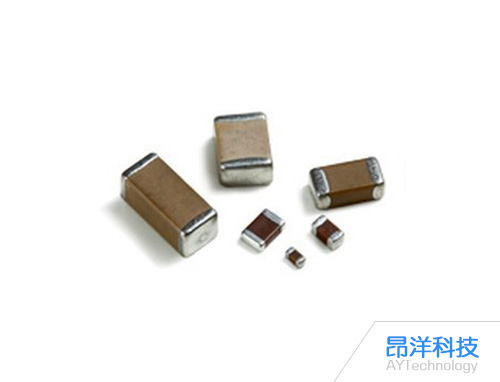

每個(gè)集成電路塊電源引腳旁增加高頻退耦電容(如0.1μF陶瓷電容),抑制電源諧波干擾。電容需靠近芯片電源引腳放置,容值搭配覆蓋不同頻段(如10μF+0.1μF)。

電源入口處加TVS管和保險(xiǎn)絲,進(jìn)行過壓/過流保護(hù)。

地線隔離與連接

模擬地與數(shù)字地隔離:模擬地線和數(shù)字地線通過高頻扼流磁珠或直接隔離,單點(diǎn)互聯(lián)于公共地線,防止數(shù)字信號(hào)干擾模擬信號(hào)。例如,ADC/DAC芯片下方布置模擬地-數(shù)字地單點(diǎn)連接。

接地策略:數(shù)字地與模擬地在芯片下方或入口處單點(diǎn)連接,混合信號(hào)芯片接地方式參考芯片手冊(cè)推薦方案。多層板中地平面盡量完整,避免形成“孤島”。

四、布局與工藝優(yōu)化

分區(qū)布局

模擬電路與數(shù)字電路分區(qū)布置,避免交叉。高速信號(hào)線盡量走在內(nèi)層,并保證參考平面完整。例如,DSP系統(tǒng)需將DSP芯片、時(shí)鐘電路、復(fù)位電路、片外存儲(chǔ)器等組成最小系統(tǒng),減少干擾。

高功耗器件(如電源芯片)遠(yuǎn)離電解電容、晶振等怕熱元件,并通過多過孔連接至底層地平面散熱。

工藝細(xì)節(jié)

過孔尺寸控制:高頻信號(hào)過孔宜采用小孔徑(如8-12mil),減少寄生電感。盲埋孔可提高布線密度,但成本較高,通常用于高端產(chǎn)品。

阻焊開窗處理:散熱焊盤需明確標(biāo)注阻焊開窗,避免綠油覆蓋,增強(qiáng)散熱效果。

關(guān)于高頻PCB布線設(shè)計(jì)有什么技巧?高頻PCB設(shè)計(jì)布線技巧的知識(shí)點(diǎn),想要了解更多的,可關(guān)注領(lǐng)卓PCBA,如有需要了解更多PCBA打樣、PCBA代工、PCBA加工的相關(guān)技術(shù)知識(shí),歡迎留言獲取!

審核編輯 黃宇

-

PCB布線

+關(guān)注

關(guān)注

22文章

473瀏覽量

43539

發(fā)布評(píng)論請(qǐng)先 登錄

三環(huán)電容ESL對(duì)高頻信號(hào)完整性影響?

技術(shù)資訊 I 信號(hào)完整性與阻抗匹配的關(guān)系

揭秘高頻PCB設(shè)計(jì):體積表面電阻率測(cè)試儀如何確保信號(hào)完整性

串?dāng)_如何影響信號(hào)完整性和EMI

PCB疊層設(shè)計(jì)避坑指南

PCB疊層設(shè)計(jì)避坑指南

了解信號(hào)完整性的基本原理

高頻晶振的信號(hào)完整性挑戰(zhàn):如何抑制EMI與串?dāng)_

信號(hào)完整性測(cè)試基礎(chǔ)知識(shí)

信號(hào)完整性視角下,SMA插頭PCB連接的原理剖析

技術(shù)資訊 | 信號(hào)完整性測(cè)試基礎(chǔ)知識(shí)

高頻PCB布線“避坑指南”:4大核心技巧讓信號(hào)完整性提升90%

高頻PCB布線“避坑指南”:4大核心技巧讓信號(hào)完整性提升90%

評(píng)論