最近調(diào)試芯片遇到一個(gè)選擇題,需要決定數(shù)據(jù)接口的接口標(biāo)準(zhǔn),是選用LVDS差分接口還是CMOS單端接口。說(shuō)實(shí)話,之前接觸多的還是CMOS單端接口,只是看到過(guò)很多資料介紹過(guò)LVDS差分接口。

官方說(shuō)法里,它的主要優(yōu)點(diǎn)有:

抗干擾能力強(qiáng),具有更高的數(shù)據(jù)傳輸速率

更好的信號(hào)完整性

降低了電平幅度和電路功耗

既然有這么多優(yōu)點(diǎn),這次我們就選用LVDS差分接口,看看我們能不能感受到LVDS的優(yōu)勢(shì)。

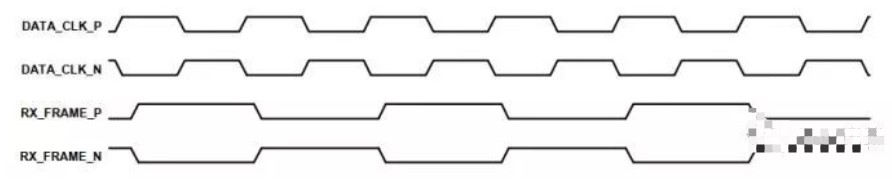

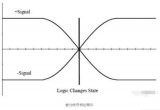

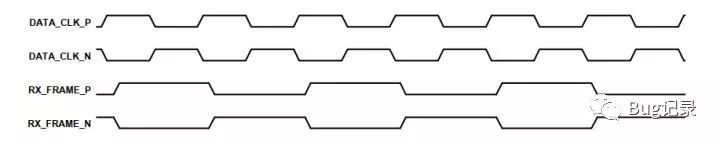

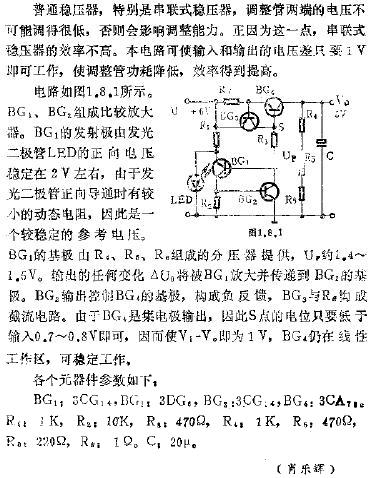

每對(duì)LVDS信號(hào)是一個(gè)差分信號(hào)對(duì),一個(gè)信號(hào)用兩個(gè)相反的p,n信號(hào)線表示,通過(guò)差值 |Vp - Vn|傳輸數(shù)據(jù),這樣可以有效減小共模噪聲的干擾,信號(hào)線傳輸如下圖:

圖中含有DATA_CLK, RX_FRAME兩個(gè)LVDS信號(hào)對(duì)

而FPGA內(nèi)部處理信號(hào)肯定還是需要使用單端信號(hào),這時(shí)就需要經(jīng)過(guò)一個(gè)差分轉(zhuǎn)單端的“工具”,將差分信號(hào)轉(zhuǎn)換為FPGA更方便處理的單端信號(hào)。

在Xilinx中,我們可以用IBUFDS原語(yǔ),可以在Language Template中找到這個(gè)原語(yǔ)的示例,經(jīng)過(guò)修改一番后,可以將差分的data_clk轉(zhuǎn)換為單端的data_clk, 原語(yǔ)如下:

IBUFDS #(

.DIFF_TERM("FALSE"), // Differential Termination

.IBUF_LOW_PWR("TRUE"), // Low power="TRUE", Highest performance="FALSE"

.IOSTANDARD("DEFAULT") // Specify the input I/O standard

) IBUFDS_inst (

.O(data_clk_tmp), // Buffer output

.I(data_clk_p), // Diff_p buffer input (connect directly to top-level port)

.IB(data_clk_n) // Diff_n buffer input (connect directly to top-level port)

);

將需要轉(zhuǎn)換的data_clk P端和N端接入IBUFDS的I和IB端口,就可以在O端口得到轉(zhuǎn)換的單端信號(hào)。

除了CLK時(shí)鐘信號(hào),其他信號(hào)的輸入轉(zhuǎn)換基本結(jié)束了;而CLK時(shí)鐘信號(hào)還需要接入BUFG,因?yàn)镃LK時(shí)鐘只有接入BUFG才能接入全局時(shí)鐘網(wǎng)絡(luò),這對(duì)于減小時(shí)序問(wèn)題有幫助。

同樣在Language Template中找到這個(gè)原語(yǔ)的示例,修改后如下:

BUFG BUFG_i0 (

.O(data_clk), // 1-bit output: Clock output, 36MHz.

.I(data_clk_tmp) // 1-bit input: Clock input, 36MHz.

);

一個(gè)輸入一個(gè)輸出,非常簡(jiǎn)單的原語(yǔ)調(diào)用!

另一邊,有輸入就會(huì)有輸出,輸出的問(wèn)題也好解決,同樣使用一個(gè)OBUFDS原語(yǔ)實(shí)現(xiàn)單端轉(zhuǎn)差分,在Language Template中找到原語(yǔ),修改后如下:

OBUFDS #(

.IOSTANDARD("LVDS18"), // Specify the output I/O standard

.SLEW("SLOW") // Specify the output slew rate

) OBUFDS_inst (

.O(tx_frame_p), // Diff_p output (connect directly to top-level port)

.OB(tx_frame_n), // Diff_n output (connect directly to top-level port)

.I(tx_frame) // Buffer input

);

設(shè)置好相應(yīng)的參數(shù)之后,將單端信號(hào)接入OBUFDS的I端口,O端口輸出差分信號(hào)的P端,OB端口輸出差分信號(hào)的N端。

最后一個(gè)小問(wèn)題就是在XDC設(shè)置中,因?yàn)橐粋€(gè)信號(hào)對(duì)有兩個(gè)管腳,比單端信號(hào)多了一倍的管腳綁定工作量;但其實(shí)我們可以只需要綁定P端的管腳,軟件會(huì)自動(dòng)幫我們綁定N端的管腳。

在設(shè)置輸入輸出端口的“IOSTANDARD”中,遇到了些許問(wèn)題,這里寫出來(lái)記錄一下,也讓后面遇到這個(gè)問(wèn)題的人有個(gè)參考;最初設(shè)置差分信號(hào)的“IOSTANDARD”時(shí),我想當(dāng)然的使用了“LVDS”,“LVDS18”等參數(shù),但是這些參數(shù)都不能最終生成比特流;

在查了一些資料以及Vivado本身的I/O Port界面里參數(shù)后發(fā)現(xiàn),差分信號(hào)的IOSTANDARD需要這樣設(shè)置:

set_property IOSTANDARD DIFF_HSTL_II_18 [get_ports tx_frame_p]

因?yàn)槲业腎O電壓是1.8V,所以最終使用了“DIFF_HSTL_II_18”,如果有更好的方案,可以一起探討探討。

總結(jié):

輸入信號(hào)需要用到IBUFDS實(shí)現(xiàn)差分轉(zhuǎn)單端,輸入時(shí)鐘還需要加BUFG

輸出信號(hào)使用OBUFDS實(shí)現(xiàn)單端轉(zhuǎn)差分

差分信號(hào)只需要綁P端管腳,“IOSTANDARD”設(shè)置需要注意

輸入輸出端口的簡(jiǎn)單處理之后,這些信號(hào)為了提高傳輸數(shù)據(jù)的效率,還使用了DDR(Double Data Rate)技術(shù)傳輸數(shù)據(jù),如何解決DDR問(wèn)題,下一篇文章再來(lái)探討。

審核編輯:劉清

LVDS差分接口信號(hào)輸入輸出的處理簡(jiǎn)析

- FPGA(632052)

- CMOS(241942)

- lvds接口(18086)

- 差分接口(11467)

相關(guān)推薦

熱點(diǎn)推薦

基于LVDS差分接口之IOSERDES的高速串行通信

項(xiàng)目涉及5片F(xiàn)PGA之間的多機(jī)通信,1片主FPGA,4片從FPGA,5片F(xiàn)PGA采用星形連接的拓?fù)浣Y(jié)構(gòu)。4個(gè)從機(jī)與主機(jī)之間通信接口采用基于LVDS_33的差分IO接口標(biāo)準(zhǔn),以滿足高速率,抗干擾

2022-12-22 14:05:33 4075

4075

4075

4075LVDS發(fā)送芯片之輸入與輸出信號(hào)

這種接口電路中,采用單路方式傳輸,每個(gè)基色信號(hào)采用6位數(shù)據(jù),共18位RGB數(shù)據(jù),因此,也稱18位或18bit LVDS接口。此,也稱18位或18bit LVDS接口。

2023-03-28 11:46:23 5314

5314

5314

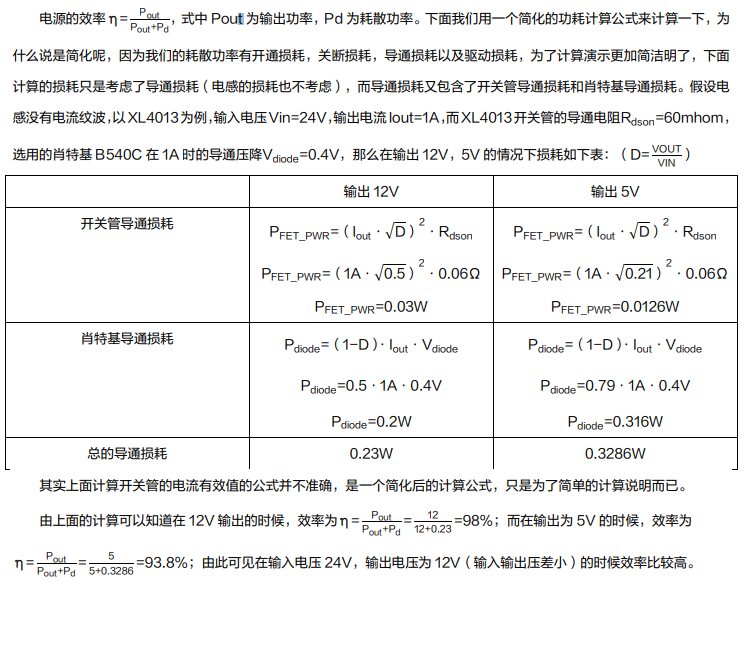

5314降壓DCDC有輸入輸出電壓差嗎

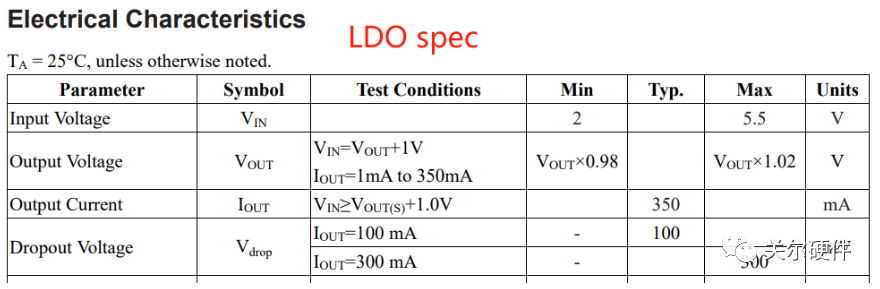

在LDO specfication里面,有Dropout Voltage(輸入輸出電壓差)的參數(shù)。如下圖,輸出電流100mA時(shí),典型壓差是100mV;輸出電流是300mA時(shí),MAX壓差是300mV(線路阻抗不變下,流過(guò)電流越大,壓降也就越大。二極管的壓降也是電流越大,壓降越大。)。

2023-11-15 18:41:26 6793

6793

6793

6793

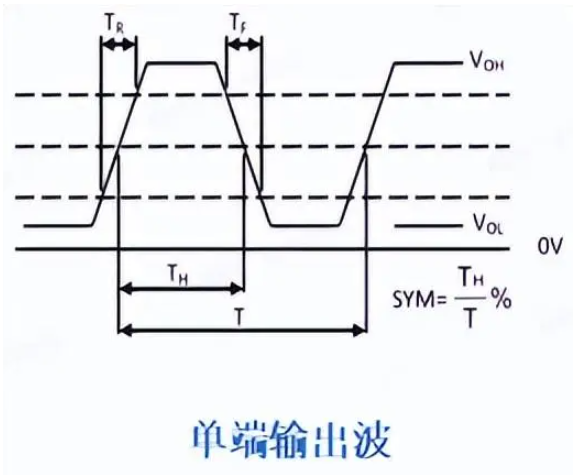

差分輸出與單端輸出的差別

差分輸出是一種電路設(shè)計(jì)技術(shù),主要用于提取信號(hào)的變化情況,以及對(duì)信號(hào)進(jìn)行放大和處理。差分輸出將輸入信號(hào)通過(guò)差動(dòng)放大器進(jìn)行放大,然后輸出兩個(gè)相位相反的信號(hào)。

2024-01-31 18:17:12 6775

6775

6775

6775

常見(jiàn)差分邏輯電平和相關(guān)輸入輸出原理

本篇主要介紹常用的差分邏輯電平,包括LVDS、xECL、CML、HCSL/LPHCSL、TMDS等。 1、LVDS電平 LVDS器件是近年來(lái)National Semiconductor公司發(fā)展的一種

2020-12-23 15:09:14 17407

17407

17407

17407

LVDS接口標(biāo)準(zhǔn)

使得信號(hào)能在差分PCB線對(duì)或平衡電纜上以幾百M(fèi)bps的速率傳輸,其低壓幅和低電流驅(qū)動(dòng)輸出實(shí)現(xiàn)了低噪聲和低功耗。幾十年來(lái),5V供電的使用簡(jiǎn)化了不同技術(shù)和廠商邏輯電路之間的接口。然而,隨著集成電路的發(fā)展

2011-02-23 09:55:17

LVDS低電壓差分信號(hào)

LVDS:Low-Voltage Differential Signaling 低電壓差分信號(hào)。一種信號(hào)傳輸模式,是一種電平標(biāo)準(zhǔn),LVDS接口又稱RS-644總線接口,是一種數(shù)據(jù)傳輸和接口

2016-04-15 16:13:33

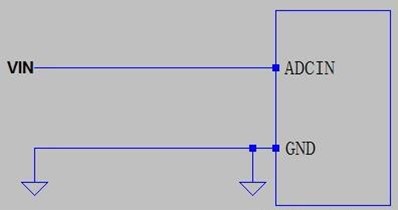

差分輸入的AD轉(zhuǎn)換芯片如何處理單端輸入的信號(hào)?

對(duì)一個(gè)儀表放大器輸出的信號(hào)進(jìn)行AD轉(zhuǎn)換,怎么使用差分輸入呢,IN-端是接地么?還是怎么處理?

即是:差分輸入的AD轉(zhuǎn)換芯片如何處理單端輸入的信號(hào)

2025-02-07 06:40:42

輸入輸出電壓差

本帖最后由 洌洌的水 于 2015-5-8 22:27 編輯

請(qǐng)問(wèn)開(kāi)關(guān)型降壓變換器輸入輸出電壓差是什么意思,是輸出達(dá)到額定值時(shí),輸入端與輸出端的最小壓降嗎?是的話,這個(gè)值隨輸出電流變化嗎?就像圖里面的輸入——輸出電壓差(V),這是LM2576的資料圖

2015-05-08 22:18:20

ADC3663輸出SLVDS差分電壓超過(guò)FPGA接口LVDS接口的輸入電壓范圍,如何處理?

根據(jù)ADC3663手冊(cè),輸出格式為SLVDS,VCM=1.0V, VOD=500mV(min),700mV(typ), 850mV(max). 而FPGA通常LVDS接口(輸入)VIDIFF最大

2024-11-27 06:23:32

ADS5463的單端輸入信號(hào)(70MHz左右)怎么轉(zhuǎn)差分輸入?

ADS5463的單端輸入信號(hào)(70MHz左右)怎么轉(zhuǎn)差分輸入,DAC3162的差分輸出怎么轉(zhuǎn)成電壓型的單端輸出。

2025-02-11 06:40:20

FPGA | LVDS屏幕接口的應(yīng)用

;4) PCB 板盡可能鋪設(shè)大面積的 GND ;

5) LVDS 輸出差分信號(hào)走線設(shè)計(jì)成 100Ω差分匹配,走線盡可能保持等長(zhǎng);6) LVDS 輸出差分信號(hào)正負(fù)通道間隔 S1 盡可能

2023-06-05 17:31:08

FPGA編程LVDS信號(hào)圖像處理技術(shù)

各位大神,小弟這邊先謝過(guò)了,真的很急!目前我需要使用FPGA技術(shù)來(lái)處理一款1對(duì)時(shí)鐘LVDS信號(hào)和8對(duì)數(shù)據(jù)LVDS信號(hào)攝像頭模組,我這邊只能對(duì)并口信號(hào)和MIPI信號(hào)輸出的攝像頭模組進(jìn)行測(cè)試調(diào)焦,對(duì)于LVDS信號(hào)的模組沒(méi)有相關(guān)技術(shù),請(qǐng)大神幫忙啊!!!非常感謝!!!可付報(bào)酬!!!

2014-07-17 16:40:58

Input接口信號(hào)的比較

,提高數(shù)據(jù)的傳輸速度,發(fā)展了低壓差分信號(hào)LVDS接口技術(shù)。LVDS是一種低擺幅的差分信號(hào)技術(shù),它使得信號(hào)能在差分PCB線對(duì)或平衡電纜上以幾百M(fèi)bps的速率傳輸,其低壓幅和低電流驅(qū)動(dòng)輸出實(shí)現(xiàn)了低噪聲

2019-09-23 09:05:05

LDO輸入輸出電壓差

輸入輸出電壓差輸入輸出電壓差是低壓差線性穩(wěn)壓器最重要的參數(shù)。在保證輸出電壓穩(wěn)定的前提下,該電壓差越低,線性穩(wěn)壓器的性能越好。比如,5.0V的低壓差線性穩(wěn)壓器,只要輸入5.5V,就能使輸出電壓穩(wěn)定在5.0V。

2011-06-16 16:15:33

OpenHarmony智慧設(shè)備開(kāi)發(fā)-芯片模組簡(jiǎn)析RK3568

處理器采用22nm工藝,主頻高達(dá)2.0GHz;支持藍(lán)牙、Wi-Fi、音頻、視頻和攝像頭等功能,擁有豐富的擴(kuò)展接口,支持多種視頻輸入輸出接口,配置雙千兆自適應(yīng)RJ45以太網(wǎng)口,可滿足NVR、工業(yè)網(wǎng)關(guān)等多網(wǎng)口

2023-05-16 14:56:42

PGA5807差分輸入差分輸出,可否改成單端輸入輸出?

如上圖所示PGA5807差分輸入差分輸出,可否改成單端輸入輸出? 按照上圖連接方法,使用信號(hào)發(fā)生器

在輸入端加載一個(gè)2.5MHzVpp100mv正弦波,通過(guò)串口控制增益,在空載與負(fù)載

2024-08-21 07:02:09

以太網(wǎng)的接口信號(hào)在PCB走線的時(shí)候差分可以不等長(zhǎng)么?

以太網(wǎng)的接口信號(hào),在PCB走線的時(shí)候,差分可以不等長(zhǎng)么?如果要等長(zhǎng),誤差是多少?

2023-04-07 17:38:17

低功耗差分接口的基本約束

之間傳輸差分電流。接下來(lái)如果有要求,在使用一個(gè)單獨(dú)的互感級(jí)實(shí)現(xiàn)電流電壓轉(zhuǎn)換前增大差分電流。如果容性負(fù)載沒(méi)有足夠大到影響電壓信號(hào),在芯片內(nèi)部要進(jìn)行低阻抗到高阻抗的變換。低輸入阻抗對(duì)于電流處理來(lái)說(shuō)非常

2019-04-16 07:00:03

在差分輸入或者輸出的另外一個(gè)端口用一個(gè)電容接地來(lái)實(shí)現(xiàn)是否合理

最近一直在調(diào)試放大器方面的芯片,突然有個(gè)關(guān)于“差分信號(hào)”單端輸入輸出的疑問(wèn),寫出來(lái)討論一下! 對(duì)于差分輸入輸出的好處我就不再多說(shuō)了,相信大家都有一定的了解!我的疑問(wèn)就是,我們實(shí)驗(yàn)室使用的幾款放大器

2018-11-29 09:17:14

怎么實(shí)現(xiàn)一種基于FPGA高速數(shù)據(jù)采集系統(tǒng)中的輸入輸出接口?

本文給出了基于FPGA高速數(shù)據(jù)采集系統(tǒng)中的輸入輸出接口的實(shí)現(xiàn),介紹了高速傳輸系統(tǒng)中RocketIO設(shè)計(jì)以及LVDS接口、LVPECL接口電路結(jié)構(gòu)及連接方式,并在我們?cè)O(shè)計(jì)的高速數(shù)傳系統(tǒng)中得到應(yīng)用。

2021-04-29 06:04:42

時(shí)鐘分配輸入74.25的差分或單端,輸出至少2路74.25M的差分LVDS,請(qǐng)問(wèn)有哪些芯片通達(dá)到功能

您好,我需要一個(gè)時(shí)鐘分配器,輸入74.25的差分或單端,輸出至少2路74.25M的差分LVDS,有哪些芯片通達(dá) 到功能,謝謝

2018-12-17 09:33:40

有沒(méi)有人有使用差分HSTL與LVDS接口的經(jīng)驗(yàn)?

我正在使用Artix 7 fpga。我沒(méi)有2.5V IO庫(kù),所以我不能使用LVDS輸出。有沒(méi)有人有使用差分HSTL與LVDS接口的經(jīng)驗(yàn)? TI建議為接口提供交流耦合終端,有何評(píng)論?見(jiàn)附件。

2020-07-30 10:49:04

有沒(méi)有使用FPGA控制tdc-gpx2芯片LVDS輸入輸出功能的朋友?

有無(wú)大佬用過(guò)TDC_GPX2這款芯片的LVDS輸入輸出功能,有償求助

2024-04-23 22:56:11

液晶屏MIPI接口與LVDS接口區(qū)別(總結(jié))

是RGB666或者RGB888還有行場(chǎng)同步和時(shí)鐘;LVDS接口信號(hào)類型是LVDS信號(hào)(低電壓差分對(duì)),信號(hào)的內(nèi)容是RGB數(shù)據(jù)還有行場(chǎng)同步和時(shí)鐘;MIPI DSI接口信號(hào)類型是LVDS信號(hào),信號(hào)的內(nèi)容是視頻流數(shù)據(jù)

2016-06-13 20:18:24

請(qǐng)問(wèn)AD9516的差分參考輸入和外部時(shí)鐘輸入能否為LVDS

請(qǐng)教AD9516的差分參考輸入(ref)和外部時(shí)鐘輸入(clk)能否為LVDS?還是必須為TTL?謝謝!

2018-11-05 09:24:01

請(qǐng)問(wèn)AFE5801的輸入輸出可以直接和FPGA的IO連嗎?

請(qǐng)問(wèn)AFE5801的輸入輸出可以直接和FPGA的IO連嗎?FPGA的bank電壓標(biāo)準(zhǔn)是LVDS25,AFE5801的輸出信號(hào)標(biāo)準(zhǔn)是差分LVDS信號(hào)。這樣連會(huì)不會(huì)導(dǎo)致信號(hào)采集不到?

還有,AFE5801如果在差分輸出端沒(méi)有外接100歐的匹配電阻,會(huì)有什么影響?

謝謝!

2025-02-05 06:00:34

請(qǐng)問(wèn)ad8331怎么配置差分輸入?

把a(bǔ)d8331配制成差分輸入差分輸出,還能根據(jù)數(shù)據(jù)手冊(cè)上的單端輸入的說(shuō)明配置嗎?為什么單獨(dú)仿真ad8331的LNA差分輸出信號(hào)和輸入信號(hào)幅度差不多,沒(méi)有放大19dB。

2023-11-21 08:15:40

請(qǐng)問(wèn)超高速比較的是否有差分輸入,LVDS輸出的?

咨詢超高速比較的是否有差分輸入,LVDS輸出的?關(guān)于差分輸入的如何實(shí)現(xiàn)過(guò)零比較。

2018-08-07 08:13:23

音頻的輸入輸出問(wèn)題

手機(jī)的耳機(jī)插孔那塊是差分輸出的音頻還是單端的左右聲道的音頻信號(hào)?我現(xiàn)在使用的是tlv320aic31音頻編解碼芯片,需要差分音頻輸入,可以使用手機(jī)接口進(jìn)行測(cè)試嗎??

2018-06-21 11:17:46

高清圖像處理芯片串行差分輸出接口測(cè)試研究

本文提供了平板顯示屏連接接口信號(hào)LVDS的測(cè)試方案及FPD-Link 接口的多種格式數(shù)據(jù)的支持。主要討論了滿足TIA/EIA標(biāo)準(zhǔn)的測(cè)試,信號(hào)質(zhì)量測(cè)試方法中的眼圖測(cè)試和位錯(cuò)誤率測(cè)試法及多種

2009-06-10 11:08:40 2

2

2

2視頻打印機(jī)的輸入輸出

視頻打印機(jī)的輸入輸出 輸入輸出指的是產(chǎn)品輸入輸出視頻信號(hào)的端口,比較常見(jiàn)的是S端子和復(fù)合視頻端口。

2009-12-31 10:38:28 1768

1768

1768

1768怎樣才能充分利用低壓差分信號(hào)LVDS

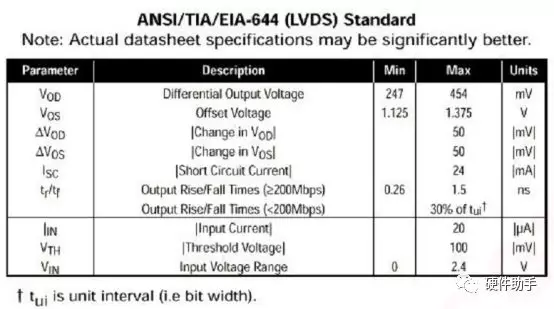

低壓差分信號(hào)(LVDS)是一種低壓、差分信號(hào)傳輸方案,主要用于高速數(shù)據(jù)傳輸。根據(jù) ANSI/TIA/EIA-644 規(guī)范中的定義,它是一種最為常見(jiàn)的差分接口。這種標(biāo)準(zhǔn)只對(duì)適合于 LVDS 應(yīng)用的驅(qū)動(dòng)

2010-06-10 09:59:48 2560

2560

2560

2560

高速LVDS(低壓差分信號(hào))接口電路設(shè)計(jì)

隨著數(shù)字電路數(shù)據(jù)量的提高,數(shù)據(jù)的傳輸速率也越來(lái)越快,LVDS(低壓差分信號(hào))標(biāo)準(zhǔn)越來(lái)越多的應(yīng)用在FPGA和ASIC器 件中。文章對(duì)LVDS信號(hào)的特點(diǎn)進(jìn)行了分析,說(shuō)明了PCB設(shè)計(jì)中差分走線的注意事項(xiàng)并結(jié)合實(shí)際應(yīng)用設(shè)計(jì)了一塊LVDS接口板。 關(guān)鍵詞: LVDS; PCB設(shè)計(jì);接口;阻抗

2011-02-23 09:54:03 341

341

341

341模擬量輸入輸出

這類接口板(卡)能使計(jì)算機(jī)具有輸入輸出模擬量信號(hào)的功能,將用模擬量表示的外部狀態(tài)轉(zhuǎn)換成數(shù)據(jù)(數(shù)字量信號(hào)),然后傳送到計(jì)算機(jī);計(jì)算機(jī)也可以發(fā)送一個(gè)數(shù)據(jù)(數(shù)字量信號(hào))

2011-04-04 14:45:01 126

126

126

126什么是輸入輸出模塊_輸入輸出模塊有什么作用

輸入輸出模塊也稱為控制模塊,在有控制要求時(shí)可以輸出信號(hào),或者提供一個(gè)開(kāi)關(guān)量信號(hào),使被控設(shè)備動(dòng)作,同時(shí)可以接收設(shè)備的反饋信號(hào),以向主機(jī)報(bào)告,是火災(zāi)報(bào)警聯(lián)動(dòng)系統(tǒng)中重要的組成部分。市場(chǎng)上的輸入輸出

2018-05-21 10:28:16 121544

121544

121544

121544介紹作為表示線性調(diào)整器基本性能之一的輸入輸出電壓差

此外,按字面解釋輸入輸出電壓差是表示輸入電壓和輸出電壓的電壓差,由此說(shuō)明“只要輸入電壓和輸出電壓之間存在一定的電壓差即可汲取相對(duì)應(yīng)的電流”。作為參考,圖8表示XC6222x281的輸入輸出電位差特性

2018-05-29 11:44:05 6748

6748

6748

6748

淺談差分處理和信號(hào)分析

差分線是PCB設(shè)計(jì)中非常重要的一部分信號(hào)線,信號(hào)處理要求也是相當(dāng)嚴(yán)謹(jǐn),今天為大家介紹下差分信號(hào)的原理以及其在PCB設(shè)計(jì)中的處理方法。 什么是差分信號(hào) 差分傳輸是一種信號(hào)傳輸?shù)募夹g(shù),區(qū)別于傳統(tǒng)的一根

2020-03-09 09:54:38 2586

2586

2586

2586

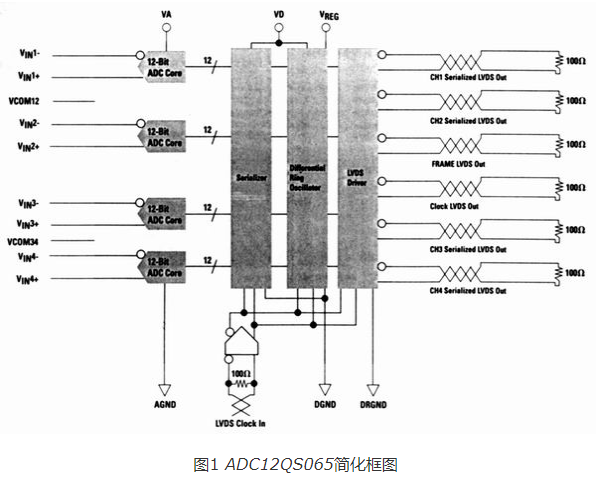

ADC12QS065里用LVDS格式解決輸出信號(hào)傳輸問(wèn)題

在輸入信號(hào)轉(zhuǎn)換數(shù)字?jǐn)?shù)據(jù)之后,必須傳輸它們到DSP或ASIC/FPGA進(jìn)行處理。流行的全差分輸出信號(hào)傳輸是方便的。全差分的輸出信號(hào)通過(guò)兩條對(duì)稱線給出和吸收電流。這種信號(hào)傳輸?shù)囊粋€(gè)例子是LVDS(低壓差分信號(hào))格式。ADC12QS065用LVDS來(lái)解決所有這些系統(tǒng)問(wèn)題(圖1)。

2020-04-04 17:43:00 3015

3015

3015

3015

差分處理方法詳解及信號(hào)分析

來(lái)源:羅姆半導(dǎo)體社區(qū) 差分線是PCB設(shè)計(jì)中非常重要的一部分信號(hào)線,信號(hào)處理要求也是相當(dāng)嚴(yán)謹(jǐn),今天為大家介紹下差分信號(hào)的原理以及其在PCB設(shè)計(jì)中的處理方法。 什么是差分信號(hào) 差分傳輸是一種信號(hào)傳輸

2022-12-13 11:28:36 2998

2998

2998

2998簡(jiǎn)析用電阻設(shè)定增益的單端至差分轉(zhuǎn)換器資料下載

電子發(fā)燒友網(wǎng)為你提供簡(jiǎn)析用電阻設(shè)定增益的單端至差分轉(zhuǎn)換器資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計(jì)、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-04 08:46:29 3

3

3

3LTC6362LT5400演示電路-采用匹配電阻的差分輸入輸出ADC驅(qū)動(dòng)器

LTC6362LT5400演示電路-采用匹配電阻的差分輸入輸出ADC驅(qū)動(dòng)器

2021-06-05 19:13:28 2

2

2

2DC-DC降壓芯片是否有輸入輸出壓差范圍要求?

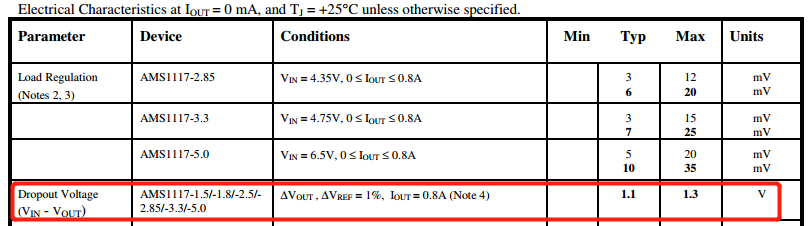

在LDO應(yīng)用中,會(huì)有一個(gè)輸入輸出壓差范圍的概念,如AMS1117,壓差Dropout Voltage的典型值為1.1V,即:輸入至少比輸出高1.1V的壓降才能支持所需要的輸出。在之前寫過(guò)...

2021-11-09 20:06:01 16

16

16

16單片機(jī):A/D 差分輸入信號(hào)

文章目錄A/D 差分輸入信號(hào)A/D 差分輸入信號(hào)在前面的文章已經(jīng)提到過(guò),控制字的第4位和第5位是用于控制 PCF8591 的模擬輸入引腳是單端輸入還是差分輸入。差分輸入是模擬電路常用的一個(gè)技巧,這里

2021-11-23 17:36:20 10

10

10

10淺析差分信號(hào)和單端信號(hào)的區(qū)別

差分信號(hào)其實(shí)就是把兩個(gè)單路信號(hào)的差值經(jīng)行傳輸或者輸入輸出處理。

2021-11-28 15:21:08 20837

20837

20837

20837GM8827C 多通道LVDS 串行發(fā)送器,27位CMOS/TTL信號(hào)轉(zhuǎn)化為多路LVDS信號(hào)

差分形式并保持與輸出串行數(shù)據(jù)流的同步關(guān)系。LVDS 輸出有 2 個(gè)鏈路,每個(gè)鏈路包括 4 對(duì) LVDS 差分?jǐn)?shù)據(jù)輸出和 1 對(duì)并行的 LVDS 差分時(shí)鐘。 24 位 LVDS 發(fā)送器1 、產(chǎn)品概述本產(chǎn)品為一款多通道 LVDS 串行發(fā)送器,實(shí)現(xiàn)將 27 位 CMOS/TTL 信號(hào)(24 位 RGB

2021-11-30 21:06:05 15

15

15

15GPIO通用輸入輸出

GPIO通用輸入輸出一、GPIO的功能概述用途:GPIO是通用輸入輸出(General Purpose I/O)的簡(jiǎn)稱,主要用于工業(yè)現(xiàn)場(chǎng)需要用到數(shù)字量輸入/輸出的場(chǎng)合。例如:輸出功能:繼電器、LED

2021-12-20 18:58:47 6

6

6

6HDMI模塊接口概念及接口信號(hào)定義介紹

HDMI模塊接口概念及接口信號(hào)定義介紹

HDMI的應(yīng)用范圍

HDMI接口PCB布局要點(diǎn)

HDMI接口PCB布線要點(diǎn)

2022-04-12 14:38:59 0

0

0

0龍迅HDMI接口信號(hào)轉(zhuǎn)換的應(yīng)用案例

Lontium龍迅MIPI/LVDS接口信號(hào)轉(zhuǎn)換器有著多種接口格式,芯片功能包括Transmitter、Receiver、Switch、Splitter、Repeater、Matrix/Crosspoint、Converter

2022-06-14 17:00:55 5565

5565

5565

5565

Logos系列FPGA輸入輸出接口(IO)用戶指南

電子發(fā)燒友網(wǎng)站提供《Logos系列FPGA輸入輸出接口(IO)用戶指南.pdf》資料免費(fèi)下載

2022-09-26 10:19:46 18

18

18

18基于LVDS差分接口之IOSERDES的高速串行通信

項(xiàng)目涉及5片F(xiàn)PGA之間的多機(jī)通信,1片主FPGA,4片從FPGA,5片F(xiàn)PGA采用星形連接的拓?fù)浣Y(jié)構(gòu)。4個(gè)從機(jī)與主機(jī)之間通信接口采用基于LVDS_33的差分IO接口標(biāo)準(zhǔn),以滿足高速率,抗干擾

2022-12-23 06:15:04 1871

1871

1871

1871DC-DC降壓芯片的輸入輸出壓差范圍的要求

**在LDO應(yīng)用中,會(huì)有一個(gè)輸入輸出壓差范圍的概念** ,如AMS1117,壓差Dropout Voltage的典型值為1.1V,即:輸入至少比輸出高1.1V的壓降才能支持所需要的輸出。

2023-02-17 10:59:53 9990

9990

9990

9990

LVDS差分信號(hào)輸入輸出的處理方法

最近調(diào)試芯片遇到一個(gè)選擇題,需要決定數(shù)據(jù)接口的接口標(biāo)準(zhǔn),是選用LVDS差分接口還是CMOS單端接口。

2023-06-16 09:55:33 4052

4052

4052

4052

plc帶模擬量輸入輸出和不帶模擬量輸入輸出有什么區(qū)別啊?

的PLC類型,它們之間有很大的差異。 PLC帶模擬量輸入輸出與PLC不帶模擬量輸入輸出的區(qū)別在于它們可以控制和處理的不同信號(hào)類型。模擬量輸入輸出和數(shù)字量輸入輸出都是一種用于控制系統(tǒng)的信號(hào)類型。 “數(shù)字量”信號(hào)是通過(guò)開(kāi)關(guān)等離散的狀態(tài)表

2023-10-17 16:44:51 2673

2673

2673

2673什么叫做LVDS信號(hào)?請(qǐng)問(wèn)TTL信號(hào)與LVDS信號(hào)有什么區(qū)別?

什么叫做LVDS信號(hào)?請(qǐng)問(wèn)TTL信號(hào)與LVDS信號(hào)有什么區(qū)別? LVDS信號(hào) LVDS(Low Voltage Differential Signaling)又稱低壓差分信號(hào)傳輸技術(shù),是一種采用差分

2023-10-18 15:38:18 4101

4101

4101

4101在差分電路中輸出電壓為什么要偏置呢?

在差分電路中輸出電壓為什么要偏置呢? 差分電路是一種常見(jiàn)的電路,在信號(hào)處理、放大和傳輸中廣泛應(yīng)用。它的基本原理是將兩個(gè)輸入信號(hào)的差異轉(zhuǎn)換為電壓輸出信號(hào),因此差分電路也被稱為差分放大器。而在差分電路中

2023-10-23 10:23:57 2855

2855

2855

2855差分放大電路的四種輸入和輸出方式比較

,差分電路可以很好地抑制噪聲和干擾信號(hào),這使得差分電路在高精度、低噪聲等應(yīng)用中有廣泛的應(yīng)用。 差分電路的四種輸入輸出方式包括差模輸入、共模輸入、差模輸出和共模輸出。下面我們將分別對(duì)這四種方式進(jìn)行詳細(xì)的介紹和比

2023-10-25 11:01:43 12649

12649

12649

12649什么是差分輸出方式?什么東西會(huì)影響差分輸出幅值呢?

什么是差分輸出方式?什么東西會(huì)影響差分輸出幅值呢? 差分輸出方式是一種電路設(shè)計(jì)技術(shù),常用于提取信號(hào)的變化情況,以及對(duì)信號(hào)進(jìn)行放大和處理。它可以將輸入信號(hào)通過(guò)差動(dòng)放大器進(jìn)行放大,然后輸出兩個(gè)相位

2023-11-20 16:36:00 3589

3589

3589

3589輸入輸出電壓差與效率的關(guān)系

在開(kāi)關(guān)穩(wěn)壓電源中,輸入電壓的范圍是預(yù)知的,輸出電壓也是知道的,但是輸入輸出的電壓差和轉(zhuǎn)換效率的關(guān)系很多人 不清楚,有經(jīng)驗(yàn)的工程師就會(huì)根據(jù)公式去推導(dǎo)出來(lái)輸入輸出電壓差越小,轉(zhuǎn)換效率越高。

2024-01-05 15:12:04 1757

1757

1757

1757

PLC的輸入輸出接口是否需要進(jìn)行隔離保護(hù)?

PLC(可編程邏輯控制器)的輸入輸出接口是否需要進(jìn)行隔離保護(hù),取決于具體的應(yīng)用場(chǎng)景和需求。

2024-02-23 09:09:14 3440

3440

3440

3440差分編碼器信號(hào)如何接plc?

差分編碼器信號(hào)通常用于測(cè)量旋轉(zhuǎn)運(yùn)動(dòng)或線性位置,接收差分編碼器信號(hào)的PLC(可編程邏輯控制器)需要進(jìn)行相應(yīng)的信號(hào)處理才能正確讀取并理解編碼器的輸出。下面是將差分編碼器信號(hào)接入PLC的一般步驟: 1.

2024-03-05 08:42:49 6626

6626

6626

6626

差分的概念

端TXD,接收端RXD,參考端是地,GND,是典型的單端信號(hào)輸入輸出。 單端輸入時(shí),是判斷信號(hào)與?地的電壓差。 RS232單端信號(hào)接口示意圖 差分信號(hào): 差分(Differential)是將單端信號(hào)進(jìn)行差分變換,輸出兩個(gè)信號(hào),一個(gè)和原信號(hào)同相,一個(gè)和原信號(hào)反相。差分信號(hào)有較強(qiáng)的抗共

2024-04-01 10:13:38 1903

1903

1903

1903

差分放大電路輸入與輸出的大小和相位關(guān)系

和一個(gè)輸出端的放大器,其放大倍數(shù)與兩個(gè)輸入端之間的差值成正比。當(dāng)兩個(gè)輸入端的電壓相等時(shí),輸出為零;當(dāng)兩個(gè)輸入端的電壓不相等時(shí),輸出為兩個(gè)輸入端電壓差的放大值。 1.2 差分放大電路的分類 差分放大電路可以分為兩種類型:?jiǎn)味溯?/div>

2024-07-08 14:58:14 5196

5196

5196

5196差分放大電路可以放大什么信號(hào)

電路是一種雙端輸入、單端輸出的放大器。它有兩個(gè)輸入端,分別稱為正輸入端(+)和負(fù)輸入端(-),以及一個(gè)輸出端。差分放大電路的主要功能是放大兩個(gè)輸入信號(hào)之間的差值,即輸出信號(hào)與輸入信號(hào)差值成正比。 基本結(jié)構(gòu) 差分放大

2024-07-09 15:03:16 2088

2088

2088

2088差模輸入信號(hào)的概念、原理及應(yīng)用

差模輸入信號(hào)(Differential Input Signal)是一種信號(hào)處理技術(shù),主要用于模擬信號(hào)處理領(lǐng)域。它涉及到兩個(gè)輸入信號(hào),這兩個(gè)輸入信號(hào)通常被稱為差模信號(hào)(Differential

2024-07-15 10:29:12 3169

3169

3169

3169差分放大電路同相輸入和反相輸入怎么看

差分放大電路是一種具有高輸入阻抗、高增益和高抗干擾能力的放大電路,廣泛應(yīng)用于模擬信號(hào)處理領(lǐng)域。差分放大電路的輸入端有兩個(gè),分別是同相輸入端和反相輸入端。 同相輸入端和反相輸入端的特點(diǎn) 差分放大電路

2024-08-05 09:24:42 6491

6491

6491

6491寄存器的輸入輸出方式

寄存器的輸入輸出方式是數(shù)字電路設(shè)計(jì)中至關(guān)重要的部分,它決定了數(shù)據(jù)如何在寄存器中進(jìn)出以及處理的效率。下面將詳細(xì)探討寄存器的幾種主要輸入輸出方式,包括并行輸入輸出、串行輸入輸出以及雙向輸入輸出,并會(huì)擴(kuò)展到移位寄存器的特定輸入輸出方式。

2024-09-05 14:09:52 3531

3531

3531

3531差分放大電路輸入信號(hào)類型和應(yīng)用優(yōu)勢(shì)

差分放大電路的核心功能是放大兩個(gè)輸入端之間的電壓差異,即差分信號(hào)。當(dāng)兩個(gè)輸入端的電壓存在差別時(shí),電路的輸出電壓會(huì)隨之變動(dòng),從而實(shí)現(xiàn)信號(hào)的放大。這種放大方式對(duì)于提取和處理小信號(hào)非常有效,尤其是在那些

2024-10-04 14:57:00 1557

1557

1557

1557

差分放大電路對(duì)差模信號(hào)有什么作用

差分放大電路是一種電子電路,它能夠放大兩個(gè)輸入信號(hào)之間的差值,同時(shí)抑制兩個(gè)輸入端共同的信號(hào)(共模信號(hào))。這種電路在許多應(yīng)用中非常重要,比如音頻放大器、傳感器信號(hào)處理、模擬信號(hào)處理等領(lǐng)域。 差分放大

2024-10-15 10:41:13 1905

1905

1905

1905lvds接口和HDMI的區(qū)別 lvds接口電路設(shè)計(jì)技巧

LVDS(Low Voltage Differential Signaling,低電壓差分信號(hào))接口和HDMI(High-Definition Multimedia Interface,高清多媒體

2024-11-21 16:06:50 4098

4098

4098

4098MAX9374/MAX9374A差分LVPECL至LVDS變換器技術(shù)手冊(cè)

MAX9374和MAX9374A是為電訊應(yīng)用而設(shè)計(jì)的2.0GHz差分LVPECL到LVDS電平轉(zhuǎn)換器,具有250ps的傳輸延遲。差分輸出信號(hào)符合ANSI TIA/EIA-644 LVDS標(biāo)準(zhǔn)。輸入

2025-05-19 10:43:28 743

743

743

743

SN65LVDS20和SN65LVP20:高速差分信號(hào)處理的理想之選

20和SN65LVP20芯片,看看它們?cè)贚VPECL和LVDS信號(hào)處理方面的卓越表現(xiàn)。 文件下載: sn65lvp20.pdf 一、產(chǎn)品概述 SN65LVDS20和SN65LVP20是將高速差分接收器

2025-12-29 16:40:03 154

154

154

154 電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論