Verilog語言和VHDL語言是兩種不同的硬件描述語言,但并非所有人都同時精通兩種語言,所以在某些時候,需要把Verilog代碼轉(zhuǎn)換為VHDL代碼。本文以通用的XHDL工具為例對Verilog轉(zhuǎn)換

2020-11-10 15:41:11 11658

11658

首先,考慮x和z在verilog條件語句中的使用情況,然后我們再考慮在verilog中用x和z給其他reg/wire賦值的情況。

2023-11-02 09:40:10 2928

2928

),遇到了幾個問題:1)文件名怎么放到接口上,我知道VHDL有text數(shù)據(jù)類型,這種數(shù)據(jù)類型如何放到接口上,怎么操作?2) 我使用的readline讀一行數(shù)據(jù)(這樣如果一行有幾個數(shù)據(jù)就不方便

2016-01-14 22:31:19

verilog 宏功能很弱,不能定義宏參數(shù),很不方便,比如一組組合電路持續(xù)賦值:ssign wto_0 =wt[0];assign wto_1 =wt[1];assign wto_2 =wt[2

2012-10-07 10:56:13

verilog 語法在復(fù)習(xí)進(jìn)階

2013-09-19 08:18:00

大家好使用Verilog語言,可以在PSoC中創(chuàng)建類似CysDelay-()、CysDelayUs()的毫秒級或微秒級延遲。……任何人請幫助我如何使用Verilog在PSoC中創(chuàng)建延遲 以上

2018-11-06 14:17:33

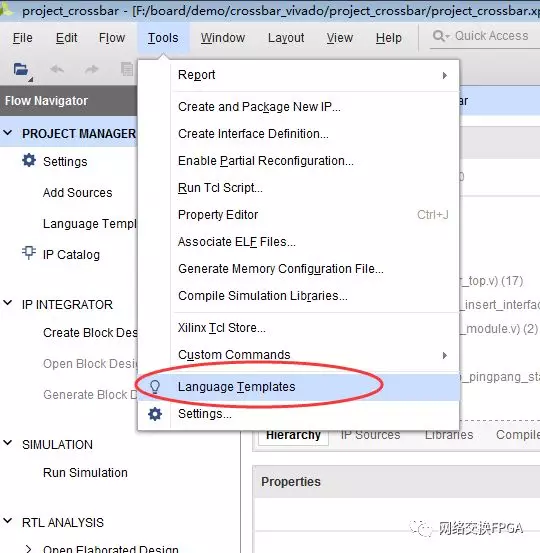

[table][tr][td]習(xí)慣了自己發(fā)現(xiàn)一些小問題,既然發(fā)現(xiàn)了,就記下來吧,不然又要忘了,這是多么悲痛的領(lǐng)悟。 今天在用vivado進(jìn)行塊設(shè)計時所生成的頂層模塊居然是用VHDL語言描述的,這時

2018-07-03 12:58:49

[table][tr][td]習(xí)慣了自己發(fā)現(xiàn)一些小問題,既然發(fā)現(xiàn)了,就記下來吧,不然又要忘了,這是多么悲痛的領(lǐng)悟。 今天在用vivado進(jìn)行塊設(shè)計時所生成的頂層模塊居然是用VHDL語言描述的,這時

2018-07-09 01:14:18

在使用和訪問數(shù)組的時候需要注意些什么地方

2023-10-10 07:41:38

在練習(xí)labview與數(shù)據(jù)庫的連接的時候,編寫的VI運(yùn)行經(jīng)常是閃退。但是再次打開,數(shù)據(jù)已經(jīng)輸入進(jìn)去了,說明VI運(yùn)行成功了,但是就是一直閃退,對于程序的調(diào)試非常不方便,導(dǎo)致我非常的苦惱。

用

2023-05-15 17:34:15

我在走差分線的時候出線一定要走一段平行線然后才能轉(zhuǎn)角度,在空間比較有限的地方很不方便,太占地方了。有些PCB的差分線在出線后馬上就可以轉(zhuǎn)角度,有什么地方可以設(shè)置嗎?

2016-06-29 20:45:47

多線程安全的。 選擇了Run in any thread方式,LabVIEW會在最方便的線程內(nèi)運(yùn)行動態(tài)鏈接庫函數(shù),且一般會與調(diào)用它的VI在同一個線程內(nèi)運(yùn)行。因為LabVIEW是自動多線程的語言,它也

2015-02-12 11:28:26

PROTEUS8里,兩個元器件距離較遠(yuǎn),連線不方便,怎么用一對接口表示,如何實現(xiàn)?

2016-05-20 16:39:14

因為網(wǎng)絡(luò)環(huán)境的原因,不能經(jīng)常上網(wǎng),需要用WEBENCH的時候要跑到能上網(wǎng)的地方去,很不方便。之前在TI培訓(xùn)會上看到TI的工程師就是脫機(jī)使用的WEBENCH,請問如何脫機(jī)使用?

2024-09-12 06:29:07

cadence界面拖動視圖很不方便 不知有沒有辦法改為右鍵拖動啊

2015-01-13 10:03:18

fpga用什么軟件工具開代碼比較方便比如看C語言,用Source Insight比較方便,但是發(fā)現(xiàn)用source insight 看verilog語言沒有對關(guān)鍵詞進(jìn)行特殊顏色顯示看起來比較不方便!不知道大家有沒有好的建議?

2013-04-15 21:55:44

顯存是外掛SDRAM,顯示是LTDC驅(qū)動800*480,GUI是touchgfx生成的,在顯示的時候,在像素點差異比較大的地方,顯示錯誤,都是顯示單色R或G,求大佬!!!

2024-03-28 06:42:34

已知外部輸入時鐘信號clk為50MHz,請用verilog實現(xiàn)計數(shù)器的計時1秒鐘,每間隔1秒輸出一個clk時鐘周期的脈沖信號flag,參考波形如下:

2023-08-17 09:13:59

Verilog HDL 的特點Verilog HDL 語言不僅定義了語法,而且對每個語法結(jié)構(gòu)都定義了清晰的模擬、仿真語義。使用這種語言編寫的模型可以方便地使用 Verilog 仿真器進(jìn)行驗證

2018-09-18 09:33:31

Menu Activation等等。有些時候我真的需要知道到底哪個亊件先被執(zhí)行……為了做到這個,通過在計數(shù)端線加上探針,通過比較值我就可以方便地確定哪個亊件先運(yùn)行了。

2012-01-04 10:05:15

求問大神,我想像demo_nice例子一樣仿真看核內(nèi)部信號,嘗試在IDE中寫內(nèi)部寄存器值,然后轉(zhuǎn)成.verilog用于vcs仿真讀入ITCM,這總思路是對的嗎,為什么按照demo_nice的例子編譯時候無法生成.verilog文件呢,求大神指點

2023-08-16 07:14:03

VEE用戶,我應(yīng)該做我的VEE程序,以便它可以支持條形碼閱讀器。唯一的問題是,在需要時從外部totext常量設(shè)置焦點不方便。(例如,如果我從選擇控件更改用戶,焦點應(yīng)該移動到文本控制而不需要單擊它

2019-11-04 13:23:25

我盡量描述下問題:交通燈的自學(xué)習(xí)式倒計時器,自學(xué)習(xí)的意思是倒計時器自動跟隨紅綠燈的通電時間而顯示這個時間,我碰到了一個問題,就是綠燈要結(jié)束的時候,綠燈會閃爍3秒,綠燈閃爍的時候倒計時也要繼續(xù)計時,這塊程序怎么寫。用的51單片機(jī)。

2016-10-11 09:21:52

``我們鋼廠鼓風(fēng)機(jī)用變頻器控制調(diào)速,想在距離500米外的控制室通過一臺西門子PLC遠(yuǎn)程遙控變頻器,拉線不方便,你們有這個方面的案例嗎?``

2015-05-29 09:42:02

現(xiàn)在我們知道鴻蒙內(nèi)核是liteos-a,那么基于liteos-a,能方便地開發(fā)GUI程序嗎?

2020-09-30 10:03:01

可能您像我一樣,在設(shè)計過程中曾經(jīng)經(jīng)歷過大量的工程設(shè)計審查,無論是在項目的前端還是在制造的后端,總有很多遍對每個環(huán)節(jié)進(jìn)行核查。進(jìn)行工程設(shè)計審查是為了完成多個目標(biāo),那是因為現(xiàn)在的工程團(tuán)隊都是采用基于系統(tǒng)

2022-06-14 13:43:55

國外大神Nathan Iyer在Github上發(fā)布的QuickSmith可以很好的讓我們在線分析史密斯圓圖。不僅可以分析阻抗,還能加入一系列元器件,分析插損等。你還在拿著密密麻麻的紙質(zhì)史密斯圓圖在對

2018-10-12 10:22:59

發(fā)現(xiàn)夏宇聞那本verilog HDL編程規(guī)范看起來很費勁啊,有些地方看不懂,求大神指教該怎么學(xué)習(xí)verilog,或者有沒有一些好一點的例題供我學(xué)習(xí)?

2013-09-17 09:15:04

有沒有verilog語法手冊可以方便查找

2013-04-18 17:47:10

本壇好內(nèi)容很多,但是過多的壓縮軟件,閱讀非常不方便!酒好也怕巷子深,大家都很忙,不想兜圈子,閱讀要效率,盡量全面展開內(nèi)容,讓大家暢游吧!大數(shù)據(jù)時代!

2015-12-30 21:33:35

我寫了一些實用函數(shù)來管理 ESP 上 EEPROM 中的數(shù)據(jù)。我現(xiàn)在將它重組為一個庫,以便我可以在其他項目中方便地使用它。我想把它貼在github上。我看到有一個區(qū)域“ESP8266 社區(qū)論壇”是放置它的好地方。

我可以在該區(qū)域創(chuàng)建項目嗎?如果是這樣,如何?

2023-05-22 10:21:37

紅綠燈的倒計時器,綠閃時候怎么倒計時呢,大家給提提意見,我說的是自學(xué)習(xí)式倒計時器。

2016-10-10 09:41:27

START1命令之后將CS引腳置高,在發(fā)送讀數(shù)命令之前再將CS引腳置低,但是實際采集出來的數(shù)據(jù)完全不對。請問在使用ADS1262采集數(shù)據(jù)的時候有什么需要注意的地方嗎?

2024-12-27 06:30:44

求教!C6678計時中,使用time.h中的clock()或者TSCL計數(shù)只能在軟件仿真的時候用,而實際在板子上運(yùn)行的時候不能用。在實際運(yùn)行的時候只能用硬件定時器?因為我發(fā)現(xiàn),clock()和使用硬件定時器測出來的時間不一樣。謝謝解答!

2018-08-03 09:30:45

請問VSCODE里的MicroPython程序怎么方便地下載到開發(fā)板中去運(yùn)行。目前我的SPI-Flash已掛載,MicroPython組件已安裝并可以運(yùn)行。

2022-08-29 11:33:30

allegro走線的時候如何不捕捉焊盤中心,有的時候自動捕捉焊盤中心在布線的時候很不方便

2019-02-26 10:44:47

各位專家好! 請問在調(diào)試過程中,開啟優(yōu)化后得代碼,調(diào)試很不方便,比如斷點加不上,但是不優(yōu)化執(zhí)行速度跟不上,對于這個問題,有沒有什么好的辦法?謝謝!

2018-07-31 10:02:48

作為一個新手,有幾個問題還是不懂。能麻煩大牛給解釋下嗎?使用定時器邊沿計時模式時,是在//啟動捕捉模塊 TimerEnable(TIMER4_BASE, TIMER_A);后就開始計時了嗎?可是我

2018-08-16 06:20:04

食品甲醇快速檢測儀器在什么地方可以買。食品甲醇快速檢測儀器【恒美儀器HM-C12】可快速定量檢測各類酒中的甲醇的含量,儀器預(yù)留其他項目檢測程序和端口,根據(jù)日后需求可方便的自主增加檢測

2021-03-25 09:41:33

目前,市面上的工業(yè)Modem主要以外置為主。外置Modem具有體積大、成本高、集成不方便等缺點;而嵌入式Modem以其性能穩(wěn)定、高度集成化等優(yōu)點,可以方便地嵌

2006-03-11 12:40:17 1332

1332

恩智浦的ATOP解決方案將交通事故自動報警系統(tǒng)方便地集成到車輛中

恩智浦半導(dǎo)體借助極具成本效益的汽車緊急呼叫設(shè)備全力支持歐盟每年挽救2500多條生命

2008-09-25 08:21:50 850

850 【摘 要】 介紹了一種基于Verilog-HDL描述的多功能步進(jìn)電機(jī)控制芯片的可綜合方案,該方案可方便地構(gòu)成兩相雙極或四相單極步進(jìn)電機(jī)的控制系統(tǒng)。外接元件極少,只需給定時鐘

2009-05-16 19:12:41 2343

2343

原標(biāo)題:Nonblocking Assignments in Verilog Synthesis, Coding Styles That Kill! ATTN:所有括號內(nèi)外注為理解方便或有疑問的地方,原文里并沒有。所有翻譯都是為遵循共同進(jìn)步的理想但并沒有去努力得

2011-03-29 16:25:53 0

0 廚房計時器 主要是方便家庭廚房而做的一個小設(shè)計

2015-12-22 10:45:03 8

8 一款基于verilog與VHDL相互轉(zhuǎn)化的軟件,用著很方便,很實用。

2016-03-21 17:26:48 20

20 本章講述在Verilog HDL中編寫表達(dá)式的基礎(chǔ)。表達(dá)式由操作數(shù)和操作符組成。表達(dá)式可以在出現(xiàn)數(shù)值的任何地方使用。verilog相關(guān)教程材料,有興趣的同學(xué)可以下載學(xué)習(xí)。

2016-04-25 16:09:32 19

19 Xilinx FPGA工程例子源碼:在FPGACPLD中實現(xiàn)AD或DA的文章(英文Verilog)

2016-06-07 15:07:45 18

18 用 Verilog實現(xiàn)基于FPGA 的通用分頻器的設(shè)計時鐘分頻包括奇數(shù)和偶數(shù)分頻

2016-07-14 11:32:47 46

46 當(dāng)時鐘開始計時,它將運(yùn)行并且繼續(xù)計秒直到它停止。當(dāng)讓它開始計時的程序停止的時候,時鐘繼續(xù)運(yùn)行。但是,你想要計時的事件可能不再有效。例如,如果程序測量輸入的等待時間,當(dāng)程序停止的時候,輸入已經(jīng)被接收。在這種情況下,當(dāng)程序停止的時候,程序?qū)⒉荒堋翱吹健笔录陌l(fā)生。

2018-04-03 15:45:41 11565

11565 本文首先介紹了verilog的概念和發(fā)展歷史,其次介紹了verilog的特征與Verilog的邏輯門級描述,最后介紹了Verilog晶體管級描述與verilog的用途。

2018-05-14 14:22:44 47073

47073

古代沒有機(jī)械時鐘,一般采用滴漏計時。水“滴答”著從滴漏里滴出來,通過調(diào)節(jié)滴水的速度,可以比較精確地計算出時間,可以說滴漏計時裝置是古代的“水鐘”。還有一種改進(jìn)過的滴漏計時裝置,在滴漏下面放置一個水罐

2018-08-03 14:59:56 33389

33389 如果我們只從打電話、發(fā)短信的角度來講,大屏幕手機(jī)確實不方便,現(xiàn)在有的手機(jī)屏幕超過了6.0英寸,接電話的時候甚至都需要兩個手來操作。平時出門買東西、吃個飯什么的,手機(jī)都沒地方裝,非常的麻煩。

2018-08-31 14:08:29 8159

8159 利用比較器電路方便地轉(zhuǎn)換電平和極性,use comparator circuit to convert electric polarity

關(guān)鍵字:比較器,電平轉(zhuǎn)換,極性轉(zhuǎn)換,MAX913

2018-09-20 18:33:17 1297

1297 ,可以方便地實現(xiàn)斷點計時功能,當(dāng)計時器遞減到零時,會發(fā)出光電報警信號。本設(shè)計完成的中途計時功能,實現(xiàn)了在許多的特定場合進(jìn)行時間追蹤的功能,在社會生活中也具有廣泛的應(yīng)用價值。

2018-10-12 08:00:00 70

70 目前的純電動汽車大都采用充電樁充電的方式來補(bǔ)充續(xù)航,據(jù)統(tǒng)計,截至2018年9月,國內(nèi)的公共充電樁數(shù)量已經(jīng)達(dá)到了28.5萬個。雖然充電樁的數(shù)量在不斷增加,但是始終無法解決充電慢和使用不方便的問題。

2018-12-08 11:14:31 2213

2213 本文檔的主要內(nèi)容詳細(xì)介紹的是Verilog HDL教程之Verilog HDL的命令格式資料說明。

2019-01-09 08:00:00 32

32 Verilog HDL是一種用于數(shù)字系統(tǒng)設(shè)計的語言。用Verilog HDL描述的電路設(shè)計就是該電路的Verilog HDL模型也稱為模塊。Verilog HDL既是一種行為描述的語言也是一種結(jié)構(gòu)描述的語言。

2019-03-08 14:29:12 13726

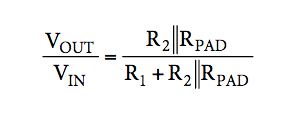

13726 有時可以方便地對音頻系統(tǒng)中的音量進(jìn)行數(shù)字控制。由于梯形網(wǎng)絡(luò)的切換噪聲,使用乘法DAC(MDAC)是有問題的。這種噪聲來自位開關(guān),當(dāng)它們打開和關(guān)閉時將電荷注入信號。音頻工程師將這種噪音稱為“拉鏈噪音

2019-08-12 16:35:02 6616

6616

在基本的PCB設(shè)計時卻容易忽略最熟悉的最簡單的地方,而導(dǎo)致錯誤出現(xiàn)。

2019-08-28 10:03:36 988

988 本文檔的主要內(nèi)容詳細(xì)介紹的是兩個運(yùn)動員賽跑計時的秒表項目的verilog設(shè)計資料免費下載。

2020-08-04 17:02:18 17

17 使用的無線網(wǎng)橋越來越多,尤其是布線不方便。建筑環(huán)境不好的地方被廣泛使用。

2020-08-18 16:08:53 2847

2847

通用版 Red Hat Marketplace 旨在幫助企業(yè)在運(yùn)行 Red Hat OpenShift 的混合云環(huán)境中,更方便地從各供應(yīng)商處購買、部署和管理企業(yè)軟件。 Red Hat

2020-09-23 15:24:55 2138

2138 在Verilog中何時用wire,何時用reg? Verilog HDL中的變量可以定義為wire型和reg型,這兩種類型的變量在定義時要設(shè)置位寬,缺省為1位,變量的每一位可以取0、1、x、z,其中

2020-09-28 11:26:13 15345

15345

出口限制,公司和美國相關(guān)政府部門等進(jìn)行了積極交流與溝通,對于具體細(xì)節(jié),公司不方便透露。 11月12日的財報會議上,中芯國際董事長周子學(xué)在業(yè)績會上表示,當(dāng)前國際形勢日趨復(fù)雜,公司合法合規(guī)經(jīng)營,對美國的出口管制表示遺憾,對

2020-11-27 16:44:08 2446

2446 日前有消息稱比亞迪電子和深科技將為榮耀代工生產(chǎn)。據(jù)科創(chuàng)板日報報道,深科技方面作出了回應(yīng)。 深科技董秘辦人士表示,不方便回應(yīng)榮耀代工,公司原來就有手機(jī)制造業(yè)務(wù),后者一直是OEM業(yè)務(wù)的一部分,OEM業(yè)務(wù)

2021-01-20 18:07:54 2472

2472 本教程介紹Altera的QuartusII軟件如何處理基于Verilog硬件描述語言的設(shè)計中的計時問題。它討論了各種定時參數(shù),并解釋了用戶如何設(shè)置特定的定時約束。

2021-01-27 15:52:00 37

37 Verilog 黃金參考指南并不是要代替IEEE 的標(biāo)準(zhǔn)Verilog 語言參考手冊它不像IEEE 的標(biāo)準(zhǔn)手冊提供了Verilog 完整正式的描述相反黃金參考指南以一種方便的參考格式解答了在Verilog 的實踐應(yīng)用過程中經(jīng)常遇到的問題

2021-02-02 16:19:00 0

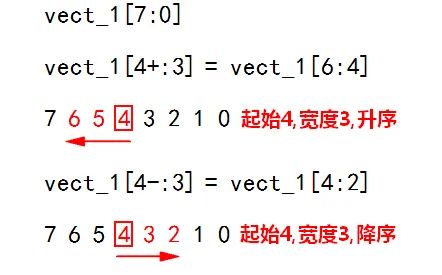

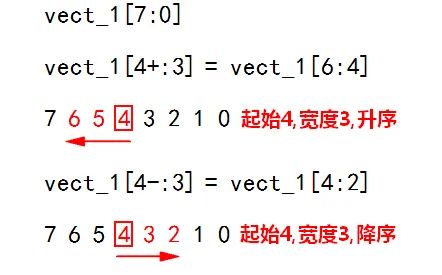

0 Verilog比較方便的一個特點就是數(shù)據(jù)的截取和拼接功能了,截取使用方括號[],拼接使用大括號{}。

2021-03-21 10:01:47 3944

3944

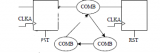

一、邏輯設(shè)計 (1)組合邏輯設(shè)計 下面是一些用Verilog進(jìn)行組合邏輯設(shè)計時的一些注意事項: ①組合邏輯可以得到兩種常用的RTL 級描述方式。第一種是always 模塊的觸發(fā)事件為電平敏感信號列表

2021-06-23 17:45:10 6056

6056

通過Verilog在SRAM讀寫程序源代碼

2021-06-29 09:26:15 9

9 ,SDRAM的控制邏輯復(fù)雜,使用很不方便。 為了解決這個矛盾,需要設(shè)計專用的SDRAM控制器,使系統(tǒng)用戶象使用SRAM一樣方便的使用SDRAM是十分必要的。考慮到控制器的通用性,本文提出了一種通用的SDRAM控制器的 Verilog設(shè)計,并給出了實現(xiàn)結(jié)果。 1 SDRAM的工作原理

2021-06-30 09:16:47 3420

3420

的完整 Verilog 代碼 。 在這個FPGA Verilog項目中,一些簡單的處理操作都是在Verilog中實現(xiàn)的,比如反相、亮度控制和閾值操作。圖像處理操作由“parameter.v”文件選擇

2021-09-23 16:17:07 5361

5361 阻塞賦值,但從字面意思來看,阻塞就是執(zhí)行的時候在某個地方卡住了,等這個操作執(zhí)行完在繼續(xù)執(zhí)行下面的語句,而非阻塞就是不管執(zhí)行完沒有,我不管執(zhí)行的結(jié)果是什么,反正我繼續(xù)下面的事情。而Verilog中的阻塞賦值與非阻塞賦值正好也是這個意思,通過執(zhí)行一個例子

2021-12-02 18:24:36 7318

7318

Verilog HDL入門教程-Verilog HDL的基本語法

2022-01-07 09:23:42 189

189 電子計時器是一種新型的電子讀數(shù)工具,有時候又叫做秒表。在日常生活工作學(xué)習(xí)中,能夠非常有效地幫助我們更好的進(jìn)行時間管理。通過電子計時器來記錄運(yùn)動員的數(shù)據(jù)也十分方便,特別是在各種田徑賽場,電子計時器能夠

2022-05-19 17:10:25 11000

11000 可能您像我一樣,在設(shè)計過程中曾經(jīng)經(jīng)歷過大量的工程設(shè)計審查,無論是在項目的前端還是在制造的后端,總有很多遍對每個環(huán)節(jié)進(jìn)行核查。進(jìn)行工程設(shè)計審查是為了完成多個目標(biāo),那是因為現(xiàn)在的工程團(tuán)隊都是采用基于系統(tǒng)的方法進(jìn)行設(shè)計和生產(chǎn),電子設(shè)計團(tuán)隊需要審查的不僅僅是 PCB 布局和 BOM。

2022-12-09 09:42:07 1505

1505 Verilog-2005中有3個generate 語句可以用來很方便地實現(xiàn)重復(fù)賦值和例化(generate for)或根據(jù)條件選擇性地進(jìn)行編譯(generate if和generate case)等功能。接下來就一起看下這3個語句的應(yīng)用場景和應(yīng)用方法吧。

2022-12-28 15:21:43 3954

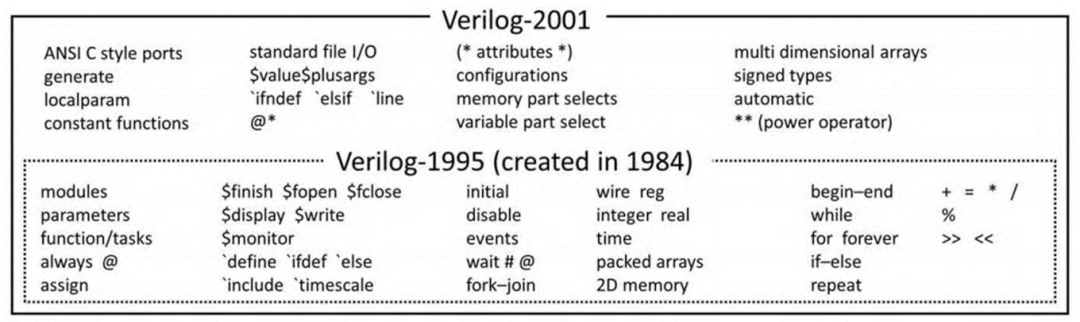

3954 Verilog始于20世紀(jì)80年代初,是一家名為Gateway Design Automation的公司的專有硬件描述語言(HDL)。最初的Verilog HDL的主要作者是Phil Moorby。

2023-04-27 09:57:42 1444

1444

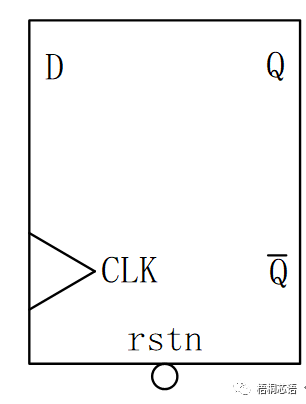

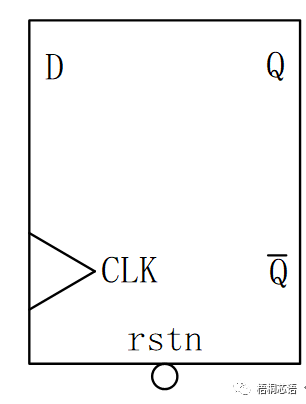

剛接觸數(shù)字集成電路設(shè)計,特別是Verilog HDL語言的同學(xué),往往不理解什么時候變量需要設(shè)置為wire型,什么時候需要設(shè)置成reg型。

2023-07-13 15:53:26 1962

1962

之前在使用Verilog做FPGA項目中、以及其他一些不同的場合下,零散的寫過一些練手性質(zhì)的testbench文件,開始幾次寫的時候,每次都會因為一些基本的東西沒記住、寫的很不熟練,后面寫的時候稍微

2023-08-01 12:44:27 5757

5757

對微小信號進(jìn)行放大的時候有什么要注意的地方?在器件選擇和布局布線上有什么要考慮的? 微小信號放大是一種常見的電子設(shè)計技術(shù),在各種應(yīng)用中廣泛使用。這種技術(shù)通常用于檢測和放大傳感器、檢測儀器、接收無線電

2023-11-09 10:02:16 1406

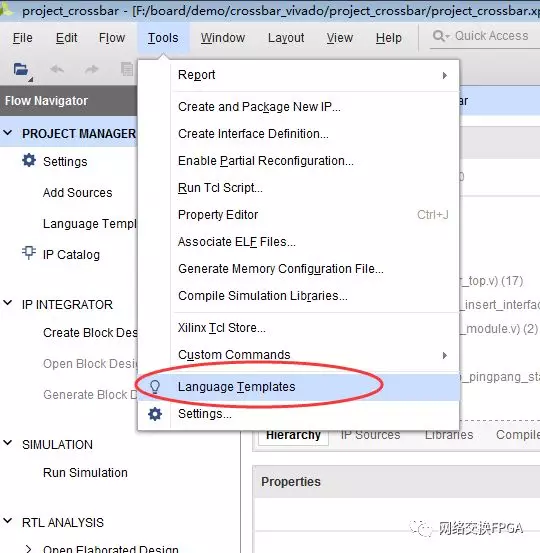

1406 相信大家寫verilog代碼的時候,都會用到notepad++,大家也知道notepad++可以和vivado關(guān)聯(lián)使用,這樣寫起工程代碼的時候,調(diào)試很方便。

2023-12-21 09:41:35 4151

4151

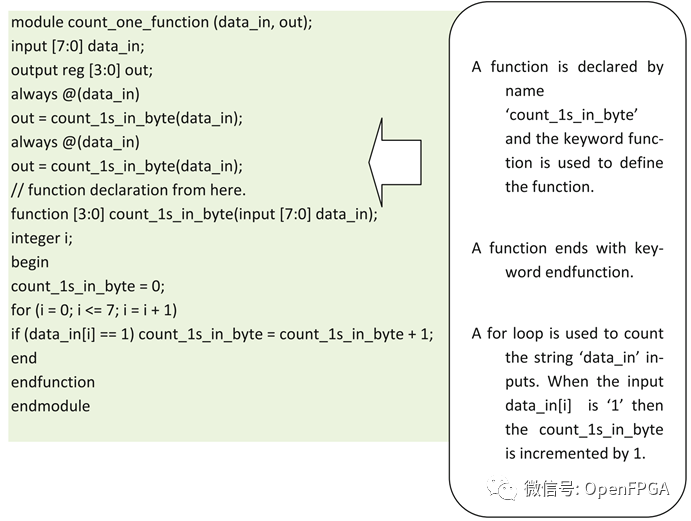

Verilog 是一種硬件描述語言 (HDL),主要用于描述數(shù)字電子電路的行為和結(jié)構(gòu)。在 Verilog 中,函數(shù) (Function) 是一種用于執(zhí)行特定任務(wù)并返回一個值的可重用代碼塊。函數(shù)在

2024-02-22 15:49:27 8456

8456 。 1.2 為什么要調(diào)用其他模塊? 在復(fù)雜的設(shè)計中,我們通常需要實現(xiàn)各種不同的功能,并且這些功能往往可以通過不同的模塊來實現(xiàn)。通過調(diào)用其他模塊,我們可以將問題分解為更小的子問題,并且可以更方便地實現(xiàn)和維護(hù)我們的設(shè)計。 1.3 調(diào)用模塊的基本語法

2024-02-22 15:56:25 8556

8556 :由于其類似于 C 語言的語法,Verilog 代碼通常更易于閱讀和維護(hù),尤其是在處理復(fù)雜邏輯時。 VHDL :VHDL 的正式性和豐富

2024-12-17 09:44:44 2874

2874 Verilog與ASIC設(shè)計的關(guān)系 Verilog作為一種硬件描述語言(HDL),在ASIC設(shè)計中扮演著至關(guān)重要的角色。ASIC(Application Specific Integrated

2024-12-17 09:52:26 1542

1542 在現(xiàn)代電子設(shè)計自動化(EDA)領(lǐng)域,Verilog作為一種硬件描述語言,已經(jīng)成為數(shù)字電路設(shè)計和驗證的標(biāo)準(zhǔn)工具。它允許設(shè)計師以高級抽象的方式定義電路的行為和結(jié)構(gòu),從而簡化了從概念到硅片的整個設(shè)計流程

2024-12-17 09:53:28 1689

1689

電子發(fā)燒友App

電子發(fā)燒友App

評論