大咖簡介: 胡振波是上海交大本科研究生,具有超過10年處理器研發經驗。 在Mavell和Synopsys等知名企業領導多款高性能和低功耗處理器研發工作。 是國內RISC-V社區領袖,以及蜂鳥E203

2020-11-10 15:17:21 3036

3036 胡振波老師的E203處理器讓小編受益匪淺,十分感激!E203 CPU的設計非常經典且精簡,大量邏輯復用,追求極低功耗、極小面積。

2022-09-27 10:21:19 1788

1788 電子發燒友網報道(文/吳子鵬)近日,全志科技在回答投資者問詢時表示,公司已經在多個型號的處理器芯片上應用了RISC-V內核,相關項目進展順利。公司將圍繞智慧城市、智能汽車、智能商顯、智能家電、智能

2022-08-09 08:16:00 4813

4813 電子發燒友網報道(文/吳子鵬)根據外媒的最新報道,半導體IP大廠Imagination Technology已經停止了RISC-V處理器內核的開發,轉而更加專注于其核心的GPU和AI產品

2025-01-10 00:15:00 3362

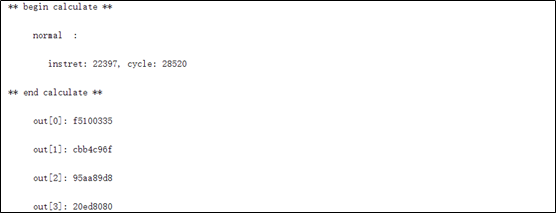

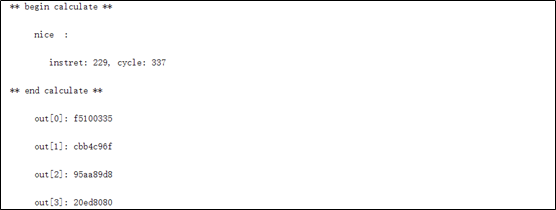

3362 蜂鳥E203原有的軟核處理器是利用booth 4 算法從低位到高位迭代生成一個一個部分積,然后與之前的部分和送至數據通路加和生成下一個部分和。依次迭代17個時鐘周期可以得到最終的乘法器結果,這種

2025-10-21 14:56:29

《在手把手教你RISC-V CPU上》

3.F拓展的軟件實現

為實現對蜂鳥E203的F拓展,筆者未采用蜂鳥E203中遺存的FPU端口,選擇NICE接口完成蜂鳥E203浮點運算指令拓展,在NICE端口

2025-10-20 09:23:24

本文將分享我們團隊提高E203軟核主頻的辦法。

查閱芯來科技官方出版的《手把手教你設計CPU——RISC-V處理器篇》教材,我們發現,原本設計的E203主時鐘域應該是100MHZ

2025-10-29 06:19:19

具體方法

這篇分享中RISC-V 蜂鳥E203平臺是在Arty A7 100T上進行的搭建,ddr 200t的板子上是有2塊qspi flash的,所有FPGA的bitstream燒錄在了

2025-10-28 07:47:08

具體方法

E203的源碼請參考鏈接:

https://github.com/riscv-mcu/e203_hbirdv2

E203的overview鏈接:

https

2025-10-28 06:26:05

,一步到位喲。overview就是對E203的整個平臺做了整體介紹,有什么樣的外設,如何燒錄等等。最主要看第四節的交叉編譯環境的安裝,安裝RISC-V GNU toolchain、Nuclei

2025-10-28 06:16:38

,可以被任何支持RISC-V ISR的處理器解釋執行。

需要注意,B擴展是與基本RV32I/RV64I RISC-V指令集完全兼容的。因此,使用支持B擴展的芯片可以同時享受到原始架構指令集以及B擴展的優勢

2025-10-21 13:01:45

RISC-V處理器是開源的,那開發環境需要廠商自己開發還是沿用傳統的開發環境呢?比如keil

2024-01-13 19:18:35

RISC-V嵌入式開發準備篇2:嵌入式開發的特點介紹隨著國內第一本RISC-V中文書籍《手把手教你設計CPU——RISC-V處理器篇》 正式上市,越來越多的愛好者開始使用開源的蜂鳥E203

2021-11-08 08:33:47

本期文章目錄一個小型RISC-V開源處理器核介紹!#SOC#FPGA#RISC-V點擊閱讀數字積木從零開始寫RISC-V處理器(超詳細)#RISC-V點擊閱讀數字積木為什么說模擬工程...

2021-07-23 09:42:00

RISC-V是什么?有哪些特點?如何去設計RISC-V處理器?

2021-06-18 09:24:03

需要用到UART中斷,即使能FIFO中數據與閾值比較后產生的中斷,這時就會設計到UART中斷閾值的設置。在E203 SoC的代碼里我們可以看到,中斷閾值主要是由UART模塊里面的trigger_level_n

2025-10-30 06:42:08

的問題。

通過閱讀SoC工程RTL代碼可以發現,e203_subsys_perips.v,蜂鳥在私有外設總線接口(PPI)上,給我們預留了一定的地址空間(Reserved)。

我們知道,E203采用

2025-10-30 07:51:55

蜂鳥E203的GPIO好像沒有設置推挽輸出或者開漏輸出的寄存器,那GPIO的輸出模式只有一種嗎?還可以用來模擬SPI IIC等通信協議嗎

2023-08-16 07:22:34

蜂鳥E203 mret/dret/wfi指令代表什么意思,我看手冊上沒有這三條指令

2025-11-10 07:31:20

對蜂鳥E203內核進行優化可以考慮以下幾個方面:

編譯器優化:使用適合蜂鳥E203的編譯器選項和指令集,優化編譯器的選項和參數,開啟對硬件的特定支持,比如使用-O2等優化選項,以提高代碼執行效率

2025-10-21 07:55:16

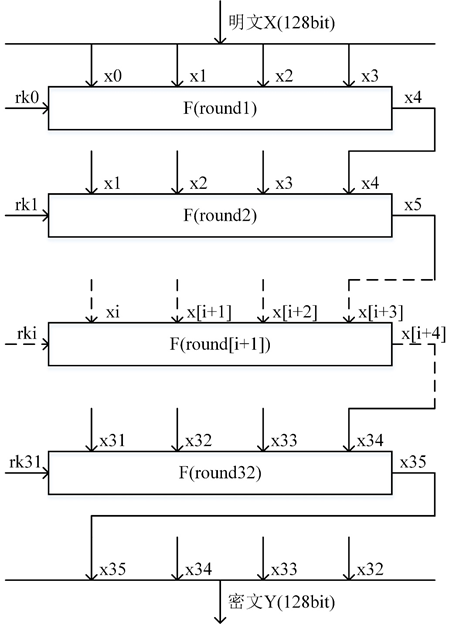

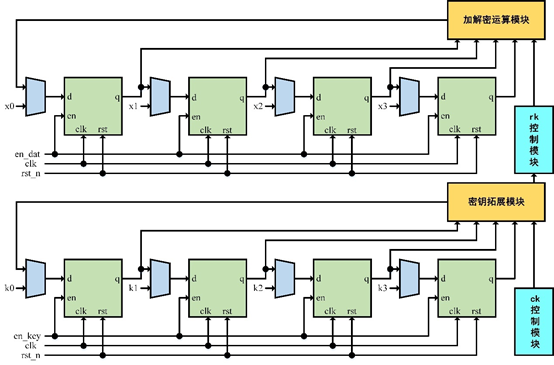

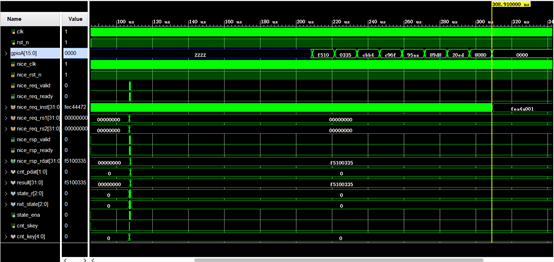

蜂鳥E203為了節約資源,乘法運算采用循環移位方式計算最終結果,這樣的乘法器需要經過較多時鐘周期來處理數據,導致處理數據效率較低。為了提高計算效率,這里分享一種基于流水線思想的乘法器,即采用多個

2025-10-22 07:28:51

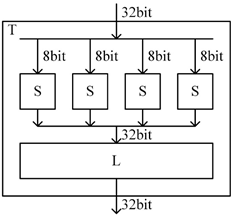

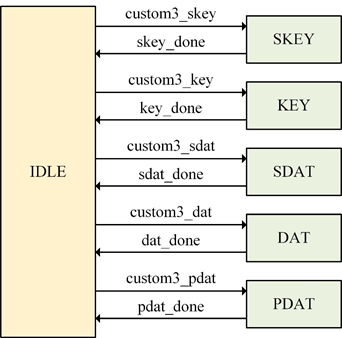

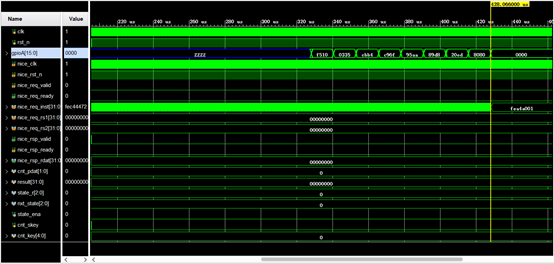

,各種不同的組合代表了不同的指令類型,我們用到了預定義的custom-3指令擴展協處理器指令,因此指令的opcode為7’b1111011。

由于蜂鳥E203處理器核基于Custom指令進行協

2025-10-24 07:23:37

周期。

總結

本文介紹的內容是為了完成基礎功能:對蜂鳥E203 RISC-V內核的微架構實現進行一定優化,在添加F拓展的過程中的一些記錄。

2025-10-24 08:57:20

關于蜂鳥E203的浮點指令集拓展(F拓展)

Whetstone中有很多浮點數運算,而蜂鳥e203中沒有硬件支持,是通過將浮點數轉化成整型數來計算,效率大大降低。

為了提高Whetstone跑分

2025-10-24 11:51:39

1.蜂鳥E203的原有分支預測

蜂鳥E203處理器為了能夠連續不斷的取指令,需要在每個時鐘周期都能生成一條待取的指令。因此,在取指令的階段,IFU單元模塊進行了簡單的譯碼處理,用以判別

2025-10-24 07:45:54

在合作開發的時候,本人負責SD卡的讀寫模塊,然而在完成RTL級編程之后,得到的.v后綴的文件,不知道怎么掛上蜂鳥e203的soc上。求求指點一下,我應該怎么把自己的.v后綴的文件加入soc。是掛總線嗎?那要用哪個地址呢?

2023-08-16 06:44:35

新人嘗試在蜂鳥e203soc上進行開發,試圖讀取sd卡,但sd卡讀取有較復雜的規則,我應該將sd卡掛在soc的spi端口上,然后在芯來sdk上使用c語言內嵌匯編完成控制,還是說我能自行寫一個簡化操作的模塊然后掛在總線上?如果是后者,由于總線上好像沒有多余的端口,我是否要添加很多代碼呢?

2023-08-16 06:51:25

求助蜂鳥e203處理器開源代碼中惡的Makefile編譯腳本和測試腳本怎么修改?有沒有大佬指點一下,萬分感謝

2023-08-12 06:52:25

內容:蜂鳥e203在虛擬機unbuntu上面驗證時報錯的可能原因

現象:

解決措施:

蜂鳥e203在虛擬機unbuntu上面驗證時不要重復輸入命令:

make install

make compile SIM=iverilog

只需輸入一遍

2025-10-24 08:27:17

1.蜂鳥e203的uart為什么沒有使能寄存器?按照手冊設置了所有寄存器后,uart完全不工作。使用Modelsim仿真后發現,uart的PSEL和PENABLE信號一直是低電平狀態。

2.官方

2023-08-12 07:32:41

蜂鳥e203有嘗試ram直接編譯代碼,求指導,怎么將.c文件生成ram可直接讀入的文件,然后在soc.v的文件中在哪修改ram的讀入,有試過的大神請指導一下,萬分感謝

2023-08-12 07:49:09

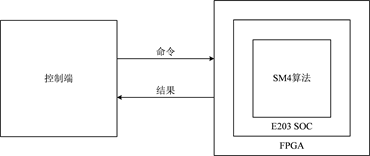

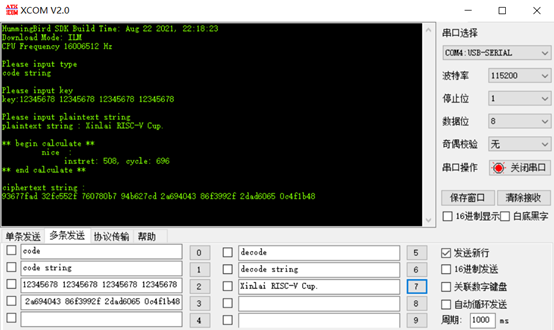

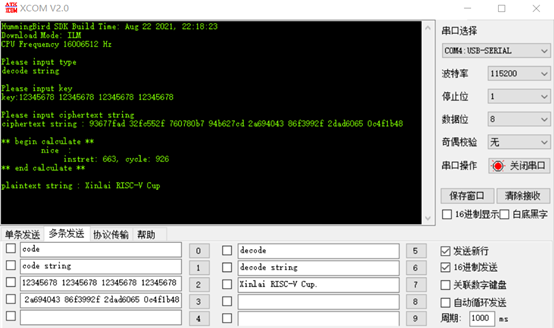

本設計首先根據MD5協處理器的功能設計MD5算法IP核,軟件部分使用串口程序助手進行64位加解密結果的輸出,E203內核根據地址取出對應的數據,使用相關的指令進行傳輸顯示。通過NICE接口將MD5協

2025-10-30 07:54:24

本團隊本次分享內容為NucleiStudio基于一代蜂鳥E203的工程創建。

1.下載NucleiStudio;

2.啟動IDE;——啟動后會指定工作目錄,選定后直接Lunch;

3.新建C

2025-10-29 06:08:39

位 FPU,以及兩顆來自美光的 16GB HBM2e 內存。處理器的內核通過中介層實現互連,雙塊 CPU 可提供 0.75 FP64 TFLOPS 的性能和 6 FP8 TFLOPS 算力。那么Occamy RISC-V 前景如何呢?

2023-05-13 08:44:36

在fpga嵌入e203內核實現以太網,開發板有PHY芯片LAN8720A,怎么搭建soc,如何使用總線,實現通信功能?

2025-11-10 06:54:38

作為大中專院校師生學習RISC-V處理器設計(使用Verilog語言)的教學或自學案例。蜂鳥E200主要面向極低功耗與極小面積的場景而設計,非常適合于替代傳統的8051內核或者Cortex-M系列內核應用于

2021-08-02 13:47:42

作為大中專院校師生學習RISC-V處理器設計(使用Verilog語言)的教學或自學案例。蜂鳥E200主要面向極低功耗與極小面積的場景而設計,非常適合于替代傳統的8051內核或者Cortex-M系列內核應用于

2021-08-25 14:31:07

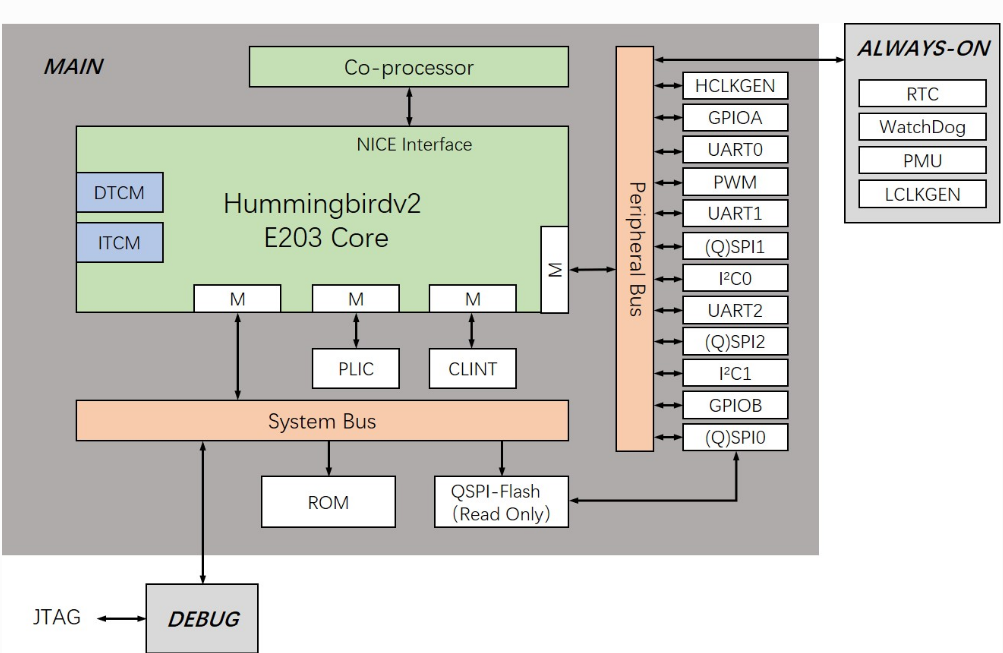

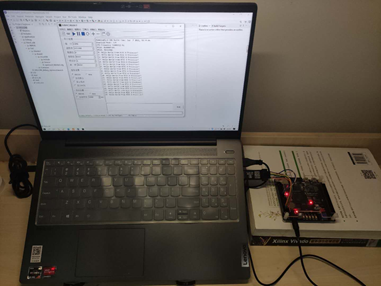

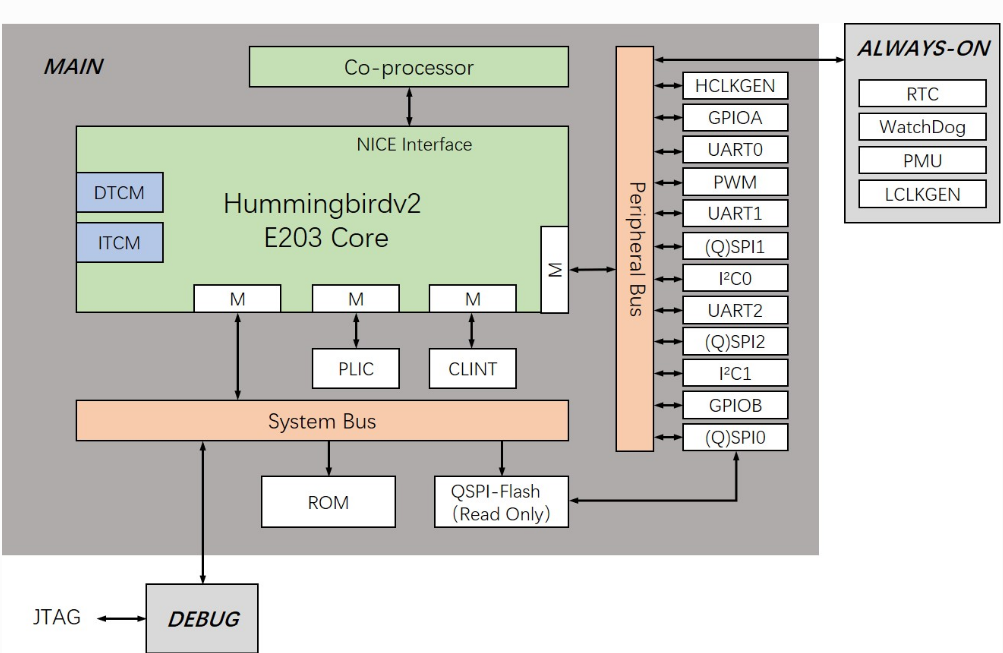

予以介紹。完整的 FPGA 開發板原型(包括 FPGA 開發板和MCU調試器)如下圖所示:蜂鳥E203開源SoC對于一個處理器核,還需要配套的 SoC 才能具備完整的功能。蜂鳥 E203 內核不僅僅

2022-07-26 22:00:29

修改蜂鳥E203 v2內核源碼后,測試“hello world”程序,vivado仿真可以順利通過,再輸出界面打印出“hello world”字樣,但上板后出現問題,hello world

2024-01-10 06:12:46

E203的SOC的模塊圖中的這個模塊是FLASH的控制器嗎?

如果我想完成FLASH的讀寫控制的話,在SOC的代碼層面(.v文件)該如何實現波形仿真呢?

2023-08-11 12:38:55

存在三種不同的商業模式,分析圖3第一行,開放免費的指令集(RISC-V)包含了三種模式的微架構設計[5]:開源模式,Berkeley的Rocket Chip、劍橋大學的lowRISC、蜂鳥E203等

2020-06-22 16:47:55

由于Vivado中Block Design的友好的ui界面以及豐富的IP資源,在FPGA上實現SoC大多會采用Block Design進行設計與實現。對于基于蜂鳥e203內核的SoC設計,為了使其

2025-10-30 07:35:52

本人發現還有許多朋友在尋找如何仿真蜂鳥E203的方法,并且目前論壇內還沒出現過一代蜂鳥E203(基于hbirdkit和nucleikit)仿真教程,由于本人使用的板子便是hbirdkit,因此特來

2025-10-31 06:14:34

讀者反饋,為痞子衡提供了不少遺漏廠商信息,今天痞子衡就為大家再次盤點那些發布過RISC-V MCU產品(不一定已量產)的廠商,本次又新增了7家廠商。一、芯來科技 開源蜂鳥E203蜂鳥E203處理器由芯來

2022-03-25 17:33:21

內容:在Linux ubuntu上使用riscv-formal工具驗證蜂鳥E203 SoC的正確性

步驟:

1、下載和安裝riscv-formal工具:

bash復制代碼

git clone

2025-10-24 07:52:17

如題,我們嘗試在Nexys Video上移植開源蜂鳥E203 Soc.但是開發板上flash的型號與官方板不同,Nexys Video上的flash型號是S25FL256,與官方的容量不同,請問移植時是否兼容呢?需要在工程或者NucleiStudio中修改哪些地方呢

2023-08-12 07:41:51

的默認證書就可以正常使用了。 首先我們需要把FPGA變成一塊RISC-V的開發板,因此需要燒錄蜂鳥E203的bitstream,接下來就是把它當做單片機一樣使用,上傳固件了。 下載源碼 為了方便

2022-09-16 16:15:39

在Ubuntu 虛擬機中使用verilator對蜂鳥E203內核進行仿真

蜂鳥E203是一款基于RISC-V架構的嵌入式處理器核,在開發中需要進行仿真操作來驗證其功能性。本教程將介紹如何利用

2025-10-27 08:22:44

I2S總線外設

對于I2S總線,我們需要將其掛在APB總線上,由于蜂鳥E203內核是采用自研的ICB總線協議。因此需要通過ICB2APB總線橋,將兩個協議進行連通。

I2S音頻數據流

2025-10-28 07:28:31

指令蜂鳥E203借鑒了開源RISC-V處理器Rocket Core的協處理器接口RoCC,為了與原始接口進行區分,命名為EAI(Extension Accelerator Interface)接口

2025-10-28 06:18:41

擴展到某些特定領域可以非常明顯地提高能效比。NICE協處理器(Nuclei Instruction Co-unitExtension,蜂鳥內核指令協處理器擴展機制)是一個獨立于蜂鳥E203內核的一塊運算

2025-10-21 14:35:54

非常明顯地提高能效比。NICE協處理器(Nuclei Instruction Co-unit Extension,蜂鳥內核指令協處理器擴展機制)是一個獨立于蜂鳥E203內核的一塊運算單元[24],它能

2025-10-21 10:39:24

1.介紹

蜂鳥e203中的存儲功能極為有限,對一些大規模存儲運算而言,其難以滿足要求。故我們可以將板子中的ddr存儲資源利用起來,其可通過內核中的icb轉axi總線與vivado中的mig

2025-10-23 06:22:22

蜂鳥E203是一款基于RISC-V架構的微處理器,其指令集包含RV32I的基本指令集,RV32M的乘法擴展指令集,以及一些常用的定點指令和控制指令。如果需要擴展其指令集,可以考慮使用RISC-V的可

2025-10-21 09:38:47

軟件控制地址寄存器讀寫操作

軟件部分的主要作用是給蜂鳥E203處理器核寫指令,讓其能夠向硬件設計中相對應的地址寄存器進行寫數據和讀數據操作,在hbird-e-sdk的板級支持包下,需要添加

2025-10-30 06:48:06

我們為蜂鳥e203新添加了硬件斷點的功能。添加Trigger Module,并實現包括tselect,tdata1~7,tcontrol,tinfo在內的寄存器,在flash模式下可以在IDE中直

2025-10-23 07:11:20

硬件配置地址寄存器

由蜂鳥E203 SoC的總線地址分配表可知,私有外設總線接口的總區間為 0x1000_0000~0x1FFF_FFFF,而真正用到的只有0x1000_0000

2025-10-30 07:52:26

大概花了三天時間完成了蜂鳥E203 SOC在zynq7100 FPGA的移植工作,并完成了hello world程序的在線debug調試。

蜂鳥E203的移植在網上有大把的demo,其中bit文件

2025-10-28 07:38:36

。1. 蜂鳥E203首先我們需要把FPGA變成一塊RISC-V的開發板,因此需要燒錄蜂鳥E203的bitstream,接下來就是把它當做單片機一樣使用,上傳固件了。1.1 下載源碼為了方便,我把fpga

2022-04-01 11:48:28

蜂鳥E203是一款基于RISC-V指令集的多核處理器,內置了乘法和除法運算單元,這些運算單元的性能直接影響到整個處理器的性能表現。因此,優化乘除法器是提高整個處理器性能的重要手段之一。

一、原理介紹

2025-10-24 06:47:29

,并涌現了眾多開源處理器及SoC采用RISC-V架構,這些處理器既有標量處理器,也有超標量處理器,既有單核處理器,也有多核處理器,本文接下來將簡單介紹RISC-V架構的基本設計,隨后將詳細描述目前采用

2020-07-27 18:09:27

你們好!請問一下我將蜂鳥E203的內核移植到fpga之后該怎么進行二次開發呢?比如我想點亮板子上的led?驅動攝像頭進行圖像識別?這些該如何進行呢?蜂鳥有類似freedom studio這樣的嵌入式開發平臺嗎?

2025-11-10 07:09:56

RISC-V 處理器現狀的。一、關于 RISC-V 和開源 RISC-V 內核蜂鳥 E203RISC-V 作為一個全新的指令集架構,自 2010 年在伯克利大學誕生以來倍受關注。2015 年成立基金會

2020-07-27 17:50:25

1.簡述

這里就不詳細介紹risc-v和蜂鳥e203,大家應該都比較了解了。蜂鳥e203工程比較完善,也有一本書介紹,講解還是非常詳細的,如果以后想從事數字IC或者想學習risc-v,蜂鳥e203

2025-10-31 08:07:44

1.簡述

經過不懈的努力,終于成功運行hello word程序,這是一個極低成本的學習方案,感興趣繼續往下看。

2.準備

修改e200工程,這部分可以參考:開源RISC-V處理器(蜂鳥

2025-10-31 06:04:21

1.簡述

首先感謝芯來開源了蜂鳥E203 risc-v處理器,提供了比較完整的工程環境、配套的軟硬件。但是配套的FPGA板卡實在太貴,對于自費學習的來說是不小的學習成本,而且我也認為完備環境

2025-10-31 08:46:40

開源的蜂鳥E203可以直接用來流片嗎

2023-08-12 08:11:15

想請問怎么設置蜂鳥E203 soc外設的可配置寄存器讀寫屬性?可讀可寫、只寫、只讀三種模式具體怎么設置呢?目前是默認情況,新添加的外設寄存器寫不進去數據,讀返回為0

2024-01-10 06:24:02

想請問怎么設置蜂鳥E203 soc外設的可配置寄存器讀寫屬性?可讀可寫、只寫、只讀三種模式具體怎么設置呢?目前是默認情況,新添加的外設寄存器寫不進去數據,讀返回為0

2024-01-15 08:08:07

請問這種問題應該如何解決呢?無法下載程序到蜂鳥E203的SoC上

2023-08-12 07:08:49

蜂鳥E203 e203_ifu_ifetch.v模塊中,assign ir_valid_set= ifu_rsp_hsked & (~pipe_flush_req_real

2023-08-12 06:02:04

首先講一下我的操作過程吧。

首先,我下載了開源的蜂鳥E203處理器,新建了一個自己的vivado工程,并將rtl目錄里的所有.v文件和fpga目錄里的一個system.v文件加入到我的工程里,并添加

2023-08-16 08:23:26

請問E203 Core和 NICE協處理器的主頻各是多少?

2023-08-12 08:06:09

我看說E203支持自定義擴展,有EAI接口,可是為什么我只在LSU中找到了跟讀取存儲器有關的EAI接口呢,別的比如eai_req_instr沒有找到,請問誰知道在哪嗎,或者說如果要加可擴展協處理器的話,這些接口要自己加嗎?

2025-11-10 07:41:36

請問 蜂鳥E203 支持硬件斷點嗎?

2023-08-16 06:38:22

請問蜂鳥E203的代碼可以做asic綜合嗎? 如果需要的話需要把那些文件加進去呢?是要把rtl文件里的 core,debug,fab,general,mems,periphs,soc,subsys

2023-08-16 07:09:47

芯來科技助力道生物聯發布基于RISC-V內核的TurMass?標準無線終端SoC芯片—TK8610。該芯片產品采用芯來科技RISC-V N200系列處理器內核。

2022-03-22 15:00:19

為了便于初學者能夠快速地學習RISC-V CPU設計和RISC-V嵌入式開發,蜂鳥E203開源MCU原型SoC定制了基于Xilinx FPGA的專用開發板和專用JTAG調試器。

2018-11-12 17:10:02 22352

22352 隨著這些年的發展,RISC-V的受重視程度與與日俱增。這主要因為它是免費的、靈活的,并且速度很快。這使RISC-V成為許多開發人員的安全便捷選擇。但是您會認為RISC-V是通用RISC處理器還是定制的隨心所欲處理器?

2020-11-17 16:11:56 4207

4207 為了便于初學者能夠快速地學習 RISC-V 嵌入式開發,蜂鳥 E203 開源 MCU 原型 SoC(在本文中將其簡稱為“MCU SoC”或者“SoC”)定制了基于 Xilinx FPGA 的專用

2021-03-23 10:00:28 41

41 芯來科技為方便客戶進行基于鴻蒙生態的RISC-V軟件開發,在Nuclei RISC-V 32位處理器上移植并適配了鴻蒙LiteOS-M內核。 目前該內核已可支持Nuclei Demo SoC

2021-04-09 15:20:01 5795

5795

RISC-V嵌入式開發準備篇2:嵌入式開發的特點介紹隨著國內第一本RISC-V中文書籍《手把手教你設計CPU——RISC-V處理器篇》 正式上市,越來越多的愛好者開始使用開源的蜂鳥E203

2021-11-03 14:06:02 53

53 該存儲庫托管開源 Hummingbirdv2 E203 RISC-V 處理器內核和 SoC 項目,由中國大陸領先的 RISC-V IP 和解決方案公司Nuclei System Technology

2022-03-17 16:52:43 11

11 展開新的合作,共同加速基于SiFive RISC-V處理器的SoC設計和驗證。基于該合作,雙方客戶可采用新思科技Fusion QuickStart設計實現套件(QIKs),以優化SiFive

2022-11-09 18:33:37 1646

1646 開源RISC-V Hummingbird E203(蜂鳥E203)的仿真工具是開源的iverilog,這里利用vcs+verdi仿真工具進行仿真;

2022-11-17 10:28:36 4147

4147 自RISC-V 架構誕生以來,市場上已有數十個版本的 RISC-V 內核和SoC芯片它們中的一部分是開源免費的,而商業公司開發的 RISC-V 處理器內核和平臺是需要商業授權的。

2023-03-21 17:43:14 1868

1868 HBird v2 E203是芯來的RISCV的開源(https://github.com/riscv-mcu/e203_hbirdv2)SoC項目,Apache 2.0 License 。主要功能如下框圖:

2023-05-05 15:33:57 1849

1849

RISC-V的開放性允許定制和擴展基于 RISC-V 內核的架構和微架構,以滿足特定需求。這種對設計自由的渴望也正在將驗證部分的職責轉移到不斷壯大的開發人員社群。然而,隨著越來越多的企業和開發人員轉型RISC-V,大家才發現處理器驗證絕非易事。

2023-07-10 09:42:08 1468

1468

電子發燒友App

電子發燒友App

評論