基于DSP+FPGA的實時視頻采集系統(tǒng)設(shè)計

0 引言

圖像是自然生物或人造物理的觀測系統(tǒng)對世界的記錄,是以物理為載體,以介質(zhì)來

2010-01-11 10:15:46 833

833 1.引言

本文針對紅外圖像處理系統(tǒng)的實時性要求,提出了基于DSP+FPGA+ASIC的圖像處理架構(gòu)。

隨著紅外焦

2010-07-22 15:18:50 1160

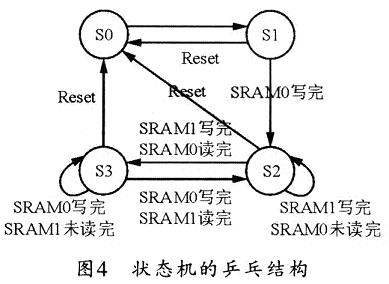

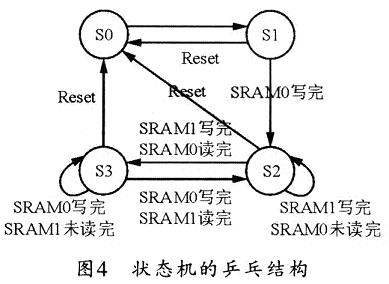

1160 為了改善實時圖像輸出質(zhì)量,研究基于SDI接口的增強(qiáng)顯示系統(tǒng)軟硬件設(shè)計.利用模塊化思想提出一個基于SDI接口輸出的硬件架構(gòu),以FPGA作為處理核心,通過2片SRAM的雙緩存結(jié)構(gòu)實現(xiàn)圖像的乒乓控制,使

2014-07-28 16:45:28 3741

3741

DSP+FPGA架構(gòu)的最大特點是結(jié)構(gòu)靈活、有較強(qiáng)的通用性、適合于模塊化設(shè)計,從而能夠提高算法效率,同時其開發(fā)周期短、系統(tǒng)易于維護(hù)和升級,適合于實時視頻圖像處理。

2015-02-03 15:20:47 1660

1660

基于DSP+FPGA的20路 50Msps AD 數(shù)據(jù)處理平臺1、板卡概述 該DSP+FPGA高速信號采集處理板由我公司自主研發(fā),包含一片TI DSP TMS320C6455和一片Xilinx

2014-06-24 14:01:53

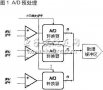

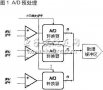

DSP+FPGA+AD控制系統(tǒng),FPGA負(fù)責(zé)AD7606的采集,將電機(jī)參數(shù)采集后,傳輸至DSP ,DSP將數(shù)據(jù)進(jìn)行變換后輸出PWM進(jìn)而控制電機(jī)的轉(zhuǎn)速。DSP采用TI公司的TMS320F28335

2016-07-18 16:59:22

DSP+FPGA架構(gòu)的最大特點是結(jié)構(gòu)靈活、有較強(qiáng)的通用性、適合于模塊化設(shè)計,從而能夠提高算法效率,同時其開發(fā)周期短、系統(tǒng)易于維護(hù)和升級,適合于實時視頻圖像處理,電機(jī)控制,數(shù)據(jù)采集。單DSP核心的系統(tǒng)

2016-09-24 10:41:18

來說,濾除噪聲、擴(kuò)展對比度、銳化以及色彩增強(qiáng)等處理能顯著提升視覺效果。這里設(shè)計一個基于FPGA的實時視頻圖像處理系統(tǒng),包含增強(qiáng)對比度擴(kuò)展和色飽和度兩種處理方法,相比于DSP和ASIC方案來說,FPGA在性能和靈活性方面具有絕對優(yōu)勢,應(yīng)用FPGA設(shè)計視頻通信系統(tǒng)更普遍。

2019-08-22 08:22:29

申請理由:TMS320C6748是TI公司推出的高速DSP,將其應(yīng)用于微光視頻圖像的實時處理,對于提高系統(tǒng)的實時性和采集具有十分重要的意義,同時也可以講更加復(fù)雜的算法加入其中,對于微光視頻圖像處理

2015-10-09 15:12:31

平臺。此平臺能充分發(fā)揮DSP的運(yùn)算速度,實現(xiàn)飛控算法。采用基于FPGA的雙RAM緩沖機(jī)制,能很好地解決異步串行數(shù)據(jù)實時同步數(shù)據(jù)處理問題,滿足飛控系統(tǒng)需求。

2019-06-26 07:29:55

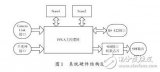

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進(jìn)行視頻處理的方案,實現(xiàn)視頻采集、處理到傳輸?shù)恼麄€過程。實時視頻圖像處理中,低層的預(yù)處理算法處理的數(shù)據(jù)量大,對處理速度要求高,但算法相對比較簡單,適合于用

2019-07-01 07:38:06

。FPGA采用Altera 公司的40nm Stratix IV 系列FPGA。通過SRIO協(xié)議,DSP可與FPGA的進(jìn)行高速通信。由于集成了DSP和FPGA各自優(yōu)點,HPS6678可在高速無線通信、多媒體系統(tǒng)、雷達(dá)及衛(wèi)星系統(tǒng)、醫(yī)療系統(tǒng)、高清圖像處理等多個領(lǐng)域中發(fā)揮重要的作用。

2019-09-24 08:29:12

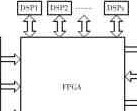

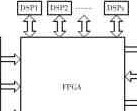

為解決高速數(shù)字圖像處理系統(tǒng)和實時性相沖突的要求,設(shè)計了以多DSP(數(shù)字信號處理器TMS320C6416)和現(xiàn)場可編程門陣列(FPGA)相結(jié)合的實時圖像處理系統(tǒng)。重點介紹了該系統(tǒng)的硬件資源選擇、基本組

2021-04-28 06:14:48

有限的不足,而且提高了監(jiān)控資源的利用率,降低了監(jiān)控成本。 1 系統(tǒng)硬件結(jié)構(gòu) 采用DSP+FPGA的硬件結(jié)構(gòu)方案,利用DSP和FPGA控制MAX4312選通所需要的視頻通道,從而達(dá)到在多路視頻通道間進(jìn)行切換的目的。系統(tǒng)結(jié)構(gòu)框圖如

2012-12-12 17:00:21

會受一定的影響。?本文所提出的基于DSP+FPGA的控制系統(tǒng)方案,利用FPGA的容量大、可編程實現(xiàn)很多功能,結(jié)合DSP具有高速的信息處理能力的特點,使得本控制系統(tǒng)非常簡潔,結(jié)構(gòu)靈活,通用性強(qiáng),系統(tǒng)也易于維護(hù)和擴(kuò)展。該方案基于軟件無線電的思想,是采用通用平臺的設(shè)計。?

2019-07-29 06:08:47

ASIC不夠靈活的缺點。與其他中小規(guī)模集成電路相比,其優(yōu)點主要在于它有很強(qiáng)的靈活性,即其內(nèi)部的具體邏輯功能可以根據(jù)需要配置,對電路的修改和維護(hù)很方便。DSP+FPGA結(jié)構(gòu)最大的特點是結(jié)構(gòu)靈活,有較強(qiáng)

2019-09-19 08:21:16

的重點是以DSP+FPGA為核心的視頻處理模塊的設(shè)計與實現(xiàn),可以完成多路視頻的切換選擇輸出控制和視頻縮放顯示的功能,同時具備通信控制等功能。

2019-06-20 06:34:25

FPGA一般用來控制整個系統(tǒng)的時序,本設(shè)計采用集成微處理器的FPGA,同時完成信號模擬和時序控制的功能,改變了以往信號處理DSP+FPGA中FPGA作為協(xié)處理器的模式[1-3]。整個設(shè)計僅需要具有嵌入

2019-07-15 06:48:33

為了實現(xiàn)—是彈武器瞄準(zhǔn)自動化,本文設(shè)計了基于DSP和FPGA的高速高精確度雙通道CCD圖像采集系統(tǒng),采用QUartuBn在AJtera的FPGA器件CYCLONEII上設(shè)計了CCD驅(qū)動時序電路,采用

2014-11-07 14:54:07

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進(jìn)行視頻處理的方案,實現(xiàn)視頻采集、處理到傳輸?shù)恼麄€過程。 實時視頻圖像處理中,低層的預(yù)處理算法處理的數(shù)據(jù)量大,對處理速度要求高,但算法相對比較簡單,適合于

2019-06-28 08:10:26

圖像數(shù)據(jù)處理的工作原理是什么?基于FPGA+DSP的圖像處理系統(tǒng)待如何去設(shè)計?

2021-06-02 06:54:28

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進(jìn)行視頻處理的方案,實現(xiàn)視頻采集、處理到傳輸?shù)恼麄€過程。 實時視頻圖像處理中,低層的預(yù)處理算法處理的數(shù)據(jù)量大,對處理速度要求高,但算法相對比較簡單,適合于

2019-06-19 06:12:05

今天給大俠帶來基于FPGA的實時圖像邊緣檢測系統(tǒng)設(shè)計,由于篇幅較長,分三篇。今天帶來第一篇,上篇,話不多說,上貨。

這里也超鏈接了中篇和下篇,方便各位大俠參考學(xué)習(xí)。基于FPGA的實時圖像邊緣檢測系統(tǒng)

2023-06-21 18:47:51

如何去實現(xiàn)對DSP系統(tǒng)的實時通信控制?

2021-06-04 07:00:33

在雷達(dá)信號處理、數(shù)字圖像處理等領(lǐng)域中,信號處理的實時性至關(guān)重要。由于FPGA芯片在大數(shù)據(jù)量的底層算法處理上的優(yōu)勢及DSP芯片在復(fù)雜算法處理上的優(yōu)勢,DSP+FPGA的實時信號處理系統(tǒng)的應(yīng)用越來越廣泛。那么,我們該怎么利用FPGA與ADSP TS201設(shè)計總線接口呢?

2019-08-09 06:56:11

隨著紅外探測技術(shù)迅猛的發(fā)展,當(dāng)今紅外實時圖像處理系統(tǒng)所要處理的數(shù)據(jù)量越來越大,速度要求也越來越快,利用目前主流的單DSP+ FPGA硬件架構(gòu)進(jìn)行較為復(fù)雜的圖像處理算法運(yùn)算時,有時就顯得有些捉襟見肘了

2019-11-08 06:31:26

大多選用這種算法。硬件實現(xiàn)上,最初是采用單片DSP芯片實現(xiàn),其原理為:圖像數(shù)據(jù)實時的傳輸給DSP,DSP接收完1塊數(shù)據(jù)后,再對整塊數(shù)據(jù)進(jìn)行增強(qiáng)處理,這樣勢必會造成時間的延遲,不能滿足精確制導(dǎo)武器系統(tǒng)實時性的要求。后來硬件結(jié)構(gòu)發(fā)展為采取DSP,FPGA芯片相結(jié)合的方式。

2019-08-16 07:10:22

隨著紅外探測技術(shù)迅猛的發(fā)展,當(dāng)今紅外實時圖像處理系統(tǒng)所要處理的數(shù)據(jù)量越來越大,速度要求也越來越快,利用目前主流的單DSP+ FPGA硬件架構(gòu)進(jìn)行較為復(fù)雜的圖像處理算法運(yùn)算時,有時就顯得有些捉襟見肘了

2019-08-23 08:29:27

FPGA是如何實現(xiàn)圖像的邊緣檢測的?怎樣去設(shè)計一種基于FPGA的實時圖像邊緣檢測系統(tǒng)?

2021-10-19 10:10:23

。而傳統(tǒng)的視頻增強(qiáng)技術(shù),例如直方圖均衡化在視頻序列的實時處理中效果并理想 。針對以上問題,提出一種交通監(jiān)控系統(tǒng),利用無線通信傳輸視頻信息,并在服務(wù)器端采用改進(jìn)單尺度 Retinex 算法獲得去霧后

2022-09-15 17:52:16

今天給大俠帶來基于FPGA的實時圖像邊緣檢測系統(tǒng)設(shè)計,由于篇幅較長,分三篇。今天帶來第二篇,中篇,話不多說,上貨。導(dǎo)讀隨著科學(xué)技術(shù)的高速發(fā)展,FPGA在系統(tǒng)結(jié)構(gòu)上為數(shù)字圖像處理帶來了新的契機(jī)。圖像中

2021-07-28 06:06:26

有朋友用DSP做出過圖像去霧嗎?最近在做這個遇到一些問題。有做過的朋友可以聯(lián)系我,能給我助攻的我可以支付一定的費(fèi)用~

2017-05-08 20:08:04

請教電力電子方向里dsp+FPGA架構(gòu)的案例

2018-12-10 18:32:58

本文設(shè)計了一種基于DSP+FPGA的實時視頻采集系統(tǒng)。

2021-06-07 06:39:43

摘要:為了改善實時圖像輸出質(zhì)量,研究基于SDI接口的增強(qiáng)顯示系統(tǒng)軟硬件設(shè)計。利用模塊化思想提出一個基于SDI接口輸出的硬件架構(gòu),以FPGA作為處理核心,通過2片SRAM的雙緩存結(jié)構(gòu)實現(xiàn)圖像的乒乓控制

2019-06-21 05:00:07

基于FPGA的小型微光視頻圖像增強(qiáng)處理系統(tǒng)Mini Low-level-light Video Image Enhancement Processing System Based on FPGA

摘要:為微光視頻圖像的實時增強(qiáng)設(shè)計了一套可應(yīng)用于空間狹小環(huán)境中

2009-01-11 12:11:18 34

34 為了實現(xiàn)夜間圖像的實時增強(qiáng),本文設(shè)計了基于DSP 的夜間圖像實時增強(qiáng)系統(tǒng),然后對Ardely 提出的DADPEQU 夜間圖像增強(qiáng)方法進(jìn)行了改進(jìn),提出了基于有效黑暗連通集的增強(qiáng)算法,取得

2009-07-07 13:07:23 14

14 簡要分析了DSP+FPGA系統(tǒng)的特點和優(yōu)越性,并且結(jié)合一個實時信號處理板的開發(fā),提出在此類系統(tǒng)中,FPGA設(shè)計的幾個關(guān)鍵問題,并且給出了詳實的分析和解決方案。

2009-09-02 17:44:44 24

24 為了在梳棉機(jī)上實現(xiàn)在線檢測監(jiān)控棉網(wǎng)中的棉結(jié)雜質(zhì),提出了一種基于DSP+FPGA架構(gòu)的硬件圖像處理在線檢測裝置,取代傳統(tǒng)的PC-Base檢測模式;采用符合梳棉機(jī)機(jī)械結(jié)構(gòu)的光源設(shè)計和控制

2010-02-24 14:06:05 18

18

提高顯示器的視覺效果,提出增強(qiáng)比度擴(kuò)展和色飽和度兩種算法,來對彩色圖像進(jìn)行增強(qiáng)處理,為滿足視頻信號的實時性要求,應(yīng)用FPGA構(gòu)造高速圖像處理系統(tǒng)。實驗結(jié)

2010-07-10 15:23:07 49

49 為了在梳棉機(jī)上實現(xiàn)在線檢測監(jiān)控棉網(wǎng)中的棉結(jié)雜質(zhì),提出了一種基于DSP+FPGA架構(gòu)的硬件圖像處理在線檢測裝置,取代傳統(tǒng)的PC-Base檢測模式;采用符合梳棉機(jī)機(jī)械結(jié)構(gòu)的光源設(shè)計和控制

2010-07-17 17:25:09 11

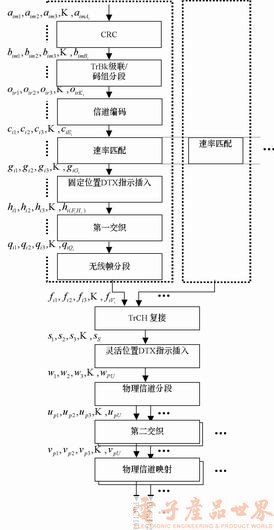

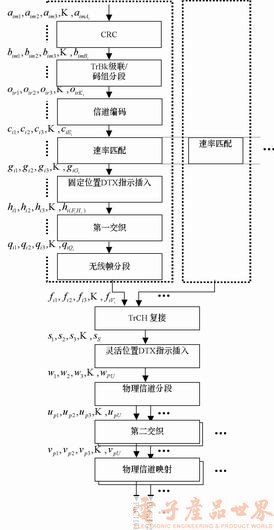

11 摘? 要: 本文在分析WCDMA系統(tǒng)基帶處理方案的基礎(chǔ)上,結(jié)合DSP和FPGA性能的比較,提出了一種在性能、靈活性和性價比上都比較理想的DSP+FPGA基帶發(fā)送的實現(xiàn)方案。 引言 隨

2006-03-11 13:29:42 1016

1016

基于DSP的實時圖像處理系統(tǒng)

引言

本文設(shè)計了基于TMS320C6000系列DSP的MPEG-4編碼器。將攝像頭獲取的圖像以MPEG-4標(biāo)準(zhǔn)進(jìn)行實時壓縮并通過VGA實時顯示,

2009-11-23 17:26:40 5344

5344

基于雙DSP的實時圖像處理系統(tǒng)

介紹了基于雙DSP的實時圖像處理系統(tǒng)。該系統(tǒng)通過兩片TMS320C6201作為系統(tǒng)計算中心,通過可重構(gòu)成的FPGA計算系統(tǒng)獲得系

2009-12-08 14:25:35 1215

1215

基于DSP+FPGA的實時視頻采集系統(tǒng)設(shè)計

0 引言

圖像是自然生物或人造物理的觀測系統(tǒng)對世界的記錄,是以物理為載體,以介質(zhì)來記錄信息的

2009-12-16 10:20:55 767

767

一種基于DSP+FPGA的控制系統(tǒng)方案設(shè)計

一、前言 ?

本文提到的控制系統(tǒng)控制通信設(shè)備的正常工作,是整個通信設(shè)備的重要組成部分。該控制系統(tǒng)要實現(xiàn)的功能

2009-12-22 17:44:41 1134

1134

基于DSP+FPGA+ASIC的實時圖像處理系統(tǒng)

1.引言

隨著紅外焦平面陣列技術(shù)的快速發(fā)展,紅外成像系統(tǒng)實現(xiàn)了高幀頻、高分辨率、高可靠性及微型化,在目標(biāo)跟蹤

2010-01-13 10:39:49 1356

1356

目前的衛(wèi)星遙感圖像壓縮系統(tǒng)硬件方案大多基于高性能可編程邏輯器件FPGA[2-4]。但這種方案整系統(tǒng)成本居高不下,且FPGA存在單粒子翻轉(zhuǎn)效應(yīng)。因此,筆者提出一種多DSP+FPGA的

2010-11-27 10:35:05 1909

1909

摘要:本文在分析TD-SCDMA系統(tǒng)基帶處理方案的基礎(chǔ)上,提出了一種在性能、靈活性和性價比方面都比較理想的DSP+FPGA基帶發(fā)送的實現(xiàn)方案。 關(guān)鍵詞:TD-SCDMA;基帶處理;DSP;FPGA

2011-03-02 01:38:41 60

60 DSP+FPGA混用設(shè)計 為了提高算法效率,實時處理圖像信息,本處理系統(tǒng)是基于DSP+FPGA混用結(jié)構(gòu)設(shè)計的。本系統(tǒng)要求DSP可以滿足算法控制結(jié)構(gòu)復(fù)雜、運(yùn)算速度高、尋址靈活、通信能力強(qiáng)大的

2011-09-08 11:55:37 2171

2171

針對目前國內(nèi)外大多數(shù)紅外圖像自動跟蹤系統(tǒng)采用DSP+FPGA 結(jié)構(gòu),系統(tǒng)存在設(shè)計電路復(fù)雜、成本高、實時性較差等缺點,開發(fā)出在單片現(xiàn)場可編程門陣列(FPGA)中實現(xiàn)以NiosⅡ軟核處理器

2011-09-13 17:29:54 77

77 針對兩軸電視經(jīng)緯儀動基座跟蹤目標(biāo)時,視軸無法隔離載體擾動造成圖像旋轉(zhuǎn)現(xiàn)象,提出一種基于數(shù)學(xué)平臺的電子消旋方法,采用捷聯(lián)式慣導(dǎo)+DSP+FPGA的硬件系統(tǒng)通過反向旋轉(zhuǎn)和雙線性插

2011-09-14 16:27:23 38

38 在雷達(dá)信號處理、數(shù)字圖像處理等領(lǐng)域中,信號處理的實時性至關(guān)重要。由于FPGA芯片在大數(shù)據(jù)量的底層算法處理上的優(yōu)勢及DSP芯片在復(fù)雜算法處理上的優(yōu)勢,DSP+FPGA的實時信號處理系統(tǒng)

2012-07-05 15:01:40 8211

8211

為了提高算法效率,實時處理圖像信息,本處理系統(tǒng)是基于DSP+FPGA混用結(jié)構(gòu)設(shè)計的。業(yè)務(wù)板以FPGA為處理核心,實現(xiàn)數(shù)字視頻信號的實時圖像處理,DSP實現(xiàn)了部分的圖像處理算法和FPGA的控

2012-10-16 11:02:47 4090

4090

基于DSP和FPGA技術(shù)的細(xì)胞圖像采集系統(tǒng)設(shè)計

2016-08-26 12:57:52 16

16 基于FPGADSP的實時圖像消旋系統(tǒng),下來看看

2016-08-26 12:58:19 4

4 基于FPGA的JPEG實時圖像編解碼系統(tǒng)

2016-08-29 16:05:01 16

16 基于FPGA的微光視頻圖像增強(qiáng)系統(tǒng),下來看看

2016-08-29 23:23:55 15

15 實時圖像增強(qiáng)算法改進(jìn)及FPGA實現(xiàn),下來看看

2016-09-17 07:28:24 15

15 基于FPGA+DSP實時圖像采集處理系統(tǒng)設(shè)計

2017-01-03 11:41:35 9

9 基于小波降噪度量的圖像去霧研究_黃鳳

2017-01-07 19:00:39 0

0 基于DSP的圖像去霧算法優(yōu)化方法_楊夢雯

2017-03-19 19:07:17 3

3 基于圖像增強(qiáng)方法,本文提出了一種使用亮度映射的圖像去霧快速算法。此算法通過調(diào)整室外多霧場景圖像的對比度,提高了霧中物體的辨識度。算法的復(fù)雜度低、處理延遲小,實時性高,利于FPGA的實現(xiàn)。實現(xiàn)時不需外存儲器,延時為ns級,并提供了強(qiáng)度調(diào)節(jié)接口,以適應(yīng)較廣的應(yīng)用環(huán)境。

2017-10-11 18:39:38 9

9 基于FPGA和DSP的高速圖像處理系統(tǒng)

2017-10-19 13:43:31 20

20 基于DSP和FPGA的模塊化實時圖像處理系統(tǒng)設(shè)計

2017-10-23 14:09:42 9

9 的單一DSP的架構(gòu)已經(jīng)不能完全滿足人們的需求。 1、DSP/MCU融合或者DSP+FPGA架構(gòu) 針對這一問題,現(xiàn)在比較流行的解決方案為:DSP/MCU融合或者DSP+FPGA架構(gòu)。 1.1 DSP特點 DSP一般采用哈佛架構(gòu),超長指令字架構(gòu)等,數(shù)據(jù)存取和指令分開,內(nèi)部運(yùn)

2017-10-25 16:26:07 0

0 針對信號處理數(shù)據(jù)量大、實時性要求高的特點,從實際應(yīng)用出發(fā),設(shè)計了以雙DSP+FPGA為核心的并行信號處理模塊。為了滿足不同的信號處理任務(wù)需求,FPGA可以靈活地選擇與不同的DSP組成不同的信號處理

2017-11-17 06:11:40 3060

3060

本文提出了一種使用亮度映射的圖像去霧快速算法。此算法通過調(diào)整室外多霧場景圖像的對比度,提高了霧中物體的辨識度。算法的復(fù)雜度低、處理延遲小,實時性高,利于FPGA的實現(xiàn)。實現(xiàn)時不需外存儲器,延時為ns級,并提供了強(qiáng)度調(diào)節(jié)接口,以適應(yīng)較廣的應(yīng)用環(huán)境。

2017-11-17 10:45:07 5906

5906

為解決高速數(shù)字圖像處理系統(tǒng)和實時性相沖突的要求,設(shè)計了以多DSP(數(shù)字信號處理器TMS320C6416)和現(xiàn)場可編程門陣列(FPGA)相結(jié)合的實時圖像處理系統(tǒng)。重點介紹了該系統(tǒng)的硬件資源選擇、基本組

2017-11-18 12:34:02 4703

4703

,改進(jìn)對大氣光和透射率的估計方法,進(jìn)而對非天空區(qū)域采用改進(jìn)的暗通道先驗算法去霧;最后,利用基于成本函數(shù)的對比度增強(qiáng)去霧算法處理天空區(qū)域。實驗結(jié)果表明,去霧后圖像在方差、平均梯度、信息熵等指標(biāo)上相對于暗通道先驗

2017-11-24 16:28:35 4

4 本文主要介紹了一種基于DSP+FPGA視頻圖像采集處理系統(tǒng)的設(shè)計與實現(xiàn),DSP-BF561作為主處理器,負(fù)責(zé)整個算法的調(diào)度和數(shù)據(jù)流的控制,完成圖像數(shù)據(jù)的采集與顯示及核心算法的實現(xiàn),FPGA作為DSP的協(xié)處理器,依托其高度的并行處理能力,完成圖像預(yù)處理中大量的累乘加運(yùn)算。實驗證明系統(tǒng)達(dá)到了實時性要求。

2017-12-25 10:39:47 5649

5649

基于圖像復(fù)原的去霧算法中參數(shù)的估計容易造成去霧圖像場景信息的丟失,對此,提出一種圖像去霧新算法。在暗通道先驗的基礎(chǔ)上,通過對大氣散射模型的分析,總結(jié)出霧氣分布對暗通道圖像的影V向,并依此對外景圖像

2018-01-05 15:53:56 2

2 傳統(tǒng)Retinex算法中對圖像R、G、B 3個通道分別進(jìn)行處理,容易造成顏色失真,而且在硬件實現(xiàn)中計算量非常大,難以滿足系統(tǒng)的實時性要求。因此,本文采用基于HSV顏色空間的Retinex算法

2018-04-26 08:51:28 6161

6161

由于現(xiàn)場實時測量的需要,機(jī)器視覺技術(shù)越來越多地借助硬件來完成,如DSP芯片、專用圖像信號處理卡等。但是,DSP做圖像處理也面臨著由于數(shù)據(jù)存儲與處理量大,導(dǎo)致處理速度較慢,系統(tǒng)實時性較差的問題。本文將

2018-10-23 17:34:44 18

18 實時視頻信號處理的實時性和跟蹤算法的復(fù)雜性是一對矛盾,為此采用DSP+FPGA 的架構(gòu)設(shè)計,同時滿足實時性和復(fù)雜性的要求,提高了系統(tǒng)的整體性能。DSP 作為主處理器,利用其高速的運(yùn)算能力,快速有效地

2018-12-18 19:27:46 15

15 在霧、霾等惡劣天氣條件下,由于空氣中渾濁介質(zhì)對大氣光的吸收、反射等作用,獲取到的圖像出現(xiàn)霧化現(xiàn)象,對視覺應(yīng)用系統(tǒng)產(chǎn)生嚴(yán)重影響。針對圖像去霧問題,許多研究者提出了多種解決方法。

2018-12-19 16:46:53 7

7 與FPGA結(jié)合在一起,組成DSP+FPGA架構(gòu),實現(xiàn)了需求獨(dú)特、靈活、功能強(qiáng)大的DSP+FPGA高速數(shù)據(jù)采集處理系統(tǒng)。

2020-02-12 13:42:30 4542

4542 本文檔的主要內(nèi)容詳細(xì)介紹的是基于直方圖優(yōu)化的圖像去霧技術(shù) 包含局部直方圖和retienx算法,以包含gui免費(fèi)下載。

2020-06-12 08:00:00 9

9 本文是收錄于CVPR2020的工作,我是被雙目圖像去霧的題目所吸引的,其實整個工作的創(chuàng)新性不高,但是可以從中學(xué)到數(shù)據(jù)集的制作,圖像去霧...

2020-12-10 15:19:42 1224

1224 為了改善紅外圖像的成像質(zhì)量,根據(jù)紅外圖像的特點,提出了一種改進(jìn)的拉普拉斯銳化算法——受限拉普拉斯銳化算法,并采用DSP+FPGA的架構(gòu)進(jìn)行實時處理。對普通拉氏銳化算法和受限拉氏銳化算法的處理效果進(jìn)行比較。受限拉氏銳化算法有效地控制了圖像的噪聲,使處理后的圖像邊緣更加清晰,又保護(hù)了圖像的細(xì)節(jié)。

2021-01-25 16:04:00 6

6 針對兩軸電視經(jīng)緯儀動基座跟蹤目標(biāo)時,視軸無法隔離載體擾動造成圖像旋轉(zhuǎn)現(xiàn)象,提出一種基于數(shù)學(xué)平臺的電子消旋方法,采用捷聯(lián)式慣導(dǎo)+DSP+FPGA的硬件系統(tǒng)通過反向旋轉(zhuǎn)和雙線性插值對圖像進(jìn)行消旋和填充

2021-02-01 16:11:03 3

3 FPGA,通過并行處理結(jié)構(gòu)及流水線技術(shù),可實時處理每秒50幀780×582×12bits的可見光圖像。在處理視頻的過程中,由前一幀圖像的直方圖信息,來增強(qiáng)后一幀圖像。理論分析和實驗結(jié)果均表明,該算法克服了直方圖均衡及平臺直方圖均衡增強(qiáng)

2021-02-03 15:21:00 10

10 ,使用~tera的Quartus II軟件,完成了其中的核心模塊——F盯算法的硬件實現(xiàn),提高了處理速度;并運(yùn)用DSP處理器,設(shè)計了一個基于FPGA的實時數(shù)字圖像處理系統(tǒng).文中給出了系統(tǒng)的硬件電路和軟件算法模塊.仿真和調(diào)試結(jié)果表明:用FPGA與高速數(shù)字信

2021-02-05 15:54:00 142

142 以FPGA為系統(tǒng)核心,為微光視頻圖像的實時增強(qiáng)設(shè)計了一套可應(yīng)用于空間狹小環(huán)境中的小型化處理系統(tǒng)。利用Ahera公司提供的IP Core,通過12C總線初始化編解碼芯片,簡化了系統(tǒng)設(shè)計,使系統(tǒng)運(yùn)行更加可靠。應(yīng)用在微光視頻圖像系統(tǒng)中,使圖像增強(qiáng)效果更加明顯。

2021-03-18 16:39:49 14

14 針對現(xiàn)有圖像去霧算法嚴(yán)重依賴中間量準(zhǔn)確估計的問題,提出了一種基于 Wasserstein生成對抗網(wǎng)絡(luò)(wGAN)的端到端圖像去霧模型。首先,使用全卷積密集塊網(wǎng)絡(luò)(FC- Dense Net充分學(xué)習(xí)

2021-04-12 15:03:33 20

20 利用暗通道先驗去霧算法處理包含大塊亮白區(qū)域的圖像時,存在圖像失真的問題。為此,提出一種改進(jìn)的的單幅圖像去霧算法。利用基于圖像子塊平均灰度值和標(biāo)準(zhǔn)差的四叉樹分解方法得到大氣光估值,通過圖像暗通道直方圖

2021-05-25 16:31:32 3

3 在圖像去霧過程中,對大氣光透射率估計不準(zhǔn)確,會降低去霧圖像場景亮度,并導(dǎo)致天空區(qū)域出現(xiàn)光暈現(xiàn)象。為此,提出一種基于分塊優(yōu)化透射率與自適應(yīng)優(yōu)化場景亮度的圖像去霧算法。根據(jù)圖像有霧程度評判標(biāo)準(zhǔn)對透射率

2021-06-09 11:06:05 15

15 霧霾環(huán)境下視頻圖像透霧系統(tǒng)設(shè)計與實現(xiàn)

2021-06-16 10:14:32 15

15 算法得以實現(xiàn)。 本篇闡述了基于FPGA設(shè)計一個能夠實時采集、實時處理并實時顯示的數(shù)字圖像處理系統(tǒng)的設(shè)計思想和流程,分析了攝像頭接口的時序;闡述了圖像信息的捕獲原理;詳細(xì)介紹了圖像邊緣檢測部分各模塊的功能;重點介紹了具有去噪

2021-06-30 09:49:01 3183

3183 本文詳細(xì)描述了FPGA實現(xiàn)圖像去霧的實現(xiàn)設(shè)計方案,采用暗通道先驗算法實現(xiàn),并利用verilog并行執(zhí)行的特點對算法進(jìn)行了加速;

2023-06-05 17:01:45 1554

1554

,系統(tǒng)實時性較差的問題。本文將FPGA的IP核內(nèi)置緩存模塊和乒乓讀寫結(jié)構(gòu)相結(jié)合,實現(xiàn)了圖像數(shù)據(jù)的緩存與提取,節(jié)省了存儲芯片所占用的片上空間,并且利用圖像預(yù)處理重復(fù)率高,但算法相對簡單的特點和FPGA數(shù)據(jù)并行處理,結(jié)合流水線的結(jié)構(gòu),大大

2023-06-15 15:20:02 2924

2924

電子發(fā)燒友App

電子發(fā)燒友App

評論