超越摩爾定律的堆疊硅片互聯技術和28Gbps 收發器引領 FPGA 創新的新時代

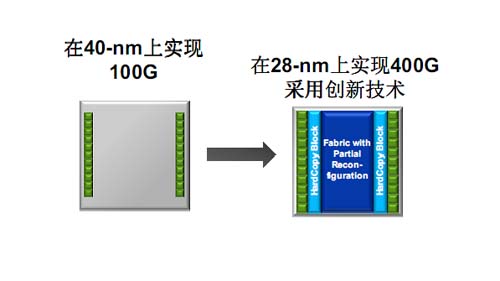

賽靈思最近推出了兩款最新創新技術,進一步擴展了 FPGA 的應用可能與市場范圍。去年 10 月底,賽靈思宣布在即將推出的 28nm 高端Virtex?-7 系列中新增堆疊硅片互聯(SSI) FPGA(見《賽靈思中國通訊》第 37 期)。最新創新型架構可在單個硅中介層上連接數個芯片,這使賽靈思的 Virtex-7 FPGA 能夠集成多達200 萬個邏輯單元(是已宣布推出的任何其他 28nm FPGA 的邏輯容量的兩倍),從而在當代工藝技術中實現下一代產品的功能。

隨后,賽靈思于去年 11 月底還透露了 Virtex-7 HT 系列器件的相關信息。Virtex-7 HT 器件利用 SSI 技術,在單個芯片上集成了 FPGA 和高速收發器芯片,這對通信領域的客戶而言是一個巨大的技術飛躍,而且能滿足越來越多應用對高速 I/O 的需求。最新 FPGA 能夠在同一器件上容納眾多 28Gbps 收發器以及數 10 個13.1Gbps 收發器,這有助于在新設備標準制定之前為當前 100Gbps 通信設備以及 400Gbps 通信線路卡的開發做好準備。

超越摩爾定律

Intel 聯合創始人戈登摩爾于1965 年 4 月 19 日在《電子》雜志上發表了深有遠見的《在集成電路上集成更多組件》一文,此后半導體產業每 22 個月更新換代都將晶體管集成量翻一番。與半導體產業中的其他公司一樣,賽靈思過去多年來也認識到,要想引領整個市場,就必須跟上摩爾定律的發展速度,每代工藝技術都要達到相應的集成標準,甚至要當引領標準發展的先鋒。

目前,隨著最新工藝的發展,復雜性、成本和設計風險日益提高,很多公司都應接不暇,而賽靈思則找到了推進新一代產品 Virtex-7 FPGA 容量翻番的獨特方法。賽靈思推出了業界首批堆疊硅片架構之一,帶來了一系列業界最大型的 FPGA。其中最大型的 FPGA 就是 28nm Virtex-7XC7V2000T,其包括 200 萬個邏輯單元和 305,400 個邏輯切片,BRAM容量高達 46,512 kb,還包括 2,160個DSP 切片 和 36 個 GTX 10.3125 Gbps 收發器。Virtex-7 系列包括多

個 SSI FPGA,采用單片 FPGA 配置。Virtex-7 是 7 系列的高端產品,其他 7 系列產品還包括新型低成本低功耗 ArtixTM FPGA 以及中端 KintexTM FPGA,上述所有產品均采用了統一面向應用的模塊化模塊 (ASMBL) 架構。

最新 SSI 技術不僅能滿足用戶使用業界最大型 FPGA 的要求,主流邏輯芯片中成功部署堆疊芯片還能帶來重大的半導

體設計成果。大多數公司還在評估堆疊芯片架構時,賽靈思就推出了堆疊硅芯片,有望改善容量和集成度,節約 PCB 板級空間,甚至進一步提高產量。大多數公司為了趕上摩爾定律不得不選擇堆疊硅片技術,而賽靈思則充分利用該技術讓其脫穎而出,在單個 IC 上組合匹配多種不同類型的芯片,從而大幅提升系統性能,降低材料清單成本 (BOM),提高功率效率。

堆疊硅片架構

賽靈思負責 FPGA 開發與芯片技術的企業副總裁 Liam Madden 指出:“這種新的堆疊硅片互聯技術使賽靈思能夠為當代工藝技術帶來下一代的高密度性能。隨著芯片尺寸的增大,良率將呈指數級下降,因此構建大型芯片相當困難,而且成本不菲。最新架構使我們能夠構建一系列較小型芯片,然后通過硅中介層并排連接在該中介層上,看起來就像一體化芯片一樣,而且功能一樣。”(如圖 1 所示)

?

?

圖 1 堆疊硅片架構在單個硅中介層上并排放置多個芯片(即切片)。

每個芯片通過硅中介層中各層互聯,其方式類似于印制電路板上各層分立組件的互聯(如圖 2 所示)。芯片和硅中介層通過多個微凸塊連接。該架構還采用穿過無源硅中介層的硅通孔 (TSV) 協助實現器件上每個芯片不同區域以及片外資源之間的通信(如圖 3所示)。相鄰 FPGA 芯片間的數據在10,000 多個路由連接之間流動。

?

?

圖 2 賽靈思的堆疊硅片互聯技術采用無源硅中介層、微凸塊和硅通孔技術。

?

?

圖 3 28nm Virtex-7 器件真實的橫截面圖。我們看到 TSV 通過硅中介層連接微凸塊(頂部虛線)。

Madden表示,采用無源硅中介層而非系統級封裝或多芯片模塊化配置能夠帶來巨大優勢。他說:“我們采用常規硅

片互聯或金屬化來連接器件上的芯片,這樣硅片中的芯片連接數量大大超過系統級封裝。而且這種方法的最大優勢還在于節能性。由于我們通過硅片互聯技術連接芯片,因此功耗遠遠低于通過大線跡、封裝或電路板連接的方式。”

事實上,SSI 技術將單位功耗芯片間連接帶寬提升了 100 倍以上,時延減至五分之一,而且不會占用任何高速串行或并行 I/O 資源。

Madden 還指出,微凸塊并非直接連接于封裝,而是互聯到無源硅中介層,進而連接到相鄰的芯片。這種設置方法能夠避免微凸塊受到靜電放電的影響,從而帶來巨大優勢。通過芯片彼此相鄰,并連接至球形柵格陣列,該器件避免了采用單純的垂直硅片堆疊方法出現的熱通量、信號完整性和設計工具流問題。

與單片 7 系列器件一樣,賽靈思在Virtex-7 系列的 SSI 產品中也采用了臺基電的 28nm HPL(高性能低功耗)工藝技術。該技術由賽靈思和臺基電聯合開發,有助于推出功率效率和性能相平衡的 FPGA(請參見封面故事輔助信息,《賽靈思中國通訊》第 37 期)。

無需新工具

Madden 指出,SSI 技術雖然大幅提升了容量,但不會使客戶設計方法產生巨變。他說:“該架構的優勢之一在于,我們能明確[器件中不同芯片]每個切片的自然分區邊緣,就好像我們在單片FPGA 架構中采用跡線一樣。這就意味著我們不必大幅改變工具就能支持新的器件。因此,客戶不必對設計方法或流程做大幅修改。”

Madden 同時表示客戶將受益于流程新增的平面規劃工具,因為現在他們能夠使用眾多邏輯單元。

供應鏈優先

設計方案本身獨具創新性, 器件推出的最大挑戰之一就在于確保制造、組裝、測試和分銷具有強大的供應鏈支持。為了生產最終產品,每個芯片都必須在晶圓級進行全面測試,還要分檔、分類并連接于中介層。整體結構要進行封裝,而且在最終產品發貨給客戶之前必須進行最終測試以確保可靠連接。

Madden 的工作團隊同臺基電及其他合作伙伴聯合構建了這樣一條供應鏈。Madden 表示:“其他公司在代工廠和OSAT[ 外包半導體組裝與測試] 之間還沒有建立供應鏈,我們此舉也是業界首創。”

Madden 還指出:“這種方法還有一大優勢,就是我們能采用與當前器件基本相同的測試方法。目前的測試技術使我們能生產已知良好的芯片,這對我們非常重要,因為堆疊硅片技術往往面臨著晶圓級測試的挑戰。”

由于堆疊硅技術在單 IC 上集成了多個賽靈思 FPGA 芯片,因此從邏輯上說,該架構能確保 FPGA 同其他芯片的組合與匹配,從而創建全新的器件,而這正是賽靈思推出超速 Virtex-7 HT 系列的根本所在。該系列產品在 SSI 技術推出后僅幾個星期就成功問世。

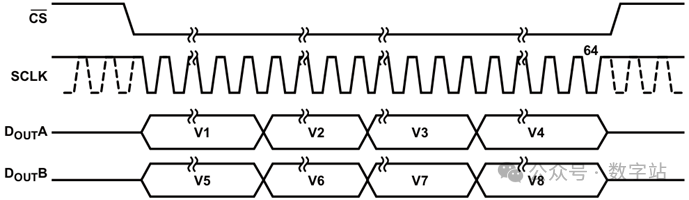

全新系列 Virtex-7 HT 器件正好面向正在開發 100~400 Gbps 設備的通信公司。Virtex-7 HT 在單個 IC 上集成了多個包括數十個 13.1Gbps 收發器的28nm FPGA 芯片和包含眾多 28Gbps 收發器的 ASIC 芯片。這樣,最終器件成品就擁有龐大的邏輯單元組合,而且實線了尖端收發器性能和可靠性。

最大型 Vi r e x - 7 HT 器件包括16 個 GTZ 28 Gbps 收發器、72個 13.1-Gbps 收發器以及邏輯單元和存儲器, 收發器性能和容量都大大超越了同類競爭產品( 觀看視頻1: user/XilinxInc#p/c/71A9E924ED61 B8F9/1/eTHjt67ViK0 )。

Madden 指出:“我們采用堆疊互聯技術為 Virtex-7 器件提供 28G 功能。我們在分立的 ASIC 芯片上提供收發器可以優化 28 Gbps 收發器性能和電離功能,從而進一步提高可靠性,滿足應用對尖端收發器性能和可靠性的需求。”

?

?

視頻 1 Howard Johnson 博士介紹帶 28 Gbps 收發器的Virtex-7 HT。

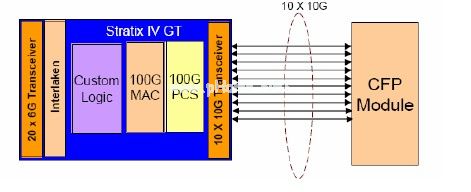

隨著帶寬需求的爆炸性增長,通信領域正加緊構建新網絡。無線產業目前積極推出支持 40Gbps 數據傳輸速率的設備,而有線網絡速度則已接近 100Gbps。FPGA 自誕生以來在各代網絡設備發展中都發揮了重要作用(請見《賽靈思中國通訊》第 37 期和 32 期的封面報道)。

通信設備設計團隊此前一直用FPGA 接收發送給設備的多協議信號,并將信號轉換為設備和網絡的常用協議,然后再將數據轉發到下一個目的地。各公司此前會在監控轉換輸入信號的 FPGA 和向下一站轉發信號的 FPGA之間放置一個處理器,但隨著 FPGA 容量的擴大以及功能的增強,單個FPGA就能就能完成接收和發送工作,同時還能進行信號處理,從而為系統帶來更高的智能和監控能力,也降低了材料清單成本,而更重要的是,這還能降低網絡設備的用電和制冷成本,確保設備全天候可靠運行。

在題為《業界最高帶寬的 FPGA支持全球首款 400G 通信線路卡單片 FPGA 解決方案》的白皮書中,賽靈思的 Greg Lara 概括介紹了可受益于 Virtex-7 HT 器件的幾種通信設備應用(敬請參閱: )。

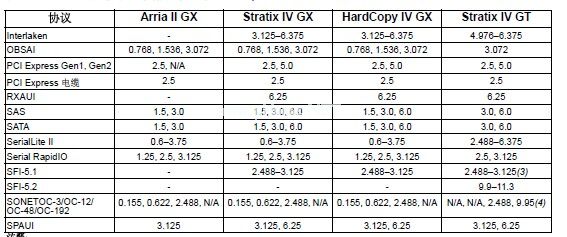

Virtex-7 HT FPGA可用于多種應用,例如支持OTU-4 (光傳輸單元)轉發器的100Gbps線路卡,也可用于多路轉發器或服務整合路由器,并在低成本 120Gbps 包處理線路卡中支持較高數據處理要求,此外也可用于多個 100G 以太網端口和橋接器以及400Gbps 以太網線路卡。其他潛在的應用還包括面向基站和遠程無線電前端的 19.6Gbps CPRI(通用公共無線電接口)以及 100Gbps 和 400Gbps 測試設備。

抖動和眼圖

用于上述市場應用的關鍵在于確保FPGA收發器信號的穩健性可靠性,能夠抗抖動、干擾以及電源系統噪聲產生的波動等。舉例來說,CEI-28G規范要求28Gbps網絡設備具有極其嚴格的抖動容限。

賽靈思的高級市場營銷經理Panch Chandrasekaran指出,信號完整性對28Gbps 工作極為重要。為了滿足嚴格的 CEI-28G抖動容限要求, 賽靈思新型FPGA中的收發器采用了基于LC諧振回路設計的鎖相回路 (PLL) 和高級均衡電路來抵消確定性抖動的影響。

Ch a n dr a s e k a r a n指出:“ 就28Gbps的信號速度而言,噪聲隔離是一個非常重要的參數。由于FPGA架構和

收發器分處于不同的芯片上,因此敏感型28Gbps模擬電路與數字FPGA電路隔離,相對于單片實現方案而言實現了出色的隔離效果。”(請見圖4a和4b)

?

?

圖4a — 賽靈思28 Gbps收發器提供了出色的眼開和抖動性能(采用PRBS31數據模式)。

?

?

圖4b — 同類競爭產品的28 Gbps信號采用的PRBS7模式簡單得多。該信號噪聲很大,眼開小得多。眼開大小參見相對尺度。

FPGA設計還包括了最小化信道間歪斜的特性,使器件能支持SFI-S等嚴格的光學標準。

此外,設計人員在進行GTZ收發器設計時,無需采用外部參考電阻器,從而降低了材料清單成本,簡化了電路板設計。內置的“眼掃描”功能可自動檢測后均衡數據眼高和眼寬。工程師可用診斷工具進行工作通道的抖動容限分析,并優化收發器參數,從而獲得最佳信號完整性,同時避免專業化設備的開支成本。

電子發燒友App

電子發燒友App

評論