FPGA的IRIG-B編碼器實(shí)現(xiàn)

我國靶場測量、工業(yè)控制、電力系統(tǒng)測量與保護(hù)、計(jì)算、通信、氣象等測試設(shè)備均采用國際標(biāo)準(zhǔn)IRIG-B格式的時(shí)間碼(簡稱B碼)作為時(shí)間同步標(biāo)準(zhǔn)。B

2010-03-29 09:58:13 2628

2628

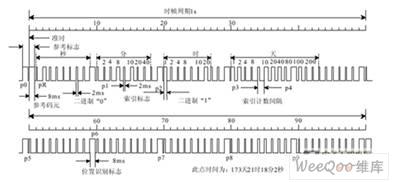

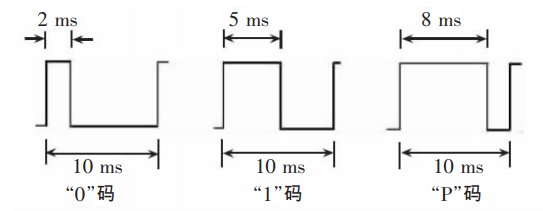

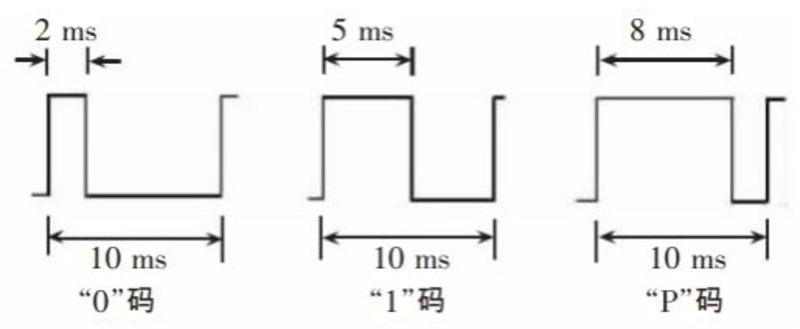

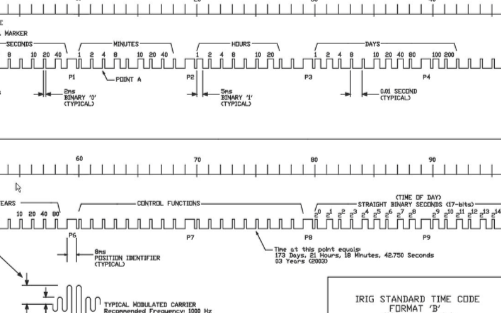

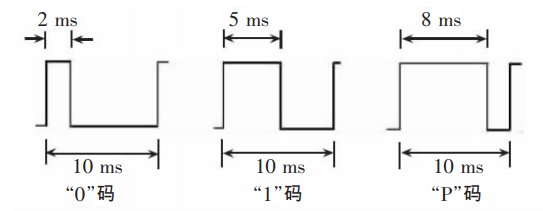

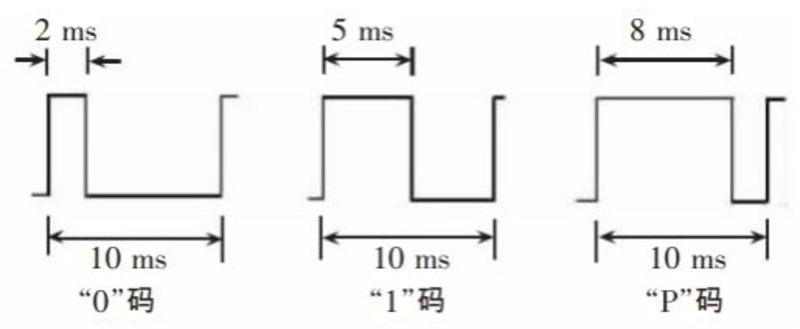

)碼是一種時(shí)間同步標(biāo)準(zhǔn),通常用于精確的時(shí)間測量和數(shù)據(jù)同步,廣泛應(yīng)用于電力、通信、航空等領(lǐng)域。IRIG-B碼為每秒一幀的時(shí)間串碼,一幀串碼中包含100個(gè)碼元,頻率為1KHz,即每個(gè)碼元占用10ms時(shí)間

2024-07-25 14:38:10

是一種時(shí)間同步標(biāo)準(zhǔn),通常用于精確的時(shí)間測量和數(shù)據(jù)同步,廣泛應(yīng)用于電力、通信、航空等領(lǐng)域。IRIG-B碼為每秒一幀的時(shí)間串碼,一幀串碼中包含100個(gè)碼元,頻率為1KHz,即每個(gè)碼元占用10ms時(shí)間

2024-07-17 11:07:13

原理IRIG-B(inter-range instrumentationgroup-B)碼是一種時(shí)間同步標(biāo)準(zhǔn),通常用于精確的時(shí)間測量和數(shù)據(jù)同步,廣泛應(yīng)用于電力、通信、航空等領(lǐng)域。IRIG-B碼為每秒一幀的時(shí)間串碼

2024-08-22 14:00:01

FPGA的IRIG-B(DC)碼產(chǎn)生電路設(shè)計(jì)FPGA的IRIG-B(DC)碼產(chǎn)生電路設(shè)計(jì).doc

2012-08-11 10:34:15

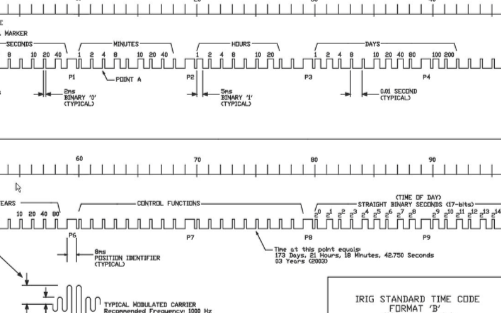

我國靶場測量、工業(yè)控制、電力系統(tǒng)測量與保護(hù)、計(jì)算、通信、氣象等測試設(shè)備均采用國際標(biāo)準(zhǔn)IRIG-B格式的時(shí)間碼(簡稱B碼)作為時(shí)間同步標(biāo)準(zhǔn)。B碼是一種串行的時(shí)間格式,分為直流碼(DC碼)和交流碼(AC碼)兩種,其格式和碼元定時(shí)在文獻(xiàn)[1]中有詳細(xì)描述。

2019-08-19 07:48:00

求給個(gè)IRIG-B解碼的VHDL或是Verilog HDL語言,發(fā)我郵箱最好。郵箱:bee_ing@163.com。感激不盡。

2013-11-30 15:01:30

摘要:為了實(shí)現(xiàn)對非相干雷達(dá)的接收相參處理,基于數(shù)字穩(wěn)定校正(DSU)的原理,采用ALTERA公司的StratixⅡ系列芯片和VHDL編程語言,設(shè)計(jì)了一種基于FPGA的DSU硬件實(shí)現(xiàn)方法。實(shí)驗(yàn)結(jié)果表明

2019-06-28 08:27:33

摘要:UART作為RS232協(xié)議的控制接口得到了廣泛的應(yīng)用,將UART的功能集成在FPGA芯片中,可使整個(gè)系統(tǒng)更為靈活、緊湊,減小整個(gè)電路的體積,提高系統(tǒng)的可靠性和穩(wěn)定性。提出了一種基于FPGA

2019-06-21 07:17:24

)。本文介紹了一種讀寫器的編解碼部分由FPGA來完成的設(shè)計(jì)方案,由FPGA負(fù)責(zé)前向鏈路的PIE編碼和后向鏈路的FM0/miller解碼,且解碼模塊可對標(biāo)簽突發(fā)傳來的數(shù)據(jù)立即檢測并實(shí)施解碼,實(shí)現(xiàn)了較快的解碼速率。FPGA選用的是Altera公司的EP1C3T100C6芯片。

2019-07-26 06:47:39

中,數(shù)字信號處理系統(tǒng)經(jīng)常要進(jìn)行高速、高精度的FFF運(yùn)算。現(xiàn)場可編程邏輯陣列(FPGA)是一種可定制集成電路,具有面向數(shù)字信號處理算法的物理結(jié)構(gòu)。用FPGA實(shí)現(xiàn)FFT處理器具有硬件系統(tǒng)簡單、功耗低的優(yōu)點(diǎn)

2019-07-03 07:56:53

在工控行業(yè)很多領(lǐng)域中,需要控制系統(tǒng)具有高精度的時(shí)間同步功能,IRIG就是美國靶場司令委員會(huì)制定的一種時(shí)間標(biāo)準(zhǔn),英創(chuàng)在EM928x系列的Linux工控主板上實(shí)現(xiàn)了IRIG-B碼校時(shí)功能

2016-06-12 15:30:46

4 通道光纖網(wǎng)絡(luò)數(shù)據(jù)的高速采集、實(shí)時(shí)記錄和寬帶回放。該板卡還具有高精密時(shí)鐘同步功能,板卡可采集精準(zhǔn)時(shí)間碼(IRIG-B)作為同步基準(zhǔn),內(nèi)嵌 TDC 測時(shí)單元,對發(fā)送和接收數(shù)據(jù)添加 64 位時(shí)間戳

2017-03-11 14:05:16

最近做的項(xiàng)目中有一個(gè)模塊是做IRIG_B碼的編碼模塊,部分程序:case count100 iswhen 1=>irig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_b

2015-10-14 21:42:56

記錄下過程,設(shè)計(jì)也有問題,望大神們批評指正。首先介紹下原理下的東西1. HDB3碼介紹三階高密度雙極性碼(英語:High Density Bipolar ofOrder 3,簡稱:HDB3碼)是一種適用于基帶傳輸?shù)木幋a

2016-04-15 21:54:08

EPM7160S的結(jié)構(gòu)及特點(diǎn),詳細(xì)闡述IRIG-B碼標(biāo)準(zhǔn)。該設(shè)計(jì)成功解決了AC碼調(diào)制精度問題。這種方法具有靈活性、開放性、簡單實(shí)用、體積小、功耗低的優(yōu)點(diǎn),同時(shí)具有較強(qiáng)的抗干擾性,是一種成功的硬件解決方案。【關(guān)鍵詞

2010-04-24 09:05:05

求助!大佬們,問一下用FPGA實(shí)現(xiàn)卷積碼編解碼的難度。

2023-10-16 23:26:26

我國靶場測量、工業(yè)控制、電力系統(tǒng)測量與保護(hù)、計(jì)算、通信、氣象等測試設(shè)備均采用國際標(biāo)準(zhǔn)IRIG-B格式的時(shí)間碼(簡稱B碼)作為時(shí)間同步標(biāo)準(zhǔn)。B碼是一種串行的時(shí)間格式.分為直流碼(DC碼)和交流碼(AC

2019-08-08 07:25:35

我國靶場測量、工業(yè)控制、電力系統(tǒng)測量與保護(hù)、計(jì)算、通信、氣象等測試設(shè)備均采用國際標(biāo)準(zhǔn)IRIG-B格式的時(shí)間碼(簡稱B碼)作為時(shí)間同步標(biāo)準(zhǔn)。

2019-10-23 08:11:07

本文介紹一種基于FPGA并執(zhí)行IRIG-B標(biāo)準(zhǔn)的AC/DC編碼技術(shù),與基于MCU或者DSP和數(shù)字邏輯電路實(shí)現(xiàn)的編碼方法相比,該技術(shù)可以大大降低系統(tǒng)的設(shè)計(jì)難度,降低成本,提高B碼的精確性和系統(tǒng)靈活性。

2021-04-29 06:56:12

ADV611的工作原理是什么?怎樣去實(shí)現(xiàn)一種ADV611編解碼方案?

2021-06-04 07:17:07

有木有哪位大俠有FPGA 實(shí)現(xiàn)IRIG B碼的quartus 工程文件呀 新手,剛學(xué)這個(gè),想找個(gè)例子學(xué)習(xí)下,望大家指導(dǎo)

2013-03-08 16:14:23

求一種基于FPGA滑動(dòng)相關(guān)法偽碼捕獲的研究與實(shí)現(xiàn)

2021-04-30 06:52:27

新手,問下看資料不是很懂IRIG_B。。有幾個(gè)問題。希望大家可以解答下。。小弟感激不盡。如下:(1)我們主要是用它做什么呢?我的理解的是 我這邊解碼出來以后,以后所有串口、網(wǎng)絡(luò)這些發(fā)送的信息都帶一個(gè)

2016-11-05 09:30:35

RT用labVIEW實(shí)現(xiàn)一種RFID編解碼的仿真

2013-05-14 23:21:59

請問怎樣去實(shí)現(xiàn)一種基于FPGA的矩陣運(yùn)算?

2021-06-22 07:00:19

一種基于IRIG-A碼輸出的超小型GPS時(shí)鐘設(shè)計(jì)

2021-05-27 06:24:52

小弟我剛開始學(xué)習(xí)此方面的內(nèi)容,對于VHDL還不是很熟悉,希望各位大神拉我一把,給我個(gè)IRIG-B解碼的VHDL程序,一次度過難過。。小弟我在此將感激不盡。。

2013-11-09 13:27:47

廣播報(bào)時(shí)信號嵌入時(shí)間碼規(guī)范GY T 219-2006

2008-11-22 16:59:09 24

24 在采用一維ST-OOC碼的基礎(chǔ)上,在光CDMA系統(tǒng)編/解碼器端分別加入起/解偏器,引入偏振信息來提高碼字維數(shù),從而得到一種新型光CDMA系統(tǒng)多維碼的構(gòu)造方法。理論分析表明通過在一

2008-12-16 23:49:48 11

11

介紹用FPGA 設(shè)計(jì)實(shí)現(xiàn)MIL-STD-1553B 總線接口中的曼徹斯特碼編解碼器。該設(shè)計(jì)采用VHDL 硬件描述語言編程,并用專門的綜合工具Synplify 對設(shè)計(jì)進(jìn)行綜合、優(yōu)化,在MAX+PLUSⅡ進(jìn)行時(shí)序仿

2009-05-15 16:25:50 43

43 變長碼作為一種最流行的數(shù)據(jù)壓縮技術(shù),已被許多數(shù)據(jù)壓縮標(biāo)準(zhǔn),如JPEG,MPEG-2和H.263 等作為編碼方法。但由于解碼過程中的循環(huán)依賴性,限制了解碼吞吐率。本文介紹了一種基于

2009-06-09 11:31:41 17

17 本文討論了一種可在FPGA 上實(shí)現(xiàn)的FFT 結(jié)構(gòu)。該結(jié)構(gòu)采用基于流水線結(jié)構(gòu)和快速并行乘法器的蝶形處理器。乘法器采用改進(jìn)的Booth 算法,簡化了部分積符號擴(kuò)展,使用Wallace 樹結(jié)構(gòu)和4-2

2009-09-11 15:46:40 16

16 DFT 偽碼捕獲算法在進(jìn)行偽碼搜索的同時(shí)估計(jì)多普勒頻偏,為了滿足捕獲精度要求,需要增加DFT 點(diǎn)數(shù),但隨著運(yùn)算點(diǎn)數(shù)的增加硬件實(shí)現(xiàn)難度成倍增長。本文提出一種基于FPGA 的在不

2009-09-22 09:59:21 12

12 一種基于FPGA 的可重構(gòu)密碼芯片的設(shè)計(jì)與實(shí)現(xiàn)楊曉輝, 戴紫彬解放軍信息工程大學(xué) 電子技術(shù)學(xué)院,河南 鄭州 450004來源:電子技術(shù)應(yīng)用摘 要: 介紹了SHA-1、SHA224 及SHA256

2010-02-05 08:25:52 36

36 為提高AC碼的調(diào)制精度,減小電路板面積,提出基于EPM7160S的IRIG-B(AC)碼調(diào)制設(shè)計(jì)。介紹EPM7160S的結(jié)構(gòu)及特點(diǎn),詳細(xì)闡述IRIG-B碼標(biāo)準(zhǔn)。該設(shè)計(jì)成功解決了AC碼調(diào)制精度問題。這種方法

2010-02-11 11:11:42 39

39 一種BIN 碼與BCD 碼轉(zhuǎn)換電路的設(shè)計(jì)與實(shí)現(xiàn)

二進(jìn)制(BIN) 碼與二- 十進(jìn)制(BCD) 碼的互換在許多測控領(lǐng)域有大量應(yīng)用, 但大多以軟件方式實(shí)現(xiàn)。本文根據(jù)一種新的以簡單移位

2010-02-22 15:43:53 23

23 介紹了一種基于DSP和FPGA的GPS-B碼時(shí)統(tǒng)終端系統(tǒng)的設(shè)計(jì)方案,提出了一種利用FPGA對IRIG-B碼進(jìn)行解碼的設(shè)計(jì)方法。詳細(xì)論述了具體的設(shè)計(jì)方案及軟硬件的實(shí)現(xiàn)。通過將快速的DSP與FPGA相結(jié)

2010-02-24 13:48:49 22

22 摘要:本文詳細(xì)敘述了基于FPGA及單片機(jī)K實(shí)現(xiàn)時(shí)碼終端系統(tǒng)的設(shè)計(jì)方法,該系統(tǒng)可用于對國際通用時(shí)間格式碼IRIG碼(簡稱B碼)的解調(diào),以及產(chǎn)生各種采樣、同步頻率信號,也可作為

2010-07-12 12:00:56 15

15 介紹了一種采用并行方式構(gòu)建的多符號可變長碼解碼器。該解碼器通過增加結(jié)構(gòu)的復(fù)雜性和對硬件資源的占用,換取可變長碼解碼的高吞吐量。這種結(jié)構(gòu)突破了可變長碼碼字之間的

2010-07-17 15:01:19 17

17 Cyclone 系列芯片是Altera公司推出的低價(jià)格、高容量的FPGA,內(nèi)置M4K存儲(chǔ)塊,最大RAM可達(dá)288kb。IRIG-B碼是標(biāo)準(zhǔn)時(shí)間碼格式之一,廣泛的應(yīng)用于靶場時(shí)間信息的傳遞和各系統(tǒng)的時(shí)間同步。利用Cyc

2010-07-28 16:59:22 51

51 時(shí)間同步裝置北斗衛(wèi)星時(shí)鐘是一款高精度時(shí)間同步裝置,支持GPS/北斗雙模雙天線,支持主備從配置。系統(tǒng)有著豐富的輸出接口和輸出類型,涵蓋電力自動(dòng)化所有對時(shí)需求,如IRIG-B(DC)、IRIG-B(AC

2024-01-08 16:43:38

威科姆VC-7850-K 電力系統(tǒng)同步擴(kuò)展時(shí)鐘以兩路地面鏈路B碼授時(shí)輸入為時(shí)間基準(zhǔn),以第一路IRIG-B碼輸入為主用時(shí)間基準(zhǔn)、第二路IRIG-B碼輸入為備用時(shí)間基準(zhǔn),設(shè)備與B碼時(shí)間基準(zhǔn)保持同

2010-08-17 10:18:08 20

20 一、論文總體思路

二、B碼簡介

三、B碼解碼

四、北斗衛(wèi)星導(dǎo)航系統(tǒng)

2010-10-18 16:22:15 0

0 IRIG碼是一種通用的國際標(biāo)準(zhǔn)傳輸碼,廣泛應(yīng)用于時(shí)統(tǒng)設(shè)備之間的時(shí)間通信。本時(shí)鐘設(shè)計(jì)采用微控制器,依據(jù)GPS時(shí)鐘信號對本地晶振進(jìn)行頻率測量,根據(jù)測量結(jié)果實(shí)時(shí)調(diào)整時(shí)間單元

2009-03-29 15:15:58 1468

1468

摘要: 介紹用FPGA設(shè)計(jì)實(shí)現(xiàn)MIL-STD1553B部接口中的曼徹斯特碼編解碼器。該設(shè)計(jì)采用VHDL硬件描述語言編程,并且專門的綜合工具Synplify對設(shè)計(jì)進(jìn)行綜合、優(yōu)化,在MA

2011-04-19 21:38:56 1940

1940

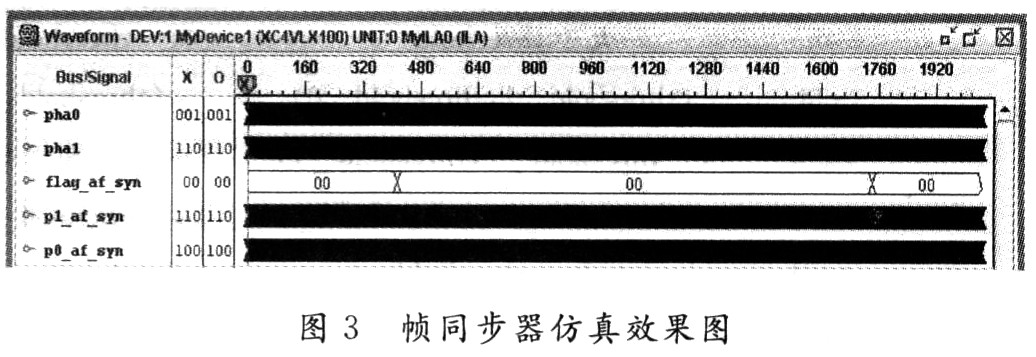

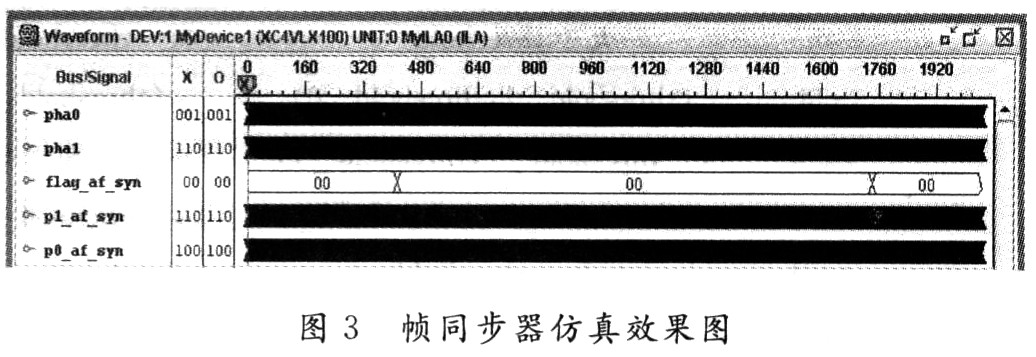

一種高速幀同步和相位模糊估計(jì)的方法及其FPGA實(shí)現(xiàn)

摘要:提出僅依靠接收符號和本地同步碼快速確定MPSK調(diào)制符號的幀同步,并同時(shí)估計(jì)其相位模糊值的計(jì)算方法,給

2010-01-27 09:38:17 1833

1833

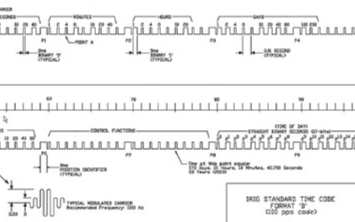

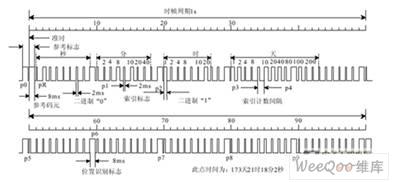

IRIG是美國靶場儀器組的簡稱,美國靶場儀器組是美國靶場司令部委員會(huì)的下屬機(jī)構(gòu)。

IRIG時(shí)間標(biāo)準(zhǔn)有兩大類:

一類是并行時(shí)間碼格式,這類碼由于是并行格式,傳輸距

2010-07-28 17:01:17 2106

2106 隨著變電站自動(dòng)化技術(shù)的發(fā)展,對變電站內(nèi)時(shí)間的精確和統(tǒng)一提出了更高的要求。本文提出了一種采用IRIG-B時(shí)間碼來對時(shí)的方案。在這種對時(shí)方案中,每個(gè)變電站只安裝一個(gè)GPS接收裝置

2011-04-13 15:52:02 45

45 摘要:為提高8B/10B編解碼的工作速度和簡化邏輯方法,提出一種基于FPGA的8B/10B編解碼系統(tǒng)設(shè)計(jì)方案。與現(xiàn)有的8B/10B編解碼方案相比,該方案是一種利用FPGA實(shí)現(xiàn)8B/lOB編解碼的模塊方

2011-05-26 11:08:20 4329

4329

傳統(tǒng)的IRIG-B碼解碼器大多采用單片機(jī)來實(shí)現(xiàn),器件較多,結(jié)構(gòu)復(fù)雜,在受到外界干擾的情況下還可能出現(xiàn)死機(jī)等故障。而采用CPLD設(shè)計(jì)的解碼器可以大大減少器件的數(shù)量、增加解碼器的穩(wěn)

2011-08-20 15:16:43 6502

6502

SPI 串行總線是一種常用的標(biāo)準(zhǔn)接口,其使用簡單方便而且占用系統(tǒng)資源少,應(yīng)用相當(dāng)廣泛。本文將介紹一種新的通用的SPI 總線的FPGA 實(shí)現(xiàn)方法。

2011-09-09 11:58:27 67

67 本文提出了一種用FPGA實(shí)現(xiàn)糾錯(cuò)編碼的設(shè)計(jì)思想,并以Altera MAX+PluslI為硬件開發(fā)平臺。利用FPGA編程的特點(diǎn),用軟件編程方法,很好的解決了糾錯(cuò)編碼中存在的碼速變換和實(shí)時(shí)性問題,實(shí)現(xiàn)

2011-11-10 17:10:59 61

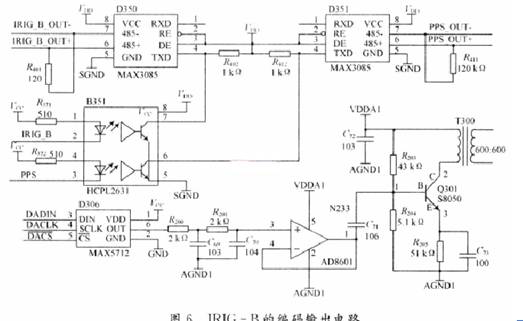

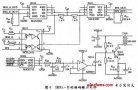

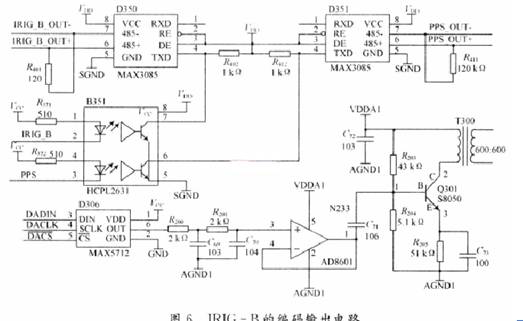

61 IRIG-B 的編碼輸出電路:

2012-04-25 16:29:48 3711

3711

在分析武器裝備靶場試驗(yàn)測控設(shè)備同步技術(shù)現(xiàn)狀基礎(chǔ)上,提出了一種多功能內(nèi)置式IRIG-B碼終端設(shè)計(jì);給出了終端的組成、功能與工作過程,詳細(xì)介紹了IRIG-B碼采集模塊、IRIG-B碼產(chǎn)生模塊

2012-07-27 16:17:56 0

0 同步時(shí)鐘信號是分布式錄波器系統(tǒng)任務(wù)順利完成的關(guān)鍵。介紹一種利用可編程CPLD器件實(shí)現(xiàn)性能優(yōu)良的分布式同步信號源。通過高度集成,將IRIG-B(DC)解碼器以及系統(tǒng)的各種同步邏輯電路集

2013-09-25 17:42:56 23

23 13曼徹斯特碼編解碼的FPGA設(shè)計(jì)與實(shí)現(xiàn)-9。

2016-04-26 15:12:57 12

12 RS編解碼的FPGA實(shí)現(xiàn)-說明RS編解碼的FPGA實(shí)現(xiàn)-說明。

2016-05-04 15:59:44 21

21 一種具有查錯(cuò)功能的10B_8B解碼器設(shè)計(jì)_鄒陳

2017-01-07 21:39:44 2

2 一種基于FPGA的時(shí)鐘相移時(shí)間數(shù)字轉(zhuǎn)換器_王巍

2017-01-07 22:23:13 3

3 一種高速卷積編解碼器的FPGA實(shí)現(xiàn)

2017-02-07 15:05:00 22

22 一種基于低成本FPGA的高速8B_10B編解碼器設(shè)計(jì)_陳章進(jìn)

2017-03-19 11:46:13 1

1 時(shí)間系統(tǒng)對于測控設(shè)備的正常運(yùn)行和故障診斷起著至關(guān)重要的作用。IRIC -B碼是國際靶場試驗(yàn)通用的同步時(shí)間碼。本文基于IRIC -B碼對某測控設(shè)備的時(shí)間系統(tǒng)進(jìn)行設(shè)計(jì),并在該設(shè)備中成功實(shí)現(xiàn)時(shí)間同步,精度

2017-11-02 15:44:41 1

1 MSP430系列單片機(jī)是集成度高、超低功耗的 16位單片機(jī)。Cyclone系列芯片是 Altera公 司推 出的低價(jià)格、RAM可達(dá) 288kb的高容量的FPGA。IRIG.B碼廣泛應(yīng)用于靶場時(shí)間信息

2017-11-28 14:41:50 4

4 鏈碼是一種以較少的數(shù)據(jù)存儲(chǔ)表示線條、曲線和區(qū)域邊界的編碼技術(shù)。為進(jìn)一步提高鏈碼的壓縮效率,提出了一種新的壓縮頂點(diǎn)鏈碼:改進(jìn)的正交3方向頂點(diǎn)鏈碼(103DVCC)。I03DVCC將頂點(diǎn)鏈碼(VCC

2017-12-01 10:26:26 0

0 時(shí)間信息的采集和處理在現(xiàn)代的各種電子計(jì)算系統(tǒng)中都有著關(guān)鍵的作用。針對美國靶場儀器組(IRJG)串行時(shí)間碼規(guī)范較多,格式多變的特性造成的其他時(shí)碼采集系統(tǒng)硬件兼容性較差的問題,設(shè)計(jì)了一種兼容各種格式

2018-02-02 14:20:57 1

1 Cyclone系列芯片是 A ltera公司推出的低價(jià)格、RAM 可達(dá) 288kb的高容量的 FPGA。 IRIG-B碼廣泛應(yīng)用于靶場時(shí)間信息的傳遞和各系統(tǒng)的時(shí)間同步。詳細(xì)介紹了IRIG-B碼解碼電路和調(diào)制電路的硬件設(shè)計(jì)。MSP430的軟件采用 C語言編寫, 使程序有很強(qiáng)的可移植性。

2018-05-02 15:32:53 10

10 B碼的各種門電路集成在一個(gè)芯片,通過高度集成的系統(tǒng)可以用于產(chǎn)生標(biāo)準(zhǔn)的串行時(shí)間碼向測量設(shè)備發(fā)送,測量設(shè)備對接收到的B碼進(jìn)行解調(diào)能產(chǎn)生出系統(tǒng)所需的絕對時(shí)間和各種控制信號。此B碼產(chǎn)生系統(tǒng)可作為基地設(shè)備檢測調(diào)試用,也可作實(shí)踐教學(xué)設(shè)備。

2019-02-06 09:32:00 3726

3726

曼徹斯特碼編碼、解碼器是1553B總線接口中不可缺少的重要組成部分。曼徹斯特碼編解碼器設(shè)計(jì)的好壞直接影響總線接口的性能。本文介紹的是MIL-STD-1553B接口中最曼徹斯特碼的編碼和解碼器的設(shè)計(jì)實(shí)現(xiàn)。

2019-04-24 08:24:00 5927

5927 在工控行業(yè)很多領(lǐng)域中,需要控制系統(tǒng)具有高精度的時(shí)間同步功能,IRIG就是美國靶場司令委員會(huì)制定的一種時(shí)間標(biāo)準(zhǔn)。自EM9X60后,英創(chuàng)EM928x嵌入式主板也實(shí)現(xiàn)了IRIG-B碼校時(shí)功能。之前的相關(guān)

2020-01-17 09:14:45 2078

2078

在工控行業(yè)很多領(lǐng)域中,需要控制系統(tǒng)具有高精度的時(shí)間同步功能,IRIG就是美國靶場司令委員會(huì)制定的一種時(shí)間標(biāo)準(zhǔn),英創(chuàng)在EM928x系列的Linux工控主板上實(shí)現(xiàn)了IRIG-B碼校時(shí)功能。 IRIG

2020-02-04 10:41:13 2380

2380

介紹了一種讀寫器的編解碼部分由FPGA來完成的設(shè)計(jì)方案,由FPGA負(fù)責(zé)前向鏈路的PIE編碼和后向鏈路的FM0/miller 解碼,且解碼模塊可對標(biāo)簽突發(fā)傳來的數(shù)據(jù)立即檢測并實(shí)施解碼,實(shí)現(xiàn)了較快的解碼速率。FPGA選用的是Altera公司的 EP1C3T100C6芯片。

2020-07-28 18:54:00 2

2 一種基于FPGA的MSK調(diào)制器設(shè)計(jì)與實(shí)現(xiàn)說明。

2021-04-27 14:08:41 22

22 一種基于FPGA的分頻器的實(shí)現(xiàn)說明。

2021-05-25 16:57:08 16

16 FPGA_ASIC-一種改進(jìn)的2D-DCT的FPGA實(shí)現(xiàn)(核達(dá)中遠(yuǎn)通電源技術(shù)有限公司招聘文員嗎?)-該文檔為FPGA_ASIC-一種改進(jìn)的2D-DCT的FPGA實(shí)現(xiàn)講解文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-09-16 10:35:54 4

4 基于FPGA的IRIGBDC碼解碼(開關(guān)電源技術(shù)教程課后習(xí)題答案)-該文檔為基于FPGA的IRIGBDC碼解碼講解文檔,是一份還算不錯(cuò)的參考文檔,感興趣的可以下載看看,,,,,,,,,,,,,,,,,

2021-09-27 15:16:58 22

22 電子發(fā)燒友網(wǎng)站提供《一個(gè)時(shí)間碼觸發(fā)的無線燈箱.zip》資料免費(fèi)下載

2022-12-16 14:14:06 0

0 格雷碼是一種特殊的二進(jìn)制碼,在結(jié)構(gòu)光三維視覺中,常常被用于編碼。比起我們常見的二進(jìn)制碼,格雷碼具有相鄰數(shù)字的編碼只有一位不同的優(yōu)點(diǎn),這個(gè)優(yōu)點(diǎn)對于解碼而言十分重要,可以減少光解碼的錯(cuò)誤率。下面我們可以看下如何對結(jié)構(gòu)光用格雷碼編碼,并如何對編碼的結(jié)構(gòu)光進(jìn)行解碼。

2022-12-21 11:14:51 2016

2016 什么是IRIG-B碼對時(shí) IRIG-B(inter-range instrumentationgroup-B)碼是一種時(shí)間同步標(biāo)準(zhǔn),通常用于精確的時(shí)間測量和數(shù)據(jù)同步,廣泛應(yīng)用于電力、通信、航空等領(lǐng)域

2024-03-07 09:55:46 1550

1550

Embedded Workbench ARM 8.11.2 硬件平臺:創(chuàng)龍科技TLFM20S-EVM評估板(基于FMQL20S400M國產(chǎn)平臺) IRIG-B碼對時(shí)原理 IRIG-B(inter-range instrumentationgroup-B)碼是一種時(shí)間同步標(biāo)準(zhǔn),通常用于精確的時(shí)

2025-02-27 10:22:23 1596

1596

GPS衛(wèi)星同步時(shí)鐘以GPS信號作為時(shí)間源,同時(shí)可選北斗衛(wèi)星、IRIG-B碼、OCX0、銣原子鐘、CDMA信號等時(shí)鐘源,對時(shí)精度達(dá)20nS。

2025-03-10 14:09:27 688

688

GPS授時(shí)裝置接收北斗衛(wèi)星、GPS衛(wèi)星、CDMA、SDH、PTP、IRIG-B碼、串口等外部時(shí)間基準(zhǔn)信號,通過智能時(shí)間源算法,實(shí)現(xiàn)多時(shí)間源的智能切換,輸出高精度、高可靠的時(shí)間同步信號和標(biāo)準(zhǔn)時(shí)間信息。

2025-06-16 14:55:01 559

559

SYN1502A型IRIG-B碼產(chǎn)生器是西安同步電子科技有限公司自主研發(fā)的高精度授時(shí)設(shè)備,以“便攜性、多功能性、高可靠性”為設(shè)計(jì)核心,兼顧操作便捷性與功能靈活性,為時(shí)間同步提供新方案。 一、產(chǎn)品概述

2025-06-23 18:10:49 497

497 在當(dāng)今數(shù)字化時(shí)代,眾多領(lǐng)域?qū)?b class="flag-6" style="color: red">時(shí)間同步的精度和可靠性有著極高的要求。SYN1502A型IRIG-B碼產(chǎn)生器作為一款專業(yè)的時(shí)間同步模塊設(shè)備,在滿足客戶多樣化需求、解決實(shí)際問題方面發(fā)揮著重要作用。 在航天

2025-06-23 18:12:16 398

398

電子發(fā)燒友App

電子發(fā)燒友App

評論