FPGA的IRIG-B編碼器實現

我國靶場測量、工業控制、電力系統測量與保護、計算、通信、氣象等測試設備均采用國際標準IRIG-B格式的時間碼(簡稱B碼)作為時間同步標準。B

2010-03-29 09:58:13 2628

2628

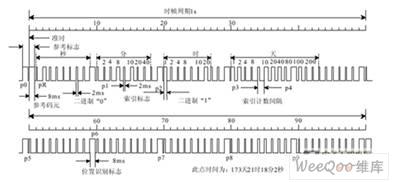

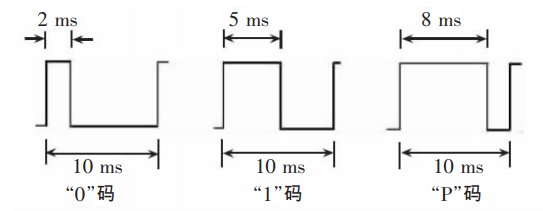

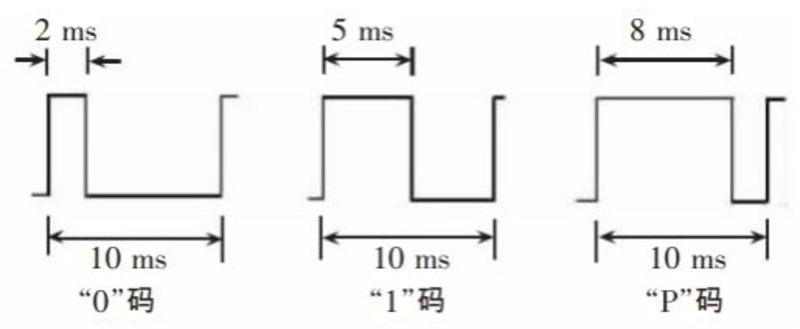

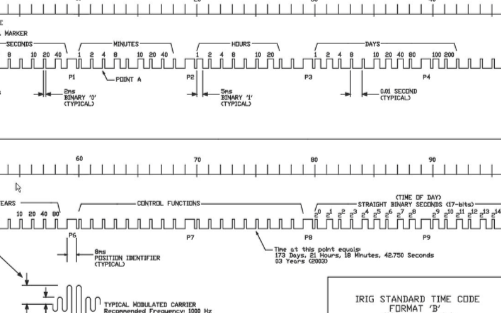

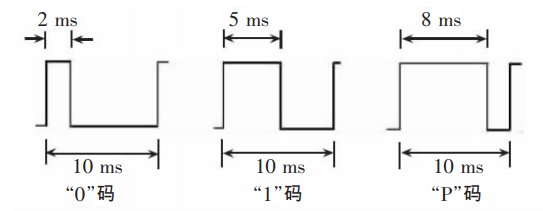

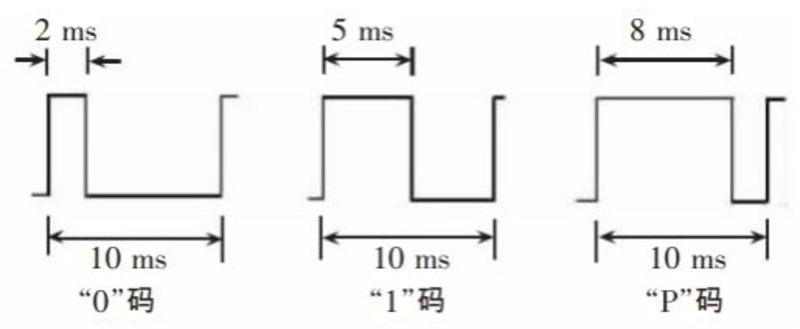

)碼是一種時間同步標準,通常用于精確的時間測量和數據同步,廣泛應用于電力、通信、航空等領域。IRIG-B碼為每秒一幀的時間串碼,一幀串碼中包含100個碼元,頻率為1KHz,即每個碼元占用10ms時間

2024-07-25 14:38:10

是一種時間同步標準,通常用于精確的時間測量和數據同步,廣泛應用于電力、通信、航空等領域。IRIG-B碼為每秒一幀的時間串碼,一幀串碼中包含100個碼元,頻率為1KHz,即每個碼元占用10ms時間

2024-07-17 11:07:13

原理IRIG-B(inter-range instrumentationgroup-B)碼是一種時間同步標準,通常用于精確的時間測量和數據同步,廣泛應用于電力、通信、航空等領域。IRIG-B碼為每秒一幀的時間串碼

2024-08-22 14:00:01

FPGA的IRIG-B(DC)碼產生電路設計FPGA的IRIG-B(DC)碼產生電路設計.doc

2012-08-11 10:34:15

我國靶場測量、工業控制、電力系統測量與保護、計算、通信、氣象等測試設備均采用國際標準IRIG-B格式的時間碼(簡稱B碼)作為時間同步標準。B碼是一種串行的時間格式,分為直流碼(DC碼)和交流碼(AC碼)兩種,其格式和碼元定時在文獻[1]中有詳細描述。

2019-08-19 07:48:00

求給個IRIG-B解碼的VHDL或是Verilog HDL語言,發我郵箱最好。郵箱:bee_ing@163.com。感激不盡。

2013-11-30 15:01:30

摘要:為了實現對非相干雷達的接收相參處理,基于數字穩定校正(DSU)的原理,采用ALTERA公司的StratixⅡ系列芯片和VHDL編程語言,設計了一種基于FPGA的DSU硬件實現方法。實驗結果表明

2019-06-28 08:27:33

摘要:UART作為RS232協議的控制接口得到了廣泛的應用,將UART的功能集成在FPGA芯片中,可使整個系統更為靈活、緊湊,減小整個電路的體積,提高系統的可靠性和穩定性。提出了一種基于FPGA

2019-06-21 07:17:24

)。本文介紹了一種讀寫器的編解碼部分由FPGA來完成的設計方案,由FPGA負責前向鏈路的PIE編碼和后向鏈路的FM0/miller解碼,且解碼模塊可對標簽突發傳來的數據立即檢測并實施解碼,實現了較快的解碼速率。FPGA選用的是Altera公司的EP1C3T100C6芯片。

2019-07-26 06:47:39

中,數字信號處理系統經常要進行高速、高精度的FFF運算。現場可編程邏輯陣列(FPGA)是一種可定制集成電路,具有面向數字信號處理算法的物理結構。用FPGA實現FFT處理器具有硬件系統簡單、功耗低的優點

2019-07-03 07:56:53

在工控行業很多領域中,需要控制系統具有高精度的時間同步功能,IRIG就是美國靶場司令委員會制定的一種時間標準,英創在EM928x系列的Linux工控主板上實現了IRIG-B碼校時功能

2016-06-12 15:30:46

4 通道光纖網絡數據的高速采集、實時記錄和寬帶回放。該板卡還具有高精密時鐘同步功能,板卡可采集精準時間碼(IRIG-B)作為同步基準,內嵌 TDC 測時單元,對發送和接收數據添加 64 位時間戳

2017-03-11 14:05:16

最近做的項目中有一個模塊是做IRIG_B碼的編碼模塊,部分程序:case count100 iswhen 1=>irig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_birig_b

2015-10-14 21:42:56

記錄下過程,設計也有問題,望大神們批評指正。首先介紹下原理下的東西1. HDB3碼介紹三階高密度雙極性碼(英語:High Density Bipolar ofOrder 3,簡稱:HDB3碼)是一種適用于基帶傳輸的編碼

2016-04-15 21:54:08

EPM7160S的結構及特點,詳細闡述IRIG-B碼標準。該設計成功解決了AC碼調制精度問題。這種方法具有靈活性、開放性、簡單實用、體積小、功耗低的優點,同時具有較強的抗干擾性,是一種成功的硬件解決方案。【關鍵詞

2010-04-24 09:05:05

求助!大佬們,問一下用FPGA實現卷積碼編解碼的難度。

2023-10-16 23:26:26

我國靶場測量、工業控制、電力系統測量與保護、計算、通信、氣象等測試設備均采用國際標準IRIG-B格式的時間碼(簡稱B碼)作為時間同步標準。B碼是一種串行的時間格式.分為直流碼(DC碼)和交流碼(AC

2019-08-08 07:25:35

我國靶場測量、工業控制、電力系統測量與保護、計算、通信、氣象等測試設備均采用國際標準IRIG-B格式的時間碼(簡稱B碼)作為時間同步標準。

2019-10-23 08:11:07

本文介紹一種基于FPGA并執行IRIG-B標準的AC/DC編碼技術,與基于MCU或者DSP和數字邏輯電路實現的編碼方法相比,該技術可以大大降低系統的設計難度,降低成本,提高B碼的精確性和系統靈活性。

2021-04-29 06:56:12

ADV611的工作原理是什么?怎樣去實現一種ADV611編解碼方案?

2021-06-04 07:17:07

有木有哪位大俠有FPGA 實現IRIG B碼的quartus 工程文件呀 新手,剛學這個,想找個例子學習下,望大家指導

2013-03-08 16:14:23

求一種基于FPGA滑動相關法偽碼捕獲的研究與實現

2021-04-30 06:52:27

新手,問下看資料不是很懂IRIG_B。。有幾個問題。希望大家可以解答下。。小弟感激不盡。如下:(1)我們主要是用它做什么呢?我的理解的是 我這邊解碼出來以后,以后所有串口、網絡這些發送的信息都帶一個

2016-11-05 09:30:35

RT用labVIEW實現一種RFID編解碼的仿真

2013-05-14 23:21:59

請問怎樣去實現一種基于FPGA的矩陣運算?

2021-06-22 07:00:19

一種基于IRIG-A碼輸出的超小型GPS時鐘設計

2021-05-27 06:24:52

小弟我剛開始學習此方面的內容,對于VHDL還不是很熟悉,希望各位大神拉我一把,給我個IRIG-B解碼的VHDL程序,一次度過難過。。小弟我在此將感激不盡。。

2013-11-09 13:27:47

廣播報時信號嵌入時間碼規范GY T 219-2006

2008-11-22 16:59:09 24

24 在采用一維ST-OOC碼的基礎上,在光CDMA系統編/解碼器端分別加入起/解偏器,引入偏振信息來提高碼字維數,從而得到一種新型光CDMA系統多維碼的構造方法。理論分析表明通過在一

2008-12-16 23:49:48 11

11

介紹用FPGA 設計實現MIL-STD-1553B 總線接口中的曼徹斯特碼編解碼器。該設計采用VHDL 硬件描述語言編程,并用專門的綜合工具Synplify 對設計進行綜合、優化,在MAX+PLUSⅡ進行時序仿

2009-05-15 16:25:50 43

43 變長碼作為一種最流行的數據壓縮技術,已被許多數據壓縮標準,如JPEG,MPEG-2和H.263 等作為編碼方法。但由于解碼過程中的循環依賴性,限制了解碼吞吐率。本文介紹了一種基于

2009-06-09 11:31:41 17

17 本文討論了一種可在FPGA 上實現的FFT 結構。該結構采用基于流水線結構和快速并行乘法器的蝶形處理器。乘法器采用改進的Booth 算法,簡化了部分積符號擴展,使用Wallace 樹結構和4-2

2009-09-11 15:46:40 16

16 DFT 偽碼捕獲算法在進行偽碼搜索的同時估計多普勒頻偏,為了滿足捕獲精度要求,需要增加DFT 點數,但隨著運算點數的增加硬件實現難度成倍增長。本文提出一種基于FPGA 的在不

2009-09-22 09:59:21 12

12 一種基于FPGA 的可重構密碼芯片的設計與實現楊曉輝, 戴紫彬解放軍信息工程大學 電子技術學院,河南 鄭州 450004來源:電子技術應用摘 要: 介紹了SHA-1、SHA224 及SHA256

2010-02-05 08:25:52 36

36 為提高AC碼的調制精度,減小電路板面積,提出基于EPM7160S的IRIG-B(AC)碼調制設計。介紹EPM7160S的結構及特點,詳細闡述IRIG-B碼標準。該設計成功解決了AC碼調制精度問題。這種方法

2010-02-11 11:11:42 39

39 一種BIN 碼與BCD 碼轉換電路的設計與實現

二進制(BIN) 碼與二- 十進制(BCD) 碼的互換在許多測控領域有大量應用, 但大多以軟件方式實現。本文根據一種新的以簡單移位

2010-02-22 15:43:53 23

23 介紹了一種基于DSP和FPGA的GPS-B碼時統終端系統的設計方案,提出了一種利用FPGA對IRIG-B碼進行解碼的設計方法。詳細論述了具體的設計方案及軟硬件的實現。通過將快速的DSP與FPGA相結

2010-02-24 13:48:49 22

22 摘要:本文詳細敘述了基于FPGA及單片機K實現時碼終端系統的設計方法,該系統可用于對國際通用時間格式碼IRIG碼(簡稱B碼)的解調,以及產生各種采樣、同步頻率信號,也可作為

2010-07-12 12:00:56 15

15 介紹了一種采用并行方式構建的多符號可變長碼解碼器。該解碼器通過增加結構的復雜性和對硬件資源的占用,換取可變長碼解碼的高吞吐量。這種結構突破了可變長碼碼字之間的

2010-07-17 15:01:19 17

17 Cyclone 系列芯片是Altera公司推出的低價格、高容量的FPGA,內置M4K存儲塊,最大RAM可達288kb。IRIG-B碼是標準時間碼格式之一,廣泛的應用于靶場時間信息的傳遞和各系統的時間同步。利用Cyc

2010-07-28 16:59:22 51

51 時間同步裝置北斗衛星時鐘是一款高精度時間同步裝置,支持GPS/北斗雙模雙天線,支持主備從配置。系統有著豐富的輸出接口和輸出類型,涵蓋電力自動化所有對時需求,如IRIG-B(DC)、IRIG-B(AC

2024-01-08 16:43:38

威科姆VC-7850-K 電力系統同步擴展時鐘以兩路地面鏈路B碼授時輸入為時間基準,以第一路IRIG-B碼輸入為主用時間基準、第二路IRIG-B碼輸入為備用時間基準,設備與B碼時間基準保持同

2010-08-17 10:18:08 20

20 一、論文總體思路

二、B碼簡介

三、B碼解碼

四、北斗衛星導航系統

2010-10-18 16:22:15 0

0 IRIG碼是一種通用的國際標準傳輸碼,廣泛應用于時統設備之間的時間通信。本時鐘設計采用微控制器,依據GPS時鐘信號對本地晶振進行頻率測量,根據測量結果實時調整時間單元

2009-03-29 15:15:58 1468

1468

摘要: 介紹用FPGA設計實現MIL-STD1553B部接口中的曼徹斯特碼編解碼器。該設計采用VHDL硬件描述語言編程,并且專門的綜合工具Synplify對設計進行綜合、優化,在MA

2011-04-19 21:38:56 1940

1940

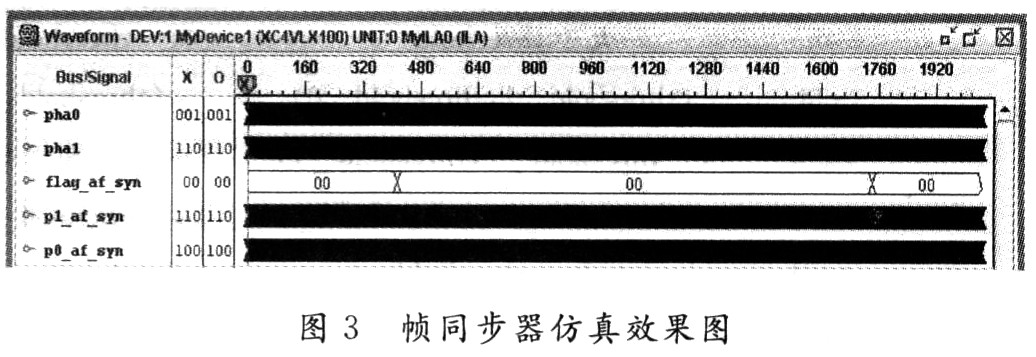

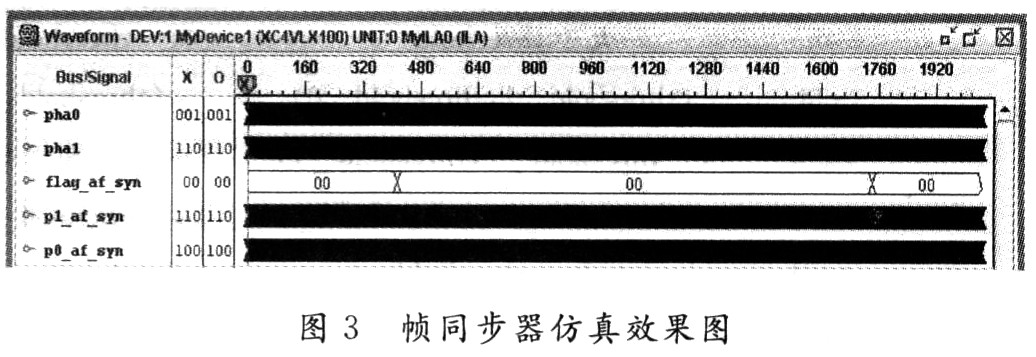

一種高速幀同步和相位模糊估計的方法及其FPGA實現

摘要:提出僅依靠接收符號和本地同步碼快速確定MPSK調制符號的幀同步,并同時估計其相位模糊值的計算方法,給

2010-01-27 09:38:17 1833

1833

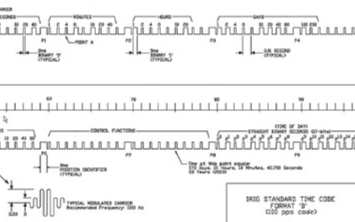

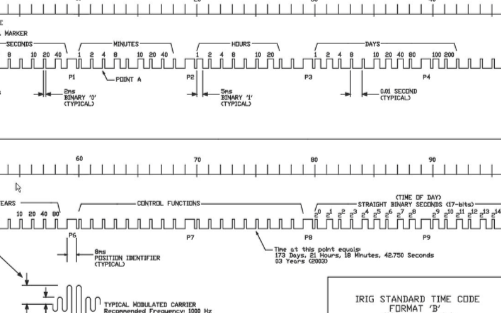

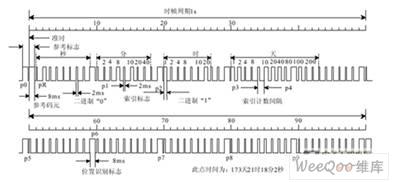

IRIG是美國靶場儀器組的簡稱,美國靶場儀器組是美國靶場司令部委員會的下屬機構。

IRIG時間標準有兩大類:

一類是并行時間碼格式,這類碼由于是并行格式,傳輸距

2010-07-28 17:01:17 2106

2106 隨著變電站自動化技術的發展,對變電站內時間的精確和統一提出了更高的要求。本文提出了一種采用IRIG-B時間碼來對時的方案。在這種對時方案中,每個變電站只安裝一個GPS接收裝置

2011-04-13 15:52:02 45

45 摘要:為提高8B/10B編解碼的工作速度和簡化邏輯方法,提出一種基于FPGA的8B/10B編解碼系統設計方案。與現有的8B/10B編解碼方案相比,該方案是一種利用FPGA實現8B/lOB編解碼的模塊方

2011-05-26 11:08:20 4329

4329

傳統的IRIG-B碼解碼器大多采用單片機來實現,器件較多,結構復雜,在受到外界干擾的情況下還可能出現死機等故障。而采用CPLD設計的解碼器可以大大減少器件的數量、增加解碼器的穩

2011-08-20 15:16:43 6502

6502

SPI 串行總線是一種常用的標準接口,其使用簡單方便而且占用系統資源少,應用相當廣泛。本文將介紹一種新的通用的SPI 總線的FPGA 實現方法。

2011-09-09 11:58:27 67

67 本文提出了一種用FPGA實現糾錯編碼的設計思想,并以Altera MAX+PluslI為硬件開發平臺。利用FPGA編程的特點,用軟件編程方法,很好的解決了糾錯編碼中存在的碼速變換和實時性問題,實現

2011-11-10 17:10:59 61

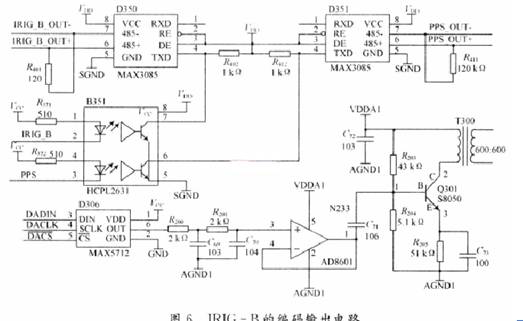

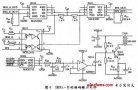

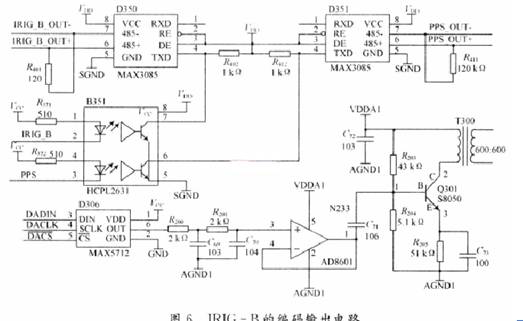

61 IRIG-B 的編碼輸出電路:

2012-04-25 16:29:48 3711

3711

在分析武器裝備靶場試驗測控設備同步技術現狀基礎上,提出了一種多功能內置式IRIG-B碼終端設計;給出了終端的組成、功能與工作過程,詳細介紹了IRIG-B碼采集模塊、IRIG-B碼產生模塊

2012-07-27 16:17:56 0

0 同步時鐘信號是分布式錄波器系統任務順利完成的關鍵。介紹一種利用可編程CPLD器件實現性能優良的分布式同步信號源。通過高度集成,將IRIG-B(DC)解碼器以及系統的各種同步邏輯電路集

2013-09-25 17:42:56 23

23 13曼徹斯特碼編解碼的FPGA設計與實現-9。

2016-04-26 15:12:57 12

12 RS編解碼的FPGA實現-說明RS編解碼的FPGA實現-說明。

2016-05-04 15:59:44 21

21 一種具有查錯功能的10B_8B解碼器設計_鄒陳

2017-01-07 21:39:44 2

2 一種基于FPGA的時鐘相移時間數字轉換器_王巍

2017-01-07 22:23:13 3

3 一種高速卷積編解碼器的FPGA實現

2017-02-07 15:05:00 22

22 一種基于低成本FPGA的高速8B_10B編解碼器設計_陳章進

2017-03-19 11:46:13 1

1 時間系統對于測控設備的正常運行和故障診斷起著至關重要的作用。IRIC -B碼是國際靶場試驗通用的同步時間碼。本文基于IRIC -B碼對某測控設備的時間系統進行設計,并在該設備中成功實現時間同步,精度

2017-11-02 15:44:41 1

1 MSP430系列單片機是集成度高、超低功耗的 16位單片機。Cyclone系列芯片是 Altera公 司推 出的低價格、RAM可達 288kb的高容量的FPGA。IRIG.B碼廣泛應用于靶場時間信息

2017-11-28 14:41:50 4

4 鏈碼是一種以較少的數據存儲表示線條、曲線和區域邊界的編碼技術。為進一步提高鏈碼的壓縮效率,提出了一種新的壓縮頂點鏈碼:改進的正交3方向頂點鏈碼(103DVCC)。I03DVCC將頂點鏈碼(VCC

2017-12-01 10:26:26 0

0 時間信息的采集和處理在現代的各種電子計算系統中都有著關鍵的作用。針對美國靶場儀器組(IRJG)串行時間碼規范較多,格式多變的特性造成的其他時碼采集系統硬件兼容性較差的問題,設計了一種兼容各種格式

2018-02-02 14:20:57 1

1 Cyclone系列芯片是 A ltera公司推出的低價格、RAM 可達 288kb的高容量的 FPGA。 IRIG-B碼廣泛應用于靶場時間信息的傳遞和各系統的時間同步。詳細介紹了IRIG-B碼解碼電路和調制電路的硬件設計。MSP430的軟件采用 C語言編寫, 使程序有很強的可移植性。

2018-05-02 15:32:53 10

10 B碼的各種門電路集成在一個芯片,通過高度集成的系統可以用于產生標準的串行時間碼向測量設備發送,測量設備對接收到的B碼進行解調能產生出系統所需的絕對時間和各種控制信號。此B碼產生系統可作為基地設備檢測調試用,也可作實踐教學設備。

2019-02-06 09:32:00 3726

3726

曼徹斯特碼編碼、解碼器是1553B總線接口中不可缺少的重要組成部分。曼徹斯特碼編解碼器設計的好壞直接影響總線接口的性能。本文介紹的是MIL-STD-1553B接口中最曼徹斯特碼的編碼和解碼器的設計實現。

2019-04-24 08:24:00 5927

5927 在工控行業很多領域中,需要控制系統具有高精度的時間同步功能,IRIG就是美國靶場司令委員會制定的一種時間標準。自EM9X60后,英創EM928x嵌入式主板也實現了IRIG-B碼校時功能。之前的相關

2020-01-17 09:14:45 2078

2078

在工控行業很多領域中,需要控制系統具有高精度的時間同步功能,IRIG就是美國靶場司令委員會制定的一種時間標準,英創在EM928x系列的Linux工控主板上實現了IRIG-B碼校時功能。 IRIG

2020-02-04 10:41:13 2380

2380

介紹了一種讀寫器的編解碼部分由FPGA來完成的設計方案,由FPGA負責前向鏈路的PIE編碼和后向鏈路的FM0/miller 解碼,且解碼模塊可對標簽突發傳來的數據立即檢測并實施解碼,實現了較快的解碼速率。FPGA選用的是Altera公司的 EP1C3T100C6芯片。

2020-07-28 18:54:00 2

2 一種基于FPGA的MSK調制器設計與實現說明。

2021-04-27 14:08:41 22

22 一種基于FPGA的分頻器的實現說明。

2021-05-25 16:57:08 16

16 FPGA_ASIC-一種改進的2D-DCT的FPGA實現(核達中遠通電源技術有限公司招聘文員嗎?)-該文檔為FPGA_ASIC-一種改進的2D-DCT的FPGA實現講解文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-09-16 10:35:54 4

4 基于FPGA的IRIGBDC碼解碼(開關電源技術教程課后習題答案)-該文檔為基于FPGA的IRIGBDC碼解碼講解文檔,是一份還算不錯的參考文檔,感興趣的可以下載看看,,,,,,,,,,,,,,,,,

2021-09-27 15:16:58 22

22 電子發燒友網站提供《一個時間碼觸發的無線燈箱.zip》資料免費下載

2022-12-16 14:14:06 0

0 格雷碼是一種特殊的二進制碼,在結構光三維視覺中,常常被用于編碼。比起我們常見的二進制碼,格雷碼具有相鄰數字的編碼只有一位不同的優點,這個優點對于解碼而言十分重要,可以減少光解碼的錯誤率。下面我們可以看下如何對結構光用格雷碼編碼,并如何對編碼的結構光進行解碼。

2022-12-21 11:14:51 2016

2016 什么是IRIG-B碼對時 IRIG-B(inter-range instrumentationgroup-B)碼是一種時間同步標準,通常用于精確的時間測量和數據同步,廣泛應用于電力、通信、航空等領域

2024-03-07 09:55:46 1550

1550

Embedded Workbench ARM 8.11.2 硬件平臺:創龍科技TLFM20S-EVM評估板(基于FMQL20S400M國產平臺) IRIG-B碼對時原理 IRIG-B(inter-range instrumentationgroup-B)碼是一種時間同步標準,通常用于精確的時

2025-02-27 10:22:23 1596

1596

GPS衛星同步時鐘以GPS信號作為時間源,同時可選北斗衛星、IRIG-B碼、OCX0、銣原子鐘、CDMA信號等時鐘源,對時精度達20nS。

2025-03-10 14:09:27 688

688

GPS授時裝置接收北斗衛星、GPS衛星、CDMA、SDH、PTP、IRIG-B碼、串口等外部時間基準信號,通過智能時間源算法,實現多時間源的智能切換,輸出高精度、高可靠的時間同步信號和標準時間信息。

2025-06-16 14:55:01 559

559

SYN1502A型IRIG-B碼產生器是西安同步電子科技有限公司自主研發的高精度授時設備,以“便攜性、多功能性、高可靠性”為設計核心,兼顧操作便捷性與功能靈活性,為時間同步提供新方案。 一、產品概述

2025-06-23 18:10:49 497

497 在當今數字化時代,眾多領域對時間同步的精度和可靠性有著極高的要求。SYN1502A型IRIG-B碼產生器作為一款專業的時間同步模塊設備,在滿足客戶多樣化需求、解決實際問題方面發揮著重要作用。 在航天

2025-06-23 18:12:16 398

398

電子發燒友App

電子發燒友App

評論