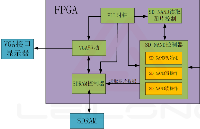

本文主要詳解基于FPGA的模糊PID控制器的設計實現,首先介紹了FPGA工作原理、基本特點以及FPGA的優勢,其次闡述了使用Altera的FPGA設計實現的數字模糊PID控制器,具體的跟隨小編一起來了解一下。

2018-06-01 09:26:51 18186

18186 ? ? Xilinx zynq系列FPGA實現神經網絡評估 本篇目錄 1. 內存占用 ??? 1.1?FPGA程序中內存的實現方式 ????1.2?Zynq的BRAM內存大小 ????1.3?一個

2022-07-10 09:24:45 2511

2511 FPGA(現場可編程門陣列)作為信號源的主要平臺,利用DDFS技術產生一個按指數衰減的頻率可調正弦衰減信號。

2019-06-24 06:18:55

FPGA(Field-Programmable Gate Array,現場可編程門陣列)是一種特殊的集成電路,其內部結構由大量的可配置邏輯塊和互連線組成。FPGA可以通過編程來實現各種數字系統功能

2024-01-26 10:03:55

求各位大神幫我看看這個程序對不對,要做一個DDFS信號源,利用單片機做波形存儲器,想用單片機的PI口接收數據,P3口發送數據,電路跟程序如圖所示:

2016-12-19 22:11:19

通過編程來改變內部結構的芯片。FPGA 功能實現:需要通過編程即設計硬件描述語言,經過 EDA 工具編譯、

2022-01-25 06:45:52

求各位大神幫我看看這個程序對不對,要做一個DDFS信號源,利用單片機做波形存儲器,想用單片機的PI口接收數據,P3口發送數據,電路跟程序如圖所示:

2016-12-20 10:17:15

作者:丁小汀(北京交通大學電子信息工程學院北京100044)摘要:直接數字頻率合成具有一系列優點,如頻率切換速度快、頻率分辨力高、頻率和相位易于控制等。DDFS可以產生各種所需要的波形。根據直接數字

2019-06-21 07:45:05

,輸出不同幅度的信號等。而實現頻率合成方法有許多種,但基本上可以歸納為直接頻率合成和間接頻率合成兩大類方法。采用傳統的頻率合成技術要實現上述要求,幾乎是不可能的。

2019-11-04 08:00:46

DDFS的原理和特點是什么?基于CPLD的函數信號發生器設計

2021-05-08 08:44:40

為了比較DSP和SOPC技術在電子設計領域的應用,采用泰勒展開法和DDFS技術,分別給出設計方案的硬件電路結構和軟件流程圖,并通過集成開發環境CCS和DE2開發板實現正弦信號發生器。結果表明,采用

2021-05-12 06:15:43

,輸出不同幅度的信號等。而實現頻率合成要領有許多種,但基本上可以歸納為直接頻率合成和間接頻率合成兩大類要領 。采用傳統的頻率合成技能要實現上述要求,幾乎是不可能的。DDFS技能 是自21世紀70年代出現的一種新型的直接頻率合成技能 。

2019-08-22 06:29:22

或DDFS)得到了飛速的發展,它以有別于其它頻率合成方法的優越性能和特點成為現代頻率合成技術中的姣姣者。

2019-08-21 07:45:04

DDS的基本原理是什么,有什么性能指標?基于FPGA的DDFS與DDWS兩種實現方式

2021-04-30 06:13:06

我們要搞個電子實驗。。。 老師叫我們搞激光測速儀 , 但為什么會有這么多電路模塊1.程控升壓電路

2.熱敏電阻測溫電路

3.DS18B20測溫電路

4.相位差測量電路

5.基于DDFS的信號發生電路

6.調制激光源

7.恒溫控制器

我們小組是想搞恒溫控制器但實在搞不懂這些是干嘛的!

2016-12-19 18:05:07

DDFS技術原理是什么?DDFS的FPGA實現的參數怎樣去計算?如何利用FPGA去實現DDFS?

2021-04-28 07:01:29

文中介紹一種基于DDFS(直接頻率合成)技術的可編程音頻儀器測試信號源設計。

2021-05-10 06:05:17

西安交通大學電信學院 周俊峰 陳濤摘要:介紹了Altera公司的即FPGA器件ACEXEPlK50的主要特點,給出了由ACEXEPlK50實現直接數字頻率合成的工作原理、設計思路、電路結構和改進優化

2019-06-18 06:05:34

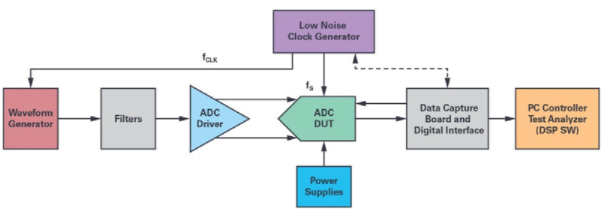

的激勵信號源通常是由函數信號發生器提供,但往往難以兼顧寬頻帶、寬幅度范圍和低諧波失真,因此需自行設計信號源實現既定信號輸出。基于直接數字頻率合成DDFS(Direct Digital Frequency Synthesize)技術,依據調制信號相關原理,設計出一種基于DDS的正弦信號發全文下載

2010-04-24 09:04:53

提升小波的FPGA實現

2009-05-08 17:23:38 9

9 本文介紹一種利用單片機、可編程邏輯器件CPLD 和波形存儲器EPROM 組成基于DDFS技術的高精度、寬變頻高載波、全數字SPWM 波形發生器。介紹SPWM 波形的數字計算方法以及采用CPLD 構成DD

2009-08-27 10:44:45 71

71 提出了一種基于FPGA 實現QPSK 調制器的方法。以FPGA 實現DDS,通過對DDS 信號輸出相位的控制實現調相。仿真結果表明方案是可行的。

2009-12-18 11:57:08 66

66 本文介紹基于FPGA 和DDFS 技術,應用Altera 公司的FPGA 開發工具DSP Builder 設計數字移相信號發生器,該數字移相信號發生器的頻率、相位、幅度均可預置,分辨率高,精確可調。且可分

2009-12-18 11:59:54 44

44 本文介紹了直接數字頻率合成器(DDFS:Direct Digital Frequency Synthesizer)的基本工作原理、主要誤差源及改善方法,在此基礎上著重討論了壓縮數據以等效增加數據容量的Sunderland 算

2009-12-25 12:41:46 19

19 基于直接數字頻率合成DDFS(Direct Digital Frequency Synthesize)技術,依據調制信號相關原理,設計以DDS集成電路AD9851為核心的正弦信號發生器,可精確輸出幅度調節范圍為50mV PP ~20V

2010-02-10 16:37:04 100

100 基于FPGA的DDS信號源設計與實現

利用DDS和 FPGA 技術設計一種信號發生器.介紹了該信號發生器的工作原理、 設計思路及實現方法.在 FPGA 器件上實現了基于 DDS技

2010-02-11 08:48:05 228

228 FPGA實現DSP應用

摘要:具有系統級性能的FPGA在半導體工藝的線寬達到深亞微米后更進一步按信號處理的要求改進器件結構和性能,不僅可實現VLSI DSP,且具有系統

2010-04-01 15:39:54 14

14 為進行高精度信號源的設計,同時降低設計成本,以Cyclone II系列低端FPGA為核心,利用直接頻率合成技術,對正弦信號等數據進行1/4周期壓縮存儲到ROM中,在外部時鐘頻率為50 MHz,實

2010-12-11 15:31:30 33

33 提出一種基于DCT域的數字水印算法,并用FPGA硬件實現其中關鍵部分DCT變換。采用VHDL語言有效設計和實現DCT變換,分析與仿真結果表明:與軟件實現相比,用FPGA實現水印算法具有高

2010-12-28 10:22:14 20

20 摘要: 介紹了DDFS的原理和Altera公司的FPGA器件ACEX 1K的主要特點,給出了用ACEX 1K系列器件EP1K10TC144-1實現數字頻率合成器的工作原理、設計思路、電路結構和仿真結

2009-06-20 14:02:25 1171

1171

FPGA 重復配置和測試的實現

從制造的角度來講,FPGA測試是指對FPGA器件內部的邏輯塊、可編程互聯線、輸入輸出塊等資源的檢測。完整的FPGA測試包括

2009-09-03 11:17:08 725

725

基于CycloneII系列FPGA的DDFS信號源實現

0 引言

在電子信息領域,函數發生器(信號源)是通用的設備。近年來電子信息技術的飛速發展,使得各領域對信號源的要

2009-12-14 11:16:51 1538

1538

FPGA重復配置和測試的實現

從制造的角度來講,FPGA測試是指對FPGA器件內部的邏輯塊、可編程互聯線、輸入輸出塊等資源的檢測。完整的FPGA測試包括兩步,一是配置FPGA

2010-01-26 09:39:56 690

690

DDS(Direct Digital Freqiaency Synthesizers)廣泛應用于雷達系統、數字通信、電子對抗、電子測量等民用軍用設備中。它是隨著半導體技術和數字技術的快速發展而發展起來的新型的頻率合成

2010-09-29 10:40:57 6690

6690

本系統以單片機和FPGA為控制核心,由DTMF信號合成模塊與DTMF信號的識別模塊構成。DTMF信號的合成是以直接數字頻率合成技術(DDFS)為基礎,根據按下鍵值,在FPGA內部合成一個雙頻數字信

2011-04-27 11:13:40 87

87 在基于DDFS 方法的任意函數發生器中,合成波形除了正弦波外,還包含各種非正弦波形。對于合成正弦波形,可以使用插值方法降低波表需求,然而對于非正弦波形,由于波形復雜,一般都采用

2011-09-07 19:00:12 47

47 隨著微電子技術的迅速發展,直接數字頻率合成器(Direct Digital Frequency Synthesis簡稱DDS或DDFS)得到了飛速的發展,它以有別于其它頻率合成方法的優越性能和特點成為現代頻率合成技術中

2012-03-30 11:38:22 3256

3256 本文介紹了一種利用FPGA實現DC~100 MHz的自動切換量程數字等精度頻率計的實現方法,并給出實現代碼。整個系統在研制的CPLD/FPGA實驗開發系統上調試通過。

2012-12-03 11:17:51 6495

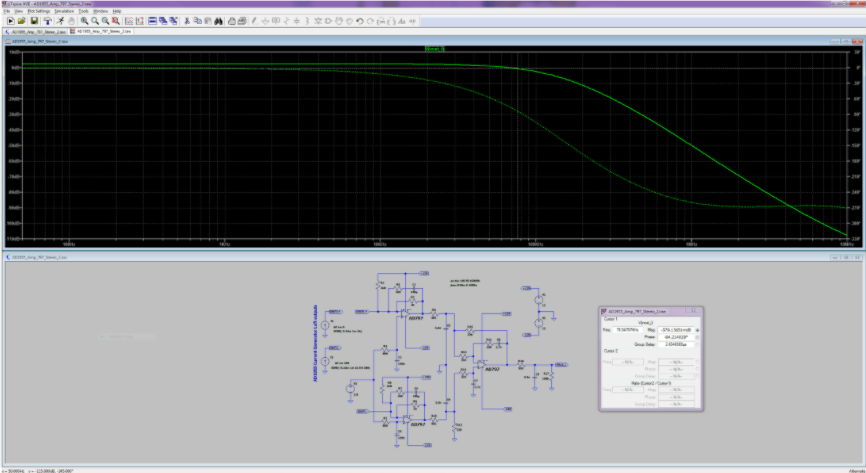

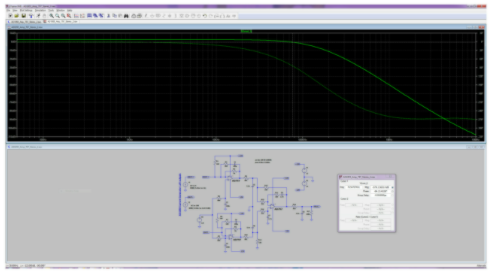

6495 文中介紹一種基于DDFS(直接頻率合成)技術的可編程音頻儀器測試信號源設計。該系統采用單片機作為控制器,以FPGA(現場可編程門陣列)作為信號源的主要平臺,利用DDFS技術產生一

2013-05-06 11:40:23 23

23 基于FPGA的開方運算實現 ,的技術論文

2015-10-30 10:59:01 5

5 基于FPGA實現POWERlink的方案

2015-11-17 15:55:08 19

19 ECT圖像重建算法的FPGA實現

ECT圖像重建算法的FPGA實現

2015-11-19 14:59:41 2

2 本書比較全面地闡述了fpga在數字信號處理中的應用問題。本書共分8章,主要內容包括典型fpga器件的介紹、vhdl硬件描述語言、fpga設計中常用軟件簡介、用fpga實現數字信號處理的數據規劃、多種

2015-12-23 11:07:46 47

47 dac0832ad08098259a,825382508255等芯片的fpga實現及仿真

2016-01-20 15:12:47 13

13 RS編解碼的FPGA實現-說明RS編解碼的FPGA實現-說明。

2016-05-04 15:59:44 21

21 基于FPGA的視頻字符疊加的設計與實現。

2016-05-10 17:46:07 30

30 基于FPGA的萬兆以太網接口的設計與實現。

2016-05-11 09:46:01 39

39 Xilinx FPGA工程例子源碼:在FPGA上實現CRC算法的程序

2016-06-07 15:07:45 28

28 Xilinx FPGA工程例子源碼:用FPGA實現數字鎖相環

2016-06-07 15:07:45 38

38 基于FPGA的JPEG解碼算法的研究與實現

2016-08-29 16:05:01 11

11 基于FPGA技術的數字相關器的設計與實現

2016-12-16 22:23:00 14

14 每個FPGA芯片(FPGA)是由有限個帶有可編程連接預定義資源組成。這些互連資源通過LabVIEW FPGA模塊實現用戶設計的數字電路。用戶創建FPGA VI時設計一個電路示意圖,以說明FPGA邏輯

2017-11-18 05:57:01 1138

1138

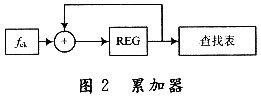

數字頻率合成技術[2](Direct Digital Frequency Synthesis,DDFS)于1971年被J.Tierney首次提出。DDFS采用數字技術,以相位為出發點進行頻率的合成

2018-06-22 14:55:00 4522

4522

頻率合成技術 (Direct Digital Frequency Synthesis,DDFS)于1971年被J.Tierney首次提出。DDFS采用數字技術,以相位為出發點進行頻率的合成,具有高

2018-07-26 15:30:45 1322

1322

近年來,隨著通信系統的發展,人們對信號源的要求越來越高,直接數字頻率合成器(Direct Digital Frequency Synthesis簡稱DDS或DDFS)正是在這樣的背景下進一步得到了發展。它具有相對帶寬、頻率分辨率高、頻率轉換時間短、控制靈活和全數字化的優點,并且成本低,功耗小。

2019-05-05 08:20:00 3388

3388

建立了一個基于FPGA的可實現流水化運行的OFDM系統的硬件平臺,包括模擬前端、基于FPGA的OFDM調制器和OFDM 解調器。重點給出了OFDM調制解調器的實現構架,對FPGA實現方法進行了詳細的描述,介紹了系統調試方法,并對系統進行了性能評價。

2018-12-13 16:45:51 22

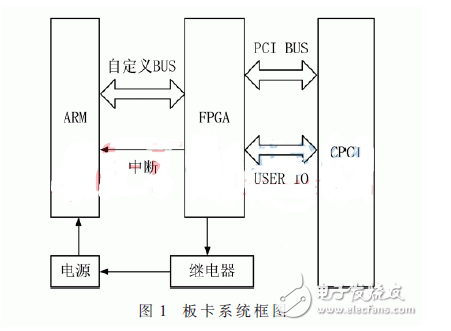

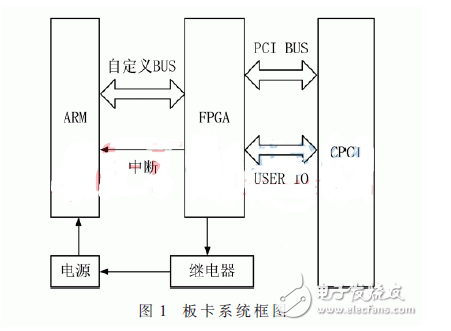

22 本文提出了一種基于FPGA的CPCI系統的設計和實現,使用廉價FPGA芯片實現CPCI通信協議,同時利用FPGA的可編程特性實現電源控制、靈活中斷、外部觸發、外部通信等特殊應用的功能,解決了CPCI協議經過CPCI橋時的沖突問題。

2019-01-06 11:37:13 3401

3401

討論了利用FPGA工具實現MBUS總線的原理、方法,以實際操作介紹了FPGA設計流程,并給出FPGA常用設計技巧。

2019-12-24 14:54:08 9

9 直接數字頻率合成技術(DirectDigitalFrequencySynthesi,即DDFS一般簡稱DDS)是從相位直接合成所需波形的一種新的頻率合成技術。近年來,直接數字頻率合成器由于其具有頻率

2020-01-03 08:00:00 2

2 用FPGA實現抽取濾波器比較復雜,主要是因為在FPGA中缺乏實現乘法運算的有效結構,現在,FPGA中集成了硬件乘法器,使FPGA在數字信號處理方面有了長足的進步。本文介紹了一種采用Xilinx公司的XC2V1000實現FIR抽取濾波器的設計方法。

2020-09-25 10:44:00 3

3 實現這一編程思想的轉變,是因為 FPGA 借助 OpenCL 實現了編程,程序員只需要通過 C/C++ 添加適當的 pragma 就能實現 FPGA 編程。為了讓您用 OpenCL 實現的 FPGA

2020-07-16 17:58:28 7215

7215

開方運算作為數字信號處理(DSP)領域內的一種基本運算,其基于現場可編程門列(FPGA)的工程實現具有較高的難度。本文分析比較了實現開方運算的牛頓-萊福森算法,逐次逼近算法,非冗余開方算法3種算法

2020-08-06 17:58:15 6

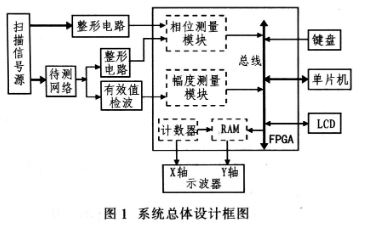

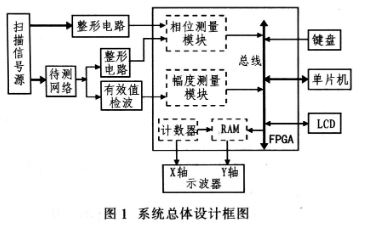

6 該系統以單片機和FPGA為控制核心,用DDFS技術產生頻率掃描信號,采用真有效值檢測器件AD637測量信號幅度。在FPGA中,采用高頻脈沖計數的方法測量相位差,經過單片機運算,可得到100 Hz

2020-08-07 10:28:52 1903

1903

本文檔的主要內容詳細介紹的是怎么樣才能使用FPGA實現數字系統內容包括了:FPGA簡介,為什么采用FPGA,開發平臺和設計工具,HDL(硬件描述語言),FPGA的設計原則,系統設計開發流程。

2020-08-11 15:29:00 9

9 在FPGA中,實現邏輯的基本單元是查找表(LUT)而非基本門電路。目前的FPGA中,單一LE或者Cell通常能實現至少4輸入查找表的邏輯功能。

2020-12-29 17:27:22 14

14 本文檔的主要內容詳細介紹的是基于FPGA的AD采樣的實現免費下載。

2021-01-21 15:33:54 32

32 基于FPGA的定點LMS算法的實現講解。

2021-04-28 11:17:25 15

15 基于FPGA的TCP/IP協議的實現說明。

2021-04-28 11:19:47 54

54 基于FPGA的SoftSerdes設計與實現講解說明。

2021-04-28 11:18:38 6

6 基于FPGA的電機測速的設計與實現介紹說明。

2021-06-01 09:39:16 11

11 基于FPGA的UART模塊設計與實現介紹說明。

2021-06-01 09:43:30 20

20 基于FPGA的無線通信系統設計與實現

2021-06-16 09:59:29 46

46 基于FPGA的簡易頻譜儀設計與實現

2021-06-16 10:01:36 67

67 基于新型FPGA的FFT設計與實現設計方法。

2021-06-17 17:07:03 49

49 FPGA的ROM實現(qt嵌入式開發編程)-該文檔為FPGA的ROM實現簡介資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-30 08:58:50 5

5 基于FPGA的ROM的實現簡介(嵌入式開發工程師培訓學校)-該文檔為基于FPGA的ROM的實現簡介資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-30 09:08:40 5

5 基于FPGA的ROM的實現的講解(如何制作嵌入式開發板)-該文檔為基于FPGA的ROM的實現的講解文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 15:27:41 3

3 基于FPGA的ROM的實現講解(嵌入式開發入門書籍下載)-該文檔為基于FPGA的ROM的實現講解文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 15:36:26 2

2 基于FPGA的ROM實現(如何制作嵌入式開發板)-該文檔為基于FPGA的ROM的實現總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 16:26:06 6

6 基于FPGA的ROM的實現(arm嵌入式開發實例電子版)-該文檔為基于FPGA的ROM的實現總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-08-04 10:08:40 9

9 FPGA_ASIC-MAC在FPGA中的高效實現(理士電源技術有限公司)-該文檔為FPGA_ASIC-MAC在FPGA中的高效實現講解文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-08-04 19:03:13 8

8 DDC_FPGA實現(通信電源技術期刊投稿)-該文檔為DDC_FPGA實現總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-08-31 18:29:26 14

14 基于FPGA的SPI協議及設計實現博主微信:flm13724054952,不懂的有疑惑的也可以加微信咨詢,歡迎大家前來投稿,謝謝!引言介紹在電子通信領域里采用的通信協議有IIC,SPI,UART

2021-11-05 19:05:59 24

24 由于浮點運算對于需要高精度和/或高動態范圍的應用至關重要,因此如今的 SHARC+ DSP 處理器,如低成本ADSP-21571或 SoC ADSP-SC571(ARM 和 SHARC)是實時處理高達 10 MSPS 的聚合采樣率的事實標準。

2022-06-06 14:43:05 1565

1565

在標準評估板上進行的初步和開箱即用測試表明,基于處理器的 DDS 技術可用于具有頂級性能的傳統正弦波 CW 生成。

2022-07-24 16:39:42 2098

2098

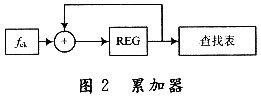

相位累加器寄存器的輸出代表生成波形的當前相位。由于相位到正弦或相位到余弦映射器引擎,每個離散累加器輸出相位值隨后被轉換為幅度正弦或余弦數據或樣本。

2022-07-24 16:51:14 2108

2108

在本系列的第1部分中,我們將了解如何設計基于直接數字頻率合成(DDFS)原理的非常精確的正弦波發生器,但在浮點DSP處理器上通過軟件實現。在第 2 部分中,我們將介紹如何在軟件中實現高精度 NCO。

2022-11-28 17:06:37 2110

2110

FPGA實現SPI協議

2023-03-20 10:35:02 2

2 文章目錄0、前言1、目標2、圖片的預處理3、SDNAND的預處理4、FPGA實現4.1、詳細設計4.2、仿真4.3、實驗結果·前言在上一篇文章《基于FPGA的SD卡的數據讀寫實現

2023-01-07 10:42:00 1604

1604

FPGA 是一種偽通用計算加速器,與 GPGPU(通用 GPU)類似,FPGA 可以很好地卸載特定類型的計算。從編程角度上講,FPGA 比 CPU 更難,但從工作負載角度上講 FPGA 是值得的:和 CPU 基線相比,好的 FPGA 實現可以提供數量級的性能和能量優勢。

2023-12-29 10:29:17 988

988

電子發燒友App

電子發燒友App

評論