流水線是為了提高效率,能并發(fā)同時進(jìn)行多個任務(wù)。

2023-09-05 15:39:56 3344

3344

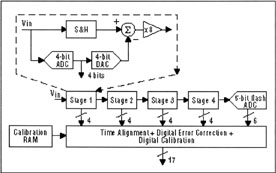

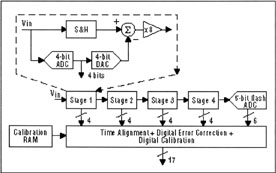

低采樣速率ADC仍然采用逐次逼近(SAR)、積分型結(jié)構(gòu)以及最近推出的過采樣ΣΔADC,而高采樣速率(幾百M(fèi)SPS以上)大多用閃速ADC及其各種變型電路。然而,最近幾年各種各樣的流水線ADC已經(jīng)在速度

2023-09-26 10:24:32 2542

2542

是比較穩(wěn)妥的做法。第三使用流水線的優(yōu)缺點(diǎn)1)優(yōu)點(diǎn): 流水線縮短了在一個時鐘周期內(nèi)給的那個信號必須通過的通路長度,增加了數(shù)據(jù)吞吐量,從而可以提高時鐘頻率,但也導(dǎo)致了數(shù)據(jù)的延時。舉例如下:例如:一個 2 級

2020-10-26 14:38:12

訪問)。

特點(diǎn):

每級流水線功能獨(dú)立,硬件單元分工明確。

吞吐量較高(理想情況下每個周期完成一條指令)。

但層級更多,硬件復(fù)雜度略高,動態(tài)功耗較大。

2級流水線(Cortex-M0+)

合并為以下

2025-11-21 07:35:31

流水線技術(shù)基本原理是什么?設(shè)計DSP流水線應(yīng)注意哪些問題?

2021-04-28 06:10:03

本帖最后由 eehome 于 2013-1-5 09:44 編輯

流水線指令及RISC

2012-08-17 15:49:58

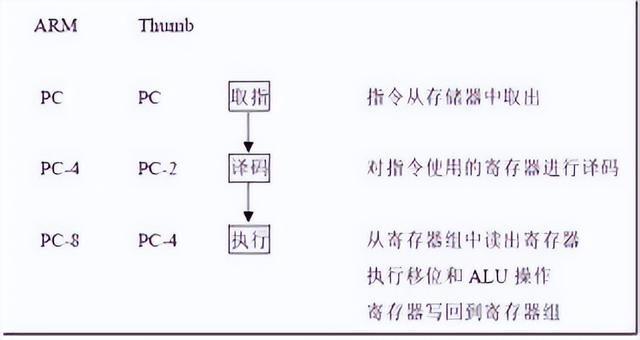

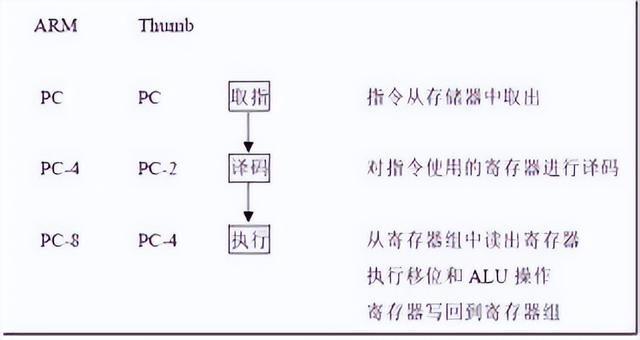

看到匯編中很多關(guān)于程序返回與中斷返回時處理地址都很特別,仔細(xì)想想原來是流水線作用的效果。所以,決定總結(jié)學(xué)習(xí)下ARM流水線。ARM7處理器采用3級流水線來增加處理器指令流的速度,能提供0.9MIPS

2021-07-16 06:53:06

系列 如圖1所示,它有 3 級流水線。它可以在3個周期內(nèi)完成它的過程。它具有基本的 FETCH-DECODE-EXECUTE(F&E) 循環(huán)。這就是為什么 ARM 7 的吞吐量低于其其他

2022-04-11 17:23:19

C66 的DSP核有幾級流水線的概念嗎? 如果有該怎么理解,是幾級流水線?

2018-06-21 01:28:01

有的單核RISC-V MCU支持四級流水線,有的只支持三級流水線,是不是級數(shù)越多,帶來的開銷越大,功耗也越高呢?

2024-05-20 16:01:17

了觸發(fā)器,數(shù)據(jù)的采集需要發(fā)生在時鐘上升沿),總處理數(shù)據(jù)的吞吐量增加了。流水線改造實(shí)例接下來我們用一個很簡單的例子來說明如何對電路進(jìn)行簡單的流水線改造,假設(shè)我們現(xiàn)在要實(shí)現(xiàn)(4*a+6*b)-10,那么我們

2019-12-05 11:53:37

如何理解fpga流水線

2015-08-15 11:43:23

前段時間發(fā)了個關(guān)于fpga的PID實(shí)現(xiàn)的帖子,有個人說“整個算法過程說直白點(diǎn)就是公式的硬件實(shí)現(xiàn),用到了altera提供的IP核,整個的設(shè)計要注意的時鐘的選取,流水線的應(yīng)用”,本人水平有限,想請教一下其中時鐘的選取和流水線的設(shè)計應(yīng)該怎么去做,需要注意些什么,請大家指導(dǎo)一下。

2015-01-11 10:56:59

可重構(gòu)平臺下AES算法的流水線性能怎么優(yōu)化?

2021-04-28 06:46:52

以降低系統(tǒng)速度為代價。從FPGA發(fā)展趨勢和DSP運(yùn)算要求看,系統(tǒng)速度指標(biāo)的意義比面積指標(biāo)更趨重要,需要我們進(jìn)一步深入研究提高芯片的最高工作速度的設(shè)計策略。我們需要討論一下基于FPGA的DSP系統(tǒng)設(shè)計中的流水線技術(shù)主要應(yīng)用在哪些方面?

2019-08-02 06:03:48

本文討論一種新型的VLD解碼結(jié)構(gòu),它通過并行偵測多路碼字,將Buffer中的多個可變長碼一次讀出,這將極大地提高VLD的吞吐量和執(zhí)行效率。然后采用FPGA對這種并行VLD算法的結(jié)構(gòu)進(jìn)行驗(yàn)證,最終得出相應(yīng)結(jié)論。

2021-04-28 06:08:06

如何計算延遲和吞吐量?在ISE時序報告中,我們發(fā)現(xiàn)一個名為“最大組合路徑延遲”的參數(shù)是否與最大時鐘頻率有關(guān)?

2020-03-19 08:55:39

本文設(shè)計的FFT處理器,基于FPGA技術(shù),由于采用移位寄存器流水線結(jié)構(gòu),實(shí)現(xiàn)了兩路數(shù)據(jù)的同時輸入,相比傳統(tǒng)的級聯(lián)結(jié)構(gòu),提高了蝶形運(yùn)算單元的運(yùn)算效率,減小了輸出延時,降低了芯片資源的使用。

2021-04-28 06:32:30

流水線模數(shù)轉(zhuǎn)換器(ADC)有哪些優(yōu)點(diǎn)?流水線ADC中常用的運(yùn)算放大器有哪些?流水線ADC的放大器結(jié)構(gòu)及工作原理是什么?

2021-04-22 06:18:28

如何通過觸發(fā)模型提高吞吐量?

2021-05-11 07:00:31

提高BLE吞吐量的可行辦法如何實(shí)現(xiàn)更快的BLE吞吐量

2021-01-18 06:26:29

基于FPGA的64位流水線加法器的設(shè)計基本要求: FPGA 可自行選擇可實(shí)現(xiàn)64位無符號數(shù)的加法運(yùn)算8級流水線深度

2014-12-18 11:00:42

流水線技術(shù)是提高系統(tǒng)吞吐率的一項(xiàng)強(qiáng)大的實(shí)現(xiàn)技術(shù),并且不需要大量重復(fù)設(shè)置硬件。20世界60年代早期的一些高端機(jī)器中第一次采用了流水線技術(shù)。第一個采用指令流水線的機(jī)器是IBM7030(又稱

2023-03-01 17:52:21

隨著互聯(lián)網(wǎng)的迅速發(fā)展,計算機(jī)日益成為人們生活中不可或缺的部分。伴隨著網(wǎng)絡(luò)業(yè)務(wù)的豐富,用戶對計算機(jī)網(wǎng)卡的要求也越來也高。如何對計算機(jī)網(wǎng)卡吞吐量進(jìn)行合理的測試,已越來越成為眾多計算機(jī)網(wǎng)卡生產(chǎn)廠家日益關(guān)注

2013-12-23 11:07:09

在ARM中,關(guān)于 LDR流水線,分支流水線,中斷流水線,其和 PC 之間的關(guān)系一直沒整明白,求大神詳解!!!

2019-04-30 07:45:25

請問一下高速流水線浮點(diǎn)加法器的FPGA怎么實(shí)現(xiàn)?

2021-05-07 06:44:26

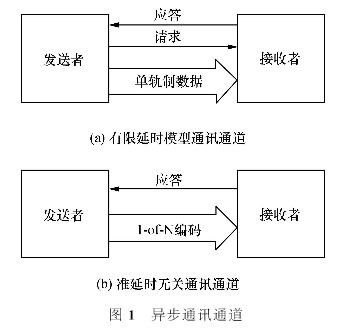

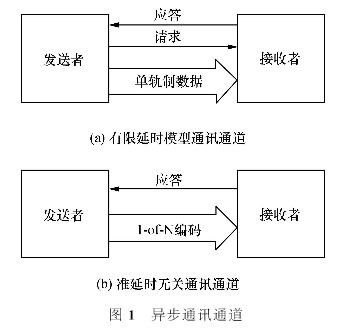

為了進(jìn)一步提高FF H1異步通信吞吐量,本文在原有優(yōu)化算法[1]的基礎(chǔ)上,提出了基于異步窗口碎片合理分布的RDA吞吐量優(yōu)化算法,并通過具體實(shí)例說明了該優(yōu)化算法在實(shí)際工程中

2009-09-03 09:17:32 9

9 使用軟件仿真硬件流水線是很耗時又復(fù)雜的工作,仿真過程中由于流水線的沖突而導(dǎo)致運(yùn)行速度緩慢。本文通過對嵌入式處理器的流水線, 指令集, 設(shè)備控制器等內(nèi)部結(jié)構(gòu)的分析和

2009-12-31 11:30:21 9

9 FPGA重要設(shè)計思想及工程應(yīng)用之流水線設(shè)

流水線設(shè)計是高速電路設(shè)計中的一 個常用設(shè)計手段。如果某個設(shè)計的處理流程分為若干步驟,而且整個數(shù)據(jù)處理 流程分

2010-02-09 11:02:20 52

52 介紹了補(bǔ)碼陣列乘法器的Pezaris 算法。為提高運(yùn)算速度,利用流水線技術(shù)進(jìn)行改進(jìn),設(shè)計出流水線結(jié)構(gòu)陣列乘法器,使用VHDL語言建模,在Quartus II集成開發(fā)環(huán)境下進(jìn)行仿真和功能驗(yàn)證

2010-08-02 16:38:00 0

0 流水線ADC

低采樣速率ADC仍然采用逐次逼近(SAR)、積分型結(jié)構(gòu)以及最近推出的過采樣ΣΔADC,而高采樣速率(幾百M(fèi)SPS以上)大多用閃速ADC及其各種變型電路。然而

2009-02-08 11:02:50 10420

10420

基于流水線技術(shù)的并行高效FIR濾波器設(shè)計

基于流水線技術(shù),利用FPGA進(jìn)行并行可重復(fù)配置高精度的FIR濾波器設(shè)計。使用VHDL可以很方便地改變?yōu)V波器的系數(shù)和階數(shù)。在DSP中采用

2009-03-28 15:12:27 995

995

摘要: 介紹了3DES加密算法的原理并詳盡描述了該算法的FPGA設(shè)計實(shí)現(xiàn)。采用了狀態(tài)機(jī)和流水線技術(shù),使得在面積和速度上達(dá)到最佳優(yōu)化;添加了輸入和輸出接口的設(shè)

2009-06-20 15:22:28 1342

1342

什么是流水線技術(shù)

流水線技術(shù)

2010-02-04 10:21:39 4305

4305 高速流水線浮點(diǎn)加法器的FPGA實(shí)現(xiàn)

0 引言現(xiàn)代信號處理技術(shù)通常都需要進(jìn)行大量高速浮點(diǎn)運(yùn)算。由于浮點(diǎn)數(shù)系統(tǒng)操作比較復(fù)雜,需要專用硬件來完成相關(guān)的操

2010-02-04 10:50:23 2778

2778

防火墻術(shù)語-吞吐量

術(shù)語名稱:吞吐量

術(shù)語解釋:網(wǎng)絡(luò)中的數(shù)據(jù)是由一個個數(shù)據(jù)包組成,防火

2010-02-24 11:06:06 1632

1632 流水線操作,應(yīng)用處理器,應(yīng)用處理器的結(jié)構(gòu)和原理是什么?

與哈佛結(jié)構(gòu)相關(guān),DSP芯片廣泛采用流水線以減少指令執(zhí)行時間.從而增強(qiáng)

2010-03-26 15:03:48 1380

1380 流水線中的相關(guān)培訓(xùn)教程[1]

學(xué)習(xí)目標(biāo)

理解流水線中相關(guān)的分類及定義;

2010-04-13 15:56:08 1244

1244 流水線中的相關(guān)培訓(xùn)教程[3]

(1) 寫后讀相關(guān)(RAW:Read After Write) (命名規(guī)則) :j 的執(zhí)行要用到 i 的計算結(jié)果,當(dāng)它們在流水線中重疊執(zhí)行時,j 可

2010-04-13 16:02:57 1025

1025 流水線中的相關(guān)培訓(xùn)教程[4]

下面討論如何利用編譯器技術(shù)來減少這種必須的暫停,然后論述如何在流水線中實(shí)現(xiàn)數(shù)據(jù)相關(guān)檢測和定向。

2010-04-13 16:09:15 5088

5088 摘要:YHFT-DX是國防科技大學(xué)設(shè)計的一款高性能定點(diǎn)DSP。論文設(shè)計并實(shí)現(xiàn)了YHFT-DX指令控制流水線,提出了在YHFT-DX超長指令字結(jié)構(gòu)中跨取指包邊界派發(fā)和指令預(yù)取的方法,有效提升了流水線的性能。對指令流水線進(jìn)行了高頻結(jié)構(gòu)優(yōu)化,將派發(fā)部件的關(guān)鍵路徑延時壓

2011-02-28 15:22:52 36

36 基于流水線技術(shù),利用FPGA進(jìn)行并行可重復(fù)配置高精度的 FIR濾波器 設(shè)計。使用VHDL可以很方便地改變?yōu)V波器的系數(shù)和階數(shù)。在DSP中采用這種FIR濾波器的設(shè)計方法可以充分發(fā)揮FPGA的優(yōu)勢。

2011-07-18 17:09:28 63

63 為了提高快速傅里葉變換( FFT)處理數(shù)據(jù)的實(shí)時性,本文利用現(xiàn)場可編程陣列( FPGA)邏輯資源豐富、運(yùn)算速度快的特點(diǎn)以及FFT算法的分級特性,實(shí)現(xiàn)了高速、高階FFT的流水線工作方式設(shè)計。通

2011-10-01 01:52:51 55

55 為了提高快速傅里葉變換( FFT)處理數(shù)據(jù)的實(shí)時性,本文利用現(xiàn)場可編程陣列( FPGA)邏輯資源豐富、運(yùn)算速度快的特點(diǎn)以及FFT算法的分級特性,實(shí)現(xiàn)了高速、高階FFT的流水線工作方式設(shè)計。通

2011-10-28 17:11:26 32

32 行為級仿真是提高流水線(Pipeline)ADC設(shè)計效率的重要手段。建立精確的行為級模型是進(jìn)行行為級仿真的關(guān)鍵。本文采用基于電路宏模型技術(shù)的運(yùn)算放大器模型,構(gòu)建了流水線ADC的行為

2012-04-05 15:37:55 21

21 電鍍流水線的PLC控制電鍍流水線的PLC控制電鍍流水線的PLC控制

2016-02-17 17:13:04 37

37 三菱plc裝配流水線課程設(shè)計

2016-12-17 15:26:59 28

28 裝配流水線控制系統(tǒng)設(shè)計

2016-12-17 15:26:59 14

14 分布式調(diào)度算法的流水線單位產(chǎn)能優(yōu)化設(shè)計_李世光

2017-01-12 20:03:43 0

0 電能計量設(shè)備自動檢定流水線調(diào)度優(yōu)化研究_方彥軍

2017-01-18 20:23:58 1

1 流水線狀態(tài)機(jī)20進(jìn)制,101序列檢測,8位加法器流水線的程序

2017-05-24 14:40:47 0

0 在航空微電子中心的某預(yù)研項(xiàng)目中,需要開發(fā)設(shè)計某32位浮點(diǎn)通用數(shù)字信號處理器(DSP)。本系統(tǒng)控制通路部分的設(shè)計采用超級哈佛及五級流水線結(jié)構(gòu)。本文分析了該流水線的設(shè)計過程,并對遇到的數(shù)據(jù)相關(guān)問題提出

2017-10-23 10:35:35 0

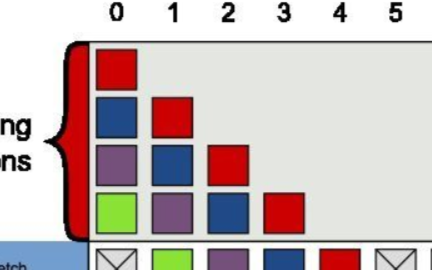

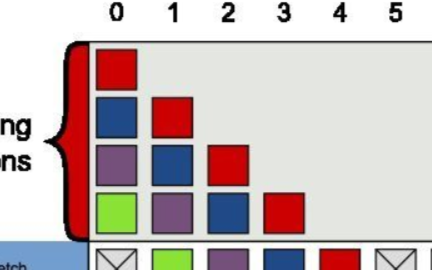

0 顏色表示了不同階段的可配置性或可編程性:綠色表示該流水線階段是完全可編程控制的,黃色表示該流水線階段可以配置但不是可編程的,藍(lán)色表示該流水線階段是由GPU固定實(shí)現(xiàn)的,開發(fā)者沒有任何控制權(quán)。實(shí)線表示該shader必須由開發(fā)者編程實(shí)現(xiàn),虛線表示該Shader是可選的.

2018-05-04 09:16:00 4111

4111

本應(yīng)用注釋討論了如何通過設(shè)計正確的時鐘電路和良好的模擬輸入網(wǎng)絡(luò),來優(yōu)化高速流水線ADC的性能,以及如何將ADC的高速不失真的數(shù)據(jù)輸送到FPGA或ASIC上。

2018-05-18 10:34:32 10

10 一級都在工作,大大提升了他的工作效率。在設(shè)計中,流水線CPU甚至?xí)榷嘀芷贑PU更好實(shí)現(xiàn)。由于數(shù)據(jù)是一級一級向下流,我們都無需進(jìn)行狀態(tài)機(jī)的狀態(tài)轉(zhuǎn)移來控制,只需要讓數(shù)據(jù)與他的控制信號同步流向器件。每一個

2018-07-16 09:20:07 6294

6294 異步電路因其具有低功耗、高性能和低電磁干擾的特性,正受到越來越多的關(guān)注。異步流水線是異步電路實(shí)現(xiàn)的主要形式,從而得到廣泛研究,實(shí)用的異步流水線結(jié)構(gòu)也被不斷提出,例如在文中提出的超高速異步流水線控制

2019-08-30 08:04:00 3416

3416

,并暫存中間數(shù)據(jù)的方法。 目的是將一個大操作分解成若干的小操作,每一步小操作的時間較小,所以能提高頻率,各小操作能并行 執(zhí)行,所以能提高數(shù)據(jù)吞吐率(提高處理速度)。 二. 什么時候用流水線設(shè)計 使用流水線一般是時序比較緊張

2018-09-25 17:12:02 7694

7694 如果有數(shù)字電路常識的人都知道,利用一塊組合邏輯電路去做8位的加法,其速度肯定比做2位的加法慢。因此這里可以采用4級流水線設(shè)計,每一級只做兩位的加法操作,當(dāng)流水線一啟動后,除第一個加法運(yùn)算之外,后面每經(jīng)過一個2位加法器的延時,就會得到一個結(jié)果。

2019-02-04 17:20:00 8869

8869 Blackfin BF608和BF609集成一個分析加速器——流水線視覺處理器。這些Blackfin處理器針對汽車駕駛員輔助系統(tǒng)、工業(yè)機(jī)器視覺和安防/監(jiān)控等各類應(yīng)用進(jìn)行了優(yōu)化。

2019-06-10 06:18:00 3182

3182 流水線的工作方式就象工業(yè)生產(chǎn)上的裝配流水線。在CPU中由5—6個不同功能的電路單元組成一條指令處理流水線,然后將一條X86指令分成5—6步后再由這些電路單元分別執(zhí)行,這樣就能實(shí)現(xiàn)在一個CPU時鐘周期完成一條指令,因此提高CPU的運(yùn)算速度。

2019-11-29 07:06:00 3152

3152 流水線的平面設(shè)計應(yīng)當(dāng)保證零件的運(yùn)輸路線最短,生產(chǎn)工人操作方便,輔助服務(wù)部門工作便利,最有效地利用生產(chǎn)面積,并考慮流水線安裝之間的相互銜接。為滿足這些要求,在流水線平面布置時應(yīng)考慮流水線的形式、流水線安裝工作地的排列方法等問題。

2019-11-28 07:07:00 2868

2868 流水線在工業(yè)生產(chǎn)中扮演著重要的角色,優(yōu)化流水線直接關(guān)系著產(chǎn)品的質(zhì)量和生產(chǎn)的效率,因此成為企業(yè)不得不關(guān)注的話題。

2019-11-28 07:05:00 2701

2701 流水線又稱為裝配線,一種工業(yè)上的生產(chǎn)方式,指每一個生產(chǎn)單位只專注處理某一個片段的工作。以提高工作效率及產(chǎn)量;按照流水線的輸送方式大體可以分為:皮帶流水裝配線、板鏈線、倍速鏈、插件線、網(wǎng)帶線、懸掛線及滾筒流水線這七類流水線。

2019-11-28 07:04:00 4174

4174 流水線主要是一種硬件設(shè)計的算法,如第一條中表述的流水線設(shè)計就是將組合邏輯系統(tǒng)地分割,并在各個部分(分級)之間插入寄存器,并暫存中間數(shù)據(jù)的方法。

2019-11-18 07:05:00 2537

2537 本人有過多年用FPGA做圖像處理的經(jīng)驗(yàn),在此也談一下自己的看法。用FPGA做圖像處理最關(guān)鍵的一點(diǎn)優(yōu)勢就是:FPGA能進(jìn)行實(shí)時流水線運(yùn)算,能達(dá)到最高的實(shí)時性。因此在一些對實(shí)時性要求非常高的應(yīng)用領(lǐng)域,做

2019-07-19 09:47:07 9503

9503 流水線設(shè)計就是將組合邏輯系統(tǒng)地分割,并在各個部分(分級)之間插入寄存器,并暫存中間數(shù)據(jù)的方法。目的是提高數(shù)據(jù)吞吐率(提高處理速度)。

2020-07-08 14:41:15 5

5 流水線設(shè)計是用于提高所設(shè)計系統(tǒng)運(yùn)行速度的一種有效的方法。為了保障數(shù)據(jù)的快速傳輸,必須使系統(tǒng)運(yùn)行在盡可能高的頻率上, 但如果某些復(fù)雜邏輯功能的完成需要較長的延時,就會使系統(tǒng)很難運(yùn)行在高的頻率上, 在這

2020-09-16 17:49:46 3

3 一、背景 自20世紀(jì)初美國人亨利路福特首次采用流水線的生產(chǎn)方法至今,流水線的發(fā)展已經(jīng)歷了百年。 由于流水線作業(yè)的高效,穩(wěn)定等優(yōu)勢,不斷被應(yīng)用于各類生產(chǎn)型企業(yè)。這個過程中不斷衍生優(yōu)化,逐漸形成了單一產(chǎn)品流水線

2020-11-02 13:55:21 1765

1765 所謂流水線處理,如同生產(chǎn)裝配線一樣,將操作執(zhí)行工作量分成若干個時間上均衡的操作段,從流水線的起點(diǎn)連續(xù)地輸入,流水線的各操作段以重疊方式執(zhí)行。這使得操作執(zhí)行速度只與流水線輸入的速度有關(guān),而與處理所需

2021-05-27 16:57:52 3133

3133 按照流水線的輸送方式大體可以分為:皮帶流水裝配線、板鏈線、倍速鏈、插件線、網(wǎng)帶線、懸掛線及滾筒流水線這七類流水線。

2021-07-05 11:12:18 9128

9128

在工程建造中,滾筒流水線演著重要的角色。在一些工程建造過程中,經(jīng)常看到滾筒流水線的身影。在工業(yè)不斷發(fā)展下的今天,滾筒流水線日益增長,走向多元化。滾筒流水線能夠長距離的輸送,而且支持重量大的貨物。

2021-07-08 09:32:56 2268

2268 目前組裝流水線的使用范圍是非常廣泛的,特別是在電子電器行業(yè)產(chǎn)品的組裝,組裝流水線使用的評價也是高的。目前組裝流水線適用范圍:電子廠,電腦廠,食品廠,建材廠等等行業(yè)。隨著它的發(fā)展,不少的企業(yè)人員都會問

2021-08-05 18:51:25 1637

1637 LED生產(chǎn)流水線輸送形式分為平面直線傳輸流水線、各種角度平面轉(zhuǎn)彎傳輸流水線、斜面上傳流水線、斜面下傳流水線這四種輸送方式,企業(yè)也是可以根據(jù)LED燈具生產(chǎn)狀況選擇合適自己的LED生產(chǎn)流水線輸送方式。選擇LED生產(chǎn)流水線時應(yīng)了解流水線各部分組成及功用。

2021-08-06 11:53:51 1354

1354 昀通科技流水線式UVLED固化爐在工作中可以與生產(chǎn)線對接,配合流水線生產(chǎn)達(dá)到快速固化的效果。需要固化的器材在經(jīng)過UV隧道式固化爐時,使其受到流水線內(nèi)UV固化光源的照射,讓器材上的膠水或油墨所含的光引發(fā)劑產(chǎn)生反應(yīng),在幾秒的時間內(nèi)完成固化。

2021-09-13 14:16:29 1700

1700 流水線一、定義流水線是指在程序執(zhí)行時多條指令重疊進(jìn)行操作的一種準(zhǔn)并行處理實(shí)現(xiàn)技術(shù)。各種部件同時處理是針對不同指令而言的,他們可同時為多條指令的不同部分進(jìn)行工作。? 把一個重復(fù)的過程分解為若干個子過程

2021-10-20 20:51:14 6

6 Mara-pipelines 是一個輕量級的數(shù)據(jù)轉(zhuǎn)換框架,具有透明和低復(fù)雜性的特點(diǎn)。其他特點(diǎn)如下: 基于非常簡單的Python代碼就能完成流水線開發(fā)。 使用 PostgreSQL 作為數(shù)據(jù)處理引擎

2021-11-16 18:20:00 3569

3569 本文解釋了流水線及其對 FPGA 的影響,即延遲、吞吐量、工作頻率的變化和資源利用率。

2022-05-07 16:51:10 7417

7417

Debug 網(wǎng)絡(luò)質(zhì)量的時候,我們一般會關(guān)注兩個因素:延遲和吞吐量(帶寬)。延遲比較好驗(yàn)證,Ping 一下或者 mtr[1] 一下就能看出來。這篇文章分享一個 debug 吞吐量的辦法。

2022-08-23 09:17:30 1564

1564 1989 年推出的 i486 處理器引入了五級流水線。這時,在 CPU 中不再僅運(yùn)行一條指令,每一級流水線在同一時刻都運(yùn)行著不同的指令。這個設(shè)計使得 i486 比同頻率的 386 處理器性能提升了不止一倍。

2022-09-22 10:04:23 2911

2911 為什么有些CPU的主頻更低,但運(yùn)算效率卻更高呢? 比如:51單片機(jī)30M主頻,STM32單片機(jī)20M主頻,執(zhí)行相同一段代碼可能主頻更低的STM32所花的時間更短。 這里就牽涉到CPU流水線的問題,本文圍繞CPU流水線描述相關(guān)內(nèi)容。

2022-10-24 14:34:48 5619

5619 隨著UVLED固化設(shè)備的普及應(yīng)用,很多工廠批量固化產(chǎn)品的時候都會選擇流水線式[UVLED固化爐]完成固化工藝環(huán)節(jié)。那么UVLED固化爐一定有它的優(yōu)勢所在今天我們就來介紹一下它的優(yōu)點(diǎn)。 流水線式

2022-12-13 16:50:51 1547

1547

stage:和聲明式的含義一致,定義流水線的階段。Stage 塊在腳本化流水線語法中是可選的,然而在腳本化流水線中實(shí)現(xiàn) stage 塊,可以清楚地在 Jenkins UI 界面中顯示每個 stage 的任務(wù)子集。

2023-01-13 15:34:18 1587

1587 字通信中,轉(zhuǎn)換器的動態(tài)性能通常比傳統(tǒng)的直流規(guī)格(如差分非線性(DNL)和積分非線性(INL))更重要。在大多數(shù)應(yīng)用中,流水線ADC的數(shù)據(jù)延遲幾乎無關(guān)緊要。 Maxim不斷為其流水線ADC產(chǎn)品組合開發(fā)新的轉(zhuǎn)換器。這些流水線ADC很好地補(bǔ)充了其采用其他架構(gòu)設(shè)計的ADC系列。

2023-02-25 09:28:18 6909

6909

iperf吞吐量測試指南

2023-04-03 15:40:26 2

2 之前看一篇論文《A Fast Approach for Generating Efficient Parsers on FPGAs》,里面主要講的是如何將P4的報文解析通過流水線技術(shù)映射到FPGA上

2023-04-08 14:15:04 1715

1715 流水線設(shè)計通常可以在一定程度上提升系統(tǒng)的時鐘頻率,因此常常作為時序性能優(yōu)化的一種常用技巧。如果某個原本單個時鐘周期完成的邏輯功能塊可以進(jìn)一步細(xì)分為若干個更小的步驟進(jìn)行處理,而且整個數(shù)據(jù)處理過程是單向

2023-05-08 10:55:14 2209

2209

jenkins 有 2 種流水線分為聲明式流水線與腳本化流水線,腳本化流水線是 jenkins 舊版本使用的流水線腳本,新版本 Jenkins 推薦使用聲明式流水線。文檔只介紹聲明流水線。

2023-05-17 16:57:31 1552

1552 stage:和聲明式的含義一致,定義流水線的階段。Stage 塊在腳本化流水線語法中是可選的,然而在腳本化流水線中實(shí)現(xiàn) stage 塊,可以清楚地在 Jenkins UI 界面中顯示每個 stage 的任務(wù)子集。

2023-07-20 16:43:16 1209

1209 電子發(fā)燒友網(wǎng)站提供《博科開放系統(tǒng)磁帶流水線、快速寫入和存儲優(yōu)化的TCP.pdf》資料免費(fèi)下載

2023-08-30 16:51:27 0

0 電子發(fā)燒友網(wǎng)站提供《基于流水線CORDIC算法通用數(shù)字調(diào)制器的FPGA實(shí)現(xiàn)方案.pdf》資料免費(fèi)下載

2023-10-27 09:46:19 1

1 Mara-pipelines 是一個輕量級的數(shù)據(jù)轉(zhuǎn)換框架,具有透明和低復(fù)雜性的特點(diǎn)。其他特點(diǎn)如下: 基于非常簡單的Python代碼就能完成流水線開發(fā)。 使用 PostgreSQL 作為數(shù)據(jù)處理引擎

2023-10-31 11:26:16 1453

1453

電子發(fā)燒友網(wǎng)站提供《TMS320VC5510 HPI吞吐量和優(yōu)化.pdf》資料免費(fèi)下載

2024-10-16 09:35:55 0

0 靈活性。 1. 理解生產(chǎn)流程 在進(jìn)行流水線布局優(yōu)化之前,首先要對SMT生產(chǎn)流程有一個深入的理解。這包括: 物料準(zhǔn)備 :包括錫膏、貼片、元件等的準(zhǔn)備。 印刷 :使用錫膏印刷機(jī)將錫膏印刷到PCB上。 貼裝 :使用貼片機(jī)將元件精確地放置到P

2024-11-14 09:11:31 1920

1920

電子發(fā)燒友App

電子發(fā)燒友App

評論