PCIe規(guī)范由PCISIG組織進(jìn)行發(fā)布的,PCISIG其英文全稱為:Peripheral Component Interconnect Special Interest Group(外圍部件互連專業(yè)組),簡稱PCISIG。

該組織擁有并管理著開放式行業(yè)標(biāo)準(zhǔn)——PCI規(guī)范。隨著行業(yè)的I/O需求的發(fā)展,該組織負(fù)責(zé)定義和實(shí)現(xiàn)新的行業(yè)標(biāo)準(zhǔn)I/O(輸入/輸出)規(guī)范。目前,全球共有900多家業(yè)界領(lǐng)先公司成為了PCI-SIG成員。

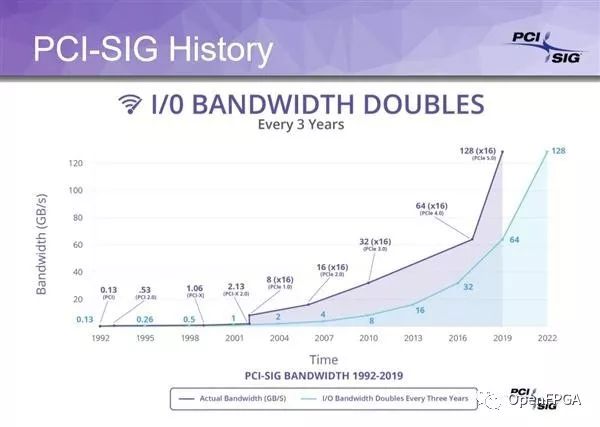

看下PCIe發(fā)展歷程:

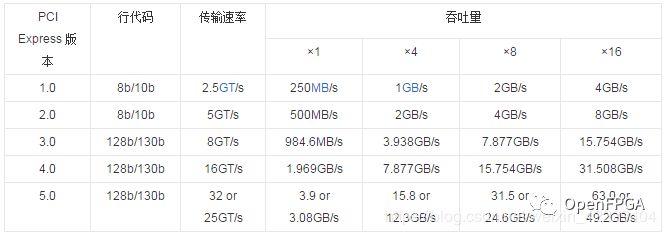

PCIE相關(guān)概念:

傳輸速率為每秒傳輸量GT/s,而不是每秒位數(shù)Gbps,因?yàn)閭鬏斄堪ú惶峁╊~外吞吐量的開銷位;比如 PCIe 1.x和PCIe 2.x使用8b / 10b編碼方案,導(dǎo)致占用了20% (= 2/10)的原始信道帶寬。

GT/s —— Giga transation per second (千兆傳輸/秒),即每一秒內(nèi)傳輸?shù)拇螖?shù)。重點(diǎn)在于描述物理層通信協(xié)議的速率屬性,可以不和鏈路寬度等關(guān)聯(lián)。

Gbps —— Giga Bits Per Second (千兆位/秒)。GT/s 與Gbps 之間不存在成比例的換算關(guān)系。

PCIE帶寬計(jì)算

PCIe 吞吐量(可用帶寬)計(jì)算方法:

吞吐量 = 傳輸速率 * 編碼方案

例如:PCI-e2.0 協(xié)議支持 5.0 GT/s,即每一條Lane 上支持每秒鐘內(nèi)傳輸 5G個Bit;但這并不意味著 PCIe 2.0協(xié)議的每一條Lane支持 5Gbps 的速率。

為什么這么說呢?因?yàn)镻CIe 2.0 的物理層協(xié)議中使用的是 8b/10b 的編碼方案。即每傳輸8個Bit,需要發(fā)送10個Bit;這多出的2個Bit并不是對上層有意義的信息。

那么, PCIe 2.0協(xié)議的每一條Lane支持 5 * 8 / 10 = 4 Gbps = 500 MB/s 的速率。

以一個PCIe 2.0 x8的通道為例,x8的可用帶寬為 4 * 8 = 32 Gbps = 4 GB/s。

同理,

PCI-e3.0 協(xié)議支持 8.0 GT/s, 即每一條Lane 上支持每秒鐘內(nèi)傳輸 8G個Bit。

而PCIe 3.0 的物理層協(xié)議中使用的是 128b/130b 的編碼方案。即每傳輸128個Bit,需要發(fā)送130個Bit。

那么, PCIe 3.0協(xié)議的每一條Lane支持 8 * 128 / 130 = 7.877 Gbps = 984.6 MB/s 的速率。

一個PCIe 3.0 x16的通道,x16 的可用帶寬為 7.877 * 16 = 126.031 Gbps = 15.754 GB/s。

由此可計(jì)算出上表中的數(shù)據(jù)

目前,僅有Intel的企業(yè)級SLC固態(tài)盤Ruler SSD直接以PCIe 5.0規(guī)范做傳輸設(shè)計(jì)。

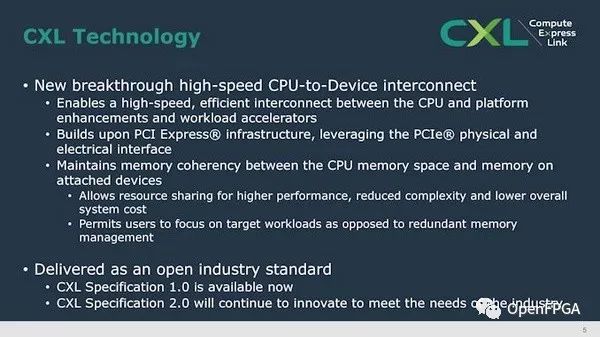

為應(yīng)對各領(lǐng)域日益增長的超高速帶寬需求,英特爾推出了全新的互聯(lián)協(xié)議Compute EXpress Link(CXL),面向超極數(shù)據(jù)中心,高性能計(jì)算和AI等領(lǐng)域,可有效解決未來所遇到的負(fù)載瓶頸。

據(jù)了解,Compute Express Link(CXL)1.0協(xié)議能幫助CPU與GPU、FPGA或其他加速器之間實(shí)現(xiàn)高效高速互聯(lián),帶來更高的帶寬和更好的內(nèi)存一致性。CXL基于PCIe 5.0基礎(chǔ)上打造,采用常規(guī)PCI-Express接口,并向下兼容當(dāng)前設(shè)備,不用通過專門接口也能實(shí)現(xiàn)很好兼容,大大簡化服務(wù)器硬件設(shè)計(jì)難度,降低了整體系統(tǒng)成本。

具體性能表現(xiàn)未透露,不過已知PCIe 5.0理論帶寬速率是PCIe gen 4.0兩倍(單通道32Gbps),毋庸置疑CXL 1.0的到來勢必會大大提升平臺性能。

與此同時,英特爾還宣布與華為、思科、戴爾易安信、Facebook、阿里巴巴集團(tuán)、谷歌、惠普以及微軟等成立共同合作發(fā)展聯(lián)盟,與聯(lián)盟成員共享技術(shù)成果,并共同持續(xù)開發(fā)。

審核編輯 :李倩

-

通信協(xié)議

+關(guān)注

關(guān)注

28文章

1092瀏覽量

42182 -

PCIe

+關(guān)注

關(guān)注

16文章

1461瀏覽量

88467 -

物理層

+關(guān)注

關(guān)注

1文章

170瀏覽量

35653

原文標(biāo)題:PCIe 5.0 標(biāo)準(zhǔn)

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

【概念產(chǎn)品】后置熱插拔雙盤位硬盤盒,讓PCIe插槽秒變磁盤陣列

總線授時卡優(yōu)勢解讀 #雙模pcie授時卡 #北斗pcie授時卡 #pcie授時板卡 #總線 #同步天下

【「芯片設(shè)計(jì)基石——EDA產(chǎn)業(yè)全景與未來展望」閱讀體驗(yàn)】--EDA了解與發(fā)展概況

新思科技在中國30周年的發(fā)展歷程回顧

嵌入式接口通識知識之PCIe接口

NVMe高速傳輸之?dāng)[脫XDMA設(shè)計(jì)17:PCIe加速模塊設(shè)計(jì)

寶馬集團(tuán)車載總線技術(shù)的發(fā)展歷程

PCIe協(xié)議分析儀能測試哪些設(shè)備?

鴻蒙發(fā)展歷程

智能氮?dú)夤竦?b class='flag-5'>發(fā)展歷程和前景展望

PCIe插槽秒變M.2存儲倉!免拆機(jī)維護(hù)神器M.2 NVMe轉(zhuǎn)PCIe 4.0 x4 硬盤抽取盒!#pcie

nvme IP開發(fā)之PCIe上

混合信號設(shè)計(jì)的概念、挑戰(zhàn)與發(fā)展趨勢

集成電路和光子集成技術(shù)的發(fā)展歷程

PCIe發(fā)展歷程與相關(guān)概念

PCIe發(fā)展歷程與相關(guān)概念

評論